#### 3V 915MHZ SPREAD-SPECTRUM TRANSMITTER IC

### Typical Applications

- Direct Sequence Spread Spectrum

- Spread Spectrum Cordless Phones

- Portable Battery Powered Equipment

- GMSK, QPSK, DQPSK, QAM Modulation

- 915MHz ISM Applications

### Product Description

The RF2909 is a monolithic integrated transmitter IC capable of universal direct modulation. The quadrature modulator allows for a variety of modulation formats and compound carriers. The transmitter has two power control modes. Two inputs can be controlled digitally for stepping output power 1 mW, 10 mW, or 70 mW output power. Or, the output level can be adjusted by an analog input from 1 mW to 80 mW. The quadrature mixers have differential inputs, and are internally biased; a DC blocking capacitor is required if external DC levels are present. The LO is split with a passive network tuned for 915 MHz.

Optimum Technology Matching® Applied Si BJT GaAs HBT GaAs MESFET Si Bi-CMOS SiGe HBT Si CMOS

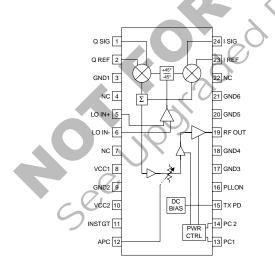

Functional Block Diagram

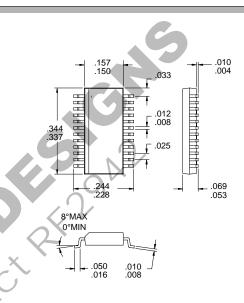

Package Style: SSOP-24

### Features

- 2.7V to 5V Power Supply

- 1mW, 10mW, 70mW Digital Output Power

- 20dB Analog Power Control Range

- Excellent Phase & Amplitude Balance

- Compatible with the RF2908

#### Ordering Information

RF2909

3V 915MHz Spread-Spectrum Transmitter IC

RF2909 PCBA

Fully Assembled Evaluation Board

RF Micro Devices, Inc.

Tel (336) 664 1233

7628 Thorndike Road

Fax (336) 664 0454

Greensboro, NC 27409, USA

http://www.rfmd.com

11

### **Absolute Maximum Ratings**

| Parameter                             | Rating               | Unit            |

|---------------------------------------|----------------------|-----------------|

| Supply Voltage                        | -0.5 to +5.5         | V <sub>DC</sub> |

| Power Down Voltage (V <sub>PD</sub> ) | V <sub>DD</sub> +0.4 | V <sub>DC</sub> |

| Input LO and RF Levels                | +6                   | dBm             |

| Operating Ambient Temperature         | -40 to +85           | °C              |

| Storage Temperature                   | -40 to +150          | C°              |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Deremeter                             |              | Specificatior |            | Unit   | Condition                                                                           |  |

|---------------------------------------|--------------|---------------|------------|--------|-------------------------------------------------------------------------------------|--|

| Parameter                             | Min.         | Тур.          | Max.       |        |                                                                                     |  |

| Carrier Input (LO IN)                 |              |               |            |        | T=25 °C, V <sub>DD</sub> =3.3V                                                      |  |

| Frequency Range                       | 100          | 902-928       | 1100       | MHz    | Phase shift optimized for 915MHz                                                    |  |

| Power Level                           |              | -10           |            | dBm    | Differential                                                                        |  |

| Input Impedance                       |              | 50            |            | Ω      | 915MHz                                                                              |  |

| Modulation Input                      |              |               |            |        |                                                                                     |  |

| Frequency Range                       | DC           | 10            | 500        | MHz    | 50Ω source, I,Q=500mV <sub>p-p</sub>                                                |  |

| Reference Voltage (V <sub>REF</sub> ) |              | 1.7           |            | V      |                                                                                     |  |

| Modulation for P <sub>OUT</sub>       |              | 500           |            | mVp    | Differential, $1V_p$ single ended                                                   |  |

| Power (I & Q)                         |              |               |            |        |                                                                                     |  |

| Maximum Modulation (I & Q)            |              | 1             |            | Vp     | Differential, 1.5Vp single ended                                                    |  |

| Quadrature Phase Error                |              | 3             | 5          | °      | $\cap$                                                                              |  |

| I/Q Amplitude Imbalance               |              | .35           |            | db     |                                                                                     |  |

| Input Impedance                       |              | 3             |            | kΩ     | Differential                                                                        |  |

|                                       |              |               |            | , L    | V <sub>DD</sub> =3.3V, LO power=-10dBm,                                             |  |

| RF Output                             |              |               |            |        | LO frequency=915MHz, SSB, I/Q=1V <sub>PP</sub>                                      |  |

|                                       |              |               |            | $\sim$ | sine wave, 100KHz                                                                   |  |

| Digital Output Power                  |              | 1, 10, 70     |            | mW     | See Table I for control logic                                                       |  |

| Output Impedance                      |              | 50            |            | Ω      |                                                                                     |  |

| Output VSWR                           |              |               | 1.5:1      |        | With external matching (see app. schematic)                                         |  |

| Second Harmonic Output                |              | -25           | $\sim$     | dBc    |                                                                                     |  |

| Other Harmonics Output                |              | -30           | $\bigcirc$ | dBc    |                                                                                     |  |

| Sideband Suppression                  |              | 30            |            | dB     | P <sub>OUT</sub> =10mW                                                              |  |

| Carrier Suppression                   |              | 27            |            | dB     | Modulation DC offset can be externally                                              |  |

|                                       |              | $\mathbf{}$   |            |        | adjusted for optimum suppression. Carrier suppression is then typically better than |  |

|                                       |              | 0             |            |        | 40dB.                                                                               |  |

| Output Level Control                  |              |               |            |        |                                                                                     |  |

| Analog Power Control Range            | 20           | <u>у</u>      |            | dB     |                                                                                     |  |

| Analog Power Control Voltage          | 0            |               | 3.6        | V      | Input voltage to pin 12 must be less than                                           |  |

| (APC)                                 |              |               |            |        | 3.6V or V <sub>CC</sub> (whichever is less).                                        |  |

| Analog Power Control Input<br>Current | $\mathbf{O}$ |               | 1          | μΑ     |                                                                                     |  |

| Analog Power Output                   |              | 80            |            | mW     | V <sub>APC</sub> =2.8V, PC1="0", PC2="0"                                            |  |

| Digital Power Output, High            |              | 70            |            | mW     | APC=0V, PC 1="0", PC 2="1"                                                          |  |

| Digital Power Output, Med             |              | 10            |            | mW     | APC=0V, PC 1="1", PC 2="0"                                                          |  |

| Digital Power Output, Low             |              | 1             |            | mW     | APC=0V, PC 1="0", PC 2="0"                                                          |  |

| PC 1/PC 2 "ON"                        |              |               | 1          |        | Threshold Voltage                                                                   |  |

| PC 1/PC 2 "OFF"                       | 2            |               |            |        | Threshold Voltage                                                                   |  |

| Standby Mode                          |              |               |            |        |                                                                                     |  |

| Turn On/Off Time                      |              | 0.15          | 1          | μS     |                                                                                     |  |

| Power Down "ON"                       | 2            |               |            | V      | Threshold voltage; Part is turned "ON"                                              |  |

| Power Down "OFF"                      |              |               | 1          | V      | Threshold voltage; Part is turned "OFF"                                             |  |

| Parameter    |      | Specificatio | n          | Unit     | Condition                                                           |  |

|--------------|------|--------------|------------|----------|---------------------------------------------------------------------|--|

|              | Min. | Тур.         | Typ. Max.  |          | Condition                                                           |  |

| Power Supply |      |              |            |          |                                                                     |  |

| Voltage      | 0.7  | 3.3          | 5.0        | V<br>V   | Specifications<br>Operating limits                                  |  |

| Current      | 2.7  | 175          | 5.0<br>200 | mA       | Total, Digital High Power, V <sub>APC</sub> , V <sub>PC1</sub> =0V, |  |

| outon        |      | 110          | 200        | 110 (    | $V_{PC2}=V_{CC}$                                                    |  |

|              |      | 45           | 60         |          | Total, Digital Medium Power, V <sub>APC</sub> ,                     |  |

|              |      |              |            |          | $V_{PC2}=0V, V_{PC1}=V_{CC}$                                        |  |

|              |      | 30           | 40         | mA       | Total, Digital Low Power, V <sub>APC</sub> , V <sub>PC1</sub> ,     |  |

|              |      |              |            |          | V <sub>PC2</sub> =0V                                                |  |

|              |      | 130          | 180        | mA       | Total, Linear Power, V <sub>APC</sub> =2.8V, V <sub>PC1</sub> ,     |  |

|              |      | 1 5          | F          | m۸       | V <sub>PC2</sub> =0V<br>PLL Buffer amp on.                          |  |

|              |      | 1.5          | 5<br>1     | mA<br>μA | Standby mode                                                        |  |

|              |      |              |            |          | $\mathcal{V}$                                                       |  |

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interface Schematic |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1   | Q SIG    | Baseband input to the Q mixer. A DC bias of approximately 1.7V is<br>present at this pin.A DC blocking capacitor is needed if the signal has a<br>different DC level. Maximum output power is obtained when the input<br>signal has a peak-to-peak amplitude of 1V. The input impedance of this<br>pin is $3k\Omega$ . The REF and SIG inputs are interchangeable. If swapping<br>the I SIG and I REF pins, the Q SIG and Q REF also need to be<br>swapped to maintain the correct phase. The SIG and REF pins may be<br>driven deferentially to increase conversion gain. |                     |

| 2   | Q REF    | Reference voltage for the Q mixer. This voltage should be the same as the DC voltage supplied to the Q SIG pin. To obtain a carrier suppression of better than 25dB it may be tuned $\pm 0.15$ V (relative to the Q SIG DC voltage). Without tuning, the carrier suppression will typically be better than 25dB. The input impedance of this pin is about 3 k $\Omega$ .                                                                                                                                                                                                   | See pin 1.          |

| 3   | GND 1    | Ground connection for the modulator circuits. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |

| 4   | NC       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 5   | LO IN+   | Balanced LO Input Pin. This pin is internally DC biased and should be DC blocked if connected to a device with a DC level present. For single-<br>ended input operation, one pin is used as an input and the other LO input is AC coupled to ground. The balanced input impedance is $100 \Omega$ . The single-ended input impedance is $50 \Omega$ .                                                                                                                                                                                                                      | LO IN+ O            |

| 6   | LO IN-   | Same as pin 4, except complementary input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | See pin 5.          |

| 7   | NC       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 8   | VCC1     | This pin is used to supply $V_{cc}$ to the modulator circuits. A RF bypass capacitor should be connected directly to this and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |

| 9   | GND2     | Ground connection. This pin is used for RF ground of the power control circuitry and the PA driver amplifier. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                                                                                                                                                   |                     |

| 10  | VCC2     | This pin is used to supply $V_{cc}$ to the power control and pre amp circuitry. A RF bypass capacitor should be connected directly to this and ground.                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |

| 11  | INSTGT   | Interstage bias point between pre amp and power amp. This pin should be pulled up to $V_{\rm cc}$ with an 8.2nH inductor for 915MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                       | See pin 18.         |

| 12  | APC      | Analog power control input. This pin can be used as a linear power out-<br>put control with a range of 20 dB. Maximum output power is achieved<br>when APC is high. APC is "wire-or'd" with the digital controls, therefore<br>should be low when using the digital control. The DC input voltage to<br>the pin should always be less than 3.6V.                                                                                                                                                                                                                           | APC O→              |

| 13  | PC 1     | This digital power control input sets the medium current and power out-<br>put, 10mW, It is "wire-or'd" with APC and PC 2 and can be overcome<br>by either, Therefore, APC and PC 2 must be low to use this setting.                                                                                                                                                                                                                                                                                                                                                       | PC 1 O-+            |

| 14  | PC 2     | This digital power control input set the high current and power output, 100mW. It is "wire-or'd" with APC and PC 1 and can override both of those controls. Therefore, PC 2 must be low to use other settings.                                                                                                                                                                                                                                                                                                                                                             |                     |

| 15  | TX PD    | Enables all of the IC except for the LO buffer when > 2V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TX PD O-+           |

| 16  | CPLEON   | Enables the LO buffer amp when > 2V.This can be switched on and off<br>independently of the rest of the IC. This amp draws 1.5mA typi-<br>cally.This can be used to minimize load pulling of the VCO when the<br>transmitter is turned on. Buffer amp is off when < 1V.                                                                                                                                                                                                                                                                                                    |                     |

| 17  | GND3     | Ground connection for RF Power Amp. Keep traces physically short<br>and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |

| 18  | GND4     | Same as pin16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Interface Schematic |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 19  | RF OUT   | Power Amp output, open collector output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INSTGT O O RF OUT   |

| 20  | GND5     | Same as pin 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

| 21  | GND6     | Same as pin 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

| 22  | NC       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

| 23  | IREF     | Reference voltage for the I mixer. This voltage should be the same as the DC voltage supplied to the I SIG pin. To obtain a carrier suppression of better than 25dB it may be tuned $\pm 0.15V$ (relative to the I SIG DC voltage). Without tuning, the carrier suppression will typically be better than 25dB. The input impedance of this pin is $3k\Omega$ .                                                                                                                                                                                                | I SIG OT TO I REF   |

| 24  | I SIG    | Baseband input to the I mixer. A DC bias of approximately 1.7V is present at this pin.A DC blocking capacitor is needed if the signal has a different DC level. Maximum output power is obtained when the input signal has a peak to peak amplitude of 1V. The input impedance of this pin is about 3 k $\Omega$ . The REF and SIG inputs are interchangeable. If swapping the I SIG and I REF pins, the Q SIG and Q REF also need to be swapped to maintain the correct phase. The SIG and REF pins may be driven differentially to increase conversion gain. | See pin 23.         |

#### Table I

|                   | be driven differentially to increase conversion gain. |           |      |      |                     |                                                         |

|-------------------|-------------------------------------------------------|-----------|------|------|---------------------|---------------------------------------------------------|

| able I            |                                                       |           |      |      | X                   |                                                         |

| Operation<br>Mode | TX<br>PD                                              | PLL<br>ON | PC 1 | PC 2 | APC                 | Function                                                |

| Sleep Mode        | Low                                                   | Low       | Low  | Low  | 0V                  | Entire chip is powered down. Total $I_{cc}$ <1µA.       |

| PLL Buffer        | Low                                                   | High      | Low  | Low  | 0V                  | LO Buffer is on. I <sub>cc</sub> =1.5mA                 |

| Linear Po Mode    | High                                                  | High      | Low  | Low  | 0-V <sub>cc</sub> V | Transmitter in on. Power output is proportional to APC. |

| Digital Po Mode   | High                                                  | High      | Low  | Low  | 0V                  | Transmitter is on. Power out is 1 mW.                   |

| Medium Power      | High                                                  | High      | High | Low  | 0V                  | Transmitter is on. Power out is 10mW.                   |

| High Power        | High                                                  | High      | Low  | High | 0V                  | Transmitter is on. Power out is 70mW.                   |

| See               | 39                                                    | 95        |      |      |                     |                                                         |

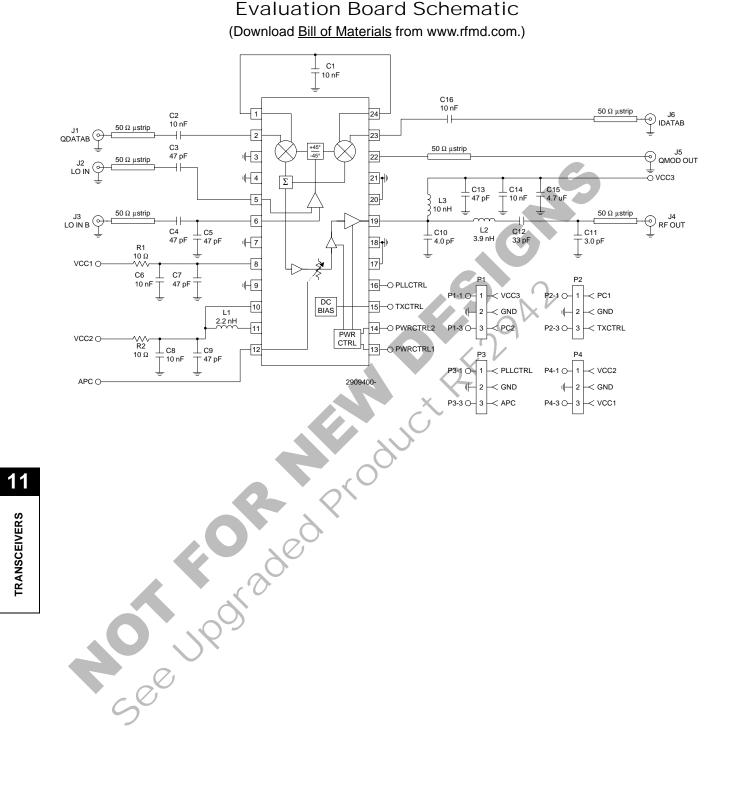

Evaluation Board Layout Board Size 1.7440" x 1.7480" J1 QDATAB 2909410(-) JJ2° LOIN ° °B0ard ⊳B0ard EVAL 2 AZ FQUT See upor ade

Rev B1 010904