Monolithic Digital IC

LB1955

## Three-Phase Brushless Motor Driver

### **Functions**

• The LB1955 is a 3-phase brushless motor driver IC that is optimal for applications such as driving the drum motor in VCRs.

### **Features**

- Current linear drive

- FG and PG free

- Single-voltage power supply

- Built-in AGC circuit

- Built-in thermal shutdown circuit

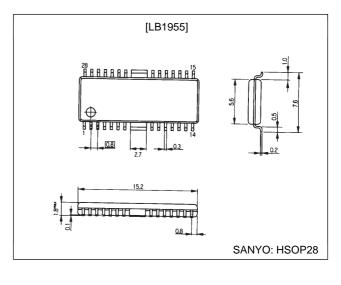

## **Package Dimensions**

unit: mm

#### 3222-HSOP28

### **Specifications**

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol              | Conditions         | Ratings     | Unit |

|-----------------------------|---------------------|--------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max |                    | 14.5        | V    |

| Maximum output current      | I <sub>OUT</sub>    |                    | 1.0         | A    |

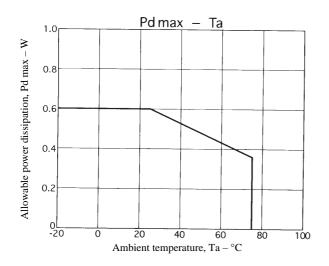

| Allowable power dissipation | Pdmax               | Independent device | 0.60        | W    |

| Operating temperature       | Topr                |                    | -20 to +75  | °C   |

| Storage temperature         | Tstg                |                    | -55 to +150 | °C   |

### Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter            | Symbol          | Conditions   | Ratings      | Unit  |

|----------------------|-----------------|--------------|--------------|-------|

| Supply voltage       | V <sub>CC</sub> |              | 10.2 to 13.8 | V     |

| Hall input amplitude | Vhall           | At the input | 70 to 500    | mVp-p |

| VC input voltage     | V <sub>C</sub>  |              | 0 to 5       | V     |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

# Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 12 V

| Parameter                                        | Symbol Conditions     |                                                                                                                                                                           |                                   | Ratings     |      |      | – Unit |     |

|--------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|------|------|--------|-----|

| Parameter Sym                                    |                       | Conditions                                                                                                                                                                |                                   |             | min  | typ  | max    |     |

| [Power Supply]                                   |                       |                                                                                                                                                                           |                                   |             |      |      |        |     |

| Current drain                                    | I <sub>CC</sub>       | V <sub>C</sub> = 0 V, LCTR = 6 V                                                                                                                                          |                                   |             | 7.0  | 10.0 | 13.0   | mA  |

| IC internal power supply                         | V <sub>REF</sub>      |                                                                                                                                                                           |                                   |             | 4.75 | 5.0  | 5.25   | V   |

| [Output]                                         |                       |                                                                                                                                                                           |                                   |             |      |      |        |     |

|                                                  | V 1                   | I <sub>O</sub> = 400 mA Sink side                                                                                                                                         |                                   |             |      |      | 0.4    | V   |

| Output saturation voltage                        | V <sub>O(sat)</sub> 1 | $V_{\rm C} = 5  \rm V,  R_{\rm f} = 0  \rm G$                                                                                                                             | 2                                 | Source side |      |      | 1.5    | V   |

| Output saturation voltage 2                      | V <sub>O(sat)</sub> 2 | I <sub>O</sub> = 800 mA Sink side                                                                                                                                         |                                   |             |      |      | 0.7    | V   |

| Oulput Saturation voltage 2                      |                       | $V_{C} = 5 V, R_{f} = 0 \Omega$ Source side                                                                                                                               |                                   |             |      |      | 2.0    | V   |

| 3-phase output current ripple                    | lor                   | $I_0 = 100 \text{ mA}, \text{ R}_{\text{f}} = 0.47 \Omega$                                                                                                                |                                   | -5          |      | +5   | %      |     |

| [Hall Amplifier]                                 |                       | ·                                                                                                                                                                         |                                   |             |      | ·    |        | -   |

| Input offset voltage                             | VHoff                 |                                                                                                                                                                           |                                   |             | -20  |      | +20    | mV  |

| Input hise current                               | IHb                   | V <sub>AGC</sub> = 1.4 V                                                                                                                                                  | U <sub>IN</sub>                   |             |      |      | 10     | μA  |

| Input bias current                               | טרוו                  | AGC - 1.4 V                                                                                                                                                               | V <sub>IN</sub> , W <sub>IN</sub> |             |      |      | 5      | μA  |

| Common-mode input voltage range                  | V <sub>HCM</sub>      |                                                                                                                                                                           |                                   |             | 2.2  |      | 5.0    | V   |

| [Control]                                        |                       |                                                                                                                                                                           |                                   |             |      |      |        | -   |

| VC pin input bias current                        | I <sub>VCb</sub>      | V <sub>C</sub> = 0 V                                                                                                                                                      |                                   |             | -10  | -1.3 |        | μA  |

| 0                                                |                       | $R_{f} = 0.47 \Omega, I_{O} \ge 10 \text{ mA}$                                                                                                                            |                                   |             | 0.05 |      |        | .,  |

| Control start voltage                            | V <sub>THVC</sub>     | With the Hall input logic fixed                                                                                                                                           |                                   |             | 2.25 | 2.5  | 2.75   | V   |

|                                                  | •                     | $\label{eq:Rf} \begin{array}{l} R_{f} = 0.47 \; \Omega, \; \Delta I_{O} = 200 \; \text{mA} \\ \\ \text{With the Hall input logic fixed and VG shorted to RF} \end{array}$ |                                   |             |      |      |        |     |

| Open-loop control gain                           | G <sub>MVC</sub>      |                                                                                                                                                                           |                                   |             | 0.72 | 0.9  | 1.08   | A/V |

| [PG]                                             |                       |                                                                                                                                                                           |                                   |             |      |      |        |     |

| PG Hall amplifier                                |                       |                                                                                                                                                                           |                                   |             | 10   |      |        |     |

| input offset voltage                             | V <sub>PGoff</sub>    | Design target                                                                                                                                                             |                                   |             | -10  |      | +10    | mV  |

| Peak hold charge current                         | I <sub>SHCHG</sub>    | (U, V, W) = (L, L, H)                                                                                                                                                     |                                   |             |      | 30   |        | μA  |

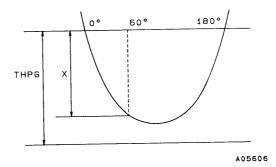

| PG comparator threshold                          | THPG                  | Design target*                                                                                                                                                            | Design target*                    |             |      | 117  |        | %   |

| PG output high-level voltage                     | V <sub>PGH</sub>      |                                                                                                                                                                           |                                   |             | 4.5  |      | 5.2    | V   |

| PG leakage current                               | ILEAKPG               |                                                                                                                                                                           |                                   |             | -10  | 0    | +10    | μA  |

| [FG]                                             |                       |                                                                                                                                                                           |                                   |             |      |      |        |     |

|                                                  |                       | In the back emf Schmitt input increasing direction, Design target                                                                                                         |                                   |             |      | 100  |        | mV  |

| hysteresis width                                 | V <sub>SCHG</sub>     | In the back emf Schmitt input decreasing direction, Design target                                                                                                         |                                   |             |      | 0    |        | mV  |

| Ringing canceller Schmitt input hysteresis width | V <sub>SCHR</sub>     | In the Schmitt input increasing direction, Design target                                                                                                                  |                                   |             |      | 180  |        | mV  |

|                                                  |                       | In the Schmitt input decreasing direction, Design target                                                                                                                  |                                   |             | -20  | 0    | +20    | mV  |

| FG output high-level voltage                     | V <sub>FGH</sub>      | FGR = 0 V                                                                                                                                                                 |                                   |             | 4.5  |      | 5.2    | V   |

| FG leakage current                               | ILEAKFG               |                                                                                                                                                                           |                                   |             | -10  | 0    | +10    | μA  |

| [TSD]                                            | LE/WW O               | 1                                                                                                                                                                         |                                   | I           |      |      |        |     |

| Thermal shutdown operating temperature           | TTSD                  | Design target                                                                                                                                                             |                                   |             |      | 180  |        | °C  |

| Thermal shutdown<br>temperature hysteresis width | ΔTSD                  | Design target                                                                                                                                                             |                                   |             |      | 15   |        | °C  |

Note: \* is provided for when X is the peak value at the 60° position of the lower side of the  $U_{IN}$ 1 Hall amplifier input: THPG = 1.17X.

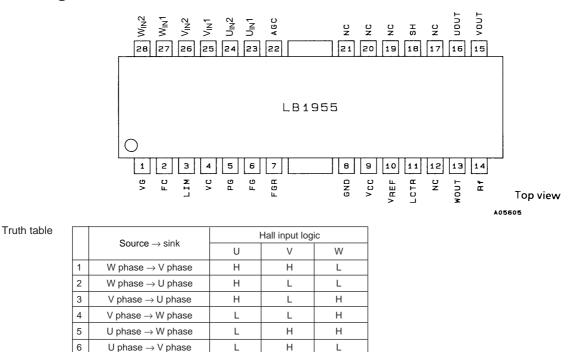

### **Pin Assignment**

Note: The Hall input "H" and "L" values are defined as follows: "H" means that for that phase the (+) input is higher than the (-) input, and "L" means that for that phase the (+) input is lower than the (-) input. However, note that an input potential difference corresponding to the Hall to output gain is required.

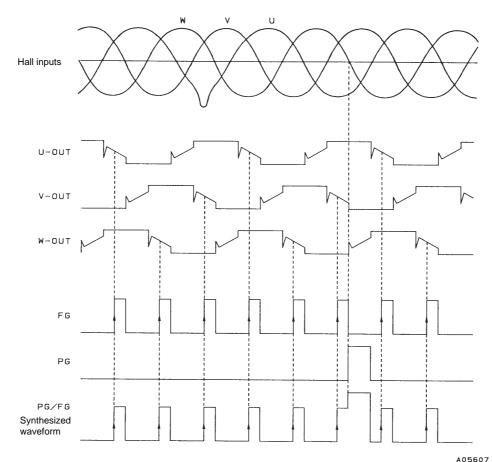

### **Timing Charts**

Note: The Hall inputs are defined as follows:  $U = U_{IN}1 - U_{IN}2$ ,  $V = V_{IN}1 - V_{IN}2$ , and  $W = W_{IN}1 - W_{IN}2$ . Inputs to the Hall input pins must be applied in the phase order shown in the timing chart.

#### **Pin Functions**

| Pin No.    | Pin                                  | Function                                                                                           |  |  |  |

|------------|--------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| 23, 24     | U <sub>IN</sub> 1, U <sub>IN</sub> 2 | U phase Hall element input                                                                         |  |  |  |

| 25, 26     | V <sub>IN</sub> 1, V <sub>IN</sub> 2 | V phase Hall element input                                                                         |  |  |  |

| 27, 28     | W <sub>IN</sub> 1, W <sub>IN</sub> 2 | W phase Hall element input                                                                         |  |  |  |

| 16         | UOUT                                 | U phase output                                                                                     |  |  |  |

| 15         | VOUT                                 | V phase output                                                                                     |  |  |  |

| 13         | WOUT                                 | W phase output                                                                                     |  |  |  |

| 11         | LCTR                                 | Pin connected to the center points of the coils that are Y-connected to the U, V, and W outputs.   |  |  |  |

| 9          | V <sub>CC</sub>                      | Power supply                                                                                       |  |  |  |

| 10         | V <sub>REF</sub>                     | Reference voltage output                                                                           |  |  |  |

| 8          | GND                                  | GND                                                                                                |  |  |  |

| 14         | Rf                                   | Output current detection                                                                           |  |  |  |

| 1          | VG                                   | Closed loop control gain switching                                                                 |  |  |  |

| 2          | FC                                   | Speed control loop frequency characteristics correction                                            |  |  |  |

| 3          | LIM                                  | Output current limit setting                                                                       |  |  |  |

| 4          | VC                                   | Speed control                                                                                      |  |  |  |

| 5          | PG                                   | PG waveform output                                                                                 |  |  |  |

| 6          | FG                                   | FG waveform output (FGR shorted to GND)                                                            |  |  |  |

| 7          | FGR                                  | PG/FG synthesized output (FGR shorted to PG)                                                       |  |  |  |

| 18         | SH                                   | PG waveform sample-and-hold circuit capacitor connection                                           |  |  |  |

| 22         | AGC                                  | Connection for the capacitor used by the AGC circuit, which holds the input gain at a fixed level. |  |  |  |

| 12, 17, 19 | NC                                   | No connection                                                                                      |  |  |  |

| 20, 21     |                                      |                                                                                                    |  |  |  |

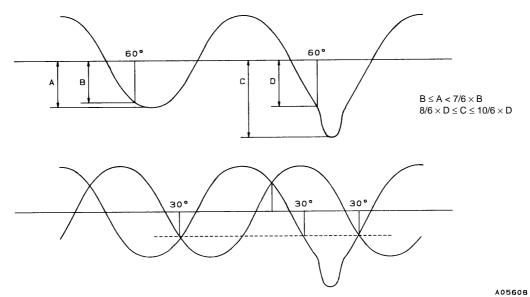

### **Recommended Special Magnetization Waveforms**

Note: Note that the intersections between the special magnetization and general waveforms and the intersections between pairs of general waveforms must be set up to be 30° apart.

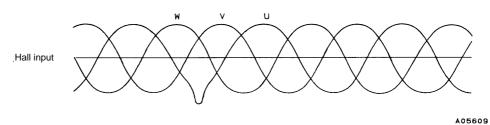

#### Hall Input Order

Note: The Hall input order must be set up to be  $W \to V \to U.$

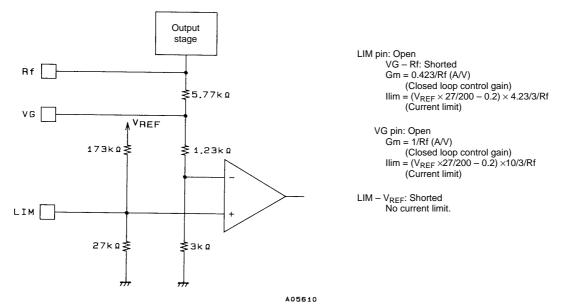

#### VG and LIM Pin Usage

function.

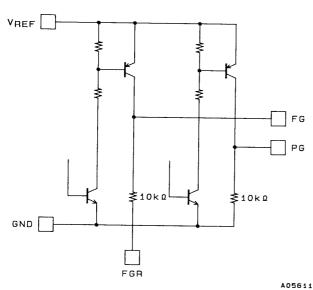

PG and FG Pin Output Circuits

Note: This current limiting function is for protection against unusual and abnormal currents. If a current limit level below the rated current is set, this will, inversely, result in heat generation within the IC. When the LIM pin is open, VG is shorted to Rf, and Rf = 0.47 Ω, this will result in a current limit level of about 1.3 to 1.4 A. If this limit falls under the rated value due to mode changes or changes in the value of the Rf resistor, set the current limit to an appropriate value by applying to the LIM pin a voltage that is divided from the V<sub>REF</sub> to ground potential by resistors of a few kΩ. Alternatively, short the LIM pin to V<sub>REF</sub> to defeat the current limit

### FG (FGR shorted to ground)

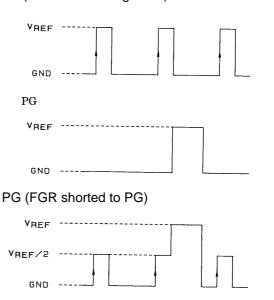

# **Block Diagram**

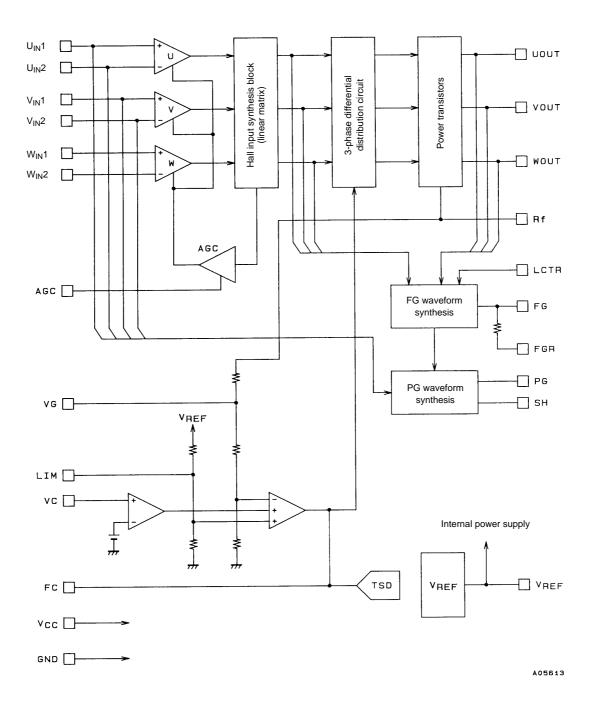

### **Sample Application Circuit**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of July, 1997. Specifications and information herein are subject to change without notice.