CMOS LSI

# LC78711E

**Graphics Display Processor**

### **Overview**

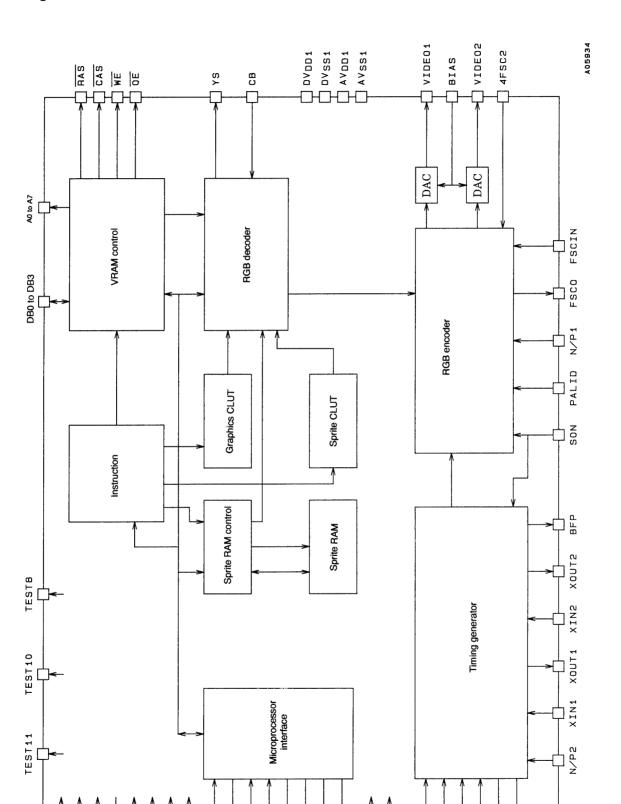

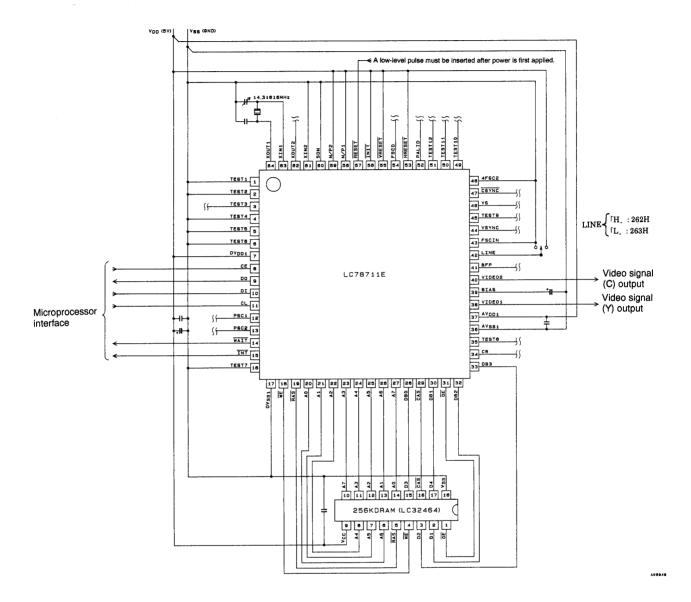

The LC78711E is a CMOS LSI that provides graphics display drawing functions. In addition to implementing graphics display for NTSC and PAL signals, it provides two  $32 \times 32$ -dot sprite display patterns and can easily implement a wide range of displays.

## **Features**

- Two-chip structure consisting of this LSI, the LC78711E, and an external 64-K  $\times$  4-bit RAM. (An RGB encoder is built in.)

- Graphics drawing controlled by a microprocessor over a serial interface.

- Includes two crystal oscillator systems, one for NTSC and one for PAL, and these system can be easily switched using the provided control pin.

The standard clocks and all necessary internal timings can be generated by connecting two crystals, a 14.31818-MHz crystal for NTSC, and a 17.734476-MHz crystal for PAL.

- Two  $32 \times 32$ -dot sprite patterns provided. Up to two sprites can be displayed, either two different types or the same pattern in two different locations.

- 16 colors from a palette of 4096 colors can be displayed in graphics screens, and seven colors can be displayed in sprite patterns.

- Y/C signal outputs (two 8-bit D/A converter outputs)

- Supports the superimpose function, and provides a timing signal output.

- Provides a color bar signal output function.

- Adopts an 8-bit serial data input format for the external control input.

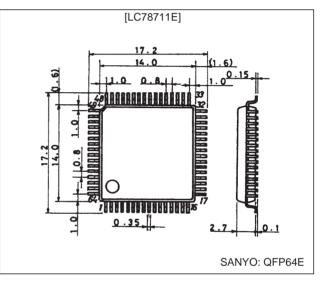

## **Package Dimensions**

unit: mm

#### 3159-QFP64E

#### VIDE01 VIDE02 FSCIN 4FSC2 CSYNC TEST9 VSYNC TESTB AVDD1 AVSS1 BIAS LINE ВFР 083 ŝ СB 48 47 46 45 44 43 36 35 34 33 42 41 40 39 38 37 TEST10 49 32 DB2 31 OE TEST11 50 TEST12 51 30 DB1 PALID 52 29 CAS HRESET 53 28 DBO FSCO 54 27 A7 VRESET 55 26 A6 INIT 56 25 A5 LC78711E RESET 57 24 A4 N/P1 58 23 A3 N/P2 59 22 A2 SON 60 21 A1 XIN2 61 20 Α0 XOUT2 62 19 RAS XIN1 63 18 WE XOUT1 64 17 DVSS1 1 2 6 8 9 11 13 Э 5 7 10 12 14 15 4 16 TESTG TEST2 TEST3 TEST4 TEST5 DVDD1 TEST1 PSC1 PSC2 WAIT FEST7 ы 00 Π СГ INT Top view A05926

### Specifications Absolute Maximum Ratings

**Pin Assignment**

| Parameter                   | Symbol               | Conditions                                                                                                                                                                        | Ratings                                        | Unit |

|-----------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max  | AV <sub>DD</sub> 1, DV <sub>DD</sub> 1                                                                                                                                            | $V_{SS}$ – 0.3 to $V_{SS}$ + 7.0               | V    |

| Maximum input voltage       | V <sub>IN</sub> max  | TEST1, TEST2, TEST4, TEST5, TEST6, CE, DI, CL,<br>TEST7, DB0 to DB3, CB, LINE, FSCIN, TEST9, 4FSC2,<br>TEST12, PALID, HRESET, VRESET, INIT, RESET, N/P1,<br>N/P2, SON, XIN1, XIN2 | V <sub>SS</sub> – 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Maximum output voltage      | V <sub>OUT</sub> max | TEST3, DO, PSC1, PSC2, WAIT, INT, WE, RAS, A0 to A7,<br>DB0 to DB3, CAS, OE, TEST8, BFP, VSYNC, YS, CSYNC,<br>TEST10, TEST11, FSC0, XOUT1, XOUT2                                  | V <sub>SS</sub> – 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max               | Ta = 25°C                                                                                                                                                                         | 500                                            | mW   |

| Operating temperature       | Topr                 |                                                                                                                                                                                   | -30 to +85                                     | °C   |

| Storage temperature         | Tstg                 |                                                                                                                                                                                   | -40 to +125                                    | °C   |

#### LC78711E

| Deveryor                 | Question            | Conditions                                                                                                              |                         | Ratings  |                         | l la it |

|--------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|-------------------------|---------|

| Parameter                | Symbol              | Conditions                                                                                                              | min                     | typ      | max                     | Unit    |

| Supply voltage           | V <sub>DD</sub>     | AV <sub>DD</sub> 1, DV <sub>DD</sub> 1                                                                                  | 4.5                     | 5.0      | 5.5                     | V       |

| Input high-level voltage | V <sub>IH</sub> 1   | TEST1, TEST2, TEST4, TEST5, TEST6, CE, DI, TEST7,<br>CB, LINE, TEST9, TEST12, PALID, HRESET, VRESET,<br>N/P1, N/P2, SON | 0.7 V <sub>DD</sub> 1   |          | V <sub>DD</sub> 1 + 0.3 | V       |

| input nigh-level voltage | V <sub>IH</sub> 2   | CL, INIT, RESET                                                                                                         | 0.8 V <sub>DD</sub> 1   |          | V <sub>DD</sub> 1 + 0.3 | V       |

|                          | V <sub>IH</sub> 3   | DB0 to DB3                                                                                                              | 2.2                     |          | V <sub>DD</sub> 1 + 0.3 | V       |

| Input low-level voltage  | V <sub>IL</sub> 1   | TEST1, TEST2, TEST4, TEST5, TEST6, CE, DI, TEST7,<br>CB, LINE, TEST9, TEST12, PALID, HRESET, VRESET,<br>N/P1, N/P2, SON | V <sub>SS</sub> 1 – 0.3 |          | 0.3 V <sub>DD</sub> 1   | V       |

|                          | V <sub>IL</sub> 2   | CL, INIT, RESET                                                                                                         | V <sub>SS</sub> 1 – 0.3 |          | 0.2 V <sub>DD</sub> 1   | V       |

|                          | V <sub>IL</sub> 3   | DB0 to DB3                                                                                                              | V <sub>SS</sub> 1 – 0.3 |          | 0.8                     | V       |

|                          | F <sub>SCIN</sub> 1 | XIN1                                                                                                                    |                         | 14.31818 |                         | MHz     |

|                          | F <sub>SCIN</sub> 2 | XIN2                                                                                                                    |                         | 17.73447 |                         | MHz     |

| Input frequency          | E 2                 | 4FSC2: NTSC mode                                                                                                        |                         | 14.31818 |                         | MHz     |

| Input frequency          | F <sub>SCIN</sub> 3 | 4FSC2: PAL mode                                                                                                         |                         | 17.73447 |                         | MHz     |

|                          |                     | FSCIN: NTSC mode                                                                                                        |                         | 3.57954  |                         | MHz     |

|                          | F <sub>SCIN</sub> 4 | FSCIN: PAL mode                                                                                                         |                         | 4.43361  |                         | MHz     |

| Input amplitude          | V <sub>IN</sub> 1   | FSCIN, 4FCS2                                                                                                            | 0.5                     |          | V <sub>DD</sub> 1       | Vp-p    |

|                          | V <sub>IN</sub> 2   | XIN1, XIN2                                                                                                              | 0.5                     |          | V <sub>DD</sub> 1       | Vp-p    |

## Allowable Operating Ranges at $Ta=-30 \ to \ +85^{\circ}C, \ V_{SS}=0 \ V$

## Electrical Characteristics at Ta = -30 to +85°C, $DV_{DD}1 = AV_{DD}1 = 5$ V unless otherwise specified.

| Parameter                                                                             | Symbol            | Conditions                                                                                                                                                                                                                                                         |                       |      | Unit              |      |

|---------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-------------------|------|

| Parameter                                                                             | Symbol            | Conditions                                                                                                                                                                                                                                                         | min                   | typ  | max               | Unit |

| Input high-level current                                                              | I <sub>IH</sub> 1 | I <sub>IH</sub> 1 TEST1, TEST2, TEST4, TEST5, TEST6, CE, DI, CL,<br>TEST7, DB0 to DB3, LINE, PALID, HRESET, VRESET,<br>INIT, RESET, N/P1, N/P2, SON: V <sub>IN</sub> = DV <sub>DD</sub> 1                                                                          |                       |      | 5                 | μΑ   |

|                                                                                       | I <sub>IH</sub> 2 | CB, TEST9, TEST12: V <sub>IN</sub> = DV <sub>DD</sub> 1                                                                                                                                                                                                            | 30                    | 100  | 200               | μA   |

| Input low-level current $I_{IL}1 = \frac{TEST7, DB0 \text{ to } DB3}{HRESET, VRESET}$ |                   | $\label{eq:test1} \begin{array}{l} \text{TEST1, TEST2, TEST4, TEST5, TEST6, CE, DI, CL,} \\ \hline \\ \underline{\text{TEST7, DB0 to DB3, CB, LINE, TEST9, TEST12,} \\ \hline \\ $ | -5                    |      |                   | μΑ   |

|                                                                                       | I <sub>IL</sub> 2 | PALID: V <sub>IN</sub> = DV <sub>SS</sub> 1                                                                                                                                                                                                                        | -200                  | -100 | -30               | μA   |

| Output high-level voltage                                                             | V <sub>OH</sub>   | TEST3, DO, PSC1, PSC2, WAIT, INT, BFP, WE, RAS,<br>A0 to A7, CAS, OE, DB0 to DB3, TEST8, VSYNC, YS,<br>CSYNC, TEST10, TEST11, FSCO: I <sub>OH</sub> = -0.5 mA                                                                                                      | V <sub>DD</sub> 1 – 1 |      | V <sub>DD</sub> 1 | V    |

| Output low-level voltage                                                              | V <sub>OL</sub>   | TEST3, DO, PSC1, PSC2, WAIT, INT, BFP, WE, RAS,<br>A0 to A7, CAS, OE, DB0 to DB3, TEST8, VSYNC, YS,<br>CSYNC, TEST10, TEST11, FSCO: I <sub>OL</sub> = 2.0 mA                                                                                                       | V <sub>SS</sub>       |      | 0.4               | V    |

| Output off leakage current                                                            | I <sub>OFF</sub>  | DB0 to DB3                                                                                                                                                                                                                                                         | -5                    |      | +5                | μA   |

| Internal feedback resistance                                                          | R <sub>X</sub>    | XIN1, XIN2, FSCIN, 4FSC2                                                                                                                                                                                                                                           |                       | 1    |                   | MΩ   |

| Clock duty                                                                            | fduty             | FSCIN, 4FSC2                                                                                                                                                                                                                                                       | 40                    |      | 60                | %    |

| 8-bit D/A converter reference voltage                                                 | V <sub>REF</sub>  | VIDEO1, VIDEO2                                                                                                                                                                                                                                                     | 2.30                  |      | 2.50              | V    |

| 8-bit D/A converter output resistance                                                 | R <sub>DA</sub>   | VIDEO1, VIDEO2                                                                                                                                                                                                                                                     |                       | 300  |                   | Ω    |

| Operating current drain                                                               | I <sub>DD</sub> 1 | AV <sub>DD</sub> 1                                                                                                                                                                                                                                                 |                       | 26   | 40                | mA   |

|                                                                                       | I <sub>DD</sub> 2 | DV <sub>DD</sub> 1                                                                                                                                                                                                                                                 |                       | 26   | 40                | mA   |

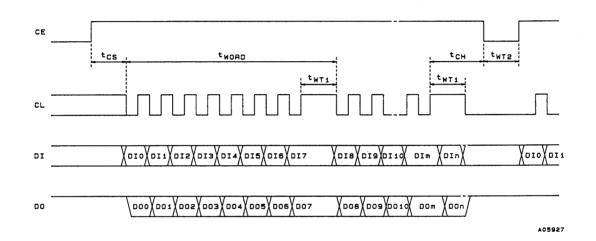

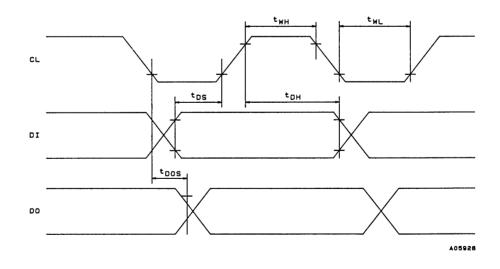

## Electrical Characteristics at Ta = $25^{\circ}$ C, V<sub>DD</sub> = 5.0 V, Fscp = 15.625 kHz

| Parameter                 | Symbol            | Conditions                   | Ratings |     |     |      |  |  |

|---------------------------|-------------------|------------------------------|---------|-----|-----|------|--|--|

| Parameter                 | Symbol            | Symbol                       |         | typ | max | Unit |  |  |

| Minimum input pulse width | t <sub>WH</sub>   | CL, high-level pulse width   | 75      |     |     | ns   |  |  |

| Minimum input pulse width | t <sub>WL</sub>   | CL, low-level pulse width    | 75      |     |     | ns   |  |  |

| Data setup time           | t <sub>DS</sub>   | DI, CL                       | 20      |     |     | ns   |  |  |

| Data hold time            | t <sub>DH</sub>   | DI, CL                       | 20      |     |     | ns   |  |  |

| CE setup time             | t <sub>CS</sub>   | CE, CL                       | 0       |     |     | ns   |  |  |

| CE hold time              | t <sub>CH</sub>   | CE, CL                       | 300     |     |     | ns   |  |  |

| DO setup time             | t <sub>DOS</sub>  | DO, CL                       |         | 30  |     | ns   |  |  |

| Data acquisition time     | t <sub>WT</sub> 1 | Serial data acquisition time | 150     |     |     | ns   |  |  |

| Data restart time         | t <sub>WT</sub> 2 | Serial data restart time     | 1.0     |     |     | μs   |  |  |

| Single word write time    | tword             | DI, CL (1 word = 8 bits)     | 1.35    |     |     | μs   |  |  |

## **Basic Specifications**

| Pin no. | Pin                | Pin type                         | I/O | Polarity | Pin function                                                                                            |

|---------|--------------------|----------------------------------|-----|----------|---------------------------------------------------------------------------------------------------------|

| 1       | TEST1              | Test input                       | 1   | Positive | Test input. Must be connected to ground during normal operation.                                        |

| 2       | TEST2              | Test input                       | 1   | Positive | Test input. Must be connected to ground during normal operation.                                        |

| 3       | TEST3              | Test output                      | 0   | Positive | Test output                                                                                             |

| 4       | TEST4              | Test input                       | I   | Positive | Test input. Must be connected to ground during normal operation.                                        |

| 5       | TEST5              | Test input                       | 1   | Positive | Test input. Must be connected to ground during normal operation.                                        |

| 6       | TEST6              | Test input                       | I   | Positive | Test input. Must be connected to ground during normal operation.                                        |

| 7       | DV <sub>DD</sub> 1 | Power supply (+5 V)              | _   | _        | Digital system power supply                                                                             |

| 8       | CE                 | Enable input                     | I   | Positive | Serial I/O data control input                                                                           |

| 9       | DO                 | Data output                      | 0   | Positive | Serial data output                                                                                      |

| 10      | DI                 | Data input                       | I   | Positive | Serial data input                                                                                       |

| 11      | CL                 | Clock input                      | I   | Positive | Serial data I/O clock input                                                                             |

| 12      | PSC1               | Monitor 1 output                 | 0   | Positive | Serial input monitor signal output                                                                      |

| 13      | PSC2               | Monitor 2 output                 | 0   | Positive | Command monitor signal output                                                                           |

| 14      | WAIT               | Wait signal output               | 0   | Negative | Serial input wait signal output (for use with bit maps)                                                 |

| 15      | INT                | Wait signal output               | 0   | Negative | Serial input wait signal output (for use with the sprite function)                                      |

| 16      | TEST7              | Test input                       | 1   | Positive | Test input. Must be connected to ground during normal operation.                                        |

| 17      | DV <sub>SS</sub> 1 | Ground                           | _   | _        | Digital system ground                                                                                   |

| 18      | WE                 | DRAM output                      | 0   | Negative | DRAM write enable signal output                                                                         |

| 19      | RAS                | DRAM output                      | 0   | Negative | DRAM row address strobe signal output                                                                   |

| 20      | A0                 | DRAM output                      | 1/0 | Positive | DRAM address (A0) output (Functions as an input in test mode.)                                          |

| 21      | A1                 | DRAM output                      | 1/0 | Positive | DRAM address (A1) output (Functions as an input in test mode.)                                          |

| 22      | A2                 | DRAM output                      | 1/0 | Positive | DRAM address (A2) output (Functions as an input in test mode.)                                          |

| 23      | A3                 | DRAM output                      | 1/0 | Positive | DRAM address (A3) output (Functions as an input in test mode.)                                          |

| 24      | A4                 | DRAM output                      | 1/0 | Positive | DRAM address (A4) output (Functions as an input in test mode.)                                          |

| 25      | A5                 | DRAM output                      | 1/0 | Positive | DRAM address (A5) output (Functions as an input in test mode.)                                          |

| 26      | A6                 | DRAM output                      | 1/0 | Positive | DRAM address (A6) output (Functions as an input in test mode.)                                          |

| 27      | A7                 | DRAM output                      | 1/0 | Positive | DRAM address (A7) output (Functions as an input in test mode.)                                          |

| 28      | DB0                | DRAM input and output            | 1/0 | Positive | DRAM data (D0) input and output                                                                         |

| 29      |                    | DRAM output                      | 0   | Negative | DRAM column address strobe signal output                                                                |

| 30      | DB1                | DRAM input and output            | 1/0 | Positive | DRAM data (D1) input and output                                                                         |

| 31      |                    | DRAM output                      | 0   | Negative | DRAM read enable signal output                                                                          |

| 32      | DB2                | DRAM input and output            | 1/0 | Positive | DRAM data (D2) input and output                                                                         |

| 33      | DB2<br>DB3         | DRAM input and output            | 1/0 | Positive | DRAM data (D2) input and output                                                                         |

| - 33    | 003                |                                  | 1/0 | FUSITIVE | Low: normal mode, high: color bar output                                                                |

| 34      | CB                 | Color bar selection              | I   | Positive | (A pull-down resistor is built in.)                                                                     |

| 35      | TEST8              | Test output                      | 0   | Positive | Test output                                                                                             |

| 36      | AV <sub>SS</sub> 1 | Ground                           | _   | _        | Analog system ground                                                                                    |

| 37      | AV <sub>DD</sub> 1 | Power supply (+5 V)              | _   | _        | Analog system power supply                                                                              |

| 38      | VIDEO1             | Video signal (Y) output          | 0   | _        | Video (luminance) signal (analog) output (D/A converter output)                                         |

| 39      | BIAS               | Capacitor connection             | 0   | _        | Connections for a ripple exclusion capacitor                                                            |

| 40      | VIDEO2             | Video signal (C) output          | 0   | _        | Video (chrominance) signal (analog) output (D/A converter output)                                       |

| 41      | BFP                | Burst flag signal output         | 0   | Positive | Burst signal output timing flag output                                                                  |

| 42      | LINE               | Line count selection             | I   | _        | Line count selection<br>NTSC mode - Low: 263H, high: 262H<br>PAL mode - Low: 314H, high: 312H           |

| 43      | FSCIN              | Clock input                      | 1   | Positive | Superimpose subcarrier clock input (A feedback resistor is built in                                     |

| 44      | VSYNC              | Vertical synchronization output  | 0   | Negative | Vertical synchronizing signal output                                                                    |

| 45      | TEST9              | Test input                       | 1   | Positive | Test input. Must be connected to ground during normal operation.<br>(A pull-down resistor is built in.) |

| 46      | YS                 | Superimpose output               | 0   | Negative | Superimpose control output                                                                              |

| 47      | CSYNC              | Composite synchronization output | 0   | Negative | Composite synchronizing signal output                                                                   |

| 48      | 4FSC2              | Clock input                      | I   | Positive | External clock input for the superimpose function<br>(A feedback resistor is built in.)                 |

| 49      | TEST10             | Test output                      | 0   | Positive | Test output                                                                                             |

| 50      | TEST11             | Test output                      | 0   | Positive | Test output                                                                                             |

Continued on next page.

Continued from preceding page.

| Pin no. | Pin    | Pin type                                  | I/O | Polarity | Pin function                                                                               |

|---------|--------|-------------------------------------------|-----|----------|--------------------------------------------------------------------------------------------|

| 51      | TEST12 | Test input                                | I   | Positive | Test input. Must be connected to ground during normal operation.                           |

| 52      | PALID  | PAL mode external control input           | I   | Positive | External superimpose function control input for PAL mode (A pull-up resistor is built in.) |

| 53      | HRESET | External horizontal synchronization input | I   | Negative | External horizontal synchronization timing control input                                   |

| 54      | FSCO   | Clock output                              | 0   | Positive | Subcarrier clock output<br>NTSC mode: 3.579545 MHz<br>PAL mode: 4.433619 MHz               |

| 55      | VRESET | External vertical synchronization input   | I   | Negative | External vertical synchronization timing control input                                     |

| 56      | INIT   | Initialization input                      | I   | Negative | System initialization signal input                                                         |

| 57      | RESET  | Reset input                               | I   | Negative | System reset signal input                                                                  |

| 58      | N/P1   | NTSC/PAL selection                        | I   | Positive | NTSC/PAL selection input (RGB encoder block)<br>High: NTSC, low: PAL                       |

| 59      | N/P2   | NTSC/PAL selection                        | I   | Positive | NTSC/PAL selection input (decoder block)<br>High: NTSC, low: PAL                           |

| 60      | SON    | Superimpose control                       | I   | Positive | Superimpose function on/off control input<br>High: superimpose on                          |

| 61      | XIN2   | Crystal oscillator element                | I   | —        | Connections for the PAL crystal oscillator element                                         |

| 62      | XOUT2  | connections                               | 0   | —        | (4·fsc = 17.734476 MHz)                                                                    |

| 63      | XIN1   | Crystal oscillator element                | Ι   | —        | Connections for the NTSC crystal oscillator element                                        |

| 64      | XOUT1  | connections                               | 0   | _        | (4·fsc = 14.31818 MHz)                                                                     |

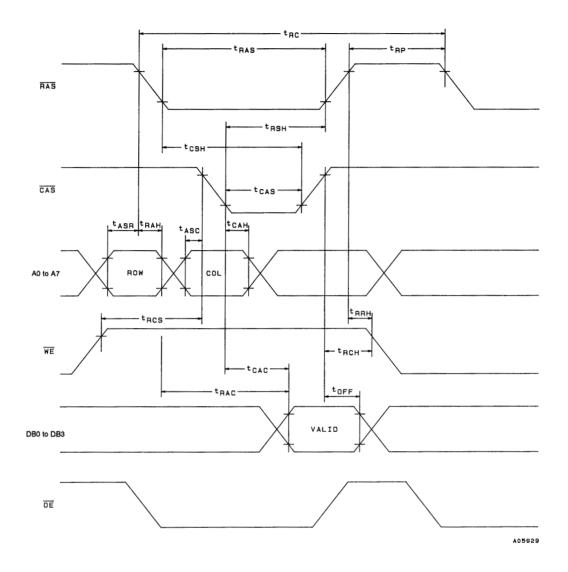

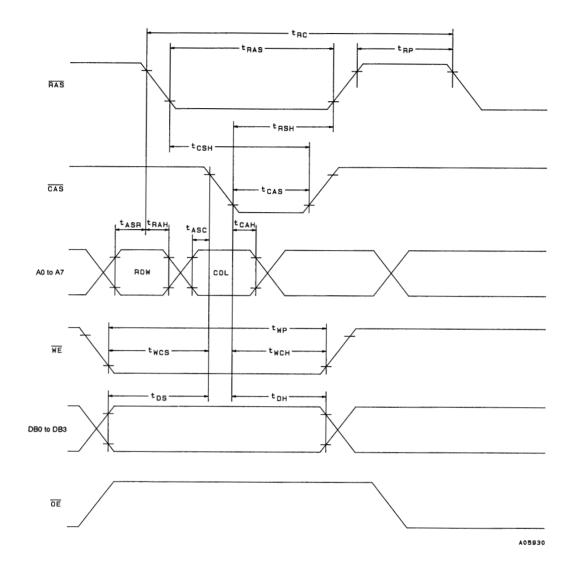

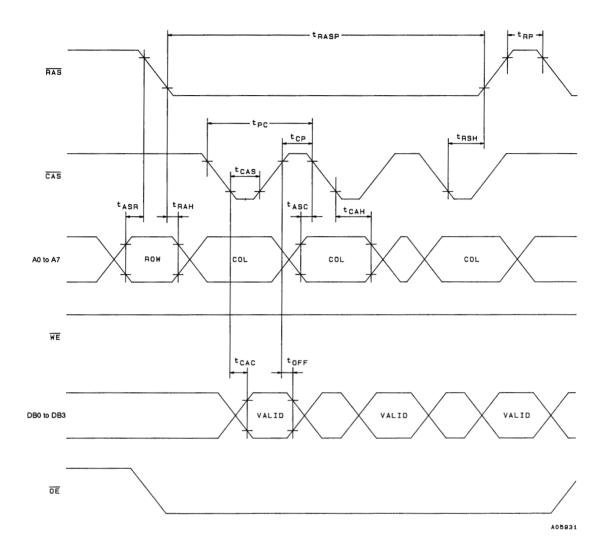

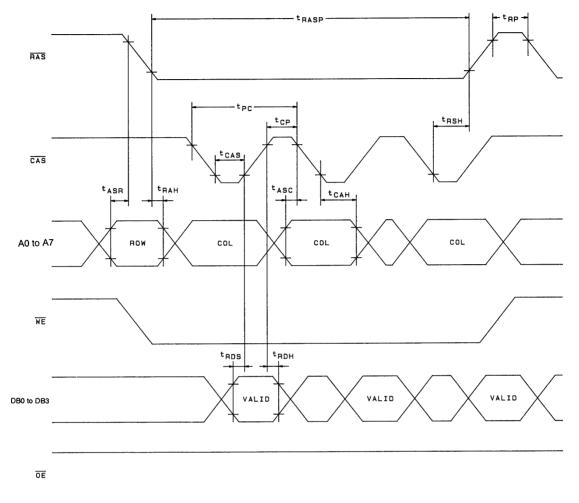

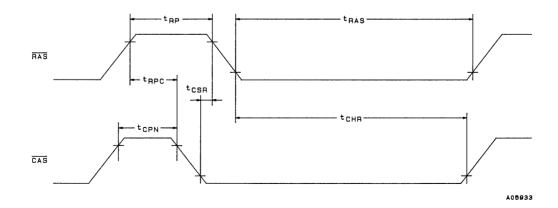

## Timing Characteristics (DRAM access timing) at Ta = +25 $^{\circ}C,\,DV_{DD}1$ = 5 V

| Deremeter                     | Symbol            | Conditions        |     | Ratings |       |      |  |

|-------------------------------|-------------------|-------------------|-----|---------|-------|------|--|

| Parameter                     | Symbol            | Conditions        | min | typ     | max   | Unit |  |

| Random read/write cycle       | t <sub>RC</sub>   |                   | 250 |         |       | ns   |  |

| Page mode cycle               | t <sub>PC</sub>   |                   | 130 |         |       | ns   |  |

| RAS access time               | t <sub>RAC</sub>  |                   |     |         | 210   | ns   |  |

| CAS access time               | t <sub>CAC</sub>  |                   |     |         | 10    | ns   |  |

| Output turn off delay         | t <sub>OFF</sub>  |                   |     |         | 20    | ns   |  |

| RAS precharge time            | t <sub>RP</sub>   |                   | 100 |         |       | ns   |  |

| RAS pulse width               | t <sub>RAS</sub>  |                   | 120 |         |       | ns   |  |

| RAS pulse width (page mode)   | t <sub>RASP</sub> |                   |     |         | 18000 | ns   |  |

| RAS hold time                 | t <sub>RSH</sub>  |                   | 60  |         |       | ns   |  |

| CAS hold time                 | t <sub>CSH</sub>  |                   | 120 |         |       | ns   |  |

| CAS pulse width               | t <sub>CAS</sub>  |                   | 60  |         |       | ns   |  |

| CAS precharge time            | t <sub>CPN</sub>  |                   | 50  |         |       | ns   |  |

| CAS precharge time            | t <sub>CP</sub>   | Page mode         | 50  |         |       | ns   |  |

| Row address setup time        | t <sub>ASR</sub>  |                   | 100 |         |       | ns   |  |

| Row address hold time         | t <sub>RAH</sub>  |                   | 50  |         |       | ns   |  |

| Column address setup time     | t <sub>ASC</sub>  |                   | 0   |         |       | ns   |  |

| Column address hold time      | t <sub>CAH</sub>  |                   | 50  |         |       | ns   |  |

| Read command setup time       | t <sub>RCS</sub>  |                   | 150 |         |       | ns   |  |

| Read command hold time        | t <sub>RCH</sub>  | Referenced to CAS | 120 |         |       | ns   |  |

| Read command hold time        | t <sub>RRH</sub>  | Referenced to RAS | 120 |         |       | ns   |  |

| Write command setup time      | twcs              |                   | 100 |         |       | ns   |  |

| Write command hold time       | t <sub>WCH</sub>  |                   | 50  |         |       | ns   |  |

| Write command pulse width     | t <sub>WP</sub>   |                   | 150 |         |       | ns   |  |

| Write data setup time         | t <sub>DS</sub>   |                   | 100 |         |       | ns   |  |

| Write data setup time         | t <sub>DH</sub>   |                   | 100 |         |       | ns   |  |

| CAS setup time                | t <sub>CSR</sub>  | CAS before RAS    | 50  |         |       | ns   |  |

| CAS hold time                 | t <sub>CHR</sub>  | CAS before RAS    | 50  |         |       | ns   |  |

| RAS precharge CAS active time | t <sub>RPC</sub>  |                   | 50  |         |       | ns   |  |

| Refresh time                  | t <sub>REF</sub>  |                   |     |         | 3.5   | ms   |  |

## 1. DRAM read cycle

## 2. DRAM Early write cycle

## 3. DRAM page mode read cycle

#### 4. DRAM page mode write cycle

A05932

## 5. DRAM $\overline{CAS}$ before $\overline{RAS}$ refresh cycle

WAIT WAIT

TEST9 [

TEST7

TEST3 [

TEST4 [ TEST5 [ TEST6 [

TEST1 [ TEST2 [ PSC2

RESET |

LINE

TEST12 [ CSYNC [

VRESET [

HRESET

VSYNC [

#### **Function Overview**

1. Crystal clock oscillator; XIN1, XOUT1, XIN2, XOUT2, N/P1, N/P2, FSCO

The XIN1 and XOUT1 pins are connections for an NTSC 14.31818-MHz crystal element, and the XIN2 and XOUT2 pins are connections for a PAL 17.734476-MHz crystal element. The N/P1 pin switches the LC78711E RGB encoder block between NTSC and PAL modes, and the N/P2 pin switches the decoder block between NTSC and PAL modes. The FSCO pin outputs a clock signal that is the crystal oscillator frequency divided by 4. The table below enumerates the pin states vs. the LC78711E operating modes.

| XIN1, XOUT1  | XIN2, XOUT2   | N/P1 | N/P2 | TV format | FSCO         |

|--------------|---------------|------|------|-----------|--------------|

| 14.31818 MHz | *             | Н    | Н    | NTSC/M    | 3.579545 MHz |

| *            | 17.734476 MHz | L    | L    | PAL/GBIDH | 4.433619 MHz |

| 14.30244 MHz | *             | L    | Н    | PAL/M     | 3.575611 MHz |

- 2. Display format; N/P1, N/P2, LINE, CSYNC, SON, 4FSC2, FSCIN, VRESET, HRESET, YS, PALID

- The LC78711E supports both NTSC and PAL modes, with the N/P1 and N/P2 pins being used to set the mode. See item (1) above for the pin states in the NTSC and PAL modes. The LINE pin switches the number of scan lines in a 1-V period.

- The SON, 4FSC2, FSCIN, VRESET, HRESET, YS, and PALID pins are used with the superimpose function. The 4FSC2 pin inputs a 4 × fsc frequency, and the FSCIN pin inputs the fsc frequency. The VRESET and HRESET pins input the external video signal VSYNC and HSYNC. The internal V and H counters are reset on the falling edges of these signals, respectively. The image may be disrupted if the 4FSC2 signal is not locked with the VRESET and HRESET signals. The YS pin is used to switch the video signal. The PALID pin is used for burst waveform phase matching in PAL mode.

- 3. DRAM interface Interface pins: A0 to A7, DB0 to DB3, RAS, CAS, WE, OE An external 64k × 4-bit DRAM must be used.

- Video outputs: VIDEO1, VIDEO2 The luminance signal can be acquired from the VIDEO1 pin. The chrominance signal can be acquired from the VIDEO2 pin.

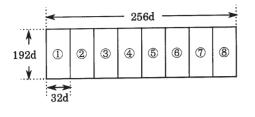

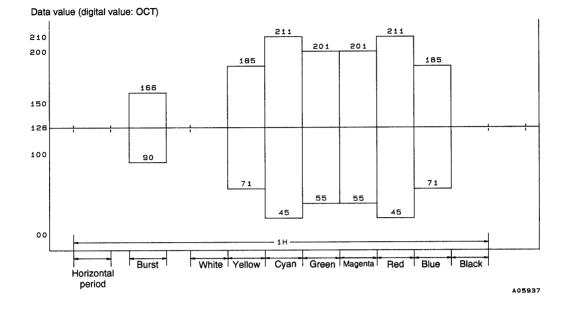

#### 5. Color bar output; CB

If the CB input pin is set high, a color bar signal will be output from the VIDEO1 and VIDEO2 pins. The table below lists the content of the color bar signal.

|                | R | G | В |

|----------------|---|---|---|

| ① White        | F | F | F |

| ② Gray         | В | В | В |

| ③ Yellow       | F | F | 0 |

| @ Cyan         | 0 | F | F |

| © Green        | 0 | F | 0 |

| 6 Magenta      | F | 0 | F |

| ⑦ Red          | F | 0 | 0 |

| ® Blue         | 0 | 0 | F |

| Border (black) | 0 | 0 | 0 |

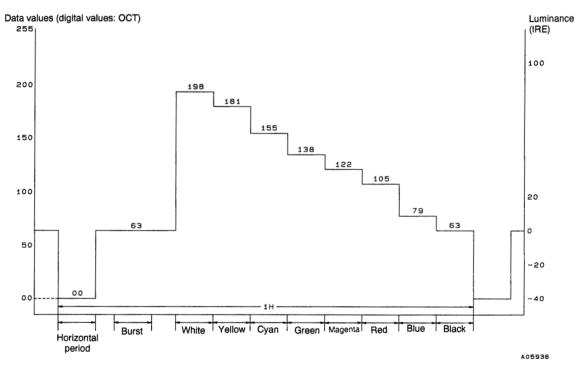

#### 6. Color bar signal output level

• Luminance signal output level (Y signal: VIDEO1, pin 38)

| Data value | Output voltage (V) | Luminance level (IRE) |

|------------|--------------------|-----------------------|

| 255        | 4.990              | 121.9                 |

| 220        | 4.648              | 100                   |

| 198        | 4.434              | 85.7                  |

| 181        | 4.268              | 74.9                  |

| 155        | 4.014              | 58.4                  |

| 138        | 3.848              | 47.6                  |

| 122        | 3.691              | 37.5                  |

| 105        | 3.525              | 26.7                  |

| 79         | 3.271              | 10.2                  |

| 63         | 3.125              | 0                     |

| 0          | 2.500              | -40                   |

Note:  $AV_{DD}1 = 5.00 V$

• Chrominance signal output level (C signal: VIDEO2, pin 40)

|            | 1                  |                       |

|------------|--------------------|-----------------------|

| Data value | Output voltage (V) | Luminance level (IRE) |

| 255        | 4.990              | 81.2                  |

| 211        | 4.560              | 52.7                  |

| 201        | 4.463              | 46.3                  |

| 185        | 4.306              | 36.2                  |

| 166        | 4.121              | 24.1                  |

| 128        | 3.750              | 0                     |

| 90         | 3.379              | -24.1                 |

| 71         | 3.193              | -36.2                 |

| 55         | 3.037              | -46.3                 |

| 45         | 2.939              | -52.7                 |

| 0          | 2.500              | -81.2                 |

Note:  $AV_{DD}1 = 5.00 V$

#### **Drawing Display Functions**

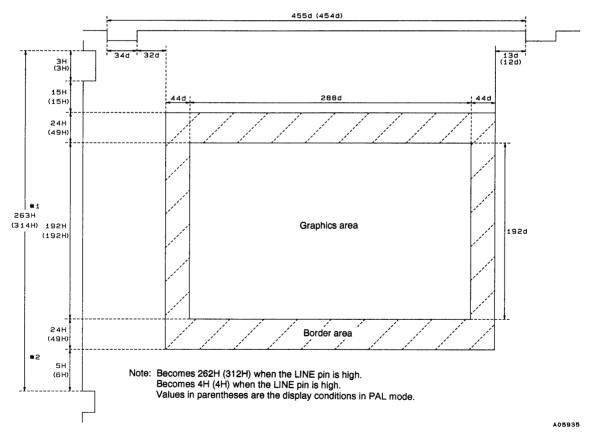

- 1. Operating mode (scan operation, display operation)

- NTSC mode:

- Non-interlaced 60 Hz (262 or 263 lines)

- Dot clock 2fsc: 7.15909 MHz (T = 139.67 ns)

- System clock 4fsc: 14.31818 MHz

- PAL mode:

- Non-interlaced 50 Hz (312 or 314 lines)

- Dot clock  $4fsc \times 2/5: 7.09379 \text{ MHz} (T = 140.97 \text{ ns})$

- System clock 4fsc: 17.734476 MHz

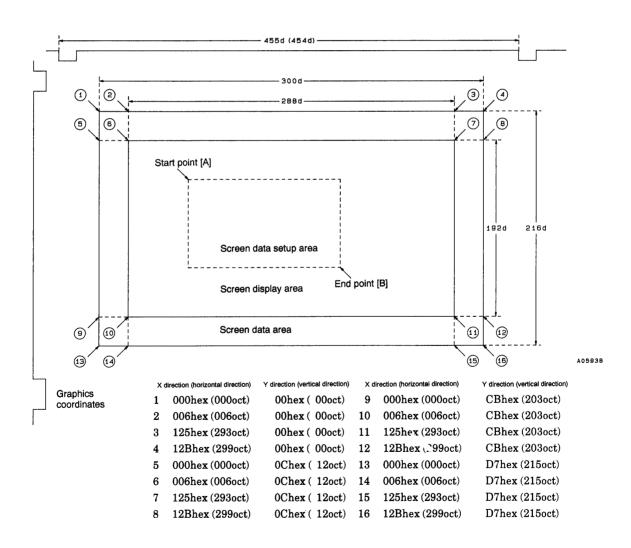

- 2. Display functions

- Display resolution  $288 \text{ dots} \times 192 \text{ H}$

- Screen data area  $300 \text{ dots} \times 216 \text{ H}$

- 16-color display 16 colors selected from a palette of 4096 colors

- 3. Sprite screen (cursor display)

- Sprite screen: Two types,  $32 \text{ dots} \times 32 \text{ H}$

- Sprite color: Seven display colors plus transparent display (7 colors selected from 4096 colors) This color setting selects colors that are independent of the bit-mapped screens.

- 4. Cross cursor display

- The X and Y coordinates are set.

A cross cursor is displayed at the point corresponding to the specified coordinates.

5. Display window area function

• A rectangular window is specified by specifying the X and Y coordinates for two points. Either the area within the display window, or the area outside the display window can be specified to be transparent (border color display).

- 6. Scrolling display function

- Scrolling in the vertical and horizontal directions

- The scroll amount can be set.

The scroll amount is set in units of 1 to 6 dots in the horizontal direction and 1 to 12 dots in the vertical direction. Text with 50 characters in the horizontal direction and 18 characters in the vertical direction can be set up in single character units.

7. Graphics display format

#### Writing graphics data

[A] Set up point (Xs, Ys): X is a 9-bit address.

- [B] Set up point (Xe, Ye): Y is an 8-bit address.

- 1. Begin writing color codes from the origin coordinate address (Xs, Ys).

- 2. If the X direction address (Xs) matches the endpoint address (Xe), reset the X address to the origin address (Xs). At the same time, increment the Y address by one count.

- 3. Terminate writing when the endpoint address (Xe, Ye) is reached.

- At termination, reset the address to the origin address (Xs, Ys) and exit.

- Terminate writing even if the CE pin has gone low. In this case, the address will be set to the endpoint address plus one and the algorithm will exit.

- The address manipulations described above, are for the case where automatic address incrementing has been set up by command.

- 1. When writing to the graphics display area, specify the address of the origin [A] to be 6 and the address of the endpoint [B] to be 11.

- When writing to a rectangular area, the origin [A] and the endpoint [B] can be set to arbitrary values. When filling is specified by command, RAM data will be set to the first specified color code. In this case, it suffices to write the color code that was specified at that point. However, add the condition that the color code setting must not be changed during the fill operation.

- 3. When writing a straight line, set either the X (horizontal) values or Y (vertical) values of the origin [A] and endpoint [B] to the same value.

For example, to draw a straight line in the vertical direction, set the origin [A] to (Xs, Ys) and set the endpoint [B] to (Xs, Ye).

To draw a straight line in the horizontal direction, set the origin [A] to (Xs, Ys) and set the endpoint [B] to (Xe, Ys). Filling must be specified by command to write straight lines.

- 4. Set up the addresses as follows to write scroll data.

- For example,

To scroll down, specify 2 as the origin [A] and 7 as the endpoint [B].

To scroll right, specify 5 as the origin [A] and 9 as the endpoint [B].

To scroll left, specify 7 as the origin [A] and 12 as the endpoint [B].

To scroll up, specify 10 as the origin [A] and 15 as the endpoint [B].

#### Reading out color codes for specific bits

It is possible to read out (not write) the color code for a given dot by using a command to set the origin address (Xs, Ys). Executing the read out command latches the data into the serial output shift register. The command manipulation terminates when the data for a single dot has been read out. (The command register is reset.)

#### Graphics display priority order

- 1. Cross cursor

- 2. Sprite A pattern

- 3. Sprite B pattern

- 4. Graphics screen

- 5. Border screen

- 6. Background screen (not displayed during graphics display)

- Note: There are cases where the same pattern is displayed for sprite patterns A and B. Thus the LC78711E may be in a state of accessing the same sprite RAM. Therefore, a time difference must be set up for the sprite pattern accesses (reads) for the A and B patterns.

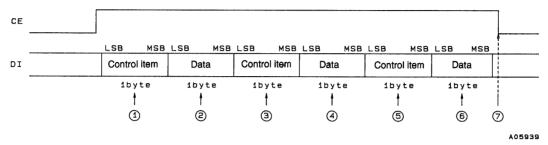

#### **Microprocessor Interface**

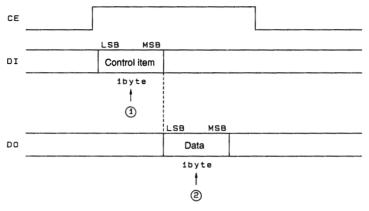

- 1. Data transfer format (for command transfers)

- A command identification code (control item) must be transferred before the data is transferred when setting up commands, positions (coordinates), or color codes (color table).

- If continuous data transfer mode is not set up, then data transfers of bit map data and sprite (cursor) data also require that a command identifier code (control item) be transferred before the data is transferred.

- Transfer format (example)

$\textcircled{1, 3, 5:} \quad \textbf{Command identification code (control item)}$

- 2, 4, 6: Command register setup data

- Image: Serial transfer completes

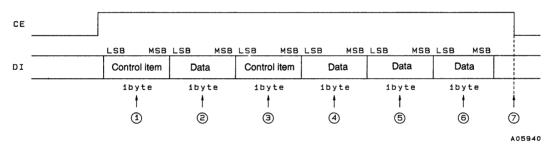

- 2. Transfer format (when continuous data transfer mode has been set up)

- Continuous data transfer mode must be set up by the data (1 byte) that follows a command identification code (control item). When a RAM data transfer command is set up and the data transfer started, the data that follows (in byte units) is all acquired as RAM data.

- Note: If continuous data transfer mode is set up, the RAM write address must be set (by command) to automatic increment mode.

- Transfer format (example)

③: Command identification code (control item)

2: Command register setup data

④, ⑤, ⑥: RAM data

⑦: Serial tran

Serial transfer completes and continuous data transfer mode is cleared.

Note: When continuous data transfer mode is cleared, the command register setting is not reset. If the control microprocessor immediately issues a RAM data transfer command and starts the data transfer, the LC78711E will switch to continuous data transfer mode once again.

- 3. Transfer format (when a check command is issued)

- Transfer format (example)

A05941

①: Control item (address = first byte: 11hex)②: Data (check flags)

#### **Control Commands**

|                                                             |    |   |     | First  | byte | e    |   |     |           |           |      | Secon | id byte   |           |           |             |

|-------------------------------------------------------------|----|---|-----|--------|------|------|---|-----|-----------|-----------|------|-------|-----------|-----------|-----------|-------------|

| Command                                                     | MS | В | Con | trol i | tem  | code |   | LSB | MSB       |           |      | Da    | ata       |           |           | LSB         |

|                                                             | 7  | 6 | 5   | 4      | 3    | 2    | 1 | 0   | 7         | 6         | 5    | 4     | 3         | 2         | 1         | 0           |

| Register 00hex<br>(Mode setup)                              | 0  | 0 | 0   | 0      | 0    | 0    | 0 | 0   | INIT      | SCP2      | SCP1 | SCP0  | СВ        | 1         | 0         | VRAM/<br>BG |

| Register 01hex<br>(Screen position fine adjustment)         | 0  | 0 | 0   | 0      | 0    | 0    | 0 | 1   | VP3       | VP2       | VP1  | VP0   | HP3       | HP2       | HP1       | HP0         |

| Register 04hex<br>(Color: RG settings)                      | 0  | 0 | 0   | 0      | 0    | 1    | 0 | 0   | CRG3      | CRG2      | CRG1 | CRG0  | CRR3      | CRR2      | CRR1      | CRR0        |

| Register 05hex<br>(Color: B settings)                       | 0  | 0 | 0   | 0      | 0    | 1    | 0 | 1   | CROS      | CRKY      | BGCL | 0     | CRB3      | CRB2      | CRB1      | CRB0        |

| Register 06hex<br>(Burst phase setting; when SON = 1)       | 0  | 0 | 0   | 0      | 0    | 1    | 1 | 0   | R/F       | 0         | 0    | 0     | 0         | BST<br>ON | PH1       | PH0         |

| Register 07hex<br>(YS output phase adjustment)              | 0  | 0 | 0   | 0      | 0    | 1    | 1 | 1   | 0         | 0         | 0    | 0     | YT3       | YT2       | YT1       | YT0         |

| Register 08hex<br>(External synchronization on/off)         | 0  | 0 | 0   | 0      | 1    | 0    | 0 | 0   | MVMD      | EXSN      | 0    | 0     | TST3      | TST2      | TST1      | TST0        |

| Register 09hex<br>(Subtitle scrolling: up/down)             | 0  | 0 | 0   | 0      | 1    | 0    | 0 | 1   | 0         | 0         | 0    | SCV4  | SCV3      | SCV2      | SCV1      | SCV0        |

| Register 0Ahex<br>(Subtitle scrolling: left/right)          | 0  | 0 | 0   | 0      | 1    | 0    | 1 | 0   | 0         | 0         | SCH5 | SCH4  | SCH3      | SCH2      | SCH1      | SCH0        |

| Register 8Bhex<br>(Scrolling control: vertical direction)   | 1  | 0 | 0   | 0      | 1    | 0    | 1 | 1   | SCRV<br>1 | SCRV<br>0 | 0    | 0     | SRFV<br>3 | SRFV      | SRFV<br>1 | SRFV        |

| Register 8Chex<br>(Scrolling control: horizontal direction) | 1  | 0 | 0   | 0      | 1    | 1    | 0 | 0   | SCRH<br>1 | SCRH<br>0 | 0    | 0     | 0         | SRFH      | SRFH<br>1 | SRFH<br>0   |

| Register 0Dhex<br>(Graphics mode setup)                     | 0  | 0 | 0   | 0      | 1    | 1    | 0 | 1   | 0         | 0         | 0    | 0     | 0         | DCRS      | DSPB      | DSPA        |

| Register 0Ehex<br>(Pin PSC1 output control)                 | 0  | 0 | 0   | 0      | 1    | 1    | 1 | 0   | 0         | 0         | 0    | 0     | 0         | 0         | 0         | SRO<br>ENM  |

| Register 0Fhex<br>(Pin PSC2 output control)                 | 0  | 0 | 0   | 0      | 1    | 1    | 1 | 1   | 0         | 0         | 0    | 0     | CRSM      | SPBM      | SPAM      | GPHM        |

| Register 11hex                                              | 0  | 0 | 0   | 1      | 0    | 0    | 0 | 1   | 0         | 0         | 0    | 0     | 0         | VBLK      | EXEC      | 1           |

Continued on next page.

#### Continued from preceding page.

|                                                              |    |   |     | First  | byte | )    |   |     |            |            |            | Secor         | nd byte      |               |            |                |

|--------------------------------------------------------------|----|---|-----|--------|------|------|---|-----|------------|------------|------------|---------------|--------------|---------------|------------|----------------|

| Command                                                      | MS | В | Con | trol i | tem  | code |   | LSB | MSB        |            |            | Da            | ata          |               |            | LSB            |

|                                                              | 7  | 6 | 5   | 4      | 3    | 2    | 1 | 0   | 7          | 6          | 5          | 4             | 3            | 2             | 1          | 0              |

| Register 20hex<br>(Color data settings: R, G)                | 0  | 0 | 1   | 0      | 0    | 0    | 0 | 0   | SGCG<br>3  | SGCG<br>2  | SGCG<br>1  | SGCG<br>0     | SGCR<br>3    | SGCR<br>2     | SGCR<br>1  | SGCR           |

| Register 21hex<br>(Color data settings: B)                   | 0  | 0 | 1   | 0      | 0    | 0    | 0 | 1   | 0          | 0          | 0          | 0             | SGCB<br>3    | SGCB<br>2     | SGCB<br>1  | SGCB<br>0      |

| Register A2hex<br>(Color data settings)                      | 1  | 0 | 1   | 0      | 0    | 0    | 1 | 0   | 0          | 0          | 0          | 0             | SCPC<br>3    | SCPC<br>2     | SCPC       | SCPC           |

| Register A3hex<br>(Border color setting)                     | 1  | 0 | 1   | 0      | 0    | 0    | 1 | 1   | 0          | 0          | 0          | 0             | SBDC<br>3    | SBDC          | SBDC       | SBDC           |

| Register 24hex<br>(Bit map address setting)                  | 0  | 0 | 1   | 0      | 0    | 1    | 0 | 0   | BMAY<br>7  | BMAY<br>6  | BMAY<br>5  | BMAY          | BMAY<br>3    | BMAY<br>2     | BMAY       | BMAY           |

| Register 25hex<br>(Bit map address setting)                  | 0  | 0 | 1   | 0      | 0    | 1    | 0 | 1   | BMAX<br>7  | BMAX<br>6  | BMAX<br>5  | BMAX<br>4     | BMAX<br>3    | BMAX<br>2     | BMAX       | BMAX<br>0      |

| Register 26hex<br>(Write control setting)                    | 0  | 0 | 1   | 0      | 0    | 1    | 1 | 0   | 0          | R/W        | 0          | STRP/<br>ENDP | FILL<br>COLR | BMAI          | BMDF       | BMAX<br>8      |

| Register A7hex<br>(Bit map data setting)                     | 1  | 0 | 1   | 0      | 0    | 1    | 1 | 1   | BMD7       | BMD6       | BMD5       | BMD4          | BMD3         | BMD2          | BMD1       | BMD0           |

| Register 28hex<br>(Color data settings: R, G)                | 0  | 0 | 1   | 0      | 1    | 0    | 0 | 0   | SSPG<br>3  | SSPG<br>2  | SSPG       | SSPG          | SSPR<br>3    | SSPR          | SSPR       | SSPR           |

| Register 29hex<br>(Color data settings: B)                   | 0  | 0 | 1   | 0      | 1    | 0    | 0 | 1   | 0          | 0          | 0          | 0             | SSPB<br>3    | SSPB          | SSPB       | ¦SSPB<br>¦0    |

| Register AAhex<br>(Sprite settings)                          | 1  | 0 | 1   | 0      | 1    | 0    | 1 | 0   | 0          | 0          | 0          | 0             | 0            | SSPC<br>2     | SSPC<br>1  | SSPC<br>0      |

| Register 2Bhex<br>(Sprite address Y setting)                 | 0  | 0 | 1   | 0      | 1    | 0    | 1 | 1   | 0          | 0          | 0          | SPAR<br>Y4    | SPAR<br>Y3   | SPAR<br>Y2    | SPAR<br>Y1 | SPAR<br>Y0     |

| Register 2Chex<br>(Sprite address X setting)                 | 0  | 0 | 1   | 0      | 1    | 1    | 0 | 0   | 0          | 0          | 0          | SPAR<br>X4    | SPAR<br>X3   | SPAR<br>X2    | SPAR<br>X1 | SPAR<br>X0     |

| Register 2Dhex<br>(Write control settings)                   | 0  | 0 | 1   | 0      | 1    | 1    | 0 | 1   | 0          | 0          | 0          | 0             | WSP2         | WSP1          | SPAI       | SPDF           |

| Register AEhex<br>(Sprite data setting)                      | 1  | 0 | 1   | 0      | 1    | 1    | 1 | 0   | 0          | SPD6       | SPD5       | SPD4          | 0            | SPD2          | SPD1       | SPD0           |

| Register 2Fhex<br>(Sprite A and B settings)                  | 0  | 0 | 1   | 0      | 1    | 1    | 1 | 1   | 0          | 0          | 0          | 0             | 0            | SPRT<br>ARA   | SPSB       | SPSA           |

| Register 30hex<br>(Sprite display address Y setting)         | 0  | 0 | 1   | 1      | 0    | 0    | 0 | 0   | SPDA<br>Y7 | SPDA<br>Y6 | SPDA<br>Y5 | SPDA<br>Y4    | SPDA<br>Y3   | SPDA<br>Y2    | SPDA<br>Y1 | SPDA<br>Y0     |

| Register 31hex<br>(Sprite display address X setting)         | 0  | 0 | 1   | 1      | 0    | 0    | 0 | 1   | SPDA<br>X7 | SPDA<br>X6 | SPDA<br>X5 | SPDA<br>X4    | SPDA<br>X3   | SPDA<br>X2    | SPDA<br>X1 | SPDA<br>X0     |

| Register 32hex<br>(Sprite display address setting control)   | 0  | 0 | 1   | 1      | 0    | 0    | 1 | 0   | 0          | 0          | 0          | 0             | WSPB         | WSPA          | 0          | ¦ SPDA<br>¦ X8 |

| Register 33hex<br>(Display window setting: Y)                | 0  | 0 | 1   | 1      | 0    | 0    | 1 | 1   | WDYS<br>7  | WDYS<br>6  | WDYS<br>5  | WDYS          | WDYS<br>3    | WDYS<br>2     | WDYS       | WDYS           |

| Register 34hex<br>(Display window setting: X)                | 0  | 0 | 1   | 1      | 0    | 1    | 0 | 0   | WDXS<br>7  | WDXS<br>6  | WDXS<br>5  | WDXS<br>4     | WDXS<br>3    | WDXS<br>2     | WDXS<br>1  | WDXS<br>0      |

| Register 35hex<br>(Display window: X; display area settings) | 0  | 0 | 1   | 1      | 0    | 1    | 0 | 1   | 0          | 0          | WDEN       | WDAR          | PAL<br>60    | SADR/<br>EADR | 0          | WDXS<br>8      |

| Register 36hex<br>(Cross cursor display position setting: X) | 0  | 0 | 1   | 1      | 0    | 1    | 1 | 0   | CRAX<br>7  | CRAX<br>6  | CRAX<br>5  | CRAX<br>4     | CRAX<br>3    | CRAX<br>2     | CRAX<br>1  | CRAX           |

| Register 37hex<br>(Cross cursor display position setting: Y) | 0  | 0 | 1   | 1      | 0    | 1    | 1 | 1   | CRAY<br>7  | CRAY<br>6  | CRAY<br>5  | CRAY<br>4     | CRAY<br>3    | CRAY<br>2     | CRAY<br>1  | CRAY           |

#### **Command Descriptions**

- Note: 1. After a hardware reset, always first send register 00 command, and only then issue the various commands. The LC78711E may operate incorrectly if a register 00 command is not issued.

- 2. All data transfers must be performed LSB first.

- 3. The (0) and (1) notations in the second byte indicate the default values.

#### 1. Register 00hex

|                                    | MSB         |             |             |             |           |          |          | LSB                |  |  |

|------------------------------------|-------------|-------------|-------------|-------------|-----------|----------|----------|--------------------|--|--|

|                                    | Data7       | Data6       | Data5       | Data4       | Data3     | Data2    | Data1    | Data0              |  |  |

| First byte                         | 0           | 0           | 0           | 0           | 0         | 0        | 0        | 0                  |  |  |

| Register 00hex identification code |             |             |             |             |           |          |          |                    |  |  |

| Second byte                        | INIT<br>(0) | SCP2<br>(1) | SCP1<br>(1) | SCP0<br>(0) | CB<br>(0) | 1<br>(0) | 0<br>(0) | VRAM<br>/BG<br>(0) |  |  |

|                                    |             |             |             |             | <u> </u>  | <u> </u> |          |                    |  |  |

- Data7: INIT

- Function: System reset

- Operation: INIT = 0: The LC78711E internal state is not reset (normal operation continues)

INIT = 1: The internal state is reset (The display is set to a blue background screen.)

- Data6: SCP2

- Data5: SCP1

Data4: SCP0

- Function: YS output (pin 46) control

- Operation: SCP2 = 0: When (SCP0, SCP1) is (0,0) or (0,1), the whole screen is set to low (transparent) if the comparison condition did not hold.

- SCP2 = 1: When (SCP0, SCP1) is (0,0) or (0,1), the whole screen is set to high (display) if the comparison condition did not hold.

The superimpose mode comparison condition is determined by the SCP1 and SCP2 setting. (Only valid when pin 60, SON, is 1)

| SCP1 | SCP0 | Comparison condition (YS pin output operation setting)                                                                                                               |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | No comparison performed                                                                                                                                              |

| 1    | 0    | If the border color was not black, YS is set to high (display) for sections that do not match the border color, and set to low (transparent) for all other sections. |

| 1    | 1    | Sets YS high for sections that do not match the chroma key color, and low for all other sections.                                                                    |

- Data3: CB

- Function: Color bar screen output setting

- Operation: CB = 0: The graphics signal is output.

- CB = 1: A color bar signal is output.

- Data2: 1

— Operation: This bit must always be set to 1. The LC78711E may not operate correctly if this bit is not set to 1.

- Data1: 0

- Operation: This bit must always be set to 0. The LC78711E may not operate correctly if this bit is not set to 0.

- Data0: VRAM/BG

- Function: Switches the displayed screen

- Operation: VRAM/BG = 0: Displays the contents of VRAM

- VRAM/BG = 1: Displays the background color

2. Register 01hex

| MSB                                |                          |                                                                                                         |                                                                                                                 |                                                                                                                                               |                                                                                                                                                                            |                                                                                                                                                                                                          | LSB                                                                                                                                                                                                                                                                                                                                |  |  |

|------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data7                              | Data6                    | Data5                                                                                                   | Data4                                                                                                           | Data3                                                                                                                                         | Data2                                                                                                                                                                      | Data1                                                                                                                                                                                                    | Data0                                                                                                                                                                                                                                                                                                                              |  |  |

| 0                                  | 0                        | 0                                                                                                       | 0                                                                                                               | 0                                                                                                                                             | 0                                                                                                                                                                          | 0                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                  |  |  |

| Register 01hex identification code |                          |                                                                                                         |                                                                                                                 |                                                                                                                                               |                                                                                                                                                                            |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                    |  |  |

| VP3<br>(0)                         | VP2<br>(0)               | VP1<br>(0)                                                                                              | VP0<br>(0)                                                                                                      | HP3<br>(0)                                                                                                                                    | HP2<br>(0)                                                                                                                                                                 | HP1<br>(0)                                                                                                                                                                                               | HP0<br>(0)                                                                                                                                                                                                                                                                                                                         |  |  |

|                                    | Data7<br>0<br>MSB<br>VP3 | Data7         Data6           0         0           ▶         Reg           MSB         VP3         VP2 | Data7     Data6     Data5       0     0     0       →     Register 01hex id       MSB       VP3     VP2     VP1 | Data7     Data6     Data5     Data4       0     0     0     0       Register 01hex identification       MSB       VP3     VP2     VP1     VP0 | Data7     Data6     Data5     Data4     Data3       0     0     0     0     0       Register 01hex identification code       MSB       VP3     VP2     VP1     VP0     HP3 | Data7     Data6     Data5     Data4     Data3     Data2       0     0     0     0     0     0       ►     Register 01hex identification code       MSB       VP3     VP2     VP1     VP0     HP3     HP2 | Data7         Data6         Data5         Data4         Data3         Data2         Data1           0         0         0         0         0         0         0         0           ▶         Register 01hex identification code         MSB         VP3         VP2         VP1         VP0         HP3         HP2         HP1 |  |  |

• Data7: VP3

Data6: VP2

Data5: VP1

Data4: VP0

- Function: These bits set the vertical direction display start position.

- Operation: Sets the display position as a two's complement value with positive indicating up in the vertical direction. The position is set in two dot units, supporting a range of from -16 to +14 dots from the center position.

- Data3: HP3

Data2: HP2

- Data1: HP1

- Data0: HP0

- Function: These bits set the horizontal direction display start position.

- Operation: Sets the display position as a two's complement value with positive indicating left in the horizontal direction. The position is set in two dot units, supporting a range of from -16 to +14 dots from the center position.

#### 3. Register 04hex

|            | MSB   |       |       |       |       |       |       | LSB   |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|

|            | Data7 | Data6 | Data5 | Data4 | Data3 | Data2 | Data1 | Data0 |

| First byte | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

-----> Register 04hex identification code

|             | MSB  |      |      |      |      |      |      | LSB  |

|-------------|------|------|------|------|------|------|------|------|

| Second byte | CRG3 | CRG2 | CRG1 | CRG0 | CRR3 | CRR2 | CRR1 | CRR0 |

| Cocona Sylo | (0)  | (0)  | (0)  | (0)  | (0)  | (0)  | (0)  | (0)  |

• Data7: CRG3

Data6: CRG2

Data5: CRG1

Data4: CRG0

- Function: The green color data setting

- Operation: Specifies the green color data. There are 16 values in the range 0 to F (hexadecimal).

- Data3: CRR3

Data2: CRR2

Data1: CRR1

Data0: CRR0

- Function: The red color data setting

- Operation: Specifies the red color data. There are 16 values in the range 0 to F (hexadecimal).

4. Register 05hex

|                                    | MSB   |       |       |       |       |       |       | LSB   |  |  |

|------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

|                                    | Data7 | Data6 | Data5 | Data4 | Data3 | Data2 | Data1 | Data0 |  |  |

| First byte                         | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     |  |  |

| Register 05hex identification code |       |       |       |       |       |       |       |       |  |  |

|                                    | CROS  | CRKY  | BGCL  | 0     | CRB3  | CRB2  | CRB1  | CRB0  |  |  |

| Second byte                        | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |  |  |

#### • Data7: CROS

- Function: Cross cursor display color setting

- Operation: Acquires the color set in bits CRR3:0, CRG3:0, and CRB3:0 as the cross cursor display color.

- Data6: CRKY

- Function: Chroma key color setting

- Operation: Acquires the color set in bits CRR3:0, CRG3:0, and CRB3:0 as the chroma key color.

- Data5: BGCL

- Function: Background color setting

- Operation: Acquires the color set in bits CRR3:0, CRG3:0, and CRB3:0 as the background color.

- Data4: Unused (Must be set to 0.)

- Data3: CRB3

- Data2: CRB2

- Data1: CRB1

- Data0: CRB0

First byte

Seco

- Function: The blue color data setting

- Operation: Specifies the blue color data. There are 16 values in the range 0 to F (hexadecimal).

- 5. Register 06hex

| MSB   |       |       |       |       |       |       | LSB   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Data7 | Data6 | Data5 | Data4 | Data3 | Data2 | Data1 | Data0 |

| 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     |

-----> Register 06hex identification code

|          | MSB |     |     |     |     |     |     | LSE |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|

|          |     |     |     |     |     | BST |     |     |

| ond byte | R/F | 0   | 0   | 0   | 0   | ON  | PH1 | PH0 |

|          | (0) | (0) | (0) | (0) | (0) | (0) | (0) | (0) |

|          |     |     |     |     |     |     | •   |     |

- Data7: R/F

- Function: Color burst phase timing setting during superimpose operation

- Operation: R/F = 0: Set to the rising edge of the 4fsc clock

R/F = 1: Set to the falling edge of the 4fsc clock

- Data6: Unused (Must be set to 0.)

- Data5: Unused (Must be set to 0.)

Data4: Unused (Must be set to 0.)

Data3: Unused (Must be set to 0.)

- Data2: BSTON

- Function: Color burst signal output control setting during superimpose operation

- Operation: BSTON = 0: Burst signal output is turned off

- BSTON = 1: Burst signal output is turned on

#### • Data1: PH1

- Data0: PH0

- Function: Color burst signal phase setting during superimpose operation

- Operation:

| PH1 | PH0 | Phase |

|-----|-----|-------|

| 0   | 0   | 0°    |

| 0   | 1   | 90°   |

| 1   | 0   | 180°  |

| 1   | 1   | 270°  |

#### 6. Register 07hex

|             | MSB   |        |               |               |       |       |           | LSB   | 3 |

|-------------|-------|--------|---------------|---------------|-------|-------|-----------|-------|---|

|             | Data7 | Data6  | Data5         | Data4         | Data3 | Data2 | Data1     | Data0 |   |

| First byte  | 0     | 0      | 0             | 0             | 0     | 1     | 1         | 1     | ] |

|             |       | > Regi | ster 07hex id | dentification | code  |       | 488.00.07 |       |   |

|             | MSB   |        |               |               | 1     |       |           | LSB   | 1 |

|             | 0     | 0      | 0             | 0             | YT3   | YT2   | YT1       | YT0   |   |

| Second byte | (0)   | (0)    | (0)           | (0)           | (0)   | (1)   | (0)       | (1)   |   |

- Data7: Unused (Must be set to 0.) Data6: Unused (Must be set to 0.) Data5: Unused (Must be set to 0.)

- Data4: Unused (Must be set to 0.)

- Data3: YT3

- Data2: YT2

- Data1: YT1

- Data0: YT0

- Function: YS (pin 46) output phase adjustment setting

- Operation: Sets the YS output timing in single 4fsc clock units. The default is a phase setting identical to that of the video output.

- 7. Register 08hex

|                                    | MSB         |             |          | -        |             |             |             | LSB         |  |  |

|------------------------------------|-------------|-------------|----------|----------|-------------|-------------|-------------|-------------|--|--|

|                                    | Data7       | Data6       | Data5    | Data4    | Data3       | Data2       | Data1       | Data0       |  |  |

| First byte                         | 0           | 0           | 0        | 0        | 1           | 0           | 0           | 0           |  |  |

| Register 08hex identification code |             |             |          |          |             |             |             |             |  |  |

| Second byte                        | MVMD<br>(0) | EXSN<br>(0) | 0<br>(0) | 0<br>(0) | TST3<br>(0) | TST2<br>(0) | TST1<br>(0) | TST0<br>(0) |  |  |

#### • Data7: MVMD

- Function: Moving display area setting during superimpose operation

- Operation: MVMD = 0: Only the display area moves

- MVMD = 1: The area including the border area moves (only left and right motion is possible with this setting.)

- Data6: EXSN

- Function: Synchronizing signal reset control setting for external synchronization mode, i.e., when SON = 1.

- Operation: EXSN = 0: Reset is executed on the falling edge of the  $\overline{\text{HRESET}}$  (pin 54) and  $\overline{\text{VRESET}}$  (pin 56) signals.

- EXSN = 1: Reset is executed on the falling edge of the  $\overline{VRESET}$  (pin 56) signal. (The  $\overline{HRESET}$  signal is not required.)

- Data5: Unused (Must be set to 0.)

Data4: Unused (Must be set to 0.)

- Data3: TST3

- Data2: TST2

- Data1: TST1

Data0: TST0

First byt

- Function: Test mode settings

- Operation: These bits must be set to 0 during normal operation.

- 8. Register 09hex

|   | MSB   | (SB   |       |       |       |       |       |       |  |  |  |  |

|---|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|   | Data7 | Data6 | Data5 | Data4 | Data3 | Data2 | Data1 | Data0 |  |  |  |  |

| е | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 1     |  |  |  |  |

Register 09hex identification code

|             | MSB |     |     |      |      |      |      | LSB  |

|-------------|-----|-----|-----|------|------|------|------|------|

| Second byte | 0   | 0   | 0   | SCV4 | SCV3 | SCV2 | SCV1 | SCV0 |

|             | (0) | (0) | (0) | (0)  | (0)  | (0)  | (0)  | (0)  |

• Data7: Unused (Must be set to 0.) Data6: Unused (Must be set to 0.)

Data5: Unused (Must be set to 0.)

- Data4: SCV4

- Data3: SCV3

- Data2: SCV2

- Data1: SCV1

Data0: SCV0

- Function: Subtitle scrolling amount (vertical direction setting in character units)

- Operation: Scrolls the screen display position up in character units. The scrolling amount can be set to a value in the range 0 to 17 characters, where a single character is 12 vertical dots (12 H).

- 9. Register 0Ahex

|             | MSB        |         |               |                 |       |       |          | LSB   |

|-------------|------------|---------|---------------|-----------------|-------|-------|----------|-------|

|             | Data7      | Data6   | Data5         | Data4           | Data3 | Data2 | Data1    | Data0 |