CMOS IC

# LC74201JE

# Single Chip MPEG Decoder

### **Overview**

The LC74201JE is a CMOS IC that integrates the signal processing functions required of a video CD decoder to a single chip. All that it takes to make a version 1 or version 2 video CD player is the addition of a CD digital signal processor, DRAM, an audio D/A converter, digital video encoder, and similar components.

#### **Features**

- Incorporation of virtually almost all the functionality required by a video CD player from the CD-ROM decoder through to the MPEG audio and video decoders in a single chip

- Fully automatic playback with automatic decoding within the LSI in response to simple external commands and the MPEG bit stream

- Special playback functions are activated by command inputs, and do not require signal processing by the host microcontroller

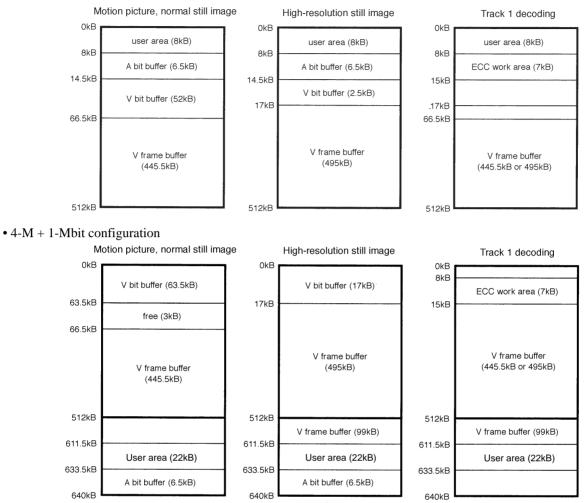

- Support for two external DRAM configurations: 4 M bits (256k × 16 bits) or 4 M bits (256k × 16 bits) + 1 M bit (64k × 16 bits)

- Support for a Track 1 DRAM user area (i.e., sector buffer) of up to 8 k bytes (4 M bits of external DRAM) or 22 k bytes (4 M +1 M bits of external DRAM)

- · Automatic synchronization of audio and video

- Built-in high-speed decoder core that supports variablespeed video playback at up to quadruple speed. Audio support for normal and double-speed playback.

- Internal registers that offer configuration settings for connecting to most commercially available CD digital signal processors and D/A converters

- Compatible with version 2 of the video CD standard. Support for superimposition of closed caption data on the output signal as specified in the EIA608 standard

- Support for Photo CD standard. (Base/4 and Base/16)

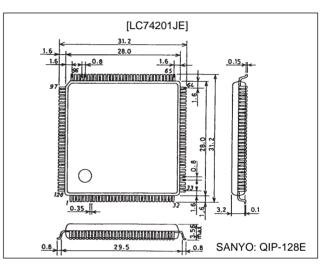

# **Package Dimensions**

unit: mm

3182-QFP-128E

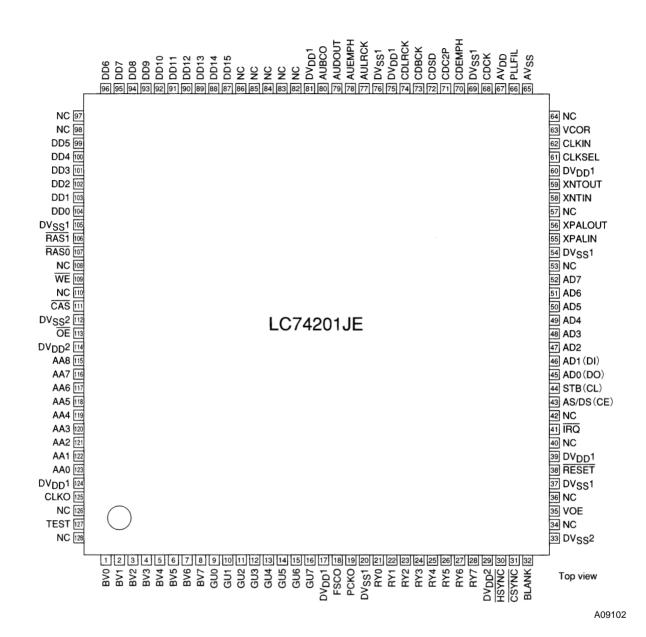

#### **Pin Assignment**

No. 5761-2/21

# **Pin Function**

Power Supply, Test Pin, Unconnected Pins

| Pin No.                           | Symbol             | I/O | Logic    | Function                                                                                                                                               |  |

|-----------------------------------|--------------------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 17<br>39<br>60<br>75<br>81<br>124 | DV <sub>DD</sub> 1 | _   | _        | System power supply (4-V power supply: 3.7 to 4.0 V)                                                                                                   |  |

| 20<br>37<br>54<br>69<br>76<br>105 | DV <sub>SS</sub> 1 | _   | _        | stem power supply (connect to ground)                                                                                                                  |  |

| 29<br>114                         | DV <sub>DD</sub> 2 | -   | _        | Power supply for 5-V I/O pins (5-V power supply: 5.0 $\pm$ 0.5 V)                                                                                      |  |

| 33<br>112                         | DV <sub>SS</sub> 2 | _   | -        | Power supply for 5-V I/O pins (connect to ground)                                                                                                      |  |

| 65                                | AV <sub>SS</sub>   | _   | -        | Power supply for VCO and PLL (connect to ground)                                                                                                       |  |

| 67                                | AV <sub>DD</sub>   | -   | -        | Power supply for VCO and PLL (4-V power supply: 3.7 to 4.0 V)                                                                                          |  |

| 125                               | CLKO               | Out | Positive | Clock output for VCO and PLL at test                                                                                                                   |  |

| 127                               | TEST               | In  | Positive | Test mode control pin (normally kept at low level)                                                                                                     |  |

|                                   | NC                 | -   | _        | Unconnected pins below must be connected to GND or left open<br>34, 36, 40, 42, 53, 57, 64, 82, 83, 84 pins<br>85, 86, 97, 98, 108, 110, 126, 128 pins |  |

#### LC74201JE

#### Clock Pins

| Pin No. | Symbol  | I/O          | Logic    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|---------|---------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 18      | FSCO    | Out          | Positive | Subcarrier clock output (frequency = $1/4$ pixel clock frequency). Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 19      | РСКО    | Out          | Positive | Pixel clock output (NTSC-4fsc, PAL-4fsc, or 13.5 MHz). Tristate output using DV <sub>DD</sub> 1 (4-V) power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 55      | XPALIN  | In           | -        | Crystal accillator connections for PAL Afric accillation circuit (Afric – 17.734475 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 56      | XPALOUT | Out          | -        | Crystal oscillator connections for PAL-4fsc oscillation circuit (4fsc = 17.734475 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 56      | XNTIN   | In           | -        | ystal oscillator connections for NTSC-4fsc oscillation circuit (4fsc = 14.31818 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 59      | XNTOUT  | XNTOUT Out – |          | Crystal Oscillator confidences for two solutions contactors and the contactor of the cont |  |  |  |

| 61      | CLKSEL  | In           | Positive | Clock selection control input. High: 54.0-MHz clock input from pin 62 (CLKIN); Low: clock from internal VCO oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 62      | CLKIN   | In           | Positive | 54.0-MHz clock input (with built-in bias). When not used, connect to $DV_{DD}1$ or $DV_{SS}1$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 63      | VCOR    | -            | -        | Adjustment resistor connection for VCO oscillator circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 66      | PLLFIL  | -            | -        | PLL filter connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 68      | CDCK    | In           | Positive | CD-DSP clock input (16.9344, 2.8224, or 2.1168 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

#### Microcontroller Interface

| Pin No. | Symbol     | I/O | Logic    | Function                                                                                                                                  |  |  |  |

|---------|------------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 38      | RESET      | In  | Negative | System reset input (Hysteresis input; built-in pull-up resistor).                                                                         |  |  |  |

| 41      | ĪRQ        | Out | Negative | rupt request signal output (N-channel open-drain output).                                                                                 |  |  |  |

| 43      | AS/DS (CE) | In  | Positive | Parallel interface: Address/data select input (Low = address).<br>Serial interface: Serial transfer enable signal input (High = enabled). |  |  |  |

| 44      | STB (CL)   | In  | Positive | Parallel interface: Strobe signal input for address input and data I/O.<br>Serial interface: Serial transfer clock signal input.          |  |  |  |

| 45      | AD0 (DO)   | I/O | Positive | Parallel interface: Address/data I/O port P0 (LSB).<br>Serial interface: ZPSerial data output (LSB-first input).                          |  |  |  |

| 46      | AD1 (DI)   | I/O | Positive | Parallel interface: Address/data I/O port P1.<br>Serial interface: Serial data input (LSB-first output).                                  |  |  |  |

| 47      | AD2        | I/O | Positive |                                                                                                                                           |  |  |  |

| 48      | AD3        | I/O | Positive | Parallel interface: Address/data I/O ports.<br>The interface mode is determined at the release of the system reset.                       |  |  |  |

| 49      | AD4        | I/O | Positive | The mode is determined by setting the three bits of AD3, AD4, and AD5.<br>• Serial interface: AD5:AD4:AD3 = 1:*:* (* = Don't care)        |  |  |  |

| 50      | AD5        | I/O | Positive | • Parallel interface: AD5:AD4:AD3 = 0:1:0 or 0:11:1 or 0:0:0                                                                              |  |  |  |

| 51      | AD6        | I/O | Positive | AD7: Parallel interface address/data I/O port P7 (MSB).                                                                                   |  |  |  |

| 52      | AD7 (MBS)  | I/O | Positive |                                                                                                                                           |  |  |  |

Note: AD0 to AD7 use N-channel open-drain outputs.

#### CD Interfaces

| Pin No. | Symbol | I/O | Logic    | Function                                       |

|---------|--------|-----|----------|------------------------------------------------|

| 70      | CDEMPH | In  | Positive | Emphasis input (hysteresis input)              |

| 71      | CDC2P  | In  | Positive | C2 error flag input (hysteresis input)         |

| 72      | CDSD   | In  | Positive | Serial data input (hysteresis input)           |

| 73      | CDBCK  | In  | Positive | Serial data bit clock input (hysteresis input) |

| 74      | CDLRCK | In  | Positive | Left/right clock input (hysteresis input)      |

#### Audio D/A Converter Interface

| Pin No. | Symbol | I/O | Logic    | Function                           |

|---------|--------|-----|----------|------------------------------------|

| 77      | AULRCK | Out | Positive | Audio data left/right clock output |

| 78      | AUEMPH | Out | Positive | Audio emphasis flag output         |

| 79      | AUDOUT | Out | Positive | Audio data serial output           |

| 80      | AUBCO  | Out | Positive | Audio data bit clock output        |

#### Video Interface

| Pin No. | Symbol    | I/O | Logic    | Function                                                       |

|---------|-----------|-----|----------|----------------------------------------------------------------|

| 1       | BV0 (LSB) | I/O | Positive | Video signal outputs (B/V signals). (Normally in output mode.) |

| 2       | BV1       | I/O | Positive |                                                                |

| 3       | BV2       | I/O | Positive |                                                                |

| 4       | BV3       | I/O | Positive | Tristate output using DV <sub>DD</sub> 1 (4-V) power supply.   |

| 5       | BV4       | I/O | Positive | Video signal outputs (B/V signals). (Normally in output mode.) |

| 6       | BV5       | I/O | Positive |                                                                |

| 7       | BV6       | I/O | Positive |                                                                |

| 8       | BV7 (MSB) | I/O | Positive | Tristate output using DV <sub>DD</sub> 2 (4-V) power supply.   |

| 9       | GU0 (LSB) | I/O | Positive | Video signal outputs (G/U signals). (Normally in output mode.) |

| 10      | GU1       | I/O | Positive |                                                                |

| 11      | GU2       | I/O | Positive |                                                                |

| 12      | GU3       | I/O | Positive | Tristate output using DV <sub>DD</sub> 1 (4-V) power supply.   |

| 13      | GU4       | I/O | Positive | Video signal outputs (G/U signals). (Normally in output mode.) |

| 14      | GU5       | I/O | Positive |                                                                |

| 15      | GU6       | I/O | Positive |                                                                |

| 16      | GU7 (MSB) | I/O | Positive | Tristate output using DV <sub>DD</sub> 2 (4-V) power supply.   |

| 21      | RY0 (LSB) | I/O | Positive | Video signal outputs (R/Y signals). (Normally in output mode.) |

| 22      | RY1       | I/O | Positive |                                                                |

| 23      | RY2       | I/O | Positive |                                                                |

| 24      | RY3       | I/O | Positive | Tristate output using DV <sub>DD</sub> 1 (4-V) power supply.   |

Continued on next page.

#### LC74201JE

Continued from preceding page

| Pin No. | Symbol     | I/O | Logic    | Function                                                                                                                                |

|---------|------------|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 25      | RY4        | I/O | Positive | Video signal outputs (R/Y signals). (Normally in output mode.)                                                                          |

| 26      | RY5        | I/O | Positive |                                                                                                                                         |

| 27      | RY6        | I/O | Positive |                                                                                                                                         |

| 28      | RY7 (MSB)  | I/O | Positive | Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.                                                                            |

| 30      | HSYNC      | Out | Negative | Horizontal synchronization signal output. Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.                                  |

| 31      | CSYNC      | Out | Negative | Composite synchronization signal output. Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.                                   |

| 32      | BLANK      | Out | Positive | Blanking signal output (horizontal and vertical blanking interval signal). Tristate output using DV <sub>DD</sub> 2 (5-V) power supply. |

| 35      | VOE        | In  | Positive | Video output enable signal input. High: Enable output.                                                                                  |

| 87      | DD15 (MSB) | I/O | Positive | Data I/O interface with DRAM.                                                                                                           |

| 88      | DD14       | I/O | Positive |                                                                                                                                         |

| 89      | DD13       | I/O | Positive |                                                                                                                                         |

| 90      | DD12       | I/O | Positive |                                                                                                                                         |

| 91      | DD11       | I/O | Positive |                                                                                                                                         |

| 92      | DD10       | I/O | Positive |                                                                                                                                         |

| 93      | DD9        | I/O | Positive |                                                                                                                                         |

| 94      | DD8        | I/O | Positive |                                                                                                                                         |

| 95      | DD7        | I/O | Positive |                                                                                                                                         |

| 96      | DD6        | I/O | Positive |                                                                                                                                         |

| 99      | DD5        | I/O | Positive |                                                                                                                                         |

| 100     | DD4        | I/O | Positive |                                                                                                                                         |

| 101     | DD3        | I/O | Positive |                                                                                                                                         |

| 102     | DD2        | I/O | Positive |                                                                                                                                         |

| 103     | DD1        | I/O | Positive |                                                                                                                                         |

| 104     | DD0 (LSB)  | I/O | Positive | Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.                                                                            |

| 106     | RAS1       | Out | Negative | Row address strobe signal output to expansion 1-Mbit DRAM.<br>Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.              |

| 107     | RAS0       | Out | Negative | Row address strobe signal output to 4-Mbit DRAM.<br>Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.                        |

| 109     | WE         | Out | Negative | Write enable signal output to DRAM. Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.                                        |

| 111     | CAS        | Out | Negative | Column address strobe signal output to DRAM. N-channel open-drain output.                                                               |

| 113     | ŌĒ         | Out | Negative | Output enable signal output to DRAM. Tristate output using DV <sub>DD</sub> 2 (5-V) power supply.                                       |

Continued on next page.

#### LC74201JE

#### Continued from preceding page

| Pin No. | Symbol    | I/O | Logic    | Function                                                     |

|---------|-----------|-----|----------|--------------------------------------------------------------|

| 115     | AA8 (MSB) | Out | Positive | Address output to DRAM.                                      |

| 116     | AA7       | Out | Positive |                                                              |

| 117     | AA6       | Out | Positive |                                                              |

| 118     | AA5       | Out | Positive |                                                              |

| 119     | AA4       | Out | Positive |                                                              |

| 120     | AA3       | Out | Positive |                                                              |

| 121     | AA2       | Out | Positive |                                                              |

| 122     | AA1       | Out | Positive |                                                              |

| 123     | AA0 (LSB) | Out | Positive | Tristate output using DV <sub>DD</sub> 2 (5-V) power supply. |

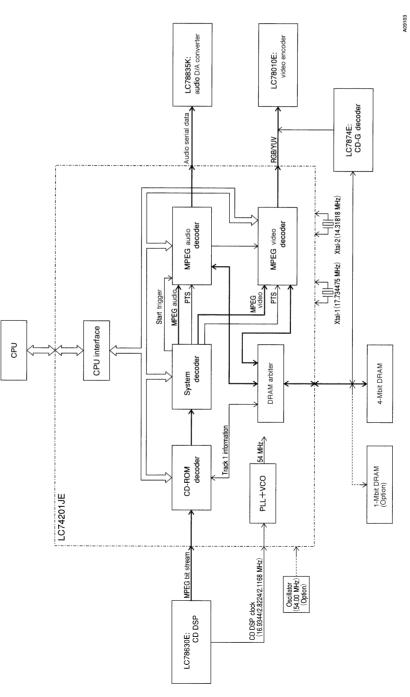

# **Block Diagram**

#### **Block Descriptions**

1. CD-ROM decoder

This block takes the MPEG bit stream from the external CD digital signal processor and decodes it in accordance with the CD-ROM standard.

- The decoded data is automatically transferred to the next stage, the system decoder.

- Storing the decoded data in DRAM is also possible.

- The high-speed decoder core supports quadruple-speed playback.

- Internal registers offer settings for connecting to most commercially available CD digital signal processors.

- 32- or 24-slot

- LSB or MSB first

- Front- or rear-justification for data

- Rising or falling edge for bit clock

- The video CD's track 1 data can be stored in a user area set aside in the external DRAM. The user area capacity can be selected from 4 K to 22 Kbytes according to the external DRAM capacity.

- An auto restart function stores the address of the last sector accessed before a pause so that playback can resume at the next sector when the pause ends.

- The contents of the sector header and subheader are available from registers.

- 2. System decoder

This block analyzes the MPEG bit stream, splits it into video and audio bit streams, and transfers these bit streams to the corresponding decoders. It calculates the decode start timing from the time stamp and the decoders' inherent delays and generates the necessary start signals to provide automatic synchronization of audio and video outputs.

3. CPU interface

This interface allows the CPU to access the internal registers to set parameters controlling operation and to read out operational status. It may be configured as either an 8-bit parallel interface multiplexing data and addresses or as a 4-wire serial interface.

4. Audio decoder

This block decodes the MPEG1 audio bit stream from the system decoder in accordance with the ISO11172-3 standard.

- The use of 24-bit internal precision yields high audio quality.

- The decoder supports all MPEG audio modes defined for layers 1 and 2 except the free format mode.

- Internal registers offer settings for connecting to most commercially available D/A converters.

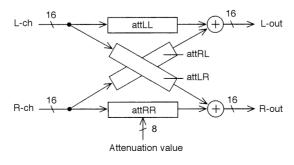

- The block includes a cross attenuator compliant with the CD-i standard.

- The block supports readout of the frame header data.

- The block performs CRC checking. If there is an error, it automatically substitutes the preceding frame stored in DRAM. If there are continuous errors, it switches to muting.

- The output format of audio D/A converter's interface may be selected between normal output and open-drain output in accordance with the D/A converter input level.

**Cross Attenuator**

#### 5. Video decoder

This block decodes all layers (from the video sequence layer to the block layer plus the headers) from the MPEG1 video bit stream from the system decoder in accordance with the ISO11172-2 standard.

- The decoding requires no external signal processing. The LSI internals handle everything automatically. All that is required from outside the chip are simple commands and the MPEG bit stream.

- A PLL circuit permits synchronization of the system clock with the CD digital signal processor. Commands offer a choice of the following frequencies.

- 16.9344 MHz

- 2.8224 MHz

- 2.1168 MHz

- The decoder supports the following image formats.

- 352 dots × 240 lines, 29.97 Hz (NTSC, PAL-60 Hz)

- 352 dots × 240 lines, 23.976 Hz (Film)

- 352 dots × 288 lines, 25.00 Hz (PAL)

- 704 dots × 480 lines, high-resolution still image (NTSC)

- 704 dots  $\times$  576 lines, high-resolution still image (PAL)

- Built-in filters provide high image quality.

- Built-in sampling rate conversion filter for horizontal direction

- Built-in vertical filter

- The decoder supports a variety of video output specifications.

- Support for NTSC (59.94 Hz) and PAL (50 Hz) monitors

- Built-in video timing generator

- Switching between interlaced and non-interlaced operation

- Built-in YUV-to-RGB conversion matrix with choice of 24-bit RGB, 24-bit YUV, and 16-bit YUV output

- Film-to-NTSC conversion

- Simple two-way conversion between NTSC or Film and PAL with built-in aspect ratio conversion

- Choice of pixel clocks: 13.5 MHz, 6.75 MHz, and 4 fsc

- The decoder offers special playback functions.

- Special playback functions require no signal processing by the CPU.

- Such functions as double-, triple-, and quadruple-speed playback, still image playback, pause, slow, and single-stepping (one-cut play) are available with simple commands.

- The built-in multitile function offers the display of 4 or 16 small images on the screen with the display

positions freely selectable and processing of up to two fields supported.

- The built-in wipe function supports wiping within a frame, display outside that frame, and changing the frame color.

- The built-in fade-in and fade-out functions.

- The decoder includes bit buffer management functions.

- These monitor the bit buffer for errors and control the decoder to automatically adjust the amount of data in the bit buffer to maintain normal operation at all times.

- Depending on the state of the bit buffer, the decoder automatically skips or repeats images. Skipping gives

precedence to B pictures.

- The decoder includes frame buffer management functions.

These provide all internal support for frame buffer mapping control (for the display, reconstruction frame, front frame, and rear frame) and the mapping control and setting accompanying mode changes between high-resolution still images and motion picture playback.

- The decoder includes various fail-safe functions.

- The decoder supports version 2 of the video CD standard.

- User data is accessible from outside the decoder.

- The decoder supports superimposition of closed caption data on the output RGB/YUV signal as specified in the EIA608 standard.

- The decoder supports decoding of Photo CDs (using Base/4 and lower).

#### 6. DRAM arbiter

This block provides the interface to the external DRAM. In addition to the standard 4-M bit DRAM, there can also be a 1-M bit DRAM for supporting PAL high-resolution still image playback. If this additional DRAM is not available, the LSI trims the top and bottom 48 lines of the image and provides a function for vertically scrolling the display area in 16-line increments.

# Absolute Maximum Ratings

| Parameter              | Cumbal             | Conditions                                                                                                | Rat                      | Linit                    |        |

|------------------------|--------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------|

| Parameter              | Symbol             | Conditions                                                                                                | min                      | max                      | - Unit |

|                        | V <sub>DD</sub> 1  | DV <sub>DD</sub> 1 pin                                                                                    | DV <sub>SS</sub> 1 - 0.3 | DV <sub>SS</sub> 1 + 4.0 | V      |

| Maximum supply voltage | V <sub>DD</sub> 2  | DV <sub>DD</sub> 2 pin                                                                                    | $DV_{SS}2 - 0.3$         | DV <sub>SS</sub> 2 + 6.0 | V      |

|                        | V <sub>DD</sub> 3  | AV <sub>DD</sub> pin                                                                                      | $AV_{SS} - 0.3$          | AV <sub>SS</sub> + 4.0   | V      |

|                        | V <sub>IN</sub> 1  | BV0 to EV3, GU0 to GU3, RY0 to RY3,<br>RESET, XPALIN, XNTIN, CLKIN, VCOR,<br>PLLFIL, TEST pins            | DV <sub>SS</sub> 1 – 0.3 | DV <sub>DD</sub> 1 + 0.3 | V      |

| Input voltage          | V <sub>IN</sub> 2  | VOE, AS/DS, STB, AD0 to AD7, CLKSEL<br>CDCK, CDEMPH, CDC2P, CDSD, CDBCK,<br>CDLRCK pins                   | DV <sub>SS</sub> 1 – 0.3 | 5.5                      | V      |

|                        | V <sub>IN</sub> 3  | BV4 to BV7, GU4 to GU7, RY4 to RY7,<br>DD0 to DD15 pins                                                   | DV <sub>SS</sub> 2-0.3   | DV <sub>SS</sub> 2 + 0.3 | V      |

|                        | V <sub>OUT</sub> 1 | BV0 to BV3, GU0 to GU3, RY0 to RY3,<br>PCK0, XPALOUT, XNTOUT, CLK0, AULRCK,<br>AUEMPH, AUDOUT, AUBC0 pins | DV <sub>SS</sub> 1 – 0.3 | DV <sub>DD</sub> 1 + 0.3 | V      |

| Output voltage         | V <sub>OUT</sub> 2 | IRQ, AD0 to AD 7, CAS pins                                                                                | DV <sub>SS</sub> 1 - 0.3 | -                        | V      |

|                        | V <sub>OUT</sub> 3 | BV4 to BV7, GU4 to GU7, RY4 to RY7,<br>FSC0, HSYNC, CSYNC, BLANK, RASO, RAS1,<br>WE, OE, AA0 to AA8 pins  | DV <sub>SS</sub> 2 - 0.3 | DV <sub>DD</sub> 2 + 0.3 | V      |

| Maximum current drain  | Pd max             | Ta = 25°C                                                                                                 | _                        | 500                      | mW     |

| Operating temperature  | Topr               |                                                                                                           | -10                      | +70                      | °C     |

| Storage temperature    | Tstg               |                                                                                                           | -40                      | +125                     | °C     |

# Recommended Operating Conditions at Ta = –25 $^{\circ}C$ to +75 $^{\circ}C$

| Parameter                | Symbol            | Conditions                                                   |                                                                     |                       | Ratings   |                         | Unit |

|--------------------------|-------------------|--------------------------------------------------------------|---------------------------------------------------------------------|-----------------------|-----------|-------------------------|------|

| Parameter                | Symbol            |                                                              | Conditions                                                          |                       | typ       | max                     |      |

|                          | V <sub>DD</sub> 1 | DV <sub>DD1</sub> pin                                        |                                                                     | 3.7                   | -         | 4.0                     | V    |

| Supply voltage           | V <sub>DD</sub> 2 | DV <sub>DD2</sub> pin                                        |                                                                     | 4.5                   | -         | 5.5                     | V    |

|                          | V <sub>DD</sub> 3 | AV <sub>DD</sub> pin                                         |                                                                     | 3.7                   | -         | 4.0                     | V    |

|                          | V <sub>IH</sub> 1 | BV0 to BV3, 0                                                | GU0 to GU3,RY0 to RY3 pins                                          | 0.7 V <sub>DD</sub> 1 | -         | V <sub>DD</sub> 1 + 0.3 | V    |

|                          | V <sub>IH</sub> 2 | RESET pin                                                    |                                                                     | 0.8 V <sub>DD</sub> 1 | -         | V <sub>DD</sub> 1 + 0.3 | V    |

|                          | V <sub>IH</sub> 3 | VOE, AD0 to                                                  | AD7, CDCK, CLKSEL, TEST pins                                        | 0.7 V <sub>DD</sub> 1 | -         | 5.5                     | V    |

| High-level input voltage | V <sub>IH</sub> 4 | AS/DS, STB,<br>CDLRCK pins                                   | CDEMPH, CDC2P, CDSD, CDBCK,                                         | 0.8 Vdd1              | -         | 5.5                     | V    |

|                          | V <sub>IH</sub> 5 | BV4 to BV7, 0<br>DD0 to DD15                                 | GU4 to GU7, RY4 to RY7, pins                                        | 0.7 Vdd1              | -         | V <sub>DD</sub> 2 + 0.3 | V    |

| Low-level input voltage  | V <sub>IL</sub> 1 |                                                              | U0 to GU7, RY0 to RY7, VOE, CDCK,<br>CLKSEL, TEST, DD0 to DD15 pins | Vss1 – 0.3            | -         | 0.3 V <sub>DD</sub> 1   | V    |

|                          | V <sub>IL</sub> 2 | RESET, AS/DS, STB, CDEMPH, CDC2P,CDSD,<br>CDBCK, CDLRCK pins |                                                                     | Vss1 – 0.3            | -         | 0.2 Vdd1                | V    |

| Clock frequency          | FOSC1             | XPALIN, XPA                                                  | LOUT pins (PAL)                                                     | _                     | 17.734475 | -                       | MHz  |

| Clock frequency          | FOSC2             | XNTIN, XNTOUT pins (NTSC)                                    |                                                                     | -                     | 14.31818  | -                       | MHz  |

| Input amplitude          | V <sub>IN</sub> 1 | CLKIN pin (C                                                 | LKSEL = high; FIN2 = 54 MHz)                                        | 1.0                   | _         | V <sub>DD</sub> 1 + 0.3 | Vp-p |

|                          |                   |                                                              | Command – 11hex; D1, D0 = 0,0                                       | -                     | 16.9344   | -                       | MHz  |

| Innut fraguancy          | F <sub>IN</sub> 1 | CDCK pin                                                     | Command – 11hex; D1, D0 = 0,1                                       | -                     | 2.1168    | -                       | MHz  |

| Input frequency          |                   |                                                              | Command – 11hex; D1, D0 = 1,0                                       | -                     | 2.8224    | -                       | MHz  |

|                          | F <sub>IN</sub> 2 | CLKIN pin (C                                                 | LKSEL = high)                                                       | _                     | 54.000    | -                       | MHz  |

| Clock duty               | fduty             | CLKIN, CDCł                                                  | <pre></pre>                                                         | 40                    | -         | 60                      | %    |

# Electrical Characteristics at Ta = -10 to $+70^{\circ}$ C, $DV_{DD}1 = AV_{DD} = 4.0$ V and $DV_{DD}2 = 5.0$ V unless otherwise specified.

| <b>D</b>                 |                   | 0.1                                                                                                      |     | Ratings |     |      |

|--------------------------|-------------------|----------------------------------------------------------------------------------------------------------|-----|---------|-----|------|

| Parameter                | Symbol            | Conditions                                                                                               | min | typ     | max | Unit |

|                          | I <sub>IH</sub> 1 | AS/DS, STB, CDEMPH, CDC2P,CDSD, CDBCK, CDLRCK pins. Condition: $\rm V_{IN}$ = 5.5 V                      | _   | -       | 1   | μA   |

|                          | I <sub>IH</sub> 2 | VOE, CLKSEL, CDCK, TEST pins.<br>Condition: V <sub>IN</sub> = 5.5 V                                      | -   | -       | 1   | μA   |

|                          | I <sub>IH</sub> 3 | $\overline{\text{RESET}}$ pin. Condition: $V_{IN} = DV_{DD}1$                                            | -   | -       | 1   | μΑ   |

| High-level input current | I <sub>IH</sub> 4 | CLKIN pin. (CLKSEL = low)<br>Condition: $V_{IN} = DV_{DD}1$                                              | _   | -       | 1   | μA   |

|                          | I <sub>IH</sub> 5 | VCOR, PLLFIL pins. ( $\overline{RESET} = Iow$ )<br>Condition: $V_{IN} = DV_{DD}1$                        | _   | -       | 1   | μA   |

|                          | I <sub>IH</sub> 6 | VCOR, PLLFIL pins. ( $\overline{RESET}$ = low)<br>Condition: V <sub>IN</sub> = DV <sub>DD</sub> 1        | -   | -       | 1   | μA   |

|                          | I <sub>IL</sub> 1 | AS/DS, STB, CDEMPH, CDC2P,CDSD, CDBCK, CDLRCK pins. Condition: $V_{IN} = DV_{SS}1$                       | -1  | -       | -   | μA   |

|                          | I <sub>IL</sub> 2 | VOE, CLKSEL, CDCK, TEST pins.<br>Condition: $V_{IN} = DV_{SS}1$                                          | -1  | -       | -   | μA   |

| Low-level input current  | I <sub>IL</sub> 3 | CLKIN pin. (CLKSEL = low)<br>Condition: $V_{IN} = DV_{SS}1$                                              | -1  | -       | -   | μA   |

|                          | I <sub>IL</sub> 4 | VCOR, PLLFIL pins. ( $\overline{\text{RESET}}$ = low)<br>Condition: V <sub>IN</sub> = DV <sub>DD</sub> 1 | -1  | -       | -   | μA   |

|                          | I <sub>IL</sub> 5 | VCOR, PLLFIL pins. ( $\overline{RESET}$ = low)<br>Condition: V <sub>IN</sub> = DV <sub>DD</sub> 1        | -1  | -       | -   | μΑ   |

| Pull-up resistor         | RPU               | RESET pin. Condition: $DV_{DD}1 = 4.0 V$                                                                 | -   | 30      | -   | kΩ   |

|                          | RPD1              | XPALIN pin. (NTSC mode)<br>Condition: DV <sub>DD</sub> 1 = 4.0 V                                         | _   | 30      | _   | kΩ   |

| Pull-down resistor       | RPD2              | XNTIN pin. (PAL mode)<br>Condition: DV <sub>DD</sub> 1 = 4.0 V                                           | _   | 30      | -   | kΩ   |

|                          | RPD3              | DD0 to DD15 pins. (Standby mode)<br>Condition: $DV_{DD}2 = 5.0 V$                                        | 100 | -       | _   | kΩ   |

Continued on next page.

Continued from preceding page.

| Parameter                      | Symbol              | Conditions                                                                                                                                                                                                                                                                                                                                                                                       |     | Unit  |     |      |

|--------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Falametei                      | Symbol              | Conditions                                                                                                                                                                                                                                                                                                                                                                                       | min | typ   | max | Unit |

| Built-in feedback resistor     | R <sub>BIAS</sub> 1 | XPALIN, XPALOUT, XNTIN, XNTOUT pins. Condition: $DV_{DD}1 = 4.0 V$                                                                                                                                                                                                                                                                                                                               | -   | 1     | -   | MΩ   |

|                                | R <sub>BIAS</sub> 2 | CLKIN pin. (CLKSEL = high)<br>Condition: DV <sub>DD</sub> 1 = 4.0 V                                                                                                                                                                                                                                                                                                                              | -   | 1     | -   | MΩ   |

|                                | V <sub>OH</sub> 1   | BV0 to BV3, GU0 to GU3, RY0 to RY3, PCK0,<br>AULRCK, AUEMPH, AUDOUT, AUBCO pins.<br>Conditions: $DV_{DD}1 = 4.0 \text{ V}$ , $I_{OH} = -1.0 \text{ mA}$                                                                                                                                                                                                                                          | 3.5 | _     | _   | v    |

|                                | V <sub>OH</sub> 2   | CLK0 pin. Conditions: $DV_{DD}1 = 4.0 \text{ V}$ , $I_{OH} = -1.0 \text{ mA}$                                                                                                                                                                                                                                                                                                                    | 3.7 | -     | -   | V    |

| High-level output voltage      | V <sub>OH</sub> 3   | $\label{eq:bound} \begin{array}{l} BV4 \text{ to } BV7, GU4 \text{ to} GU7, RY4 \text{ to} RY7, FSC0, \\ \hline \\ \overline{HSYNC}, \ \overline{CSYNC}, \ BLANK, \ DD0 \text{ to } DD15 \\ \hline \\ \overline{RAS0}, \ \overline{RAS1}, \ \overline{WE}, \ \overline{OE}, \ AA0 \text{ to } AA8 \text{ pins}. \\ \hline \\ Conditions: \ DV_{DD2} = 5.0 \ V, \ I_{OH} = -1.0 \ mA \end{array}$ | 4.5 | -     | -   | V    |

|                                | V <sub>OH</sub> 4   | XPALOUT, XNTOUT pins.<br>Conditions: $DV_{DD}1 = 4.0 \text{ V}$ , $I_{OH} = -0.1 \text{ mA}$                                                                                                                                                                                                                                                                                                     | 3.5 | _     | _   | V    |

|                                | V <sub>OL</sub> 1   | $\begin{array}{l} BV0 \text{ to } BV3, GU0 \text{ to } GU3, RY0 \text{ to } RY3, PCK0,\\ AULRCK, AUEMPH, AUDOUT, AUBCO \text{ pins}\\ Conditions: DV_{DD}1 = 4.0 \text{ V}, I_{OL} = 1.0 \text{ mA} \end{array}$                                                                                                                                                                                 | _   | _     | 0.5 | v    |

|                                | V <sub>OL</sub> 2   | CLK0 pin.<br>Conditions: DV <sub>DD</sub> 1 = 4.0 V, I <sub>OL</sub> = 1.0 mA                                                                                                                                                                                                                                                                                                                    | -   | -     | 0.3 | V    |

| Low-level output voltage       | V <sub>OL</sub> 3   | $\begin{array}{c} BV4 \text{ to } BV7, GU4 \text{ to } GU7, RY4 \text{ to} RY7, FSC0,\\ \hline \\ \overline{HSYNC}, \overline{CSYNC}, BLANK, DD0 \text{ to } DD15\\ \hline \\ \hline \\ \overline{RAS0}, \overline{RAS1}, \overline{WE}, \overline{OE}, AA0 \text{ to } AA8 \text{ pins}.\\ \hline \\ \\ Conditions: \ \\ DV_{DD2} = 5.0 \text{ V}, \ I_{OL} = 1.0 \text{ mA} \end{array}$       | _   | -     | 0.5 | V    |

|                                | V <sub>OL</sub> 4   | $\overline{IRQ}$ , AD0 to AD7 pins.<br>Conditions: DV <sub>DD</sub> 1 = 4.0 V, I <sub>OL</sub> = 1.0 mA                                                                                                                                                                                                                                                                                          | -   | -     | 0.5 | V    |

|                                | V <sub>OL</sub> 5   | $\overline{CAS}$ pin.<br>Conditions: DV <sub>DD</sub> 1 = 4.0 V, I <sub>OL</sub> = 1.0 mA                                                                                                                                                                                                                                                                                                        | -   | -     | 0.3 | V    |

|                                | V <sub>OL</sub> 6   | XPALOUT, XNTOUT pins.<br>Conditions: $DV_{DD}1 = 4.0 \text{ V}$ , $I_{OL} = 0.1 \text{ mA}$                                                                                                                                                                                                                                                                                                      | -   | -     | 0.5 | V    |

|                                | I <sub>OFF</sub> 1  | BV0 to BV3, GU0 to GU3, RY0 to RY3, PCK0 pins. Condition: $V_{OUT}$ = DV <sub>DD</sub> 1 or DV <sub>SS</sub>                                                                                                                                                                                                                                                                                     | -1  | -     | 1   | μA   |

|                                | I <sub>OFF</sub> 2  | $\overline{\text{IRQ}}$ , AD0 to AD7, $\overline{\text{CAS}}$ pins<br>Conditions: V <sub>OUT</sub> = 5.5 V or DV <sub>SS</sub>                                                                                                                                                                                                                                                                   | -1  | -     | 1   | μΑ   |

| Output off leak current        | I <sub>OFF</sub> 3  | $ \begin{array}{l} BV4 \text{ to } BV7, GU4 \text{ to } GU7, RY4 \text{ to} RY7, FSC0, \\ \hline \\ \hline \\ \overline{HSYNC}, \ \hline \\ \overline{CSYNC}, \ \\ \\ \overline{RAS0}, \ \hline \\ \overline{WE}, \ \hline \\ \overline{OE}, \ \\ AA0 \ \\ \text{to } AA7 \ \\ \text{pins.} \\ \hline \\ $       | -1  | -     | 1   | μA   |

|                                | I <sub>DD</sub> 1   | DV <sub>DD</sub> 1 pin (All outputs open)                                                                                                                                                                                                                                                                                                                                                        | -   | (100) |     | mA   |

| Current drain during operation | I <sub>DD</sub> 2   | AV <sub>DD</sub> pin (CLKSEL = low, VCO oscillating)                                                                                                                                                                                                                                                                                                                                             | _   | (15)  |     | mA   |

|                                | I <sub>DD</sub> 3   | DV <sub>DD</sub> 2 pin (All outputs open)                                                                                                                                                                                                                                                                                                                                                        | -   | (20)  |     | mA   |

#### **Microcontroller Interface**

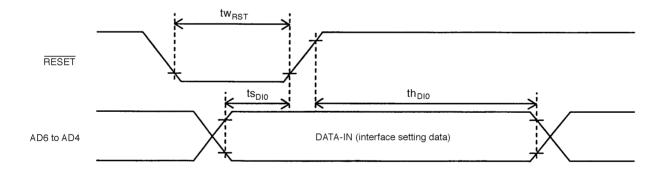

The microcontroller interface offers a choice of parallel or serial operation. The configuration is determined by the input levels at the AD4 to AD6 pins (pins 49 to 51) at the rising edge of the  $\overline{\text{RESET}}$  pin (pin 38) input.

Parallel interface setting conditions

[AD6, AD5, AD4] = [0, 1, 0]: Data read at rising edge of STB pin (pin 44) input.

[AD6, AD5, AD4] = [0, 1, 1]: Data read at falling edge of STB pin (pin 44) input.

[AD6, AD5, AD4] = [0, 0, 0]: Data read while STB pin (pin 44) input at high level.

• Serial interface setting conditions [AD6, AD5, AD4] = [1, \*, \*]

Notes: 1. Do not use any mode specifications other than the above.

- 2. A reset ( $\overline{\text{RESET}} = \text{low}$ ) configures the AD0 to AD7 pins (pins 45 to 52) for input.

- 3. The serial input mode fixes the AD2 to AD7 pins in input mode. Always treat them as input pins (by connecting them to either ground or  $DV_{DD}$ 1). If the interface is used for serial operation, the AD6 pin may be fixed at high level without any problems.

- 4. The RESET pin (pin 38) includes a built-in pul-up resistor. Do not apply a voltage higher than  $DV_{DD}1$ .

#### Timing Characteristics at Ta = +25°C, $DV_{DD}1$ = 4.0 V

| Parameter                 | Symbol            | Conditions                                           | Rat | Unit |      |

|---------------------------|-------------------|------------------------------------------------------|-----|------|------|

| Falanielei                | Symbol            | Conditions                                           | min | max  | Unit |

| Data setup time           | tS <sub>DI0</sub> | AD6 to AD4 $\rightarrow \overline{\text{RESET}}$ pin | 180 | -    | ns   |

| Data hold time            | tH <sub>DI0</sub> | AD6 to AD4 $\rightarrow \overline{\text{RESET}}$ pin | 180 | -    | ns   |

| Minimum reset pulse width | tW <sub>RST</sub> | RESET pin                                            | 180 | -    | ns   |

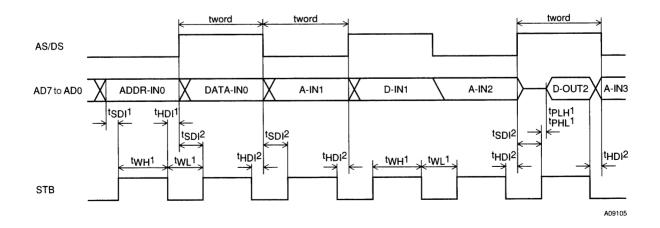

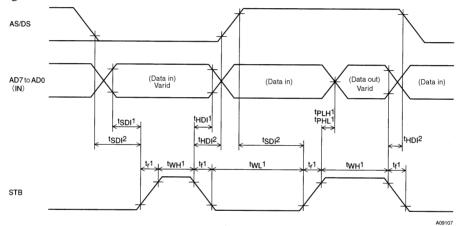

#### 1. Parallel interface

The parallel interface uses the following two input pins and eight I/O pins.

- AS/DS pin (pin 43: input): Address/data select input. low = address; high = data.

- STB pin (pin 44: input): Strobe signal input for address input and data I/O.

- AD0 pin (pin 45 : I/O): Address input and data I/O AD1 pin (pin 46 : I/O): Address input and data I/O AD2 pin (pin 47 : I/O): Address input and data I/O AD3 pin (pin 48 : I/O): Address input and data I/O AD4 pin (pin 49 : I/O): Address input and data I/O AD5 pin (pin 50 : I/O): Address input and data I/O AD6 pin (pin 51 : I/O): Address input and data I/O AD7 pin (pin 52 : I/O): Address input and data I/O AD7 pin (pin 52 : I/O): Address input and data I/O Note: The address cannot be read.

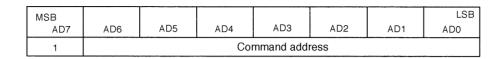

Address and data transfer procedures

The command address is assigned to the lowest seven bits of the address. The most significant bit (AD7) is used to specify write or read. The address can only be written. It cannot be read.

• Writing data

Set the AS/DS pin (pin 43) at low level to specify address input. Specify the address in the lowest seven bits. Set the top bit to 0. Set the STB pin (pin 44) at high level to cause the LSI to read the address. The parallel interface mode can be configured to read input using a choice of three different timings.

- Data read at rising edge of STB pin input.

- Data read at falling edge of STB pin input.

- Data read while STB pin input at high level.

| Pin 52     | Pin 51 | Pin 50          | Pin 49 | Pin 48 | Pin 47 | Pin 46 | Pin 45     |

|------------|--------|-----------------|--------|--------|--------|--------|------------|

| MSB<br>AD7 | AD6    | AD5             | AD4    | AD3    | AD2    | AD1    | LSB<br>AD0 |

| 0          |        | Command address |        |        |        |        |            |

Set the AS/DS pin (pin 43) at high level to specify data input. Set the STB pin (pin 44) at high level to cause the LSI to read the data.

| MSB<br>AD7 | AD6        | AD5    | AD4    | AD3    | AD2    | AD1    | LSB<br>AD0 |

|------------|------------|--------|--------|--------|--------|--------|------------|

|            | Input data |        |        |        |        |        |            |

| Data-7     | Data-6     | Data-5 | Data-4 | Data-3 | Data-2 | Data-1 | Data-0     |

#### • Reading data

Set the AS/DS pin (pin 43) at low level to specify address input. Specify the address in the lowest seven bits. Set the top bit to 1.

Set the AS/DS pin (pin 43) at high level to specify data input. Set the STB pin (pin 44) at high level to cause the LSI to output the data.

| MSB    |        |        |        |         |        |        | LSB    |

|--------|--------|--------|--------|---------|--------|--------|--------|

| AD7    | AD6    | AD5    | AD4    | AD3     | AD2    | AD1    | AD0    |

|        |        |        | Outp   | ut data |        |        |        |

| Data-7 | Data-6 | Data-5 | Data-4 | Data-3  | Data-2 | Data-1 | Data-0 |

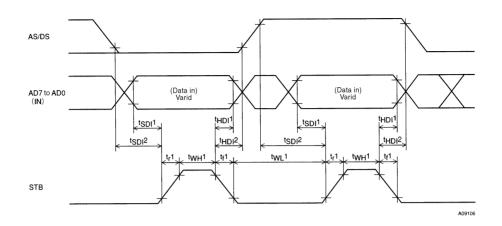

#### Timing Characteristics at $Ta = +25^{\circ}C$ , $DV_{DD}1 = 4.0 V$

| Parameter                    | Symbol             | Conditions                                                                              | Rati | ings | Unit |

|------------------------------|--------------------|-----------------------------------------------------------------------------------------|------|------|------|

| Farameter                    | Symbol             | Conditions                                                                              | min  | max  |      |

| Minimum input pulse width    | tw <sub>H</sub> 1  | STB pin high level pulse width                                                          | 180  | -    | ns   |

|                              | tw <sub>L</sub> 1  | STB pin low level pulse width                                                           | 180  | -    | ns   |

| Strobe rising time           | t <sub>r</sub> 1   | STB pin                                                                                 | -    | 50   | ns   |

| Strobe falling time          | t <sub>f</sub> 1   | STB pin                                                                                 | -    | 50   | ns   |

| Data setup time              | ts <sub>DI</sub> 1 | AD7 to AD0 $\rightarrow$ STB pin                                                        | 25   | -    | ns   |

| Data Setup time              | ts <sub>DI</sub> 2 | $AS/DS \to STB \text{ pin}$                                                             | 25   | -    | ns   |

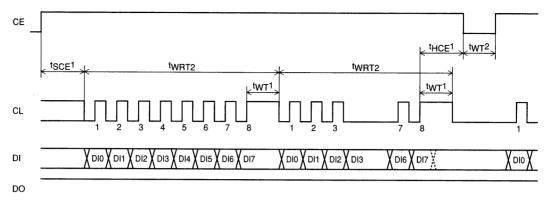

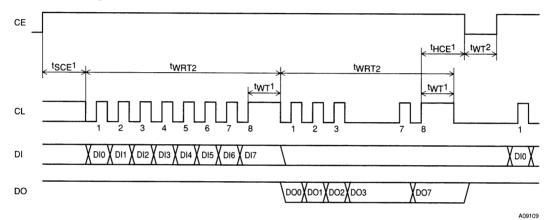

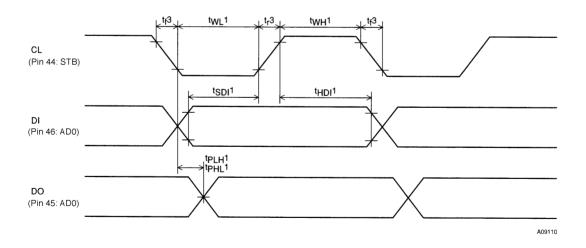

| Data hold time               | th <sub>DI</sub> 1 | $\ensuremath{STB}\xspace \to \ensuremath{AD0}\xspace$ to $\ensuremath{AD7}\xspace$ pins | 25   | -    | ns   |