# Compact Disc Player DSP with Built-in HDCD Decoder

# Overview

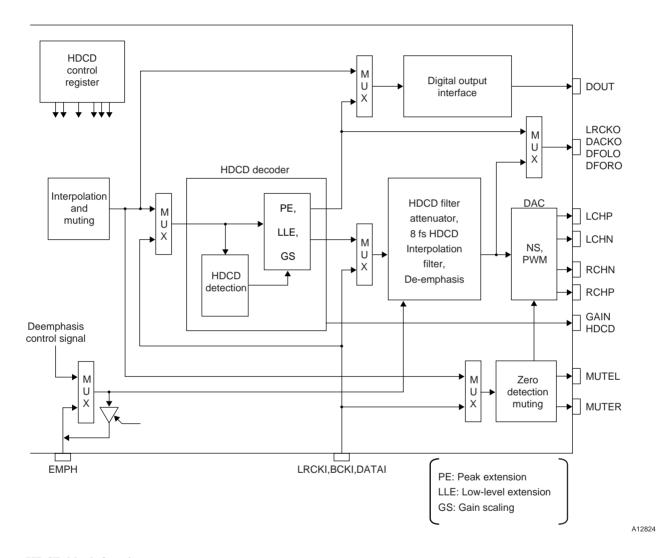

The LC78628E CMOS IC implements signal processing and servo control for compact disc players, laser disc players, CD-V, CD-I, and similar products. It provides functions for demodulation of the EFM signal from the optical pickup, deinterleaving, error detection and correction, and processing servo system commands issued by the system microprocessor. In addition to this basic CD functionality, it also provides HDCD (High Definition Compatible Digital) decoding functions and CD text functions. It also includes a built-in EFM PLL circuit.

#### **Functions**

- Full decoding and playback for discs encoded with the HDCD technique developed by Pacific Microsonics, Inc.

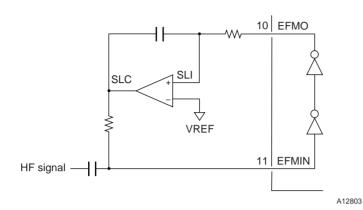

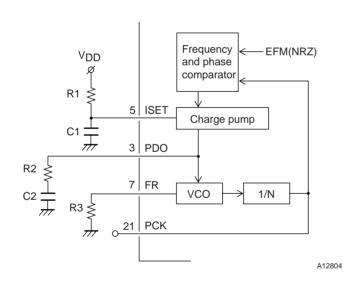

- Slices the high-frequency input signal at an accurate level, converts it into the EFM signal, and generates a PLL clock with an average frequency of 4.3218 MHz performing a phase comparison with an internal VCO.

- Accurately generates a reference clock signal and all necessary internal timings using an external 16.9344-MHz crystal.

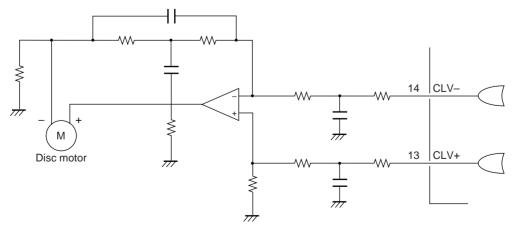

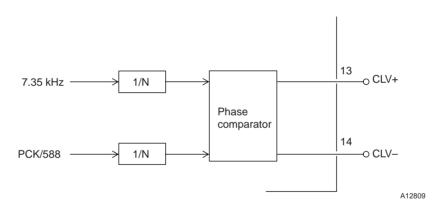

- Controls the disc motor speed using a frame phase difference signal created based on the reproduced clock signal and the reference clock.

- Performs detection, protection, and interpolation for the frame synchronizing signal to assure stable data readout.

- Demodulates the EFM signal, converting it to 8-bit symbol data.

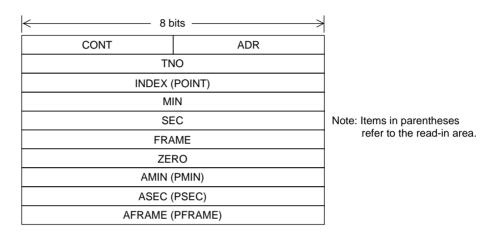

- After applying a CRC check to the subcode Q signal, outputs that data to the control microprocessor using serial data transfer.

Continued on next page.

# **Package Dimensions**

unit: mm

#### 3174-QIP80E

HDCD® (High Definition Compatible Digital®) is a registered trademark of Pacific Microsonics, Inc. in the US and other countries.

A license from Pacific Microsonics, Inc. is required to use this product.

Sanyo Electric Co., Ltd. has acquired license for the use of HDCD technology from Pacific Microsonics, Inc. The following patents apply to the design of this product:

USA: 5479168, 5638074, 5640161, 5808574, 5838274, 5854600, and 5872531.

Australia: 669114

Other patents have also been applied for.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

Continued from preceding page.

- Buffers the demodulated EFM signal data in internal RAM and compensates for ±4 frames of jitter due to disc speed fluctuations.

- Performs unscrambling and deinterleaving by reordering the demodulated EFM signal data to the stipulated order.

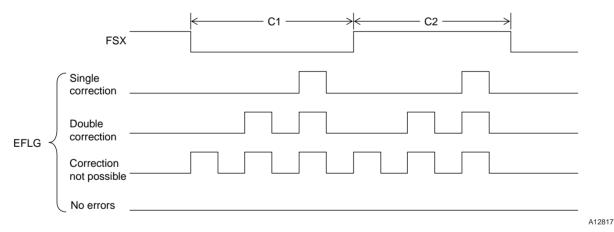

- Performs error detection and correction and flag processing (C1: dual errors, C2: dual errors)

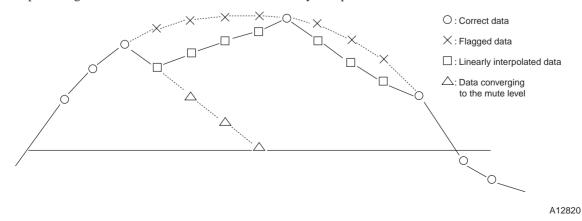

- The C2 flags are set based on the C1 flags and the result of the C2 processing, and the signal is interpolated or muted according to the C2 flags. Four-sample interpolation is adopted in the interpolation circuit. Linear (average value) interpolation is applied if up to three consecutive errors are indicated by the C2 flags, and muting at the zero level is applied if four or more consecutive errors are indicated.

- Performs track jump, focus start, disc motor start/stop, muting on/off, track count, and other operations by executing 8- or 16-bit commands serially input from the system microprocessor.

- Supports high-speed disc access operations based on arbitrary track counts.

- Provides digital outputs.

- Built-in  $\Sigma\Delta$  D/A converter based on a third-order noise shaper.

- · Zero-cross muting

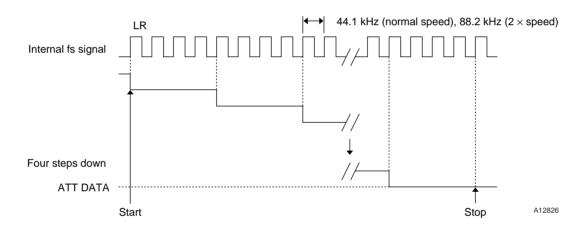

- · Digital attenuator and deemphasis filter

- Support 2 × speed playback

- · Bilingual function

- · Built-in text decoder

- Five general-purpose I/O ports

#### **Features**

- 80-pin OFP package

- Fabricated in a silicon gate CMOS process

- 3.3 and 5 V power supply voltages

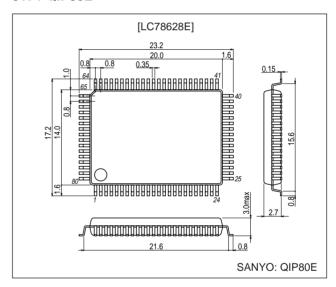

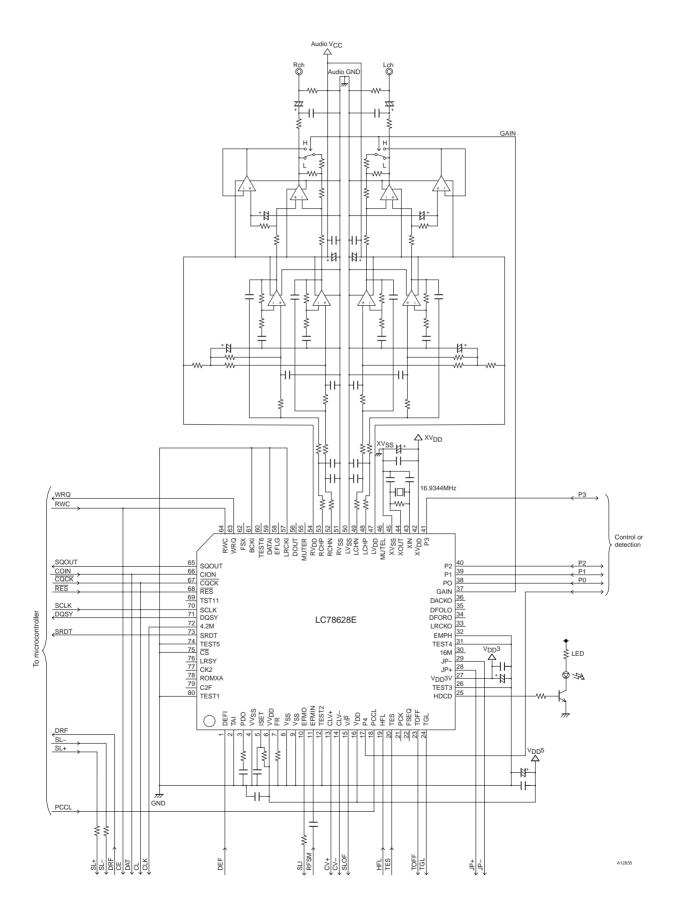

#### **Block Diagram**

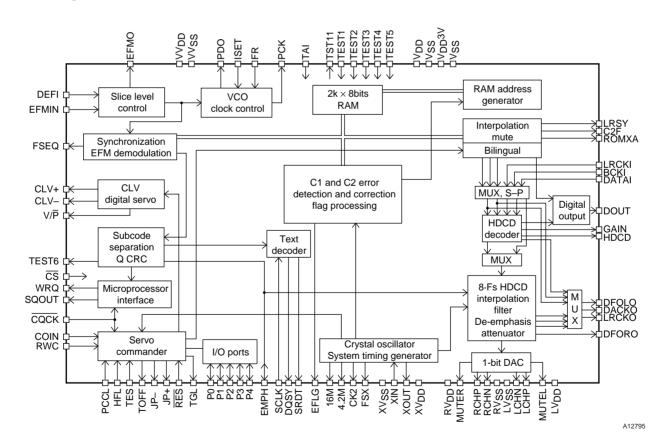

# **Pin Assignment**

# **Specifications**

# Absolute Maximum Ratings at Ta = 25 $^{\circ} C,\,V_{SS}$ = 0 V

| Parameter                   | Symbol                 | Conditions                                               | Ratings                                          | Unit |

|-----------------------------|------------------------|----------------------------------------------------------|--------------------------------------------------|------|

| Maximum aunah waltaga       | V <sub>DD</sub> max1   | $V_{DD}$ , $VV_{DD}$ , $XV_{DD}$ , $LV_{DD}$ , $RV_{DD}$ | V <sub>SS</sub> – 0.3 to V <sub>SS</sub> + 6.0   | V    |

| Maximum supply voltage      | V <sub>DD</sub> max2   | V <sub>DD</sub> 3V                                       | V <sub>SS</sub> – 0.3 to V <sub>SS</sub> + 4.0   | V    |

| lanut voltage               | V <sub>IN</sub> 5 max  |                                                          | V <sub>SS</sub> – 0.3 to V <sub>DD</sub> 1 + 0.3 | V    |

| Input voltage               | V <sub>IN</sub> 3 max  |                                                          | $V_{SS} - 0.3$ to $V_{DD}2 + 0.3$                | V    |

| Output valtage              | V <sub>OUT</sub> 5 max |                                                          | V <sub>SS</sub> – 0.3 to V <sub>DD</sub> 1 + 0.3 | V    |

| Output voltage              | V <sub>OUT</sub> 3 max |                                                          | $V_{SS} - 0.3$ to $V_{DD}2 + 0.3$                | V    |

| Allowable power dissipation | Pd max                 |                                                          | 500                                              | mW   |

| Operating temperature       | Topr                   |                                                          | -20 to +75                                       | °C   |

| Storage temperature         | Tstg                   |                                                          | -40 to +125                                      | °C   |

# Allowable Operating Conditions at Ta = 25 $^{\circ}$ C, $V_{SS}$ = 0 V

| Parameter                | Symbol            | Conditions                                               | Ratings               |     |                       | Unit |

|--------------------------|-------------------|----------------------------------------------------------|-----------------------|-----|-----------------------|------|

| Parameter                | Symbol            | Conditions                                               | min                   | typ | max                   | Unit |

| Supply voltage           | V <sub>DD</sub> 1 | $V_{DD}$ , $VV_{DD}$ , $XV_{DD}$ , $LV_{DD}$ , $RV_{DD}$ | 4.5                   | 5.0 | 5.5                   | V    |

| Supply voltage           | V <sub>DD</sub> 2 | V <sub>DD</sub> 3V                                       | 3.0                   | 3.3 | 3.6                   | V    |

|                          | V <sub>IH</sub> 1 | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$   | 0.8 V <sub>DD</sub> 1 |     | V <sub>DD</sub> 1     | V    |

| High-level input voltage | V <sub>IH</sub> 2 | P0 to P4, TEST1 to TEST5, EMPH                           | 0.7 V <sub>DD</sub> 1 |     | V <sub>DD</sub> 1     | V    |

|                          | V <sub>IH</sub> 3 | EFMIN                                                    | 0.6 V <sub>DD</sub> 1 |     | V <sub>DD</sub> 1     | V    |

|                          | V <sub>IL</sub> 1 | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$   | 0                     |     | 0.2 V <sub>DD</sub> 1 | V    |

| Low-level input voltage  | V <sub>IL</sub> 2 | P0 to P4, TEST1 to TEST5, EMPH                           | 0                     |     | 0.3 V <sub>DD</sub> 1 | V    |

|                          | V <sub>IL</sub> 3 | EFMIN                                                    | 0                     |     | 0.4 V <sub>DD</sub> 1 | V    |

Continued on next page.

# Continued from preceding page.

| Doromotor                         | Symbol            | Conditions                                                |      | Ratings |      |      |  |

|-----------------------------------|-------------------|-----------------------------------------------------------|------|---------|------|------|--|

| Parameter                         | Symbol            |                                                           | min  | typ     | max  | Unit |  |

| Input level                       | V <sub>IN</sub> 1 | EFMIN: Slice level control                                | 1.0  |         |      | Vp-p |  |

| input level                       | V <sub>IN</sub> 2 | XIN: Capacitor coupled input                              | 1.0  |         |      | Vp-p |  |

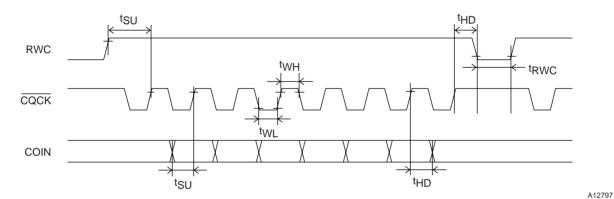

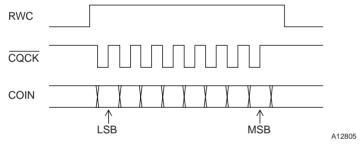

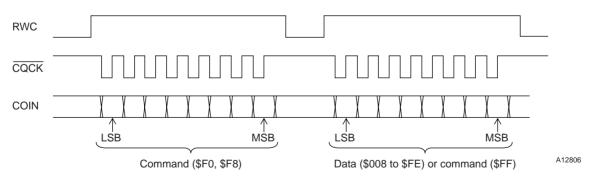

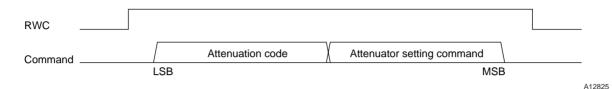

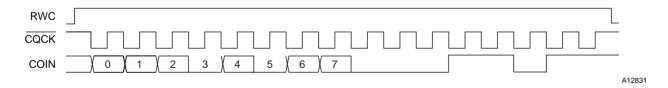

| Data setup time                   | t <sub>SU</sub>   | COIN, RWC, *: See figure 1.                               | 400  |         |      | ns   |  |

| Data hold time                    | t <sub>HD</sub>   | COIN, RWC, *: See figure 1.                               | 400  |         |      | ns   |  |

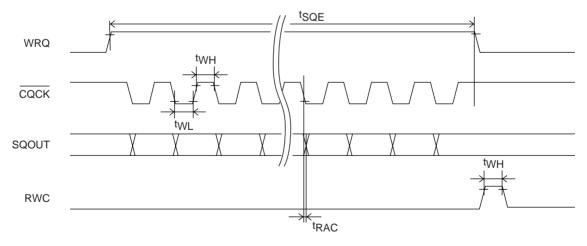

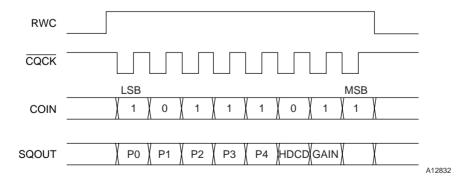

| High-level clock pulse width      | t <sub>WH</sub>   | CQCK, *: See figures 1 and 2.                             | 400  |         |      | ns   |  |

| Low-level clock pulse width       | t <sub>WL</sub>   | CQCK, *: See figures 1 and 2.                             | 400  |         |      | ns   |  |

| Data read access time             | t <sub>RAC</sub>  | SQOUT: See figures 2.                                     | 0    |         | 400  | ns   |  |

| Command output time               | t <sub>RWC</sub>  | RWC, *: See figures 1.                                    | 1000 |         |      | ns   |  |

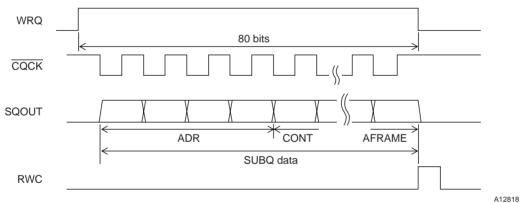

| Subcode Q readout enable time     | t <sub>SQE</sub>  | WRQ, normal speed: See figures 2, RWC = V <sub>IL</sub> 1 |      | 11.2    |      | ms   |  |

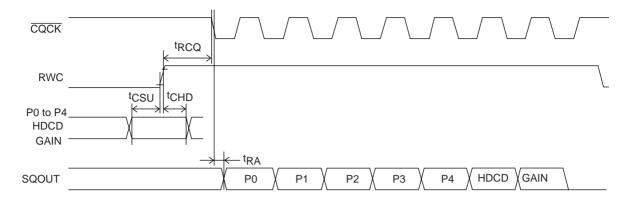

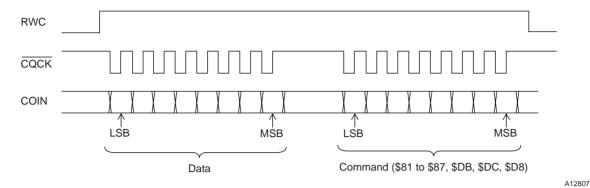

| Port input setup time             | t <sub>CSU</sub>  | P0 to P4, RWC: See figures 3.                             | 400  |         |      | ns   |  |

| Port input hold time              | t <sub>CHD</sub>  | P0 to P4, RWC: See figures 3.                             | 400  |         |      | ns   |  |

| Port input clock setup time       | t <sub>RCQ</sub>  | CQCK, RWC, *: See figures 3.                              | 100  |         |      | ns   |  |

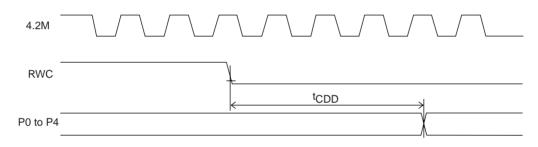

| Port output data delay time       | t <sub>CDD</sub>  | P0 to P4, RWC: See figure 4.                              |      |         | 1200 | ns   |  |

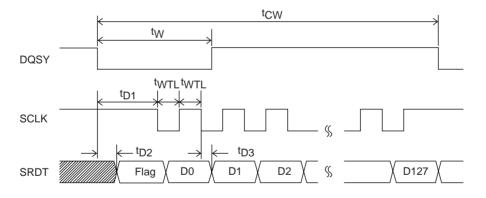

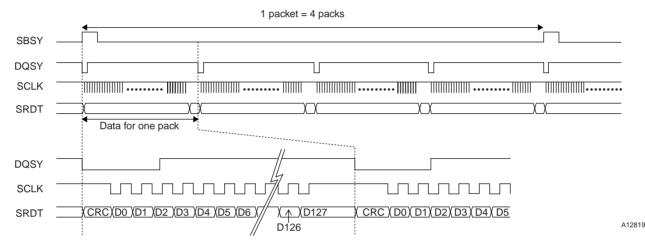

| Text readout period               | t <sub>CW</sub>   | DQSY, normal speed: See figure 5.                         | 1.5  | 3.3     | 3.7  | ms   |  |

| DQSY pulse width                  | t <sub>W</sub>    | DQSY, normal speed: See figure 5.                         | 60   | 136     | 150  | μs   |  |

| SCLK high-level clock pulse width | t <sub>WTH</sub>  | SCLK: See figure 5.                                       | 100  |         |      | ns   |  |

| SCLK low-level clock pulse width  | t <sub>WTL</sub>  | SCLK: See figure 5.                                       | 100  |         |      | ns   |  |

| SCLK clock delay time             | t <sub>D</sub> 1  | SCLK: See figure 5.                                       | 100  |         |      | ns   |  |

| Text data delay time              | t <sub>D</sub> 2  | SRDT: See figure 5.                                       |      |         | 50   | ns   |  |

| rext data delay time              | t <sub>D</sub> 3  | SRDT: See figure 5.                                       |      |         | 50   | ns   |  |

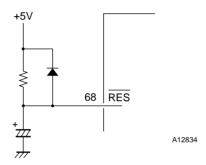

| Reset time                        | t <sub>RES</sub>  | RES                                                       | 400  |         |      | ns   |  |

| Operating frequency range         | f <sub>OP</sub>   | EFMIN                                                     |      |         | 10   | MHz  |  |

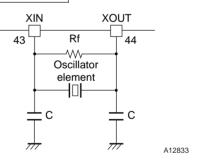

| Crystal oscillator frequency      | f <sub>X</sub>    | X <sub>IN</sub> , X <sub>OUT</sub>                        |      | 16.9344 |      | MHz  |  |

Notes: The same voltage must be applied to all 5 V system power supply pins.

\* When used in conjunction with an ASP that provides a command interface, the stricter ratings of the ASP shall be given priority.

# Electrical Characteristics at $Ta=25^{\circ}C,\,V_{DD}1=5~V,\,V_{DD}2=3.3~V,\,V_{SS}=0~V$

| Parameter                  | Symbol             | Conditions                                                                                                                                                                                                                                |                         | Ratings |     | Unit |

|----------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|-----|------|

| Faiametei                  | Symbol             | Conditions                                                                                                                                                                                                                                | min                     | typ     | max |      |

| Current drain              | I <sub>DD</sub> 1  | V <sub>DD</sub> , VV <sub>DD</sub> , XV <sub>DD</sub> , LV <sub>DD</sub> , RV <sub>DD</sub> : 4.5 V to 5.5 V                                                                                                                              |                         | 17      | 24  | mA   |

| Current drain              | I <sub>DD</sub> 2  | V <sub>DD</sub> 3V: 3.0 V to 3.6 V                                                                                                                                                                                                        |                         | 55      | 85  | mA   |

| High-level input current   | I <sub>IH</sub> 1  | DEFI, EFMIN, SCLK, COIN, RES, HFL, TES, RWC, CQCK, TEST1, LRCKI, BCKI, DATAI, XIN: V <sub>IN</sub> = V <sub>DD</sub> 1                                                                                                                    | -10                     |         | +10 | μΑ   |

|                            | I <sub>IH</sub> 2  | TAI, TEST2 to TEST5, CS, PCCL: V <sub>IN</sub> = V <sub>DD</sub> 1                                                                                                                                                                        | 10                      |         | 200 | μA   |

| Low-level input current    | I <sub>IL</sub>    | DEFI, EFMIN, SCLK, COIN, $\overline{RES}$ , HFL, TES, RWC, $\overline{CQCK}$ , TAI, TEST1 to TEST5, $\overline{CS}$ , PCCL, LRCKI, BCKI, DATAI, XIN: $V_{IN} = 0$ V                                                                       | -10                     |         | +10 | μА   |

|                            | V <sub>OH</sub> 1  | EFMO: I <sub>OH</sub> = -1 mA                                                                                                                                                                                                             | 4                       |         |     | V    |

| High-level output voltage  | V <sub>OH</sub> 2  | CLV+, CLV-, V/ $\overline{P}$ , P0 to P4, PCK, FSEQ, TOFF, TGL, JP+, JP-, 16M, EMPH, LRCKO, DACKO, DFOLO, DFORO, GAIN, MUTEL, MUTER, DOUT, EFLG, TEST6, FSX, WRQ, SQOUT, TST11, DQSY, 4.2M, SRDT, LRSY, CK2, ROMXA, C2F: $I_{OH} = -4$ mA | V <sub>DD</sub> 1 – 2.1 |         |     | V    |

|                            | V <sub>OH</sub> 3  | HDCD: I <sub>OH</sub> = -12 mA                                                                                                                                                                                                            | V <sub>DD</sub> 1 – 2.1 |         |     | V    |

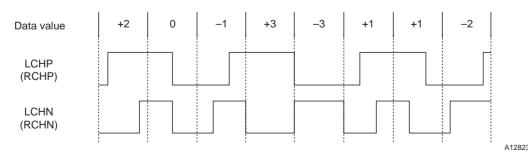

|                            | V <sub>OH</sub> 4  | LCHP, LCHN, RCHP, RCHN: I <sub>OH</sub> = -1 mA                                                                                                                                                                                           | 3.0                     |         | 4.5 | V    |

|                            | V <sub>OL</sub> 1  | EFMO: I <sub>OL</sub> = 1 mA                                                                                                                                                                                                              |                         |         | 1   | V    |

| Low-level output voltage   | V <sub>OL</sub> 2  | CLV+, CLV-, V/P, P0 to P4, PCK, FSEQ, TOFF, TGL, JP+, JP-, 16M, EMPH, LRCKO, DACKO, DFOLO, DFORO, GAIN, MUTEL, MUTER, DOUT, EFLG, TEST6, FSX, WRQ, SQOUT, TST11, DQSY, 4.2M, SRDT, LRSY, CK2, ROMXA, C2F: I <sub>OL</sub> = 4 mA          |                         |         | 0.4 | V    |

|                            | V <sub>OL</sub> 3  | HDCD: I <sub>OL</sub> = 12 mA                                                                                                                                                                                                             |                         |         | 0.4 | V    |

|                            | V <sub>OL</sub> 4  | LCHP, LCHN, RCHP, RCHN: I <sub>OH</sub> = 1 mA                                                                                                                                                                                            | 0.5                     |         | 2.0 | V    |

| Output off leakage current | I <sub>OFF</sub> 1 | PDO, CLV+, CLV-, JP+, JP-, P0 to P4, EMPH, SQOUT, EFMO: In the high-impedance output state                                                                                                                                                | -10                     |         | +10 | μA   |

| Charge pump output current | I <sub>PDOH</sub>  | PDO: $R_{ISET} = 68 \text{ k}\Omega$                                                                                                                                                                                                      | 64                      | 80      | 96  | μA   |

| Charge pump output current | I <sub>PDOL</sub>  | PDO: $R_{ISET} = 68 \text{ k}\Omega$                                                                                                                                                                                                      | -96                     | -80     | -64 | μΑ   |

D/A Converter Block Analog Characteristics at  $Ta=25^{\circ}C$ ,  $V_{DD}=LV_{DD}=RV_{DD}=XV_{DD}=VV_{DD}=5$  V,  $V_{DD}3V=3.3$  V,  $V_{SS}=LV_{SS}=RV_{SS}=XV_{SS}=VV_{SS}=0$  V.

| Parameter                 | Symbol   | Ratings Ratings                                                                                                          |     |       | Unit  |        |

|---------------------------|----------|--------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|--------|

| Falametei                 | Syllibol | Conditions                                                                                                               | min | typ   | max   | Office |

| Total harmonic distortion | THD + N  | LCHP, LCHN, RCHP RCHN;<br>1 kHz: 0 dB data input<br>With the 20 kHz low-pass filter (internal AD725D) used.              |     | 0.009 | 0.012 | %      |

| Dynamic range             | DR       | LCHP, LCHN, RCHP, RCHN;<br>1 kHz: -60 dB data input<br>With the 20 kHz low-pass and A filters (internal AD725D)<br>used. | 83  | 86    |       | dB     |

| Signal-to-noise ratio     | S/N      | LCHP, LCHN, RCHP, RCHN;<br>1 kHz: 0 dB data input<br>With the 20 kHz low-pass and A filters (internal AD725D)<br>used.   | 98  | 103   |       | dB     |

| Crosstalk (separation)    | СТ       | LCHP, LCHN, RCHP, RCHN;<br>1 kHz: 0 dB data input<br>With the 20 kHz low-pass filter (internal AD725D) used.             | 96  | 98    |       | dB     |

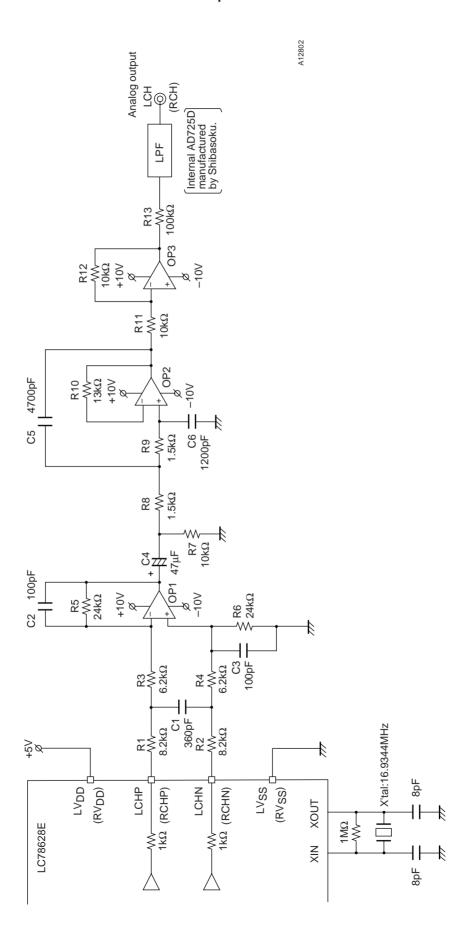

Note: Measured in the normal speed playback of the Sanyo 1-bit D/A converter reference circuit.

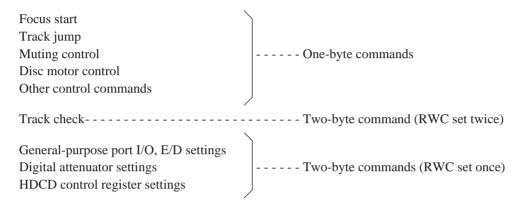

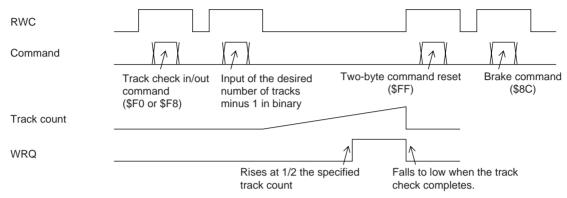

Figure 1 Command Input

Figure 2 Subcode Q Output

A12798

Figure 3 General-Purpose Port Input Timing

A12799

Figure 4 General-Purpose Port Output Timing

A12800

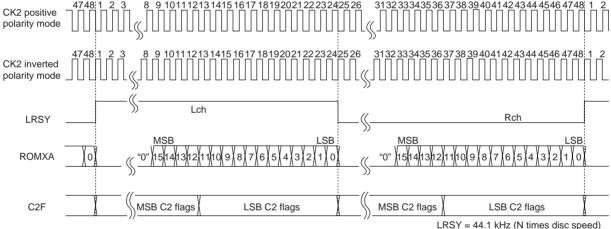

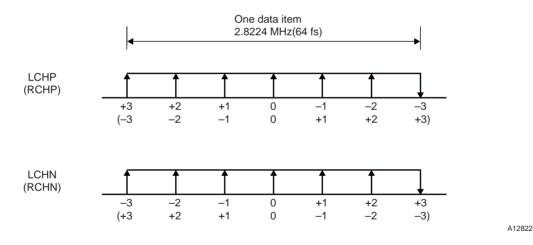

Figure 5 Text Data Output Timing

A12801

# Reference Circuit for the 1-Bit D/A Converter Output Block

# **Pin Functions**

| 1 DEFI 1 Defect detection signal (DEF) input (Must be connected to 9 V if unused.) 2 TAI 1 I Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin No. | Pin                | I/O |                                                                                                                                                                                                                                                                                                | Function                                                                                                                                                                                                                 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Test                |         |                    | 1   | Defect detection sig                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                          |  |  |

| Section   PDO   Co   Command   Com             |         |                    | I   |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                          |  |  |

| Internal VCO ground. This pin must be connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                    | 0   | -                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |  |  |

| Fig.   Section   Fig.   Section   Fig.   Section   Fig.   Section   Section   Fig.   Section   Se             |         |                    | _   | -                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |  |  |

| Internal VCO power supply: 5 V system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                    | AI  | PLL-related pins                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                          |  |  |

| FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6       |                    | _   |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                          |  |  |

| 8 Vss — Ground. This pin must be connected to 0 V. 9 Vss — Ground. This pin must be connected to 0 V. 11 EFMN 1 12 TEST2 I Test input. A pull-down resistor is built in. This pin must be connected to 0 V. 13 CLV* O Spinde control Service outputs. ELV* outputs a high level for accelerate, and CLV*- outputs a high level for decelerate. 14 CLV* O Spinde control service outputs. CLV* outputs a high level for accelerate, and CLV*- outputs a high level for accelerate, and CLV*- outputs a high level for decelerate. 15 Vp O Spinde control service outputs. CLV* outputs a high level for accelerate, and CLV*- outputs a high level for acceleration cutput. Outputs accelerate to the CLV*- outputs a high level for acceleration cutput. Outputs accelerate to be set to input mode and connected to the 0 V level, or be set to cutput acceleration cutput. Outputs acceleration during a lamp towards in acceleration during a lamp towards outer tracks, or deceleration during a lamp towards outer tracks, and acceleration during a lamp towards outer tr           |         |                    | AI  | -                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |  |  |

| 9 V <sub>SS</sub> 10 EFMO 0 11 EFMON 1 12 TESTZ 1 Test input. A pull-down resistor is built in. This pin must be connected to 0 V. 12 TESTZ 1 Test input. A pull-down resistor is built in. This pin must be connected to 0 V. 13 CLV 0 Spindle control expression is built in. This pin must be connected to 0 V. 14 CLV 0 A command is provided to set these pins to three-state output. 15 V/P 0 A Atlormatic rough servo/phase control switching monitor output. A high level indicates rough servo and a low level indicates phase control. 16 Vop - 5 V system power supply 17 P4 U0 General-purpose I/O port. If unused, this port must either be set to input mode and connected to the 0 V level, or be set to output mode and left open. 18 PCCL I High: Only general-purpose I/O port commands can be used for control 19 WFL I Tracking or signal input. This is a Schmitt input. 19 PCL I Tracking or or signal input. This is a Schmitt input. 19 PCL SPACE SP | 8       |                    |     | Ground. This pin m                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                          |  |  |

| 10   EFMON   0   11   EFMON   1   EFMON   1   EFM signal couput   EFM signal poutput   EFM signal input                |         |                    | _   |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                          |  |  |

| EFMIN   1   Since level control   EFM signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                    | 0   |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                          |  |  |

| TEST2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11      |                    | ı   | Slice level control                                                                                                                                                                                                                                                                            | EFM signal input                                                                                                                                                                                                         |  |  |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | TEST2              | ı   | Test input. A pull-do                                                                                                                                                                                                                                                                          | •                                                                                                                                                                                                                        |  |  |

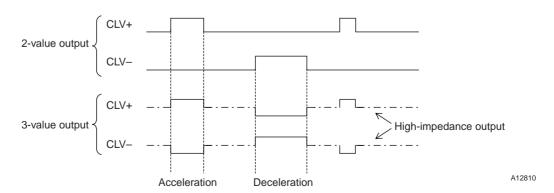

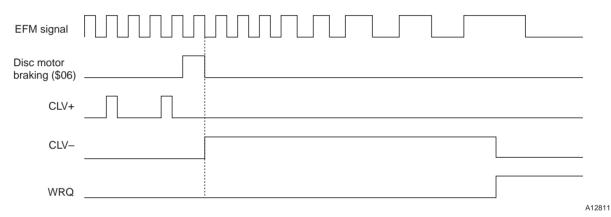

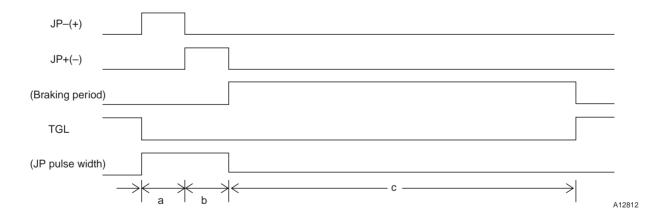

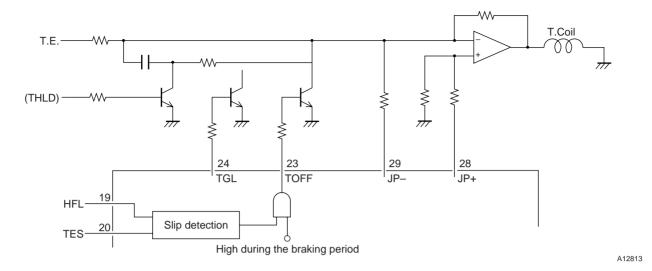

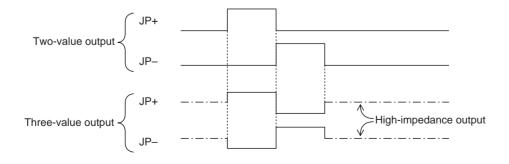

| 14 CLV O A command is provided to set these pins to three-state output.  15 ViP O Automatic rough servolphase control switching monitor output. A high level indicates rough servo and a low level indicates phase control.  16 Vip O — 5 V system power supply  17 P4 I/O General-purpose I/O port. If unused, this port must either be set to input mode and connected to the 0 V level, or be set to output mode and left open.  18 PCCL General-purpose I/O port. If unused, this port must either be set to input mode and connected to the 0 V level, or be set to output mode and left open.  19 HFL I Track decetion signal input. This is a Schmitt input.  20 TES II Tracking error signal input. This is a Schmitt input.  21 PCK O EFM data reproduction clock monitor output. Outputs 4.3218 MHz when the phase is locked.  22 Synchronizing signal autput.  23 TOFF O Tracking off state output  24 TGL O Tracking gain switching output. A low level output raises the gain.  25 HDCD O HDCD identification output. High: An HDCD disc is being played, Low: A normal disc is being played.  26 TEST3 I Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  27 Vop3V — 3 V system power supply  28 JP- O JFack jump outputs.  39 JP- O JFack jump outputs.  30 16M O 163944 MHz clock output in this pin in use to connected to 0 V.  29 JP- O JFack jump outputs.  30 16M O 163944 MHz clock output in this pin in use to connected to 0 V.  29 JP- O JFack jump outputs.  30 16M O 163944 MHz clock output in this pin in use to connected to 0 V.  31 Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  32 In high level indicates either acceleration during a jump towards where tracks, or deceleration during a jump towards inner tracks.  39 JP- O JFack jump outputs.  30 16M O 163944 MHz clock output in this pin in sused for deemphasis disc. When external data is applied to the HDCD filter engine output in the soutput during playback of a deemphasis disc. When external data is applied to the HDCD filter engine output ir           |         |                    | 0   |                                                                                                                                                                                                                                                                                                | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                    |  |  |

| No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                    |     |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                          |  |  |

| General-purpose I/O port. If unused, this port must either be set to input mode and connected to the 0 V level, or be set to output mode and left open.    General-purpose I/O command identification. A pull-down resistor is built in. High: Only general-purpose I/O command identification. A pull-down resistor is built in. High: Only general-purpose I/O port commands can be used for control Low. All commands can be used for determined the used for demands can be used for determined the control Low. All commands can be used for design and can be used for design and can be used for design and can be used for design played. Control Low. All control Low. All commands can be used for design and detected from the EFM signal and the internal played control control coupt. All colors output from the Hot. Did control              |         | _                  |     |                                                                                                                                                                                                                                                                                                | rvo/phase control switching monitor output. A high level indicates rough servo and a low level indicates                                                                                                                 |  |  |

| P4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16      | V <sub>DD</sub>    | _   | 5 V system power s                                                                                                                                                                                                                                                                             | upply                                                                                                                                                                                                                    |  |  |

| High: Only general-purpose I/O port commands can be used for control Low. All commands can be used for control Low. All commands can be used for control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17      |                    | I/O |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                          |  |  |

| Test I Tracking error signal input. This is a Schmitt input.  PCK O EFM data reproduction clock monitor output. Outputs 4.3218 MHz when the phase is locked.  Synchronizing signal output.  Synchronizing signal output.  Outputs a high level if the synchronizing signal detected from the EFM signal and the internally generated synchronizing signal match.  ToFF O Tracking off state output  TGL O Tracking gain switching output. A low level output raises the gain.  HDCD O HDCD identification output. High: An HDCD disc is being played, Low: A normal disc is being played.  Test T3 I Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  Track jump outputs.  JP+ O Track jump outputs.  JP-: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks. Or a command is provided to set these pins to three-state output.  Test Table V 1 Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  EMPH ID Co Acommand is provided to set these pins to three-state output.  EMPH ID Co 161e regine, this pin is used for deemphasis switching. After a reset, this pin goes to monitor output mode in the high-impedance state.  EMPH ID Deemphasis monitor output word clock (8is) or L/R clock output from the HDCD decoder (1fs).  DEOCH O HDCD filter engine output word clock (8is) or L/R clock output from the HDCD decoder (1fs).  Analog output stage gain indicator in internal gain scaling is performed internally. Normal clicss are –6 dB. When external gain scaling is used, peak extend should be turned on when this pin is high, and should be turned off when this output is output indicated in internal gain scaling mode, this pin always outputs a high level (unused). Gain scaling is performed internally. Normal clicss are –6 dB. When external gain scaling is used, peak extend should be turned on when this pin is high, and should be turned off when this output mode and left open.             | 18      | PCCL               | I   | High: Only general-                                                                                                                                                                                                                                                                            | purpose I/O port commands can be used for control                                                                                                                                                                        |  |  |

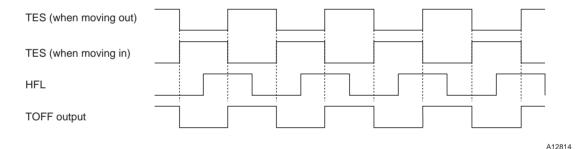

| PCK O EFM data reproduction clock monitor output. Outputs 4.3218 MHz when the phase is locked.  Synchronizing signal output. Outputs a high level if the synchronizing signal detected from the EFM signal and the internally generated synchronizing signal and the internal signal and the internal signal and the internal signal match.  Tracking off state output  Tracking gain switching output. A low level output raises the gain.  HDCD O HDCD identification output. High: An HDCD disc is being played, Low: A normal disc is being played.  Tracking pain switching output. A low level output raises the gain.  Tracking pain switching output. A low level output raises the gain.  Tracking pain switching output. A low level output raises the gain.  Tracking output.  Track jump outputs.  JP+ A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP+ A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP+ A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP+ A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP+ A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP+ A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP+ A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  LECKO I E-BMH I Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  Deemphasis monitor output/input. A high level is output during playback of a deemphasis disc. When external d           | 19      | HFL                | ı   | Track detection sign                                                                                                                                                                                                                                                                           | nal input. This is a Schmitt input.                                                                                                                                                                                      |  |  |

| FSEQ Synchronizing signal output. Outputs a high level if the synchronizing signal detected from the EFM signal and the internally generated synchronizing signal match.  Toff O Tracking off state output  Tracking gain switching output. A low level output raises the gain.  Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  Track input poutputs.  JP+ O JP+: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  Test 4                                                                                                                                                                                                                                                            | 20      | TES                | ı   | Tracking error signa                                                                                                                                                                                                                                                                           | al input. This is a Schmitt input.                                                                                                                                                                                       |  |  |

| PSEQ O Outputs a high level if the synchronizing signal detected from the EFM signal and the internally generated synchronizing signal match.  Tracking off state output  Tracking off state output  Tracking off state output  Tracking off state output. A low level output raises the gain.  Tracking off state output. A low level output raises the gain.  Tracking gain switching output. A low level output raises the gain.  Tracking output. A pull-down resistor is built in. This pin must be connected to 0 V.  Track jump outputs.  JP+ A ligh level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  JP+ A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  Track jump outputs.  JP+: A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP+: A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP+: A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP+: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP+: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP+: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP+: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a            | 21      | PCK                | 0   | EFM data reproduc                                                                                                                                                                                                                                                                              | tion clock monitor output. Outputs 4.3218 MHz when the phase is locked.                                                                                                                                                  |  |  |

| TGL O Tracking gain switching output. A low level output raises the gain.  1 Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  1 Tack jump outputs.  2 JP+ O JP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  2 JP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  3 JP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  3 JP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  3 JP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  3 JP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  3 LP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  4 LP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  4 LP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  4 LP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  4 LP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  4 LP- A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  4 LP- A light level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards inner tracks.  4 LP- A light level indicates either acceleration during a jump            | 22      | FSEQ               | 0   | Outputs a high leve                                                                                                                                                                                                                                                                            | ·                                                                                                                                                                                                                        |  |  |

| HDCD O HDCD identification output. High: An HDCD disc is being played, Low: A normal disc is being played.  TEST3 I Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  Track jump outputs.  JP+ O JP+: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  JP-: A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards inner tracks, or deceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks, or deceleration during a jump towards inner tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks.  JP-: A high level indicates either acceleration during a jump towards outer tracks.  JP-: A high level indicate           | 23      | TOFF               | 0   | Tracking off state or                                                                                                                                                                                                                                                                          | utput                                                                                                                                                                                                                    |  |  |

| TEST3 I Test input. A pull-down resistor is built in. This pin must be connected to 0 V.  27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24      | TGL                | 0   | Tracking gain switcl                                                                                                                                                                                                                                                                           | ning output. A low level output raises the gain.                                                                                                                                                                         |  |  |

| Vp-3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25      | HDCD               | 0   | HDCD identification                                                                                                                                                                                                                                                                            | output. High: An HDCD disc is being played, Low: A normal disc is being played.                                                                                                                                          |  |  |