CMOS IC

LC86P5420

# 8-Bit Single Chip Microcontroller with the One-Time Programmable PROM

## Preliminary

## Overview

The LC86P5420 is a CMOS 8-bit single chip microcontroller with one-time PROM for the LC865500 / LC865400 series.

This microcontroller has the function and the pin description of the LC865500 / LC865400 series mask ROM version, and the 20K-byte PROM.

### Features

(1) Option switching by PROM data

The option function of the LC865400 series can be specified by the PROM data.

The LC86P5420 can be checked the functions of the trial pieces using the mass production board.

(2) Internal one-time PROM capacity : 20736 bytes

(3) Internal RAM capacity

: 512 bytes

| Mask ROM version | PROM capacity | RAM capacity |

|------------------|---------------|--------------|

| LC865520         | 20480 bytes   | 512 bytes    |

| LC865516         | 16384 bytes   | 512 bytes    |

| LC865512         | 12288 bytes   | 512 bytes    |

| LC865508         | 8192 bytes    | 512 bytes    |

| LC865504         | 4096 bytes    | 512 bytes    |

| LC865412         | 12288 bytes   | 224 bytes    |

| LC865408         | 8192 bytes    | 224 bytes    |

| LC865404         | 4096 bytes    | 224 bytes    |

- (4) Operating supply voltage

(5) Instruction cycle time

: 4.5V to 6.0V

: 1.0µs to 366µs

- (6) Operating temperature  $: -30^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$

(b) Operating temperature : -50 C to  $\pm/0 \text{ C}$

(7) The pin and the package compatible with the LC865400 series mask ROM devices

- (8) Applicable mask ROM version : LC3

- : LC865520 / LC865516 / LC865512 / LC865508 / LC865504 LC865412 / LC865408 / LC865404

(9) Factory shipment

- : DIP42S, QFP48E

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

## Notice for use

The LC86P5420 is provided for the first release and small shipping of the LC865500 / LC865400 series. At using, take notice of the followings.

(1) A point of difference the LC86P5420 and the LC865500 / LC865400 series

| Item                                    | LC86P5420                                                                                                                                                           | LC865520 / 16 / 12 / 08 / 04 LC865412 / 08 / 04                                                                       |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Operation after reset<br>releasing      | The option is specified by degrees<br>until 3ms after going to a 'H' level<br>to the reset terminal. The program<br>is executed from 00H of the<br>program counter. | The program is executed from 00H of the program counter immediately after going to a 'H' level to the reset terminal. |

| Operating supply<br>voltage range (VDD) | 4.5V to 6.0V                                                                                                                                                        | 2.5V to 6.0V                                                                                                          |

| Power dissipation                       | Refer to 'electrical characteristics' of                                                                                                                            | n the semiconductor news.                                                                                             |

The LC86P5420 functions same as the followings while resetting ; LC865520 / 16 / 12 / 08 / 04, LC865412 / 08 / 04.

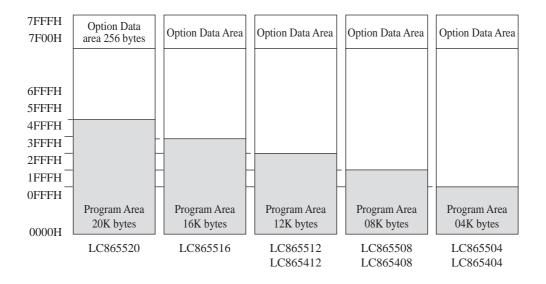

The LC86P5420 uses 256 bytes that is addressed on 7F00H to 7FFFH in the program memory as the option configulation data area.

#### •A kind of the option corresopnding of the LC86P5420

| A kind of option       | Pins, Circuits | Contents of the option                  |

|------------------------|----------------|-----------------------------------------|

| Input / output form of | Port 0         | 1. N-channel open drain output          |

| input / output ports   |                | 2. CMOS output *1                       |

|                        |                | 1. Pull-up MOS Tr. provided             |

|                        |                | 2. Pull-up MOS Tr. not provided *2      |

|                        | Port 1         | 1. Input : Programmable pull-up MOS Tr. |

|                        |                | Output : N-channel open drain           |

|                        |                | 2. Input : Programmable pull-up MOS Tr. |

|                        | *1             | Output : CMOS                           |

|                        | Port 3         | 1. Input : No Programmable pull-up      |

|                        |                | MOS Tr.                                 |

|                        |                | Output : N-channel open drain           |

|                        |                | 2. Input : Programmable pull-up MOS Tr. |

|                        | *1             | Output : CMOS                           |

\*1) Specified in bit

\*2) Specified in nibble unit. Pull-up MOS Tr. is not provided in N-channel open drain output port.

(2) Option

The option data is created by the option specified program "SU86K.EXE". The created option data is linked to the program area by the linkage loader "L86K.EXE".

#### (3) ROM space

The LC86P5420 and LC865500 / LC865400 series use 256 bytes that is addressed on 7F00H to 7FFFH in the program memory as the option specified data area. These program memory capacity are 20480 bytes that is addressed on 0000H to 4FFFH.

(4) Ordering information

- When ordering the identical mask ROM and PROM devices simultaneously. Provide an EPROM containing the target memory contents together with the separate order forms for each of the mask ROM and PROM versions.

- 2. When ordering a PROM device. Provide an EPROM containing the target memory contents together with an order form.

## How to use

(1) Create a programming data for LC86P5420

Programming data for EPROM of the LC86P5420 is required.

Debugged evaluation file (EVA file) must be converted to an INTEL-HEX formatted file (HEX file) with file converter program, EVA2HEX.EXE. The HEX file is used as the programming data for the LC86P5420.

#### (2) How to program for the EPROM

The LC86P5420 can be programmed by the EPROM programmer with attachment ; W86EP5420D, W86EP5420Q.

• Recommended EPROM programmer

| Productor          | EPROM programmer    |

|--------------------|---------------------|

| Advantest          | R4945, R4944, R4943 |

| Andou              | AF-9704             |

| AVAL               | PKW-1100, PKW-3000  |

| Minato electronics | MODEL1890A          |

• "27512 (Vpp=12.5V) Intel high speed programming" mode available. The address must be set to "0000H to 7FFFH" and a jumper (DASEC) must be set to 'OFF' at programming.

#### (3) How to use the data security function

"Data security" is the disabled function to read the data of the EPROM.

The following is the process in order to execute the data security.

- 1. Set 'ON' the jumper of attachment.

- 2. Program again. Then the EPROM programmer displays the error. The error means normally activity of the data security. It is not a trouble of the EPROM programmer or the LSI.

#### Notes

- Data security is not executed when the data of all address have 'FFH' at the sequence 2 above.

- The programming by a sequential operation "BLANK=>PROGRAM=>VERIFY" cannot be executed data security at the sequence 2 above.

Data security

• Set 'OFF' to the jumper after executing the data security.

Data security

Not data security

W86EP5420D

Not data security

W86EP5420Q

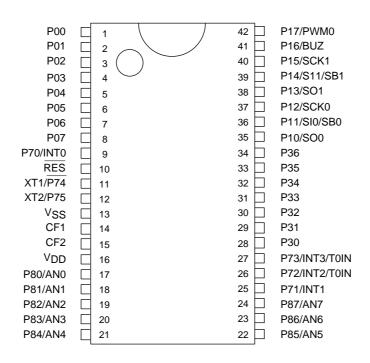

## Pin Assignment

•DIP42S

ILC00019

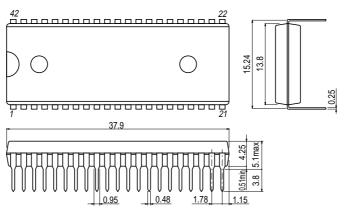

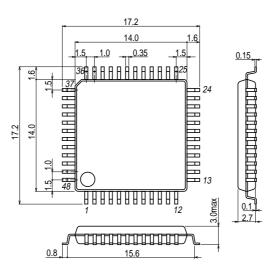

## **Package Dimension**

(unit : mm) 3025B

SANYO : DIP-42S(600mil)

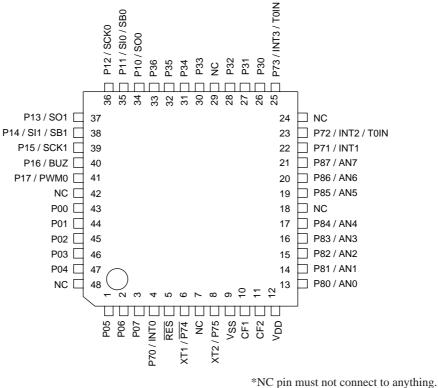

## **Pin Assignment**

•QFP48E

ILC00020

**Package Dimension**

(unit : mm) 3156

SANYO : QIP-48E

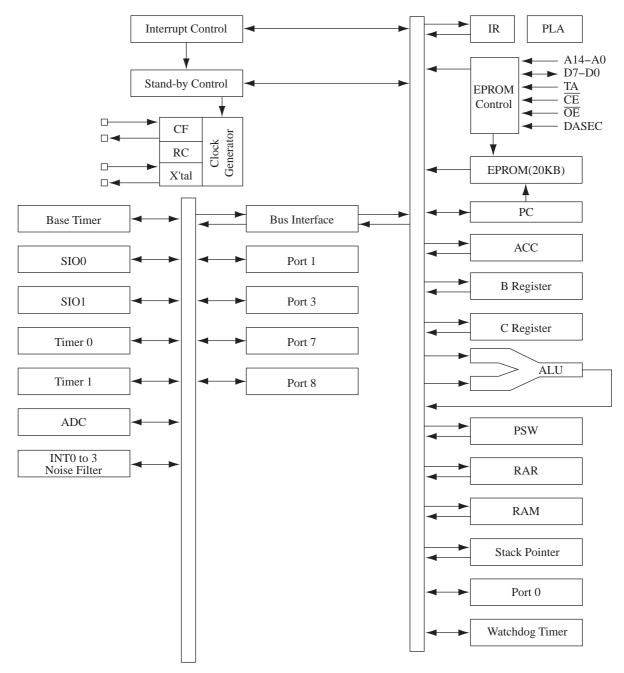

# System Block Diagram

## **Pin Description**

| Pin name    | I/O | Function description                   | Option                       | PROM mode                    |

|-------------|-----|----------------------------------------|------------------------------|------------------------------|

| VSS         |     | Power pin (-)                          |                              |                              |

| VDD         |     | Power pin (+)                          |                              |                              |

| PORT0       | I/O | •8-bit input / output port             | Pull-up resistor :           |                              |

| P00 - P07   |     | Input / output in nibble units         | Provided / Not provided      |                              |

|             |     | •Input for port 0 interrupt            | (specify every 4-bit)        |                              |

|             |     |                                        | Output form :                |                              |

|             |     | •15V withstand at N-channel open       | CMOS / N-channel open drain  |                              |

|             |     | drain output                           | (specify in bit)             |                              |

| PORT1       | I/O |                                        | •Output form :               | Data line                    |

| P10 - P17   |     | Input / output can be specified        | -                            | D0 to D7                     |

|             |     | in bit unit.                           | (specify in bit)             |                              |

|             |     | •Other pin functions                   |                              |                              |

|             |     | P10 SIO0 data output                   |                              |                              |

|             |     | P11 SIO0 data input /                  |                              |                              |

|             |     | bus input / output                     |                              |                              |

|             |     | P12 SIO0 clock input / output          |                              |                              |

|             |     | P13 SIO1 data output                   |                              |                              |

|             |     | P14 SIO1 data input /                  |                              |                              |

|             |     | bus input / output                     |                              |                              |

|             |     | P15 SIO1 clock input / output          |                              |                              |

|             |     | P16 Buzzer output                      |                              |                              |

|             |     | P17 Timer1 (PWM0) output               |                              |                              |

| PORT3       | I/O |                                        | Pull-up resistor :           |                              |

| P30 - P36   | 1,0 |                                        | Provided / Not provided      |                              |

| 150 150     |     |                                        | Output form :                |                              |

|             |     | drain output                           | CMOS / N-channel open drain  |                              |

| PORT7       |     | •4-bit input / output port             | ettios / it enamer open dram |                              |

|             |     | Input / output in bit unit             |                              |                              |

|             |     | •2-bit input port                      |                              |                              |

|             |     | •Other pin functions                   |                              |                              |

| P70 - P73   | I/O |                                        |                              | PROM control                 |

| 170-175     | 170 | input / N-channel Tr. output for       |                              | signals                      |

|             |     | watchdog timer                         |                              | •DASEC (*1)                  |

| P74, P75    | Ι   | P71 : INT1 input / HOLD release input  |                              | $\bullet \overline{OE}$ (*2) |

| 1 /4, 1 / 5 | 1   | P72 : INT2 input / timer 0 event input |                              | • $\overline{CE}$ (*3)       |

|             |     | P73 : INT3 input with noise filter /   |                              | CL(3)                        |

|             |     | timer 0 event input                    |                              |                              |

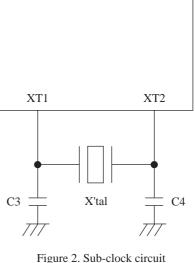

|             |     | P74 : Input pin XT1 for 32.768kHz      |                              |                              |

|             |     | crystal oscillation                    |                              |                              |

|             |     | P75 : Output pin XT2 for 32.768kHz     |                              |                              |

|             |     | crystal oscillation                    |                              |                              |

|             |     | -                                      |                              |                              |

|             |     | •Interrupt received form,              |                              |                              |

|             |     | vector address                         |                              |                              |

|             |     |                                        | low vector                   |                              |

|             |     |                                        | evel                         |                              |

|             |     | falling                                |                              |                              |

|             |     |                                        | hable 03H                    |                              |

|             |     | INT1 enable enable disable enable en   |                              |                              |

|             |     | INT2 enable enable enable disable dis  |                              |                              |

|             |     | INT3 enable enable enable disable dis  | sable 1BH                    |                              |

| Pin name  | I/O | Function description                    | Option | PROM mode |

|-----------|-----|-----------------------------------------|--------|-----------|

| PORT8     |     |                                         |        |           |

| P80 - P83 | Ι   | •4-bit input port                       |        | TA (*4)   |

| P84 - P87 | I/O | •4-bit input / output port              |        |           |

|           |     | Input / output can be specified in      |        |           |

|           |     | bit unit                                |        |           |

|           |     | •Other function                         |        |           |

|           |     | AD input port (AN7 to AN0)              |        |           |

| RES       | Ι   | Reset pin                               |        |           |

| XT1 / P74 | Ι   | •Input pin for the 32.768kHz cyrstal    |        |           |

|           |     | oscillation                             |        |           |

|           |     | •Other function                         |        |           |

|           |     | XT1 : Input port P74                    |        |           |

|           |     | In case of non use, connect to $V_{DD}$ |        |           |

| XT2 / P75 | 0   | •Output pin for the 32.768kHz           |        |           |

|           |     | crystal oscillation                     |        |           |

|           |     | •Other function                         |        |           |

|           |     | XT2 : Input port P75                    |        |           |

|           |     | In case of non use, connect to VDD      |        |           |

|           |     | at using as port or unconnect at using  |        |           |

|           |     | as oscillation.                         |        |           |

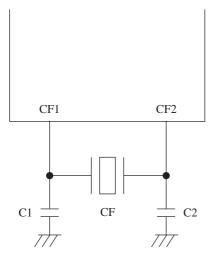

| CF1       | Ι   | Input pin for the ceramic resonator     |        |           |

|           |     | oscillation                             |        |           |

| CF2       | 0   | Output pin for the ceramic resonator    |        |           |

|           |     | oscillation                             |        |           |

■ All of port options except the pull-up resistor option of Port 0 can be specified in a bit unit.

\*1 Memory select input for data security

- \*2 Output enable input

- \*3 Chip enable input

- \*4 TA $\rightarrow$  PROM control signal input

| Para     | meter   | Symbol           | Pins                  | Conditions                 | <b></b> |      | Ratings |         | unit |

|----------|---------|------------------|-----------------------|----------------------------|---------|------|---------|---------|------|

|          |         | -                |                       |                            | VDD [V] | min. | typ.    | max.    |      |

|          | voltage | VDDMAX           |                       | V <sub>DD</sub>            |         | -0.3 |         | +7.0    | V    |

| Input v  | oltage  | VI(1)            | •Ports 74, 75         |                            |         | -0.3 |         | VDD+0.3 |      |

|          |         |                  | •Ports 80, 81, 82, 83 |                            |         |      |         |         |      |

|          |         |                  | •RES                  |                            |         |      |         |         |      |

| Input /  | -       | VIO(1)           | •Port 1               |                            |         | -0.3 |         | VDD+0.3 |      |

| voltage  |         |                  | •Ports 70, 71, 72, 73 |                            |         |      |         |         |      |

|          |         |                  | •Ports 84, 85, 86, 87 |                            |         |      |         |         |      |

|          |         |                  | •Ports 0,3 at CMOS    |                            |         |      |         |         |      |

|          |         |                  | output option         |                            |         |      |         |         |      |

|          |         | VIO(2)           | Ports 0, 3 at N-ch    |                            |         | -0.3 |         | 15      |      |

|          |         |                  | open drain output     |                            |         |      |         |         |      |

|          |         |                  | option                |                            |         |      |         |         |      |

| High     | Peak    | IOPH             | •Ports 0, 1, 3        | CMOS output                |         | -10  |         |         | mA   |

| Level    | output  |                  | •Ports 71, 72, 73     | At each pins               |         |      |         |         |      |

| output   | current |                  | •Ports 84, 85, 86, 87 |                            |         |      |         |         |      |

| current  | Total   | $\Sigma$ IOAH(1) | Ports 0, 1            | The total all              |         | -30  |         |         |      |

|          | output  |                  |                       | pins                       |         |      |         |         |      |

|          | current | $\Sigma$ IOAH(2) | Port 3                | The total all              |         | -15  |         |         |      |

|          |         |                  |                       | pins                       |         |      |         |         |      |

|          |         | $\Sigma IOAH(3)$ | •Ports 71, 72, 73     | The total all              |         | -10  |         |         |      |

|          |         |                  | •Ports 84, 85, 86, 87 | pins                       |         |      |         |         |      |

| Low      | Peak    | IOPL(1)          | Ports 0, 1, 3         | At each pins               |         |      |         | 20      |      |

| Level    | output  | IOPL(2)          | •Ports 70, 71, 72, 73 | At each pins               |         |      |         | 15      |      |

| output   | current |                  | •Ports 84, 85, 86, 87 |                            |         |      |         |         |      |

| current  | Total   | $\Sigma$ IOAL(1) | Ports 0, 1, 70        | The total all              |         |      |         | 60      |      |

|          | output  |                  |                       | pins                       |         |      |         |         |      |

|          | current | $\Sigma IOAL(2)$ | Port 3                | The total all              |         |      |         | 40      |      |

|          |         |                  |                       | pins                       |         |      |         |         |      |

|          |         | $\Sigma IOAL(3)$ | •Ports 71, 72, 73     | The total all              |         |      |         | 20      |      |

|          |         |                  | •Ports 84, 85, 86, 87 | pins                       |         |      |         |         |      |

| Power    |         | Pd max (1)       | DIP42S                | $Ta=-30$ to $+70^{\circ}C$ |         |      |         | 630     | mW   |

| dissipat | ion     | Pd max (2)       | QFP48E                | Ta=-30 to +70°C            |         |      |         | 410     |      |

| (max.)   |         |                  | -                     |                            |         |      |         |         |      |

| Operati  | ng      | Topg             |                       |                            |         | -30  |         | 70      | °C   |

| tempera  |         |                  |                       |                            |         |      |         |         |      |

| range    |         |                  |                       |                            |         |      |         |         |      |

| Storage  | :       | Tstg             |                       |                            |         | -65  |         | 150     |      |

| tempera  |         |                  |                       |                            |         |      |         |         |      |

| range    |         |                  |                       |                            |         |      |         |         |      |

# **1.** Absolute Maximum Ratings at $V_{SS} = 0V$ and $Ta = 25^{\circ}C$

# **2. Recommended Operating Range** at $Ta = -30^{\circ}C$ to $+70^{\circ}C$ , $V_{SS}=0V$

| Parameter                            | Symbol | Pins                                                      | Conditions                                             | <b>XX FX FX FX FX FX FX FX</b> | · · · ·         | Ratings |                     | unit |

|--------------------------------------|--------|-----------------------------------------------------------|--------------------------------------------------------|--------------------------------|-----------------|---------|---------------------|------|

|                                      |        |                                                           |                                                        | VDD [V]                        | min.            | typ.    | max.                |      |

| Operating<br>supply<br>voltage range | VDD    | VDD                                                       | 0.98µs≤ tCYC<br>tCYC≤400µs                             |                                | 4.5             |         | 6.0                 | V    |

| HOLD voltage                         | VHD    | VDD                                                       | RAMs and<br>Registers hold<br>voltage at HOLD<br>mode. |                                | 2.0             |         | 6.0                 |      |

| Input high<br>voltage                | VIH(1) | Port 0 at CMOS<br>output                                  | Output disable                                         | 4.5 to 6.0                     | 0.33VDD<br>+1.0 |         | VDD                 |      |

|                                      | VIH(2) | Port 0 at N-ch<br>open drain output<br>option.            | Output disable                                         | 4.5 to 6.0                     | 0.75VDD         |         | 13.5                |      |

|                                      | VIH(3) | •Port 1<br>•Ports 72, 73<br>•Port 3 at CMOS<br>output     | Output disable                                         | 4.5 to 6.0                     | 0.75VDD         |         | VDD                 |      |

|                                      | VIH(4) | Port 3 at N-ch<br>open drain output<br>option.            |                                                        | 4.5 to 6.0                     |                 |         | 13.5                |      |

|                                      | VIH(5) | •Port 70<br>Port input /<br>interrupt<br>•Port 71<br>•RES | Output disable                                         | 4.5 to 6.0                     | 0.75VDD         |         | VDD                 |      |

|                                      | VIH(6) | Port 70<br>Watchdog timer                                 | Output disable                                         | 4.5 to 6.0                     | 0.9VDD          |         | VDD                 |      |

|                                      | VIH(7) | •Port 8<br>•Ports 74, 75                                  | Output disable<br>Using as port                        | 4.5 to 6.0                     | 0.75VDD         |         | VDD                 |      |

| Input low<br>voltage                 | VIL(1) | Port 0 at CMOS<br>output option                           | Output disable                                         | 4.5 to 6.0                     | VSS             |         | 0.2VDD              |      |

|                                      | VIL(2) | Port 0 at N-ch<br>open drain output<br>option.            | Output disable                                         | 4.5 to 6.0                     | VSS             |         | 0.25V <sub>DD</sub> |      |

|                                      | VIL(3) | •Ports 1, 3<br>•Ports 72, 73                              | Output disable                                         | 4.5 to 6.0                     | VSS             |         | 0.25V <sub>DD</sub> |      |

|                                      | VIL(4) | •Port 70<br>Port input /<br>interrupt<br>•Port 71<br>•RES | Output disable                                         | 4.5 to 6.0                     | VSS             |         | 0.25VDD             |      |

|                                      | VIL(5) | Port 70<br>Watchdog timer                                 | Output disable                                         | 4.5 to 6.0                     | VSS             |         | 0.8VDD<br>-1.0      |      |

|                                      | VIL(6) | •Port 8<br>•Ports 74, 75                                  | Output disable<br>Using as port                        | 4.5 to 6.0                     | VSS             |         | 0.25V <sub>DD</sub> |      |

| Operation cycle time                 | tCYC   |                                                           |                                                        | 4.5 to 6.0                     | 0.98            |         | 400                 | μs   |

| Parameter        | Symbol   | Pins     | Conditions            |            |      | Ratings |      | - unit |

|------------------|----------|----------|-----------------------|------------|------|---------|------|--------|

| Faranieter       | Symbol   | FIIIS    | Conditions            | VDD [V]    | min. | typ.    | max. | uIIIt  |

| Oscillation fre- | FmCF(1)  | CF1, CF2 | •6MHz (ceramic        | 4.5 to 6.0 | 5.88 | 6       | 6.12 | MHz    |

| quency range     |          |          | resonator oscil-      |            |      |         |      |        |

| (Note 1)         |          |          | lation)               |            |      |         |      |        |

|                  |          |          | •Refer to figure 1    |            |      |         |      |        |

|                  | FmCF(2)  | CF1, CF2 | •3MHz (ceramic        | 4.5 to 6.0 | 2.94 | 3       | 3.06 |        |

|                  |          |          | resonator oscil-      |            |      |         |      |        |

|                  |          |          | lation)               |            |      |         |      |        |

|                  |          |          | •Refer to figure 1    |            |      |         |      |        |

|                  | FmRC     |          | RC oscillation        | 4.5 to 6.0 | 0.3  | 0.8     | 3.0  |        |

|                  | FsXtal   | XT1, XT2 | •32.768kHz            | 4.5 to 6.0 |      | 32.768  |      | kHz    |

|                  |          |          | (crystal oscillation) |            |      |         |      |        |

|                  |          |          | •Refer to figure 2    |            |      |         |      |        |

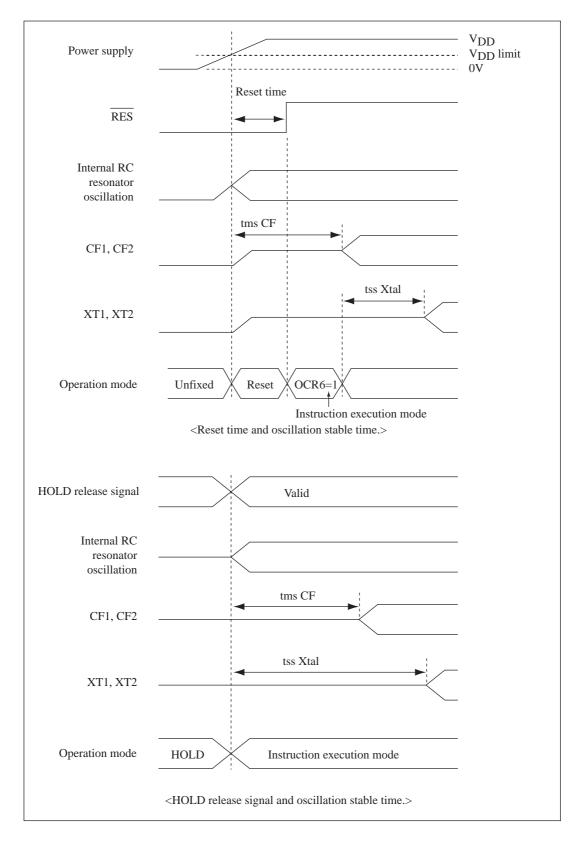

| Oscillation      | tmsCF(1) | CF1, CF2 | •6MHz (ceramic        | 4.5 to 6.0 |      | 0.05    | 0.50 | ms     |

| stable time      |          |          | resonator oscil-      |            |      |         |      |        |

| period           |          |          | lation)               |            |      |         |      |        |

| (Note 1)         |          |          | •Refer to figure 3    |            |      |         |      |        |

|                  | tmsCF(2) | CF1, CF2 | •3MHz (ceramic        | 4.5 to 6.0 |      | 0.10    | 1.00 |        |

|                  |          |          | resonator oscil-      |            |      |         |      |        |

|                  |          |          | lation)               |            |      |         |      |        |

|                  |          |          | •Refer to figure 3    |            |      |         |      |        |

|                  | tssXtal  | XT1, XT2 | •32.768kHz            | 4.5 to 6.0 |      | 1.00    | 1.50 | S      |

|                  |          |          | (crystal oscillation) |            |      |         |      |        |

|                  |          |          | •Refer to figure 3    |            |      |         |      |        |

(Note 1) The oscillation constant is shown on table 1 and table 2.

| Parameter                   | Symbol | Pins                                                                                                                  | Conditions                                                                                                      |            |                      | Ratings            |      | unit |

|-----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|----------------------|--------------------|------|------|

|                             | -      |                                                                                                                       |                                                                                                                 | VDD [V]    | min.                 | typ.               | max. |      |

| Input high<br>current       | IIH(1) | Ports 0, 3 of Open<br>drein output                                                                                    | •Output disable<br>•VIN=13.5V<br>(including off-leak<br>current of the                                          |            |                      |                    | 5    | μA   |

|                             | IIH(2) | •Port 0 without                                                                                                       | output Tr.)<br>•Output disable                                                                                  | 45  to  60 |                      |                    | 1    | -    |

|                             |        | •Port 0 without<br>pull-up MOS Tr.<br>•Ports 1, 3<br>•Ports 70, 71, 72, 73<br>•Port 8                                 | •Pull-up MOS Tr.<br>OFF.                                                                                        |            |                      |                    | 1    |      |

|                             | IIH(3) | RES                                                                                                                   | VIN=VDD                                                                                                         | 4.5 to 6.0 |                      |                    | 1    | 1    |

|                             | IIH(4) | Ports 74, 75                                                                                                          | VIN=VDD<br>at using as port                                                                                     | 4.5 to 6.0 |                      |                    | 1    |      |

| Input low<br>current        | IIL(1) | <ul> <li>Ports 1, 3,</li> <li>Port 0 without pull-up MOS Tr.</li> <li>Ports 70, 71, 72, 73</li> <li>Port 8</li> </ul> | •Output disable<br>•Pull-up MOS Tr.<br>OFF.<br>•VIN=VSS<br>(including off-leak<br>current of the<br>output Tr.) |            | -1                   |                    |      | _    |

|                             | IIL(2) | RES                                                                                                                   | VIN=VSS                                                                                                         | 4.5 to 6.0 | -1                   |                    |      | -    |

|                             | IIL(3) | Ports 74, 75                                                                                                          | VIN=VSS<br>at using as port                                                                                     | 4.5 to 6.0 | -1                   |                    |      |      |

| Output high voltage         | VOH(1) | Ports 0, 1, 3<br>of CMOS output                                                                                       | IOH=-1.0mA                                                                                                      | 4.5 to 6.0 | V <sub>DD</sub> -1   |                    |      | V    |

|                             | VOH(2) | •Ports 71, 72, 73<br>•Ports 84, 85, 86, 87                                                                            | IOH=-0.1mA                                                                                                      | 4.5 to 6.0 | V <sub>DD</sub> -0.5 |                    |      |      |

| Output low                  | VOL(1) | Ports 0, 1, 3                                                                                                         | IOL=10mA                                                                                                        | 4.5 to 6.0 |                      |                    | 1.5  |      |

| voltage                     | VOL(2) |                                                                                                                       | IOL=1.6mA                                                                                                       | 4.5 to 6.0 |                      |                    | 0.4  | 4    |

|                             | VOL(3) | •Ports 71, 72, 73<br>•Ports 84, 85, 86, 87                                                                            | IOL=1.6mA                                                                                                       | 4.5 to 6.0 |                      |                    | 0.4  |      |

|                             | VOL(4) | Port 70                                                                                                               | IOL=1.0mA                                                                                                       | 4.5 to 6.0 | 1.7                  | 40                 | 0.4  | 10   |

| Pull-up MOS<br>Tr. resistor | Rpu    | •Ports 0, 1, 3<br>•Ports 70, 71, 72, 73<br>•Ports 84, 85, 86, 87                                                      |                                                                                                                 | 4.5 to 6.0 | 15                   | 40                 | 70   | kΩ   |

| Hysteresis<br>voltage       | VHIS   | •Port 1<br>•Ports 70, 71, 72, 73<br>•RES                                                                              | Output disable                                                                                                  | 4.5 to 6.0 |                      | 0.1V <sub>DD</sub> |      | V    |

| Pin<br>capacitance          | СР     | All pins                                                                                                              | •f=1MHz<br>Unmeasurement<br>terminals for<br>input are set to<br>VSS level.<br>•Ta=25°C                         | 4.5 to 6.0 |                      | 10                 |      | pF   |

# **3. Electrical Characteristics** at Ta= $-30^{\circ}$ C to $+70^{\circ}$ C, VSS=0V

|               |              | meter      | Symbol         | Pins                   | Conditions                     |            |      | Ratings      |                     | unit |

|---------------|--------------|------------|----------------|------------------------|--------------------------------|------------|------|--------------|---------------------|------|

|               | r ai a       | ineter     | •              |                        |                                | VDD [V]    | min. | typ.         | max.                |      |

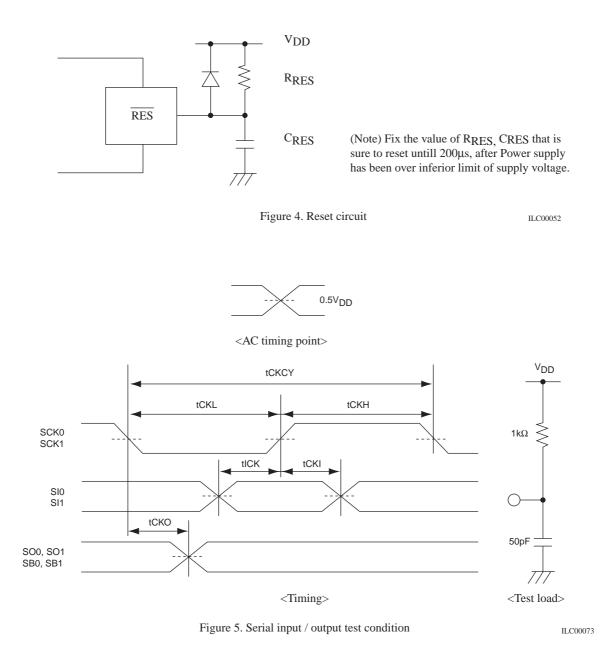

|               |              | Cycle      | tCKCY(1)       | SCK0, SCK1             | Refer to figure 5              | 4.5 to 6.0 | 2    |              |                     | tCYC |

|               |              | Low        | tCKL(1)        |                        |                                | 4.5 to 6.0 | 1    |              |                     |      |

|               | ock          | level      |                |                        |                                |            |      |              |                     |      |

|               | clc          | width      |                |                        |                                |            |      |              |                     |      |

|               | Input clock  | High       | tCKH(1)        |                        |                                | 4.5 to 6.0 | 1    |              |                     |      |

|               | In           | level      |                |                        |                                |            |      |              |                     |      |

|               |              | pulse      |                |                        |                                |            |      |              |                     |      |

| ĸ             |              | width      |                |                        | II                             | 15.0       | 2    |              |                     | -    |

| Serial clock  |              | Cycle      | tCKCY(2)       | SCK0, SCK1             | •Use pull-up<br>resistor (1kΩ) | 4.5 to 6.0 | 2    |              |                     |      |

| rial          |              |            |                |                        | when open drain                |            |      |              |                     |      |

| Sei           |              | Low        | tCKL(2)        | -                      | output.                        | 4.5 to 6.0 |      | 1 / 2 tCKCY  |                     | -    |

|               | Output clock | level      | tCRL(2)        |                        | •Refer to figure 5             | 4.5 10 0.0 |      | 1 / 2 tCKC 1 |                     |      |

|               | t cl         | pulse      |                |                        | iterer to ligure 5             |            |      |              |                     |      |

|               | tpu          | width      |                |                        |                                |            |      |              |                     |      |

|               | õ            | High       | tCKH(2)        | -                      |                                | 4.5 to 6.0 |      | 1 / 2 tCKCY  |                     |      |

|               |              | level      |                |                        |                                |            |      |              |                     |      |

|               |              | pulse      |                |                        |                                |            |      |              |                     |      |

|               |              | width      |                |                        |                                |            |      |              |                     |      |

| ıt            |              | ta set-up  | tICK           | •SI0, SI1              | •Data set-up to                | 4.5 to 6.0 | 0.1  |              |                     | μs   |

| ldu           | tim          |            |                | •SB0, SB1              | SCK0, 1                        |            |      |              |                     |      |

| Serial input  |              | ta hold    | tCKI           |                        | •Data hold from                | 4.5 to 6.0 | 0.1  |              |                     |      |

| Ser           | tim          | e          |                |                        | SCK0, 1                        |            |      |              |                     |      |

|               |              | 1 1        |                | 000.001                | •Refer to figure 5             | 15.0       |      |              | 7. (12. (0)(0)      | -    |

|               | tim          |            | tCKO(1)        | •SO0, SO1<br>•SB0, SB1 | •Use pull-up<br>resistor (1kΩ) | 4.5 to 6.0 |      |              | 7 / 12 tCYC<br>+0.2 |      |

|               |              | rial clock |                | •300, 301              | when open drain                |            |      |              | +0.2                |      |

| nt            | ``           | extrnal    |                |                        | output.                        |            |      |              |                     |      |

| utp           |              | ock)       |                |                        | output.                        |            |      |              |                     |      |

| Serial output |              | tput delay | tCKO(2)        | -                      | •Data hold from                | 4.5 to 6.0 |      |              | 1/3 tCYC            | -    |

| eri           | tim          |            | ··( <b>-</b> ) |                        | SCK0, 1                        |            |      |              | +0.2                |      |

| S             |              | rial clock |                |                        | •Refer to figure 5             |            |      |              |                     |      |

|               | `            | internal   |                |                        |                                |            |      |              |                     |      |

|               | clo          | ock)       |                |                        |                                |            |      |              |                     |      |

## 4. Serial Input / Output Characteristics at Ta=-30°C to +70°C, V<sub>SS</sub>= 0V

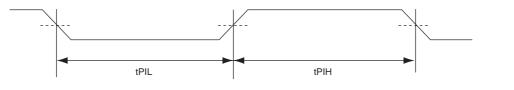

| Demonster   | Coursels a 1 | Dima               | Canditiana         |            |      | Ratings |      |      |

|-------------|--------------|--------------------|--------------------|------------|------|---------|------|------|

| Parameter   | Symbol       | Pins               |                    | VDD [V]    | min. | typ.    | max. | unit |

| High / low  | tPIH(1)      | •INT0, INT1        | •Interrupt accept- | 4.5 to 6.0 | 1    |         |      | tCYC |

| level pulse | tPIL(1)      | •INT2 / TOIN       | able               |            |      |         |      |      |

| width       |              |                    | •Timer0-countable  |            |      |         |      |      |

|             | tPIH(2)      | INT3 / TOIN        | •Interrupt accept- | 4.5 to 6.0 | 2    |         |      | 1    |

|             | tPIL(2)      | (The noise         | able               |            |      |         |      |      |

|             |              | rejection clock    | •Timer0-countable  |            |      |         |      |      |

|             |              | select to 1 / 1.)  |                    |            |      |         |      |      |

|             | tPIH(3)      | INT3 / TOIN        | •Interrupt accept- | 4.5 to 6.0 | 32   |         |      | 1    |

|             | tPIL(3)      | (The noise         | able               |            |      |         |      |      |

|             |              | rejection clock    | •Timer0-countable  |            |      |         |      |      |

|             |              | select to 1 / 16.) |                    |            |      |         |      |      |

|             | tPIH(4)      | INT3 / TOIN        | •Interrupt accept- | 4.5 to 6.0 | 128  |         |      | 1    |

|             | tPIL(4)      | (The noise         | able               |            |      |         |      |      |

|             |              | rejection clock    | •Timer0-countable  |            |      |         |      |      |

|             |              | select to 1 / 64.) |                    |            |      |         |      |      |

|             | tPIL(5)      | RES                | Reset acceptable   | 4.5 to 6.0 | 200  |         |      | μs   |

| 5. Pulse Input | <b>Conditions</b> at Ta= $-30^{\circ}$ C to $+70^{\circ}$ C, | VSS = 0V |

|----------------|--------------------------------------------------------------|----------|

|----------------|--------------------------------------------------------------|----------|

## 6. A / D Converter Characteristics at Ta=-30°C to +70°C , VSS = 0V

| Domenator     | Symbol | Pins       | Conditions     |            | Ratings |      |         | unit |

|---------------|--------|------------|----------------|------------|---------|------|---------|------|

| Parameter     |        |            |                | VDD [V]    | min.    | typ. | max.    | unit |

| Resolution    | N      |            |                | 4.5 to 6.0 |         | 8    |         | bit  |

| Absolute      | ET     |            |                | 4.5 to 6.0 |         |      | ±1.5    | LSB  |

| precision     |        |            |                |            |         |      |         |      |

| (Note 2)      |        |            |                |            |         |      |         |      |

| Conversion    | tCAD   |            | AD conversion  | 4.5 to 6.0 | 15.68   |      | 65.28   | μs   |

| time          |        |            | time=16 X tCYC |            | (tCYC = |      | (tCYC = |      |

|               |        |            | (ADCR2=0)      |            | 0.98µs) |      | 4.08µs) |      |

|               |        |            | (Note 3)       |            |         |      |         |      |

|               |        |            | AD conversion  | -          | 31.36   |      | 130.56  |      |

|               |        |            | time=32 X tCYC |            | (tCYC = |      | (tCYC = |      |

|               |        |            | (ADCR2=1)      |            | 0.98µs) |      | 4.08µs) |      |

|               |        |            | (Note 3)       |            |         |      |         |      |

| Analog input  | VAIN   | AN0 to AN7 |                | 4.5 to 6.0 | VSS     |      | VDD     | V    |

| voltage range |        |            |                |            |         |      |         |      |

| Analog port   | IAINH  |            | VAIN=VDD       | 4.5 to 6.0 |         |      | 1       | μA   |

| input current | IAINL  |            | VAIN=VSS       | 4.5 to 6.0 | -1      |      |         |      |

(Note 2) Absolute precision excepts quantizing error (±1/2 LSB).

(Note 3) The conversion time means the time from executing the AD conversion instruction to setting the complete digital conversion value to the register.

| Parameter    | Symbol   | Pins | Conditions          |            |      | Ratings |      | unit |

|--------------|----------|------|---------------------|------------|------|---------|------|------|

|              | _        |      |                     | VDD [V]    | min. | typ.    | max. | unn  |

| Current      | IDDOP(1) | VDD  | •FmCF=6MHz          | 4.5 to 6.0 |      | 14      | 26   | mA   |

| dissipation  |          |      | Ceramic resona-     |            |      |         |      |      |

| during basic |          |      | tor oscillation     |            |      |         |      |      |

| operation    |          |      | •FsXtal=32.768kHz   | z          |      |         |      |      |

| (Note 4)     |          |      | crystal oscillation |            |      |         |      |      |

|              |          |      | •System clock :     |            |      |         |      |      |

|              |          |      | CF oscillation      |            |      |         |      |      |

|              |          |      | •Internal RC        |            |      |         |      |      |

|              |          |      | oscillation stops   | .          |      |         |      |      |

|              |          |      | •1 / 1 divider      |            |      |         |      |      |

|              | IDDOP(2) |      | •FmCF=3MHz          | 4.5 to 6.0 |      | 6.5     | 14   | 1    |

|              |          |      | Ceramic resona      | -          |      |         |      |      |

|              |          |      | tor oscillation     |            |      |         |      |      |

|              |          |      | •FsXtal=32.768kHz   |            |      |         |      |      |

|              |          |      | crystal oscillation |            |      |         |      |      |

|              |          |      | •System clock :     |            |      |         |      |      |

|              |          |      | CF oscillation      |            |      |         |      |      |

|              |          |      | •Internal RC        |            |      |         |      |      |

|              |          |      | oscillation stops.  |            |      |         |      |      |

|              |          |      | •1 / 2 divider      |            |      |         |      |      |

|              | IDDOP(3) | -    | •FmCF=0Hz           | 4.5 to 6.0 |      | 4       | 12   | 1    |

|              |          |      | (when oscillation   |            |      |         |      |      |

|              |          |      | stops).             |            |      |         |      |      |

|              |          |      | •FsXtal=32.768kHz   |            |      |         |      |      |

|              |          |      | crystal oscillation | 1          |      |         |      |      |

|              |          |      | •System clock :     |            |      |         |      |      |

|              |          |      | RC oscillation      |            |      |         |      |      |

|              |          |      | •1 / 2 divider      |            |      |         |      |      |

|              | IDDOP(4) | -    | •FmCF=0Hz           | 4.5 to 6.0 |      | 3.5     | 9    | -    |

|              |          |      | (when oscillation   | 1          |      |         | -    |      |

|              |          |      | stops).             |            |      |         |      |      |

|              |          |      | •FsXtal=32.768kHz   |            |      |         |      |      |

|              |          |      | crystal oscillation |            |      |         |      |      |

|              |          |      | •System clock :     |            |      |         |      |      |

|              |          |      | crystal oscillation |            |      |         |      |      |

|              |          |      | •Internal RC        |            |      |         |      |      |

|              |          |      | oscillation stops.  |            |      |         |      |      |

|              |          |      | •1 / 2 divider      |            |      |         |      |      |

# **7.** Current Dissipation Characteristics at Ta=-30°C to +70°C, VSS = 0V

| Parameter                                       | Symbol     | Pins | Conditions Vap IV                                                                                                                                                                                                                       |            | Ratings |      |      | unit |

|-------------------------------------------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|------|------|------|

|                                                 |            |      |                                                                                                                                                                                                                                         | VDD [V]    | min.    | typ. | max. |      |

| Current<br>dissipation<br>HALT mode<br>(Note 4) | IDDHALT(1) | VDD  | •HALT mode<br>•FmCF=6MHz<br>Ceramic resona-<br>tor oscillation<br>•FsXtal=32.768kHz<br>crystal oscillation<br>•System clock :                                                                                                           | 4.5 to 6.0 |         | 4    | 9    | mA   |

|                                                 |            |      | CF oscillation<br>•Internal RC<br>oscillation stops.<br>•1 / 1 devider                                                                                                                                                                  |            |         |      |      |      |

|                                                 | IDDHALT(2) |      | •HALT mode<br>FmCF=3MHz<br>Ceramic resona-<br>tor oscillation<br>•FsXtal=32.768kHz<br>crystal oscillation<br>•System clock :<br>CF oscillation<br>•Internal RC<br>oscillation stops.<br>•1 / 2 devider                                  |            |         | 2.2  | 5    |      |

|                                                 | IDDHALT(3) |      | •HALT mode<br>FmCF=0Hz<br>(when oscillation<br>stops).<br>•FsXtal=32.768kHz<br>crystal oscillation<br>•System clock :<br>RC oscillation<br>•1 / 2 devider                                                                               | 4.5 to 6.0 |         | 400  | 1600 | μΑ   |

|                                                 | IDDHALT(4) |      | <ul> <li>HALT mode<br/>FmCF=0Hz<br/>(when oscillation<br/>stops).</li> <li>FsXtal=32.768kHz<br/>crystal oscillation</li> <li>System clock :<br/>32.768kHz</li> <li>Internal RC<br/>oscillation stops.</li> <li>1 / 2 devider</li> </ul> | 4.5 to 6.0 |         | 25   | 100  |      |

| Current<br>dissipation<br>HOLD mode<br>(Note 4) | IDDHOLD    | VDD  | HOLD mode                                                                                                                                                                                                                               | 4.5 to 6.0 |         | 0.05 | 30   |      |

(Note 4) The currents of output transistors and pull-up MOS transistors are ignored.

| A kind of oscillation  | Producer | Oscillator             | C1        | C2   |

|------------------------|----------|------------------------|-----------|------|

| 6MHz ceramic resonator | Murata   | CSA 6.00MG             | 33pF      | 33pF |

| oscillation            |          | CST 6.00MGW            | on chip   |      |

|                        | Kyocera  | KBR-6.0MSA             | 33pF      | 33pF |

|                        |          | PBRC 6.00A (chip type) | 33pF 33pl |      |

|                        |          | KBR-6.0MKS             | on chip   |      |

|                        |          | PBRC 6.00B (chip type) |           |      |

| 3MHz ceramic resonator | Murata   | CSA 3.00MG             | 33pF      | 33pF |

| oscillation            |          | CST 3.00MGW            | on chip   |      |

|                        | Kyocera  | KBR-3.0MS              | 47pF      | 47pF |

Table 1. Ceramic resonator oscillation guaranteed constant (main-clock)

\* Both C1 and C2 must use K rank (±10%) and SL characteristics.

#### Table 2. Crystal oscillation guaranteed constant (sub-clock)

| A kind of oscillation | Producer | Oscillator     | C3   | C4   |

|-----------------------|----------|----------------|------|------|

| 32.768kHz crystal     | Kyocera  | KF-38G-13P0200 | 18pF | 18pF |

| oscillation           |          |                |      |      |

\* Both C3 and C4 must use J rank ( $\pm 5\%$ ) and CH characteristics.

(It is about the application which is not in need of high precision. Use K rank ( $\pm 10\%$ ) and SL characteristics.)

•Since the circuit pattern affects the oscillation frequency, place the oscillation-related parts as close to the oscillation pins as possible with the shortest possible pattern length.

•If you use other oscillators herein, we provide no guarantee for the characteristics.

Figure 1. Main-clock circuit Ceramic resonator oscillation

ILC00059

Figure 2. Sub-clock circui Cryatal oscillation

Figure 3. Oscillation stable time

Figure 6. Pulse input timing condition

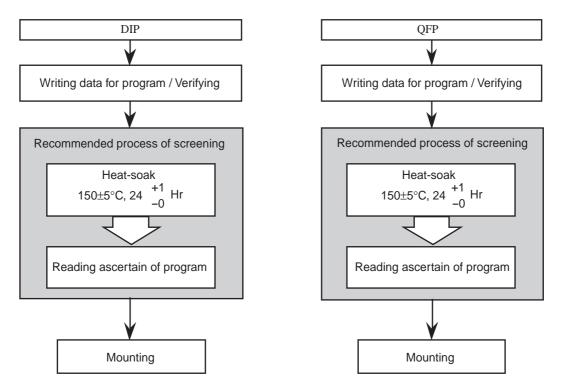

#### Notice for use

- The construction of the one-time programmable microcomputer with a blank built-in PROM makes it impossible for Sanyo to completely factory-test it before shipping. To probe reliability of the programmed devices, the screening procedure shown in the following figure should always be followed.

- It is not possible to perform a writing test on the blank PROM. 100% yield, therefore, cannot be guaranteed.

- Keeping the dry packing The environment must be held at a temparature of 30°C or less and a humidity level of 70% or less.

- After opening the packing

After opening the packing, a controlled environment must be maintained until soldering. The environment must be held at a temperature of 30°C or less and a humidity level of 70% or less. Please solder within 96 hours.

a. Shipping with a blank PROM (Programming the data by yourself)

This microcomputer is provided DIP / QFP packages, but the condition before mounting is different. Refer to the mounting procedure as follows.

#### b. Shipping with a programmed PROM (Programming the data by Sanyo)

memo :

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data,services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only ; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of January, 2001. Specifications and information herein are subject to change without notice.