# ID242 Series Flash Memory Card

(Model Numbers: ID242xxx)

Spec No.: CPS0002-002

Issue Date: May, 1998

#### **ID242 SERIES PRODUCT OVERVIEW**

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2). even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- · Office electronics

- · Instrumentation and measuring equipment

- · Machine tools

- · Audiovisual equipment

- · Home appliances

- · Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- · Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- · Mainframe computers

- · Traffic control systems

- · Gas leak detectors and automatic cutoff devices

- · Rescue and security equipment

- · Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- · Aerospace equipment

- · Communications equipment for trunk lines

- · Control equipment for the nuclear power industry

- · Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

## Contents

| 1.  | Introduction                                   | Р. | 3  |

|-----|------------------------------------------------|----|----|

| 2.  | Features                                       | P. | 3  |

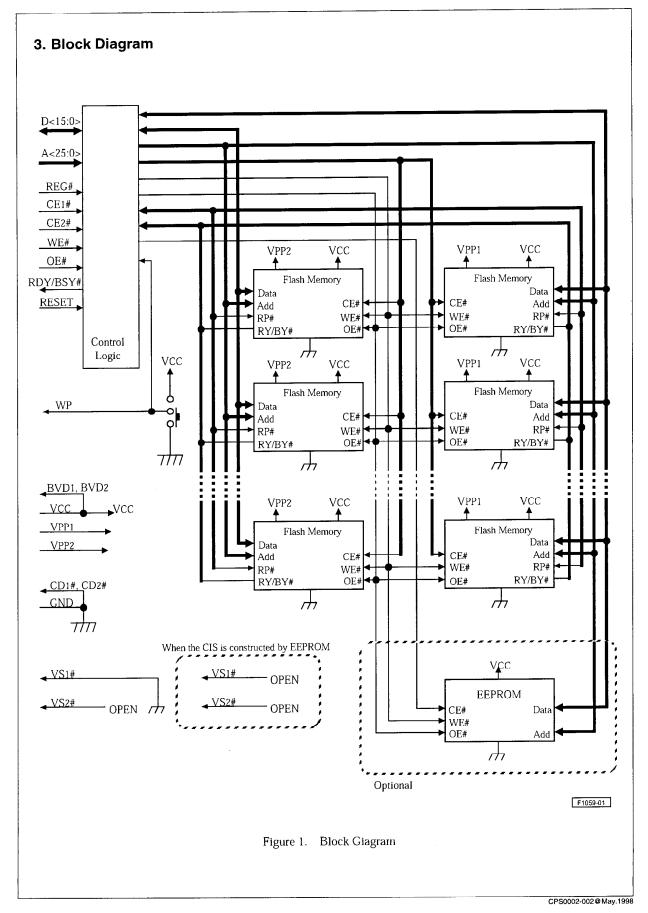

| 3.  | Block Diagram                                  | P. | 4  |

| 4.  | Pin Connections                                | P. | 5  |

| 5.  | Signal Description                             | P. | 6  |

| 6.  | Functions                                      | P. | 7  |

|     | 6. 1 Common Memory                             | P. | 7  |

|     | 6. 2 Attribute Memory                          | P. | 8  |

|     | 6. 3 Function Table                            | P. | 9  |

| 7.  | Card Information Structure (CIS)               | P. | 9  |

| 8.  | Card Control                                   | P. | 12 |

|     | 8. 1 Reset                                     | P. | 12 |

|     | 8. 2 Status Register                           | P. | 12 |

|     | 8. 3 Write Protect Switch                      | P. | 12 |

|     | 8. 4 Identifier Codes                          | P. | 12 |

| 9.  | Component Management Register (CMR)            | P. | 14 |

| 10. | Command Definitions                            | P. | 16 |

| 11. | Electrical Specifications                      | P. | 17 |

|     | 11. 1 Absolute Maximum Ratings                 | P. | 17 |

|     | 11. 2 Recommended Operating Conditions         | P. | 17 |

|     | 11. 3 Capacitance                              | P. | 17 |

|     | 11. 4 AC Input/Output Test Conditions          | P. | 17 |

| 12. | DC Characteristics                             | P. | 18 |

| 13. | AC Characteristics                             | P. | 20 |

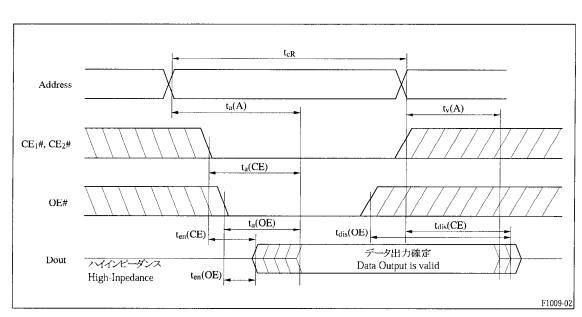

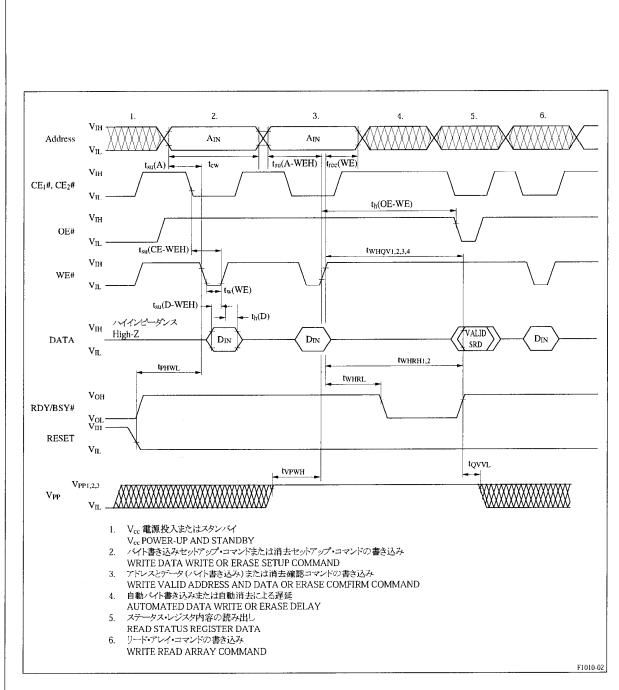

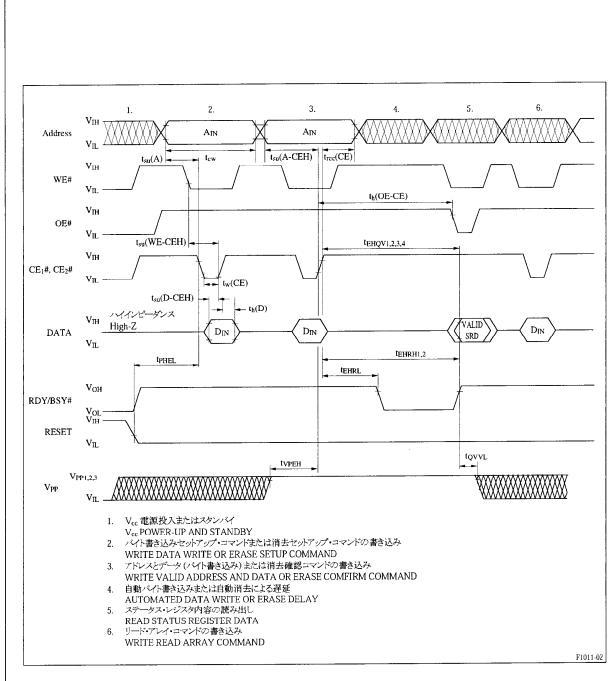

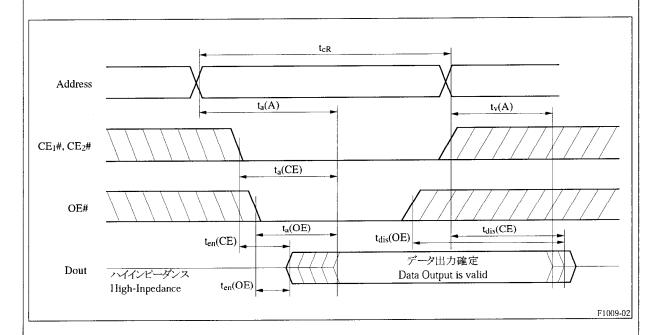

|     | 13. 1 Common Memory Read Operations            | P. | 20 |

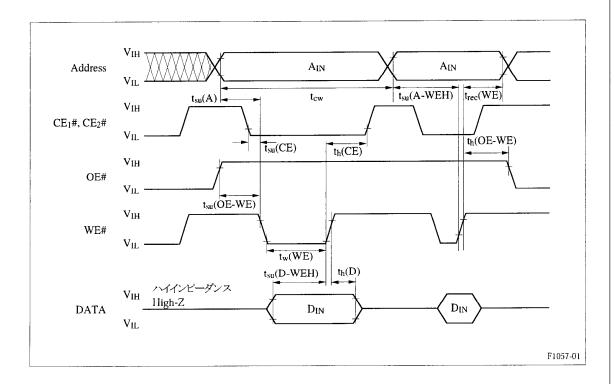

|     | 13. 2 Command Write Operations : Common Memory | P. | 22 |

|     | 13. 3 Attribute Memory Read Operations         | P. | 28 |

|     | 13. 4 Attribute Memory Write Operations        | P. | 29 |

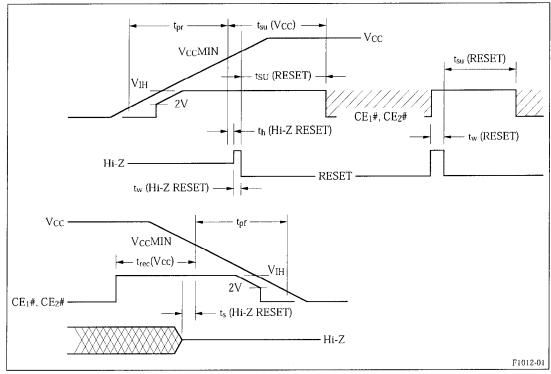

|     | 13. 5 Power-Up/Power Down                      | P. | 30 |

| 14. | Specification Changes                          | P. | 31 |

| 15. | Other Precautions                              | P. | 31 |

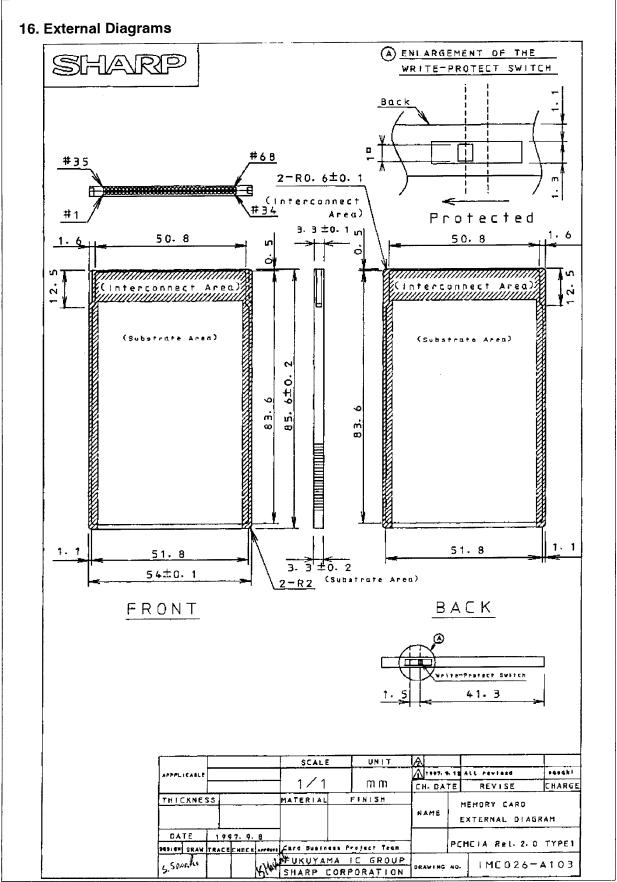

| 16. | External Diagrams                              | P. | 32 |

## 1. Introduction

This datasheet is for SHARP's ID242 series flash memory card. This datasheet provides all AC and DC characteristics (including timing waveforms) and a convenient reference for the device command set and the card's integrated registers(including the Flash Memory's status registers). This datasheet provides description of the methods which are very helpful for customer to use the card.

## 2. Features

2.1 Type

Flash Memory Card

#### 2.2 Overview

|                         |        | ID242Dxx                        | ID242Exx                                   | ID242Gxx               | ID242Hxx                | ID242Kxx               | ID242Lxx                |  |  |  |  |

|-------------------------|--------|---------------------------------|--------------------------------------------|------------------------|-------------------------|------------------------|-------------------------|--|--|--|--|

| Common                  | Byte   | 2Mbyte                          | 4Mbyte                                     | 4Mbyte 8Mbyte          |                         | 16Mbyte                | 20Mbyte                 |  |  |  |  |

| Memory<br>Capacity      | Word   | 1Mword                          | 2Mword                                     | 4Mword                 | 5Mword                  | 8Mword                 | 10Mword                 |  |  |  |  |

| Device                  |        | LH28F008SC<br>2devices          | LH28F008SC<br>4devices                     | LH28F008SC<br>8devices | LH28F008SC<br>10devices | LH28F016SC<br>8devices | LH28F016SC<br>10devices |  |  |  |  |

| Attribute I<br>Capasity | Memory |                                 | 2Kbyte (Note:standard CIS is not writable) |                        |                         |                        |                         |  |  |  |  |

| Supply Vo               | oltage | Smart Voltage                   |                                            |                        |                         |                        |                         |  |  |  |  |

| Access tin              | ne     |                                 | 150ns(@Vcc=5v)<br>250ns(@Vcc=3.3v)         |                        |                         |                        |                         |  |  |  |  |

| Erase Unit              | t      | 64K word blocks                 |                                            |                        |                         |                        |                         |  |  |  |  |

| Program/Erase<br>Cycles |        | 100,000cycles/Block             |                                            |                        |                         |                        |                         |  |  |  |  |

| External<br>Dimensions  |        | PCMCIA Type 1 54.0× 85.6× 3.3mm |                                            |                        |                         |                        |                         |  |  |  |  |

T1050-01

| 2.3 | Interface                      | Parallel I/O Interface                                         |

|-----|--------------------------------|----------------------------------------------------------------|

| 2.4 | Function Table                 | See Function Table in page. 9                                  |

| 2.5 | Pin Connections                | See Pin Connections in page. 6                                 |

| 2.6 | Type of Connector              | Conforms to PCMCIA PC Card Standard 95 Card Use Connector      |

|     |                                | (Card connector: JC20-J68S-NB3 JAE or FCN-568J068-G/0 Fujitsu) |

| 2.7 | Operating Temperature          | 0 to 60°C                                                      |

| 2.8 | Storage Temperature            | -20 to 65°C                                                    |

| 2.9 | Not designed for rated radiati | on hardened.                                                   |

## 4. Pin Connections

Table 1. Pin Connections

| PIN<br>No. | SIGNAL           | I/O | FUNCTION        | ACTIVE | PIN<br>No. | SIGNAL            | I/O | FUNCTION                 | ACTIVE |

|------------|------------------|-----|-----------------|--------|------------|-------------------|-----|--------------------------|--------|

| 1          | GND              |     | Ground          |        | 35         | GND               |     | Ground                   |        |

| 2          | $D_3$            | I/O | Data Bit 3      |        | 36         | CD <sub>1</sub> # | 0   | Card Detect 1            | LOW    |

| 3          | D <sub>4</sub>   | I/O | Data Bit 4      |        | 37         | D <sub>II</sub>   | I/O | Data Bit 11              |        |

| 4          | D <sub>5</sub>   | I/O | Data Bit 5      |        | 38         | D <sub>12</sub>   | I/O | Data Bit 12              |        |

| 5          | $D_6$            | I/O | Data Bit 6      |        | 39         | D <sub>13</sub>   | I/O | Data Bit 13              |        |

| 6          | D <sub>7</sub>   | I/O | Data Bit 7      |        | 40         | D <sub>14</sub>   | I/O | Data Bit 14              |        |

| 7          | CEı#             | I   | Card Enable 1   | LOW    | 41         | D <sub>15</sub>   | I/O | Data Bit 15              |        |

| 8          | A10              | 1   | Address Bit 10  |        | 42         | CE <sub>2</sub> # | I   | Card Enable 2            | LOW    |

| 9          | OE#              | I   | Output Enable   | LOW    | 43         | VS <sub>1</sub> # | 0   | Voltage Sense 1          |        |

| 10         | A11              | I   | Address Bit 11  |        | 44         | RFU               |     | Reserved                 |        |

| 11         | A <sub>9</sub>   | I   | Address Bit 9   |        | 45         | RFU               |     | Reserved                 |        |

| 12         | A <sub>8</sub>   | I   | Address Bit 8   |        | 46         | A <sub>17</sub>   | I   | Address Bit 17           |        |

| 13         | A <sub>13</sub>  | I   | Address Bit 13  |        | 47         | A <sub>18</sub>   | I   | Address Bit 18           |        |

| 14         | A <sub>14</sub>  | I   | Address Bit 14  |        | 48         | A <sub>19</sub>   | I   | Address Bit 19           |        |

| 15         | WE#              | I   | Write Enable    | LOW    | 49         | A <sub>20</sub>   | I   | Address Bit 20           |        |

| 16         | RDY/BSY#         | 0   | Ready Busy      | LOW    | 50         | A <sub>21</sub>   | I   | Address Bit 21           |        |

| 17         | Vcc              |     | Supply Voltage  |        | 51         | $V_{cc}$          |     | Supply Voltage           |        |

| 18         | V <sub>PP1</sub> |     | Program Voltage |        | 52         | $V_{PP2}$         |     | Program Voltage          |        |

| 19         | A <sub>16</sub>  | I   | Address Bit 16  |        | 53         | A <sub>22</sub>   | I   | Address Bit 22           |        |

| 20         | A15              | I   | Address Bit 15  |        | 54         | A <sub>23</sub>   | I   | Address Bit 23           |        |

| 21         | A12              | I   | Address Bit 12  |        | 55         | A <sub>24</sub>   | I   | Address Bit 24           |        |

| 22         | A <sub>7</sub>   | I   | Address Bit 7   |        | 56         | A <sub>25</sub>   | I   | Address Bit 25           |        |

| 23         | A6               | I   | Address Bit 6   |        | 57         | VS <sub>2</sub> # | 0   | Voltage Sense 2          |        |

| 24         | A5               | I   | Address Bit 5   |        | 58         | RESET             | I   | Reset                    | HIGH   |

| 25         | A <sub>4</sub>   | I   | Address Bit 4   |        | 59         | RFU               |     | Reserved                 |        |

| 26         | A <sub>3</sub>   | I   | Address Bit 3   |        | 60         | RFU               |     | Reserved                 |        |

| 27         | A2               | I   | Address Bit 2   |        | 61         | REG#              | I   | Atribute Memory Select   | LOW    |

| 28         | Αı               | I   | Address Bit 1   |        | 62         | BVD <sub>2</sub>  | 0   | Battery Boltage Detect 2 |        |

| 29         | A <sub>0</sub>   | I   | Address Bit 0   |        | 63         | BVD,              | 0   | Battery Boltage Detect 1 |        |

| 30         | $D_0$            | I/O | Data Bit 0      |        | 64         | $D_8$             | I/O | Data Bit 8               |        |

| 31         | Dı               | I/O | Data Bit 1      |        | 65         | $D_9$             | I/O | Data Bit 9               |        |

| 32         | D <sub>2</sub>   | I/O | Data Bit 2      |        | 66         | D <sub>10</sub>   | I/O | Data Bit 10              |        |

| 33         | WP               | 0   | Write Protect   | HIGH   | 67         | CD <sub>2</sub> # | 0   | Card Detect 2            | LOW    |

| 34         | GND              |     | Ground          |        | 68         | GND               |     | Ground                   |        |

# 5. Signal Description

Table 2. Signal Description

| Symbol                              | I/O | Electrical Interface                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------|-----|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A25                              | 1   | Pull-down<br>(250k Ω @ Vcc=5v)           | ADDRESS INPUTS: These are address bus lines which enable direct addressing of memory on the card. Signal A <sub>0</sub> is not used in word access mode. The system should NOT access memory beyond the card's density, because the upper addresses are not decoded.                                                                                                                                                                                                                                                                   |

| D0-D15                              | I/O | Pull-down<br>(250k Ω @ Vcc=5v)           | DATA INPUT/OUTPUT: Do through D <sub>15</sub> constitute the bi-directional data bus. D <sub>15</sub> is the most significant bit.                                                                                                                                                                                                                                                                                                                                                                                                     |

| CE <sub>1</sub> #,CE <sub>2</sub> # | 1   | Pull-up<br>(250k Ω @ Vcc=5v)             | CARD ENABLE 1 & 2:<br>CE <sub>1</sub> # enables D <sub>0</sub> -D <sub>7</sub> , CE <sub>2</sub> # enables D <sub>8</sub> -D <sub>15</sub> .                                                                                                                                                                                                                                                                                                                                                                                           |

| OE#                                 | 1   | Pull-up<br>(250k Ω @ Vcc=5v)             | OUTPUT ENABLE: Active low signal gating read data from the memory card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WE#                                 | 1   | Pull-up<br>(250k Ω @ Vcc=5v)             | WRITE ENABLE: Active low signal gating write data to the memory card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RDY/BSY#                            | 0   |                                          | READY/BUSY OUTPUT: Indicates status of internally timed erase or write activities. ID242 series has two types of Ready/Busy output mode; PCMCIA mode and High-Performance mode. In PCMCIA mode, a high output indicates the memory card is ready to accept accesses. A low output indicates that a device in the memory card is busy. In High-Performance mode, the card outputs low when the card is in default state. A high output indicates at least one of flash memory devices in the card comes to be ready to accept accesses. |

| CD#, CD2#                           | 0   | Pull-down 0W                             | CARD DETECT 1 & 2: These signals provide for card insertion detection. The signals are connected to ground internally on the memory card, and will be forced low whenever a card is placed in the socket. The host socket interface circuitry shall supply 10K or larger pull-up resistors on these signal pins.                                                                                                                                                                                                                       |

| WP                                  | 0   | Low:Pull-down 0W<br>High:Pull-up 100kW   | WRITE PROTECT: Write Protect reflects the status of the Write Protect switch on the memory card. WP set to high = write protected.                                                                                                                                                                                                                                                                                                                                                                                                     |

| VPP1, VPP2                          |     |                                          | WRITE/ERASE POWER SUPPLY 1 & 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vcc                                 |     |                                          | CARD POWER SUPPLY:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND                                 |     |                                          | GROUND:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REG#                                | I   | Pull-up<br>(250kW @Vcc=5v)               | REGISTER SELECT: Provides access to attribute memory when REG# is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RESET                               | 1   | Pull-up<br>(250kW @Vcc=5v)               | RESET: Active high signal for placing card in Power-On Default State.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BVD <sub>1</sub> , BVD <sub>2</sub> | 0   | Pull-up 100kW                            | BATTERY VOLTAGE DETECT 1 & 2:<br>These signals are pulled high to maintain SRAM card compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VS1#, VS2#                          | 0   | VS1#: Pull-down or<br>N.C.<br>VS2#: N.C. | VOLTAGE SENSE 1 & 2:<br>Notifies the host socket of the CIS's VCC requirements. VS 1# is pulled-down to ground when using the standard CIS, that indicate 3.3V operating is available. And when using the EEPROM for CIS, the VS2# is open. That indicate the available operation voltage is 5V only.                                                                                                                                                                                                                                  |

| RFU                                 |     |                                          | RESERVED FOR FUTURE USE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

T1039-01

#### 6. Functions

#### 6. 1 Common Memory

## 6. 1. 1 Common Memory Architecture

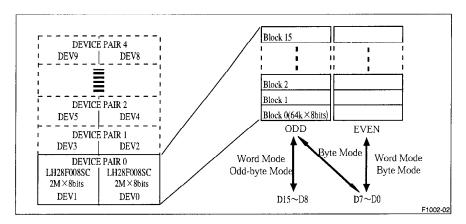

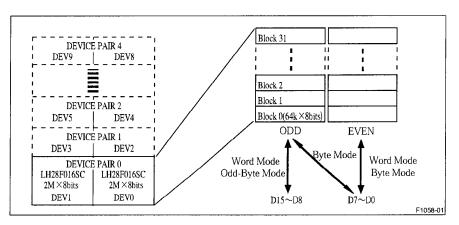

Figure 2 shows common memory architecture of ID242 series flash memory card. Device pair is consisted of two pieces of flash memory devices. Each device has individually erasable and lockable blocks. All blocks are divided into odd bytes and even bytes.

Each device pair and block is selected by address bits. Table 3 shows definitions of address bits.

(a) For 2, 4, 8, 10MB

(b) For 16MB, 20MB

Figure 2. Common Memory Architecture

Table 3. Address Difinitions

| Address Pifinitions                             | 2MB - 10MB   16MB , 20M |         |  |  |

|-------------------------------------------------|-------------------------|---------|--|--|

| Select Even / Odd byte in the byte access mode. | A0                      |         |  |  |

| Select address in the block.                    | A16~A1                  |         |  |  |

| Select a block.                                 | A20~A17                 | A21~A17 |  |  |

| Select a device pair.                           | A25~A21                 | A25~A22 |  |  |

T1051-01

#### 6. 1. 2 Erase

Erase is executed one block at a time. Erasable block size is 64K bytes in byte access mode and 128K bytes in word access mode.

#### 6. 1. 3 Address Decoding

The higher address area of ID242 series flash memory card which goes beyond common memory area is not decoded in common memory access. It means that the system will access to random memory address of the memory card even if system will try to access to the memory address which exceeds memory capacity of the card. Please do not access to the memory address which goes beyond memory capacity of the card.

As an enhanced function, the memory card enables to output invalid data (either of 0000h or FFFFh) when system will access to the memory address which exceeds memory capacity of the card. Please contact our sales & marketing support to find concrete way of setting.

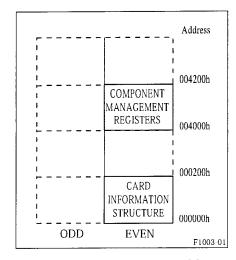

## 6. 2 Attribute Memory

Figure 3 shows attribute memory map of ID242 series flash memory card. Attribute memory is contained within the Card Control Logic. Attribute memory contains the Card Information Structure (CIS) and Component Management Registers (CMRs). The CIS contains tuple information and is located at even byte addresses beginning with address 0000h (Please refer to section 7). The standard CIS of ID242 series flash memory card is hardwired and is for read only. As an enhanced function, the hardwired CIS area is switchable to EEPROM so that customer can program required CIS. Please contact our sales & marketing support to find concrete way of setting. The CMRs are located at even byte addresses beginning with address 4000h (Please refer to section 9).

Figure 3. Attribute Memory Map

## 6.3 Function Table

## 6.3.1 Common Memory Access

Table 4. Common Memory Access

| Mode           | REG# | CE <sub>2</sub> # | CE <sub>1</sub> # | $A_{0}$ | OE# | WE# | D <sub>15-8</sub> | D <sub>7-0</sub> |

|----------------|------|-------------------|-------------------|---------|-----|-----|-------------------|------------------|

| Stand-by       | X    | Н                 | Н                 | X       | X   | X   | High-Z            | High-Z           |

| D . D . I      | Н    | Н                 | L                 | L       | L   | Н   | High-Z            | Even             |

| Byte Read      | Н    | Н                 | L                 | Н       | L   | Н   | High-Z            | Odd              |

| Word Read      | Н    | L                 | L                 | X       | L   | Н   | Odd               | Even             |

| Odd Byte Read  | Н    | L                 | Н                 | X       | L   | Н   | Odd               | High-Z           |

| Data Waita     | Н    | Н                 | L                 | L       | Н   | L   | Don't care        | Even             |

| Byte Write     | Н    | Н                 | L                 | Н       | Н   | L   | Don't care        | Odd              |

| Word Write     | Н    | L                 | L                 | X       | Н   | L   | Odd               | Even             |

| Odd Byte write | Н    | L                 | Н                 | X       | Н   | L   | Odd               | Don't care       |

## 6.3.2 Attribute Memory Access

Table 5. Attribute Memory Access

| Mode           | REG# | CE <sub>2</sub> # | CE <sub>1</sub> # | $A_0$ | OE# | WE# | D <sub>15~8</sub> | D <sub>7-0</sub> |

|----------------|------|-------------------|-------------------|-------|-----|-----|-------------------|------------------|

| Stand-by       | X    | Н                 | Н                 | X     | X   | X   | High-Z            | High-Z           |

| D. A. D I      | L    | Н                 | L                 | L     | L   | Н   | High-Z            | Even             |

| Byte Read      | L    | Н                 | L                 | Н     | L   | Н   | High-Z            | XXX              |

| Word Read      | L    | L                 | L                 | X     | L   | Н   | XXX               | Even             |

| Odd Byte Read  | L    | L                 | Н                 | X     | L   | Н   | XXX               | High-Z           |

| D              | L    | Н                 | L                 | L     | Н   | L   | Don't care        | Even             |

| Byte Write     | L    | Н                 | L                 | Н     | Н   | L   | Don't care        | Don't care       |

| Word Write     | L    | L                 | L                 | X     | Н   | L   | Don't care        | Even             |

| Odd Byte write | L    | L                 | Н                 | X     | Н   | L   | Don't care        | Don't care       |

XXX:Output data is invalid.

The standard CIS is for read only. Write operation is only for CMRs and CIS on EEPROM

## 7. Card Information Structure (CIS)

The CIS is contained within attribute memory (Please refer to section 6.2). Table 6 shows standard CIS tuples, but it is for read only. As an enhanced function, the hardwired CIS area is switchable to EEPROM so that customer can program required CIS. Please contact our sales & marketing support to find concrete way of setting.

Table 6. Standard CIS

| Address | Value      | Description                                     |

|---------|------------|-------------------------------------------------|

| 00h     | 01h        | Device Info (Common Memory)                     |

| 02h     | 04h        | Tuple Link                                      |

| 04h     | 57h        | Flash Memory                                    |

| 06h     | 22h        | Access Time 150ns                               |

|         |            | Capacity                                        |

|         | 06h        | 2MB                                             |

| 001     | 0Eh<br>1Eh | 4MB<br>8MB                                      |

| 08h     | 26h        | 10MB                                            |

|         | 3Eh        | 16MB                                            |

|         | 4Eh        | 20MB                                            |

| 0Ah     | FFh        | End of Tuple                                    |

| 0Ch     | 1Ch        | Device Info (Common Memory<br>Other Conditions) |

| 0Eh     | 05h        | Tuple Link                                      |

| 10h     | 02h        | Conditions 3Vcc                                 |

| 12h     | 57h        | Flash Memory                                    |

| l4h     | 32h        | Access Time 250ns                               |

|         |            | Capacity                                        |

|         | 06h        | 2MB                                             |

| 16h     | 0Eh<br>1Eh | 4MB<br>8MB                                      |

| 1011    | 26h        | 10MB                                            |

|         | 3Eh        | 16MB                                            |

|         | 4Eh        | 20MB                                            |

| 18h     | FFh        | End of Tuple                                    |

| l Ah    | 17h        | Device Info ID<br>(Attribute Memory)            |

| 1Ch     | 04h        | Tuple Link                                      |

| 1Eh     | 1Fh        | ROM                                             |

| 20h     | 2Ah        | Access Time 200ns                               |

| 22h     | 01h        | Capacity 2KB                                    |

| 24h     | FFh        | End of Tuple                                    |

| 26h     | 1Dh        | Device Info ID (Attribute Memory)               |

| 28h     | 05h        | Tuple Link                                      |

| 2Ah     | 02h        | Conditions 3Vcc                                 |

| 2Ch     | 17h        | ROM                                             |

| 2Eh     | 2Ah        | Access Time 200ns                               |

| 30h     | 01h        | Capacity 2KB                                    |

| 32h     | FFh        | End of Tuple                                    |

| 34h     | 18h        | JEDEC Code ID                                   |

| 36h     | 02h        | Tuple Link                                      |

| 38h     | 89h        | Manufacture Code                                |

| 3Ah     | A6h        | Device Code                                     |

| 3Ch     | 00h        | End of Tuple                                    |

| 3Eh     | 15h        | Version Info Level 1                            |

| 40h     | 23h        | Tuple Link                                      |

| 42h     | 04h        | Major Version                                   |

| 44h     | 01h        | Minor Version                                   |

|         | 7111       |                                                 |

| Address | Value | Description                       |

|---------|-------|-----------------------------------|

| 46h     | 53h   | S :Product Info                   |

| 48h     | 48h   | H                                 |

| 4Ah     | 41h   | A                                 |

| 4Ch     | 52h   | R                                 |

| 4Eh     | 50h   | p                                 |

|         |       | END TEXT                          |

| 50h     | 00h   |                                   |

| 52h     | 49h   | I                                 |

| 54h     | 44h   | D                                 |

| 56h     | 32h   | 2                                 |

| 58h     | 34h   | 4                                 |

| 5Ah     | 53h   | S                                 |

| 5Ch     | 52h   | R                                 |

| 5Eh     | 20h   | SPACE                             |

| 60h     | 00h   | END TEXT                          |

| 62h     | 53h   | S :Maker Info                     |

| 64h     | 48h   | Н                                 |

| 66h     | 41h   | A                                 |

| 68h     | 52h   | R                                 |

| 6Ah     | 50h   | P                                 |

| 6Ch     | 20h   | SPACE                             |

| 6Eh     | 43h   | C                                 |

| 70h     | 4Fh   | 0                                 |

| 72h     | 52h   | R                                 |

| 74h     | 50h   | P                                 |

| 76h     | 4Fh   | 0                                 |

| 78h     | 52h   | R                                 |

| 7Ah     | 41h   | A                                 |

| 7Ch     | 54h   | T                                 |

| 7Eh     | 49h   | I                                 |

| 80h     | 4Fh   | 0                                 |

| 82h     | 4Eh   | N                                 |

| 84h     | 00h   | END TEXT                          |

| 86h     | FFh   | End of Tuple                      |

| 88h     | 1Ah   | Configuration Info                |

| 8Ah     | 05h   | Tuple Link                        |

| 8Ch     | 01h   | 2 Bytes Field                     |

| 8Eh     | 06h   | Last Index of Configuration Table |

| 90h     | 00h   | CMRs Base Adress(LSB)             |

| 92h     | 40h   | CMRs Base Adress(MSB)             |

| 94h     | 0Bh   | CMR Mask                          |

| 96h     | 00h   | Null                              |

| 98h     | 1Bh   | Configuration Table Entry 1       |

| 9Ah     | 0Fh   | Tuple Link                        |

| 9Ch     | 01h   | Index                             |

| 9Eh     | 02h   | Vcc & Vpp                         |

| A0h     | 79h   | Parameter Selection               |

| A2h     | 55h   | Vcc Voltage 5V                    |

|         |       | CP50002 0004                      |

Table 8. Standard CIS (Continued)

| Address | Value | Description                 |

|---------|-------|-----------------------------|

| A4h     | 0Ch   | Icc Static 1.2mA            |

| A6h     | 06h   | Icc Average 100mA           |

| A8h     | 06h   | Icc Peak 100mA              |

| AAh     | 23h   | Icc Powerdown 50mA          |

| ACh     | 79h   | Parameter Selection         |

| AEh     | D5h   | Vpp Voltage 5V              |

| B0h     | 7Dh   | NC OK                       |

| B2h     | 1Bh   | Ipp Static 150mA            |

| B4h     | 75h   | Ipp Average 80mA            |

| B6h     | 75h   | Ipp Peak 80mA               |

| B8h     | 52h   | Ipp Powerdown 50mA          |

| BAh     | 1Bh   | Configuration Table Entry 2 |

| BCh     | 0Fh   | Tuple Link                  |

| BEh     | 02h   | Index                       |

| C0h     | 02h   | Vcc & Vpp                   |

| C2h     | 79h   | Parameter Selection         |

| C4h     | 55h   | Vcc Voltage 5V              |

| C6h     | 0Ch   | Icc Static 1.2mA            |

| C8h     | 06h   | Icc Average 100mA           |

| CAh     | 06h   | Icc Peak 100mA              |

| CCh     | 23h   | Icc Powerdown 50mA          |

| CEh     | 79h   | Parameter Selection         |

| D0h     | 8Eh   | Vpp Voltage 12V             |

| D2h     | 7Dh   | NC OK                       |

| D4h     | 1Bh   | Ipp Static 150mA            |

| D6h     | 35h   | Ipp Average 30mA            |

| D8h     | 35h   | Ipp Peak 30mA               |

| DAh     | 52h   | Ipp Powerdown 50mA          |

| DCh     | 1Bh   | Configuration Table Entry 3 |

| DEh     | 11h   | Tuple Link                  |

| E0h     | 03h   | Index                       |

| E2h     | 02h   | Vcc & Vpp                   |

| E4h     | 79h   | Parameter Selection         |

| E6h     | B5h   | Vcc Voltage 3.3V            |

| E8h     | 1Eh   |                             |

| EAh     | 0Ch   | Icc Static 1.2mA            |

| ECh     | 7Dh   | Icc Average 90mA            |

| EEh     | 7Dh   | Icc Peak 90mA               |

| F0h     | 1Bh   | Icc Powerdown 150mA         |

| F2h     | 79h   | Parameter Selection         |

| F4h     | B5h   | Vpp Voltage 3.3V            |

| F6h     | 9Eh   |                             |

| FAh     | 1Bh   | Ipp Static 150mA            |

| FCh     | 75h   | Ipp Average 80mA            |

| FEh     | 75h   | Ipp Peak 80mA               |

| 100h    | 52h   | Ipp Powerdown 50mA          |

| 102h    | 1Bh   | Configuration Table Entry 4 |

|         | CIS (Continued)                        |                                               |  |  |  |  |  |

|---------|----------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Address | Value                                  | Description                                   |  |  |  |  |  |

| 104h    | 10h                                    | Tuple Link                                    |  |  |  |  |  |

| 106h    | 04h                                    | Index                                         |  |  |  |  |  |

| 108h    | 02h                                    | Vcc & Vpp                                     |  |  |  |  |  |

| 10Ah    | 79h                                    | Parameter Selection                           |  |  |  |  |  |

| 10Ch    | B5h                                    | Vcc Voltage 3.3V                              |  |  |  |  |  |

| 10Eh    | 1Eh                                    | vec voltage 5.5 v                             |  |  |  |  |  |

| 110h    | 0Ch                                    | Ice Static 1.2mA                              |  |  |  |  |  |

| 112h    | 7Dh                                    | Icc Average 90mA                              |  |  |  |  |  |

| 114h    | 7Dh                                    | Ice Peak 90mA                                 |  |  |  |  |  |

| 116h    | 1Bh                                    | Icc Powerdown 150mA                           |  |  |  |  |  |

| 118h    | 79h                                    | Parameter Selection                           |  |  |  |  |  |

| 11Ah    | 8Eh                                    | Vpp Voltage 12V                               |  |  |  |  |  |

| 11Ch    | 7Dh                                    | NC OK                                         |  |  |  |  |  |

| 11Eh    | 1Bh                                    | Ipp Static 150mA                              |  |  |  |  |  |

| 120h    | 35h                                    | Ipp Average 30mA                              |  |  |  |  |  |

| 122h    | 35h                                    | Ipp Peak 30mA                                 |  |  |  |  |  |

| 124h    | 52h                                    | Ipp Powerdown 50mA                            |  |  |  |  |  |

| 126h    | 00h                                    | Null                                          |  |  |  |  |  |

| 128h    | 00h                                    | Null                                          |  |  |  |  |  |

| 12Ah    | 1Eh                                    | Device Geometry                               |  |  |  |  |  |

| 12Ch    | 06h                                    | Tuple Link                                    |  |  |  |  |  |

| 12Eh    | 02h                                    | Bus: 2bytes                                   |  |  |  |  |  |

| 130h    | l lh                                   | Erase Block: 64Kbytes                         |  |  |  |  |  |

| 132h    | 01h                                    | Read size: 1byte                              |  |  |  |  |  |

| 134h    | 01h                                    | Write size: 1byte                             |  |  |  |  |  |

| 136h    | 01h                                    | Partation: 1block                             |  |  |  |  |  |

| 138h    | 01h                                    | Non-interleaved                               |  |  |  |  |  |

| 13Ah    | 20h                                    | Manufacturer ID                               |  |  |  |  |  |

| 13Ch    | 04h                                    | Tuple Link                                    |  |  |  |  |  |

| 13Eh    | B0h                                    | Manufacturer Code                             |  |  |  |  |  |

| 140h    | 00h                                    | Traditional Code                              |  |  |  |  |  |

| 142h    | 06h<br>07h<br>09h<br>0Ah<br>0Dh<br>0Eh | Manufacturer Info: 2MB 4MB 8MB 10MB 16MB 20MB |  |  |  |  |  |

| 144h    | 33h                                    | Manufacturer Info: DVO                        |  |  |  |  |  |

| 146h    | 21h                                    | Function Identification                       |  |  |  |  |  |

| 148h    | 02h                                    | Tuple Link                                    |  |  |  |  |  |

| 14Ah    | 01h                                    | Function: MEMORY                              |  |  |  |  |  |

| 14Ch    | 00h                                    | System Init: None                             |  |  |  |  |  |

| 14Eh    | FFh                                    | End of CIS                                    |  |  |  |  |  |

|         |                                        | · · · · · · · · · · · · · · · · · · ·         |  |  |  |  |  |

CPS0002-002@May.1998

#### 8. Card Control

#### 8.1 Reset

The card is in initial state directly after power-up. But we recommend to do reset operation after power-up to make sure to initialize the card.

During block erase, byte write, or lock-bit configuration modes, an active RESET will abort the operation. RDY/BSY# remains low until the reset operation completes. Memory contents being altered are no longer valid; the data may be partially erased or written. The host must wait after RESET goes to logic-Low  $(V_{IL})$  before it can write another command, as determined by  $t_{PHWL}$ .

It is important to assert RESET to the card during a system reset. If a CPU reset occurs without a card reset, the host will not be able to read from the card if that card is in a different mode when the system reset occurs.

For example, if an end-user initiates a host reset when the card is in read status register mode, the host will attempt to read code from the card, but will actually read status register data. Sharp's ID242 Series Flash Memory Card allows proper card reset following a system reset through the use of the RESET input.

#### 8. 2 Status Register

Each flash memory device in the card has status register. The status register may be read to determine when a write, block erase, or lock-bits configuration is complete, and whether that operation completed successfully (please refer to Table 10). It may be read at any time by writing the Read Status Register command (70h, 7070h) into the CUI. In word access mode, the status register data of even byte devices are output to D7~0, and the status register data of odd byte devices are output to D15~8.

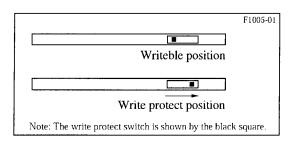

## 8. 3 Write Protect Switch

The ID242 Series Flash Memory Card has a write protect switch on the back of the card. When the switch is in the write protect position, the card blocks all writes to the common and attribute memory without Card Management Registers region (see Figure 5).

#### 8. 4 Read Identifier Codes / Lock bits Information

Manufacture Code and Device Code are contained within each flash memory device in the memory card. The identifier code operation is initiated by writing the Read Identifier Codes command (90h, 9090h) into the CUI of each memory device. The specific address of each device is necessary to be selected to read these codes (Table 8).

Figure 4. Write Protect Switch

| bit7 | bit6 | bit5  | bit4   | bit3 | bit2 | bit1 | bit0 |

|------|------|-------|--------|------|------|------|------|

| SR.7 | SR.6 | SR.5  | SR.4   | SR.3 | SR.2 | SR.1 | SR.0 |

| WSMS | ESS  | ECLBS | BWSLBS | VPPS | BWSS | DPS  | RFU  |

#### SR.7 = WRITE STATE MACHINE STATUS

1 = Readv

0 = Busy

#### SR.6 = ERASE-SUSPEND STATUS

1 = Erase Suspended

0 = Erase in Progress/Completed

#### SR.5 = ERASE AND CLEAR LOCK-BITS STATUS

1 = Error In Block Erasure or Clear Lock-Bits

0 = Successful Block Erase or Clear Lock-Bits

## SR.4 =BYTE WRITE AND SET LOCK-BIT STATUS

1 = Error in Byte Write or Set Block/Master Lock-Bit

0 = Successful Byte Write or Set Block/Master Lock-Bit

#### SR.3 = VPP STATUS

1 = VPP Low Detect, Operation Abort

0 = VPP OK

#### SR.2 =BYTE WRITE SUSPEND STATUS

1 = Byte Write Suspended

0 = Byte Write in Progress/Completed

#### SR.1 =DEVICE PROTECT STATUS

1 = Master Lock-bit,Block Lock-bit and/or RP# Lock Detected, Operation Abort

0 = Unlock

SR.0 =Reserved for Future Enhancements

#### Notes:

Chech RDY/BSY# or SR.7 to determine block erase, word/byte write, or lock-bit configuration completion. SR.6-0 are invalid while SR.7="0".

If both SR.5 and SR.4 are "1"s after a block erase or lockbit configuration attempt, an improper command sequence was entred.

SR.3 does not provide a continuous indication of  $V_{PP}$  level. The WSM interrogates and indicates the  $V_{PP}$  level only after Block Erase, Word/Byte Write, Set Block/Master Lock-bit, or Clear Lock-bits command sequences. SR.3 is not guaranteed to reports accurate feedback only when  $V_{PP} = V_{PPH1/2/3}$ .

SR.1 does not provide a continuous indication of master and block lock-bit values. The WSM interrogates the master lock-bit, block lock-bit, and RP# only after Block Erase, Word/Byte Write, or Lock-bit configuration command sequences. If informs the system, depending on the attempted operation, if the block lock-bit is set, master lock-bit is set, and/or RP# is not 12V. Reading the block lock and master lock configuration codes after writing the Read Identifier Codes command indicates master and block lock-bit status.

SR.0 is reserved for future use and should be masked out when polling the status register.

Table 8. Identifier Codes / Lock bits

|                                | Select Device-pair | Address in Device | Even/Odd        | Data Outp            | out D7-D0  |  |

|--------------------------------|--------------------|-------------------|-----------------|----------------------|------------|--|

|                                | A25-A21            | A20-A1            | A0              | 2MB - 10MB           | 16MB, 20MB |  |

| Manufacture Identifier<br>Code | DPA                | 00000h            | 0:Even<br>1:Odd | 89h                  | 89h        |  |

| Device Identifier Code         | DPA                | 00001h            | 0:Even<br>1:Odd | A6h                  | AAh        |  |

| Block Lock                     |                    | X0002h            | 0:Even          | BLKD                 |            |  |

| Configuration                  | DPA                | (X: Select Block) | 1:Odd           | D0: 0=Unlock, 1=Lock |            |  |

| Ü                              |                    |                   |                 | D7-D1: Reserved      | i          |  |

| Master Lock                    |                    |                   | 0:Even          | MLKD                 |            |  |

| Configuration                  | DPA                | 00003h            | 1:Odd           | D0: 0=Unlock, 1      |            |  |

|                                |                    |                   |                 | D7-D1: Reserved      | 1          |  |

NOTE: A0 is ignored in word access mode, and D15-D8 outputs the Odd byte data.

T1052-01

DPA: Address as select device pair BLKD: Block Lock Configuration Data MLKD: Master Lock Configuration Data

## 9. Component Management Registers (CMR)

Component Management Registers (CMR) are mapped at even byte locations beginning at address 4000h in attribute memory.

## 9. 1 Configuration Option Register (Address:4000h)

|   | Address | Bit.7   | Bit.6       | Bit.5                         | Bit.4 | Bit.3    | Bit.2 | Bit.1 | Bit.0 |  |  |

|---|---------|---------|-------------|-------------------------------|-------|----------|-------|-------|-------|--|--|

| ſ | 4000h   | SRESET  |             |                               |       | Reserved | •     |       |       |  |  |

| ſ |         | SRESET: | 1=Reset Sta | Reset State 0=End Reset Cycle |       |          |       |       |       |  |  |

## 9. 2 Card Configuration Register (Address:4002h)

| Address | Bit.7 | Bit.6                                          | Bit.5         | Bit.4       | Bit.3        | Bit.2         | Bit.1        | Bit.0    |

|---------|-------|------------------------------------------------|---------------|-------------|--------------|---------------|--------------|----------|

| 4002h   |       |                                                | Reserved      |             |              | PWDN          | Rese         | erved    |

|         | PWDN: | 1=Power-D<br>Device pair<br>Down.<br>0=Power-U | s that apoint | ed by Sleep | Control Regi | ister(4118h-4 | 11Ah) are ii | ı Power- |

## 9. 3 Socket and Copy Register (Address:4006h)

| Address                           | Bit.7     | Bit.6                                    | Bit.5 | Bit.4        | Bit.3          | Bit.2         | Bit.1 | Bit.0 |

|-----------------------------------|-----------|------------------------------------------|-------|--------------|----------------|---------------|-------|-------|

| 4006h Reserved Copy No. Soket No. |           |                                          |       |              |                |               |       | ·     |

|                                   | Copy No.: | Socket Nun<br>Copy Numb<br>ay use to dis | oer   | veen similar | cards installe | ed in a syste | m.    |       |

T1053-01

## 9. 4 Card Status Register (Address:4100h)

| Address | Bit.7 | Bit.6 | Bit.5  | Bit.4 | Bit.3 | Bit.2 | Bit.1 | Bit.0   |

|---------|-------|-------|--------|-------|-------|-------|-------|---------|

| 4100h   | ADM   | ADS   | SRESET | CMWP  | PWDN  | CISWP | WP    | RDY/BSY |

ADM: ORed value of the Ready/Busy Mask Register.

1 =Any device is masked. 0 =All Devices are not Masked.

ADS: ORed value of the Sleep Control Register.

1 = Any device-pair is Controled power-down by bit.2 of the Card Configuration Register.

SRESET: Reflects the bit.7 of the Configuration Option Register.

CMWP: Reflects the bit.1 of the Write Protection Register.

PWDN: Reflects the bit.2 of the Card Configuration Register.

CISWP: Reflects the bit.0 of the Write Protection Register.

WP: Indicates the Write Protect Switch status.

1 = Write Protect Switch: ON 1 = Write Protect Switch: OFF

RDY/BSY: Reflects the Ready/Busy Status Register.

1 = All devices are READY. 0 = Any device is BUSY.

T1054-01

## 9. 5 Write Protection Register (Address:4104h)

| Address | Bit.7 | Bit.6 | Bit.5    | Bit.4 | Bit.3 | Bit.2 | Bit.1 | Bit.0 |

|---------|-------|-------|----------|-------|-------|-------|-------|-------|

| 4104h   |       |       | Reserved |       |       | BLKEN | CMWP  | CISWP |

BLKEN: Block Locking Enable

1 = Enable Block Locking 0 = All Blocks Unlocked

CMWP: Common Memory Write Protect

1 = Common Memory without CIS region in Write Protect Status

CISWP: Common Memory CIS Write Protect

1 = Common Memory CIS in Write Protect Status

NOTE: ID242 series ignores BLKEN bit. Block Locking is always enable.

## 9. 6 Sleep Control Register (Address:4118h~411Ah)

| Address | Bit.7                                                                                                                                                             | Bit.6 | Bit.5    | Bit.4  | Bit.3  | Bit.2  | Bit.1  | Bit.0  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|--------|--------|--------|--------|--------|--|--|

| 411Ah   |                                                                                                                                                                   |       |          | Rese   | erved  |        |        |        |  |  |

| 4118h   | Rese                                                                                                                                                              | rved  | DEV10/11 | DEV8/9 | DEV6/7 | DEV4/5 | DEV2/3 | DEV0/1 |  |  |

|         | 1= Select sleep mode device-pair If set to "1", the corresponding device-pairs are putted into deep power-down mode by PWDN bit of Configuration Status Register. |       |          |        |        |        |        |        |  |  |

T1047-01

## 9. 7 Ready/Busy Mask Register (Address:4120h~4122h)

| Address | Bit.7 | Bit.6 | Bit.5 | Bit.4 | Bit.3          | Bit.2          | Bit.1         | Bit.0 |

|---------|-------|-------|-------|-------|----------------|----------------|---------------|-------|

| 4122h   |       | Rese  | erved |       | DEV11          | DEV10          | DEV9          | DEV8  |

| 4120h   | DEV7  | DEV6  | DEV5  | DEV4  | DEV3           | DEV2           | DEV1          | DEV0  |

|         |       |       | _     |       | # signals to s | et bit are ign | ored for card | 's    |

T1040-01

## 9. 8 Ready/Busy Status Register (Address:4130h~4132h)

| Address                                                                       | Bit.7 | Bit.6 | Bit.5 | Bit.4 | Bit.3 | Bit.2 | Bit.1 | Bit.0 |

|-------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 4132h                                                                         |       | Rese  | erved |       | DEV11 | DEV10 | DEV9  | DEV8  |

| 4130h                                                                         | DEV7  | DEV6  | DEV5  | DEV4  | DEV3  | DEV2  | DEV1  | DEV0  |

| 1=READY 0=BUSY Each bit indicates the corresponding device's Rdy/Bsy# signal. |       |       |       |       |       |       |       |       |

T1041-01

## 9. 9 Ready/Busy Mode Register (Address:4140h)

| Address | Bit.7 | Bit.6 | Bit.5 | Bit.4 | Bit.3 | Bit.2 | Bit.1 | Bit.0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 4140h   |       |       |       | rved  |       |       | RACK  | MODE  |

RACK: Ready Acknowledge Bit

Must clear this bit after receiving ready status to prepare for next device's ready

transition.

MODE: RDY/BSY# Mode

1 = High-Performance Mode 0 = PCMCIA Mode

T1055-01

#### 10. Command Definitions

Device operations are determined by writing specific commands to the Command User Interface. Table 9 defines the commands.

Table 9. Command Definitions

| C1                                         | Note | Fi        | rst Bus Cy | cle                                    | Sec       | ond Bus C | ycle           |

|--------------------------------------------|------|-----------|------------|----------------------------------------|-----------|-----------|----------------|

| Command                                    | Note | Operation | Address    | Data                                   | Operation | Address   | Data           |

| Read Array / Reset                         |      | Write     | DA         | FFh<br>(FFFFh)                         | -         | -         | -              |

| Read Identifier Codes                      | 1    | Write     | DA         | 90h<br>(9090h)                         | Read      | IA        | ID             |

| Read Status Register                       | 2    | Write     | DA         | 70h<br>(7070h)                         | Read      | DA        | SRD            |

| Clear Status Register                      |      | Write     | DA         | 50h<br>(5050h)                         | -         | -         | -              |

| Word/Byte Write                            | 3    | Write     | WA         | 40h<br>(4040h)<br>or<br>10h<br>(1010h) | Read      | WA        | WD             |

| Block Erase                                | 3    | Write     | BA         | 20h<br>(2020h)                         | Write     | BA        | D0h<br>(D0D0h) |

| Block Erase and Word/Byte Write<br>Suspend | 3    | Write     | DA         | B0h<br>(B0B0h)                         | -         | -         | -              |

| Block Erase and Word/Byte Write<br>Resume  | 3    | Write     | DA         | D0h<br>(D0D0h)                         | -         | -         | -              |

| Set Block Lock-Bit                         |      | Write     | BA         | 60h<br>(6060h)                         | Write     | BA        | 01h<br>(0101h) |

| Set Master Lock-Bit                        | 4    | Write     | DA         | 60h<br>(6060h)                         | Write     | DA        | Flh<br>(F1F1h) |

| Clear Block Lock-Bit                       |      | Write     | DA         | 60h<br>(6060h)                         | Write     | DA        | D0h<br>(D0D0h) |

Address Data

IA =Identifier code Address ID =Identifier Codes

WA =Write Address WD =Write Data

BA =Block Address SRD =Data from Status Register

DA =Device Address

## Note:

- 1. Following the Read Identifier Codes command, read operations access manufacture, device, block lock, and master lock codes.

- 2. Status Register may be read to determine when a write, block erase, or lock bit configuration is complete, and whether that operation completed successfully.

- 3. If the block is locked, block erase or write operations are desabled.

- 4. This command is not available.

## 11. Electrical Specifications

#### 11. 1 Absolute Maximum Ratings

| PARAMETER             | NOTE | SYMBOL           | RATING                   | UNIT |

|-----------------------|------|------------------|--------------------------|------|

| Supply Voltage        | 2    | V <sub>cc</sub>  | -0.3 to 6.0              | V    |

| Program Voltage       | 2    | V <sub>PP</sub>  | -2.0 to 14.0             | V    |

| Input Voltage         | 2    | V <sub>IN</sub>  | -0.3 to Vcc+0.3(Max:6.0) | V    |

| Operating Temperature | 1    | T <sub>OPR</sub> | 0 to 60                  | ℃    |

| Storage Temperature   |      | T <sub>stg</sub> | -20 to 65                | °C   |

## NOTES:

- 1. Operating temperature is for commercial product defined by this specification.

- 2. All specified voltages are with respect to GND. During transitions, this level may undershoot to -2.0v for periods <20ns or overshoot to Vcc+2.0v for periods <20ns.

## 11.2 Recommended Operating Conditions

| PARAMETER             | NOTE | SYMBOL           | MIN  | MAX  | UNIT                   |

|-----------------------|------|------------------|------|------|------------------------|

|                       |      | V <sub>cci</sub> | 3.0  | 3.6  | V                      |

| Supply Voltage        |      | V <sub>cc2</sub> | 4.75 | 5.25 | V                      |

|                       |      | V <sub>CC3</sub> | 4.5  | 5.5  | V                      |

|                       |      | $V_{pp_1}$       | 3.0  | 3.6  | V                      |

| Program Voltage       |      | V <sub>PP2</sub> | 4.5  | 5.5  | V                      |

|                       |      | $V_{PP3}$        | 11.4 | 12.6 | V                      |

| Operating Temperature |      | T <sub>OPR</sub> | 0    | 60   | $^{\circ}\!\mathbb{C}$ |

## 11.3 Capacitance

Ta=25 $^{\circ}$ C, f=1MHz

| PARAMETER                | SYMBOL          | MIN | TYP | MAX | UNIT | CONDITION        |

|--------------------------|-----------------|-----|-----|-----|------|------------------|

| Input Capacitance        | C <sub>IN</sub> | -   | 15  | -   | pF   | $V_{IN}=0.0V$    |

| Input/Output Capacitance | C <sub>io</sub> | -   | 25  | ·-  | pF   | $V_{OUT} = 0.0V$ |

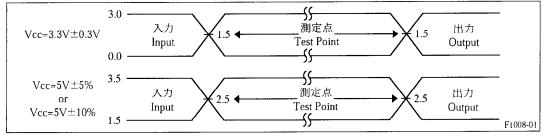

## 11. 4 AC Input/Output Test Conditions

Figure 5. Transient Input/Output Reference Waveform

Figure 8 shows Input/Output level and test level for AC test. Input rise and fall times (10% to 90%) < 10 ns.

## 12. DC Characteristics

$(Ta = 0 \text{ to } 60^{\circ}C)$

|                                                    | ,                      | <del>,</del> | ,            | 1       |         |     |                           |      | T                                                      |

|----------------------------------------------------|------------------------|--------------|--------------|---------|---------|-----|---------------------------|------|--------------------------------------------------------|

| PARAMETER                                          | SYM-<br>BOL            | NO-<br>TE    | Densi-<br>ty | Vcc=3.3 | V± 0.3V |     | $V\pm~5\%$<br>$V\pm~10\%$ | UNIT | TEST CONDITION                                         |

|                                                    | BOL                    | I LE         | Ly           | MIN     | MAX     | MIN | MAX                       |      |                                                        |

| Input Low Voltage                                  | VIL                    | 1            |              |         | 0.3Vcc  |     | 1.5                       | V    |                                                        |

| Input High Voltage                                 | $V_{IH}$               | 1            |              | 0.7Vcc  |         | 3.5 |                           | V    |                                                        |

| I I C                                              | $-I_{_{\mathrm{IL}1}}$ | 2            |              |         | ± 2.0   |     | ± 2.0                     | μΑ   | $V_I = 0V$                                             |

| Input Low Current                                  | $-I_{_{\rm IL2}}$      | 3            |              | 2.0     | 30.0    | 8.0 | 60.0                      | μΑ   | $V_1 = 0V$                                             |

| Input High Current                                 | I                      | 3            |              |         | ± 2.0   |     | ± 2.0                     | μΑ   | $V_I = Vcc$                                            |

| input riigh Current                                | $I_{_{\mathrm{IH2}}}$  | 2            |              | 2.0     | 30.0    | 8.0 | 60.0                      | μΑ   | $V_I = Vcc$                                            |

| Output Low Voltage                                 | Voli                   | 4,5          |              |         | -       |     | 0.4                       | V    | Iol = 6mA                                              |

| Output Low Voltage                                 | VOLI                   | 4,5          |              |         | 0.4     |     | -                         | V    | $I_{OL} = 3mA$                                         |

|                                                    | <b>3</b> 7             | 4            |              | -       |         | 4.0 |                           | V    | $I_{OH} = -3mA$                                        |

| 0                                                  | Vohi                   | 4            |              | Vcc-0.5 |         | -   |                           | V    | Iон = -1.5mA                                           |

| Output High Voltage                                | 17                     | 5            |              | -       |         | 4.0 |                           | V    | Іон = -6mA                                             |

|                                                    | V <sub>OH2</sub>       | )            |              | Vcc-0.5 |         | -   |                           | V    | I <sub>он</sub> = -3mA                                 |

|                                                    |                        |              | 2MB          |         | 240     |     | 240                       | μΑ   |                                                        |

|                                                    |                        |              | 4MB          |         | 450     | -   | 450                       | μΛ   |                                                        |

| Von Stand by Compart                               | ,                      | _            | 8MB          |         | 850     |     | 850                       | μА   | $CE_1$ #, $CE_2$ #= $Vcc$<br>$A_0 \sim A_{25}$ = $GND$ |

| Vcc Stand-by Current I <sub>Cc</sub>               | 1 <sub>ccs</sub>       | 6            | 10MB         |         | 1050    |     | 1050                      | μА   | I <sub>out=0mA</sub>                                   |

|                                                    |                        |              | 16MB         |         | 850     |     | 850                       | μΑ   |                                                        |

|                                                    |                        |              | 20MB         |         | 1050    |     | 1050                      | μΑ   |                                                        |

|                                                    |                        |              | 2MB          |         | 45      |     | 75                        | μΑ   |                                                        |

|                                                    |                        |              | 4MB          |         | 70      |     | 110                       | μΑ   | RESET=Vcc                                              |

| Vcc Deep Power-Down                                | l <sub>T</sub>         | 6            | 8MB          |         | 120     |     | 170                       | μΑ   | CE <sub>1</sub> #,CE <sub>2</sub> #=Vcc                |

| Current                                            | I <sub>CCD</sub>       | U            | 10MB         |         | 145     |     | 205                       | μА   | A <sub>0</sub> ~A <sub>25</sub> =GND                   |

|                                                    |                        |              | 16MB         |         | 185     |     | 205                       | μΑ   | I <sub>out=0mA</sub>                                   |

|                                                    |                        |              | 20MB         |         | 225     |     | 250                       | μΑ   |                                                        |

| Vcc Read Current                                   | I <sub>CCR</sub>       | 6,8          |              |         | 90      |     | 100                       | mA   | CE <sub>1</sub> #,CE <sub>2</sub> #=GND<br>Iout=0mA    |

|                                                    |                        |              |              |         | 35      |     | -                         | mA   | $V_{PP} = 3.3V \pm 0.3V$                               |

| Vcc Word Write or Set Lock-Bit Current             | I <sub>ccw</sub>       | 6,9          |              |         | 35      |     | 75                        | mA   | $V_{PP}=5.0V\pm 10\%$                                  |

| Lock-Dit Cuitent                                   |                        |              |              |         | 25      |     | 65                        | mA   | Vpp=12.0V ± 5%                                         |

|                                                    |                        |              |              |         | 35      |     | -                         | mA   | $V_{PP} = 3.3 V \pm 0.3 V$                             |

| Vcc Block Erase or Clear Lock-Bit Current          | I <sub>CCE</sub>       | 6,9          |              |         | 35      |     | 65                        | mA   | $V_{PP}=5.0V\pm 10\%$                                  |

| Cical Lock-Bit Current                             |                        |              |              |         | 25      |     | 55                        | mA   | V <sub>PP</sub> =12.0V ± 5%                            |

| VccWord Write or<br>Block Erase Suspend<br>Current | I <sub>CCWS</sub>      | 6            |              |         | 13      |     | 21                        | mA   |                                                        |

| Vcc Lockout Voltage                                | VLKO                   |              |              | 2.0     |         | 2.0 |                           | V    |                                                        |

(Continue to next page)

T1042-01

#### DC Characteristics (Continued)

$(Ta = 0 \text{ to } 60^{\circ}C)$

|                                                          | -                   |                                                  |        |         |         |     |                 |       |                                 |

|----------------------------------------------------------|---------------------|--------------------------------------------------|--------|---------|---------|-----|-----------------|-------|---------------------------------|

| PARAMETER                                                | SYM-                | NO-                                              | Densi- | Vcc=3.3 | ∨± 0.3V |     | V± 5%<br>V± 10% | UNIT  | TEST CONDITION                  |

| TARAMETER                                                | BOL                 | TE                                               | ty     | MIN     | MAX     | MIN | MAX             | 01111 |                                 |

|                                                          | <del> </del>        | <del>                                     </del> | 2MB    |         | ± 30    |     | ± 30            | μΑ    |                                 |

|                                                          | 1                   |                                                  | 4MB    |         | ± 60    |     | ± 60            | μΑ    |                                 |

|                                                          |                     |                                                  | 8MB    |         | ± 120   |     | ± 120           | μΑ    |                                 |

|                                                          |                     |                                                  | 10MB   |         | ± 150   |     | ± 150           | μΑ    | Vpp≦ Vcc                        |

|                                                          |                     |                                                  | 16MB   |         | ± 120   |     | ± 120           | μΑ    |                                 |

| V <sub>pp</sub> Stand-by or Read                         | <sub>T</sub>        |                                                  | 20MB   |         | ± 150   |     | ± 150           | μΑ    |                                 |

| Current                                                  | $I_{pps}$ $I_{ppR}$ | 6                                                | 2MB    |         | 0.4     |     | 0.4             | mA    |                                 |

|                                                          |                     |                                                  | 4MB    |         | 0.8     |     | 0.8             | mA    |                                 |

|                                                          |                     |                                                  | 8MB    |         | 1.6     |     | 1.6             | mA    | 37 - 37                         |

|                                                          |                     |                                                  | 10MB   |         | 2.0     |     | 2.0             | mA    | V <sub>PP</sub> >Vcc            |

|                                                          |                     |                                                  | 16MB   |         | 1.6     |     | 1.6             | mA    |                                 |

|                                                          |                     |                                                  | 20MB   |         | 2.0     |     | 2.0             | mA    |                                 |

|                                                          | 1                   |                                                  | 2MB    |         | 10      |     | 10              | μА    |                                 |

|                                                          | 1                   |                                                  | 4MB    |         | 20      |     | 20              | μΑ    |                                 |