#### SHARP

# SM5K6

## DESCRIPTION

The SM5K6 is a CMOS 4-bit single-chip microcomputer incorporating 4-bit parallel processing function, serial interface function, ROM, RAM, 10bit A/D converter and timer/counters. It provides five kinds of interrupts and 8 levels subroutine stack. Being fabricated through CMOS process, the chip requires less power and available in a small package : best suitable for low power controlling, compact equipment like a precision charger.

# FEATURES

- ROM capacity : 4 096 x 8 bits

- RAM capacity : 256 x 4 bits

- Instruction sets : 52

- Subroutine nesting : 8 levels

- I/O port :

input 4

input/output 20

Interrupts : Internal interrupt x 3 (2 timers, 1 serial interface) External interrupt x 2 (2 external interrupt inputs)

- A/D converter : Resolution 10 bits

- Inputs channels 8

- Timer/counter : 8 bits x 2

- Serial interface : 8 bits synchrounous x 1

- Watch dog timer : 8 bits x 1 (also used as timer 2)

- Built-in main clock oscillator for system clock

- Signal generation for real time clock

- Built-in 15 stages divider for real time clock

- Instruction cycle time :

- 1 µs (4 MHz, at 5 V ± 10%)

- 4 µs (4 MHz, at 2.0 to 5.5 V)

- Large current output pins (LED direct drive) : 8

- Buzzer output

- Supply voltage : 2.0 to 5.5 V

# 4-Bit Single-Chip Microcomputer (Controller With 10-Bit A/D Converter)

• Packages :

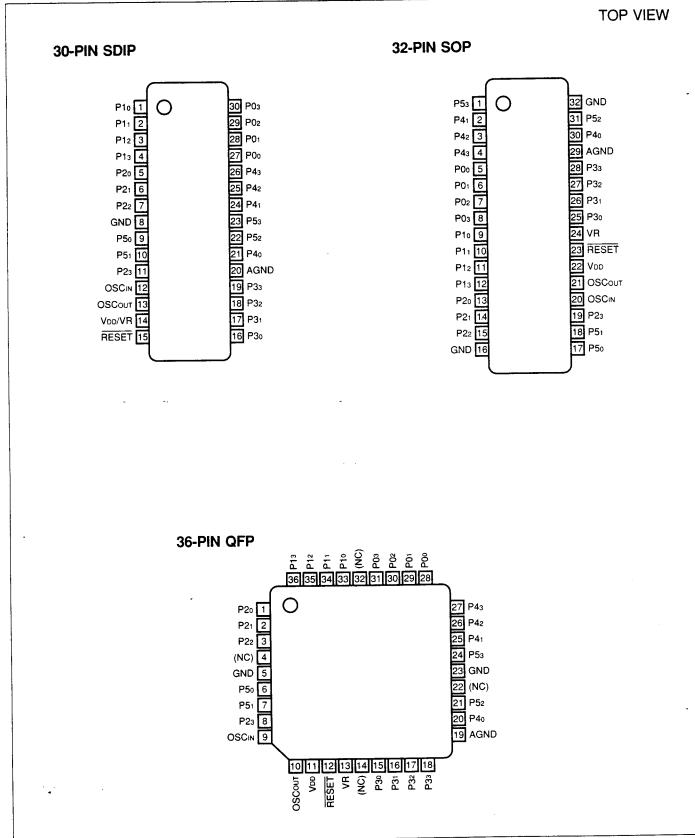

30-pin SDIP (SDIP030-P-0400) 32-pin SOP (SOP032-P-0525) 36-pin QFP (QFP036-P-1010)

#### **PIN CONNECTIONS**

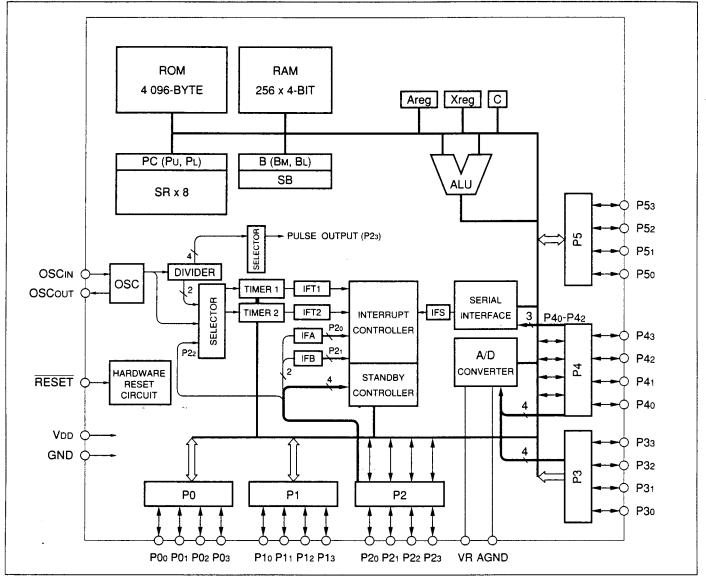

# **BLOCK DIAGRAM**

#### Nomenciature

| Areg          | : A register (Accumulator) | PC   | : Program counter              |

|---------------|----------------------------|------|--------------------------------|

| ALU           | : Arithmetic logic unit    | RAM  | : Data memory                  |

| В             | : RAM address register     | ROM  | : Program memory               |

| С             | : Carry latch flag         | SB   | : SB register (Stack B-reg)    |

| IFA, IFB, IFS | : Interrupt request flag   | SR   | : Stack register (Stack PC)    |

| IFT1, IFT2    |                            | Xreg | : X register (Sub accumulator) |

| OSC           | : System clock oscillator  |      |                                |

|               |                            |      |                                |

P0, P1, P2 : I/O access

•

P3, P4, P5

# **PIN DESCRIPTION**

| PIN NAME                              | I/O  | FUNCTION                                                                                     |

|---------------------------------------|------|----------------------------------------------------------------------------------------------|

| P0 <sub>0</sub> -P0 <sub>3</sub>      | 1/0  | Parallel input/output : Direction of pins can be set in units of 4 bits. When set at output, |

| FU0-FU3                               |      | each pin serves as a drive with a 15 mA (Typ.) current sinking capability.                   |

| P10-P13                               | I/O  | Parallel input/output : Direction of pins can be set in units of 4 bits. When set at output, |

|                                       |      | each pin serves as a drive with a 15mA (Typ.) current sinking capability                     |

| P20                                   | 1/0  | Input or output (independent) : Direction of this pin can be set independently. Assumes      |

|                                       |      | external interrupt input or standby release.                                                 |

| P21                                   | 1/0  | Input or output (independent) : Direction of this pin can set independently. Assumes count   |

| ·····                                 | 1 10 | clock input or standby release.                                                              |

| <b>P2</b> ₂                           | 1/0  | Input or output (independent) : Direction of this pin can be set independently. Assumes      |

| · <b>-</b> 2                          |      | external interrupt input or standby release.                                                 |

| P23                                   | I/O  | Input or output (independent) : Direction of this pin can be set independently. Assumes      |

|                                       |      | standby release or buzzer output (divider clock).                                            |

| P30-P33                               |      | Parallel input : Accepts input in units of 4 bits. Also assumes A/D pins.                    |

| P40                                   | I/O  | Input or output (independent) : Direction of this pin can be set independently. Assumes A/D  |

|                                       |      | pin or SIO data input.                                                                       |

| P41                                   | I/O  | Input or output (independent) : Direction of this pin can be set independently. Assumes A/D  |

| · · · ·                               |      | pin or SIO data output.                                                                      |

| P4₂                                   | 1/0  | Input or output (independent) : Direction of this pin can be set independently. Assumes A/D  |

| · · · · · · · · · · · · · · · · · · · |      | pin or SIO clock I/O.                                                                        |

| P43                                   | I/O  | Input or output (independent) : Direction of this pin can be set independently. Also         |

|                                       |      | assumes A/D pin.                                                                             |

| P50-P53                               | 1/0  | Parallel input/output : Direction of pins can be set in units of 4 bits.                     |

| RESET                                 | 1    | Hardware reset input : Input to this pin resets the microcomputer. For normal run, connect   |

|                                       |      | 0.1 µF (Typ.) across RESET and GND.pins.                                                     |

| QSCIN, OSCOUT                         | í, O | Main clock circuit pins. Connecting a crystal across these pins completes main clock         |

|                                       |      | oscillator. The divided-by-4 main clock is used as the system clock.                         |

| VDD, GND                              | -    | Power supply input to the microcomputer                                                      |

| VR, AGND                              | -    | A/D converter reference voltage : Connect to VR to VDD pin and AGND to GND pin.              |

#### NOTES :

1. Hardware reset sets all I/O pins to input.

2. Input ports and I/O ports programmed as input port are provided with pull-up resistors.

-

# ABSOLUTE MAXIMUM RATINGS

| PARAMETER             | SYMBOL     | CONDITIONS                                                                                                                                                                                                                                                                      | RATING                                                          | UNIT |

|-----------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------|

| Supply voltage        | VDD        |                                                                                                                                                                                                                                                                                 | -0.3 to +7.0                                                    | V    |

| Input voltage         | ViN        |                                                                                                                                                                                                                                                                                 | -0.3 to VDD+0.3                                                 | V    |

| Output voltage        | Vout       |                                                                                                                                                                                                                                                                                 | -0.3 to VDD+0.3                                                 | V    |

|                       | Іон        | High-level output current (at each output)                                                                                                                                                                                                                                      | 4                                                               | mA   |

| Max. Output current   |            | Low-level output current (P00-P03, P10-P13)                                                                                                                                                                                                                                     | 30                                                              | mA   |

|                       | IOL1       | -0.3 to Vbb+0.3T $-0.3$ to Vbb+0.3High-level output current (at each output)4Low-level output current (P0o-P03, P1o-P13)30Low-level output current (all but P0o-P03, P1o-P13)4High-level output current (all outputs)20Low-level output current (all outputs)120A120A-20 to +70 | mA                                                              |      |

|                       | Σюн        | High-level output current (all outputs)                                                                                                                                                                                                                                         | -0.3 to Vpp+0.3<br>-0.3 to Vpp+0.3<br>4<br>30<br>4<br>20<br>120 | mA   |

| Total output current  | $\sum$ IOL | Low-level output current (all outputs)                                                                                                                                                                                                                                          | P1₃) 30 m.<br>₀-P1₃) 4 m.<br>20 m.<br>120 m.<br>−20 to +70 °C   |      |

| Operating temperature | TOPR       |                                                                                                                                                                                                                                                                                 | -20 to +70                                                      | °C   |

| Storage temperature   | Тята       |                                                                                                                                                                                                                                                                                 | -55 to +150                                                     | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER               | SYMBOL   | CONDITIONS                     | RATING           | UNIT |  |

|-------------------------|----------|--------------------------------|------------------|------|--|

| Supply voltage          | VDD      |                                | 2.0 to 5.5       | V    |  |

| Instruction quals       | <b>.</b> | V <sub>DD</sub> = 2.0 to 5.5 V | 4 to 122         | – μs |  |

| Instruction cycle       | tcyc     | $V_{DD} = 5.0 V \pm 10\%$      | 1 to 122         |      |  |

| System alcole fragmanes | 4        | V <sub>DD</sub> = 2.0 to 5.5 V | 250 k to 8.192 k | – Hz |  |

| System clock frequency  | fsys     | $V_{DD} = 5 V \pm 10\%$        | 1 M to 8.192 k   |      |  |

| Main clock frequency    |          | V <sub>DD</sub> = 2.0 to 5.5 V | 1 M to 32.768 k  |      |  |

| (OSCIN-OSCOUT)          | fosc     | $V_{DD} = 5.0 V \pm 10\%$      | 4 M to 32.768 k  | Hz   |  |

# **DC CHARACTERISTICS**

| PARAMETER      | SYMBOL    | (Ta = -20 to 70°C, Typ. va<br>CONDITIONS |                                | MIN.                           | TYP.  | MAX.      | UNIT   | NOTE     |  |

|----------------|-----------|------------------------------------------|--------------------------------|--------------------------------|-------|-----------|--------|----------|--|

| Input voltage  | ViHt      |                                          |                                | 0.8 x VDD                      |       | VDD       | _ v    | 1        |  |

|                | VIL1      |                                          |                                | 0                              |       | 0.2 x VDD |        |          |  |

|                | VIH2      |                                          |                                | 0.9 x VDD                      |       | VDD       | - v    | 2        |  |

|                | VIL2      |                                          |                                | 0 0.1 x Vr                     |       |           |        | 2        |  |

| Input current  | lılı      | <u> </u>                                 | VDD = 2.0 to 3.3 V             | 2                              | 25    | 90        | μA     | 3        |  |

|                |           | $V_{IN} = 0 V$                           | VDD = 4.5 to 5.5 V             | 25                             | 70    | 250       |        |          |  |

|                | Іінт      | VIN = VDD                                | · · · ·                        |                                |       | 2         |        |          |  |

|                | 1L2       | $V_{IN} = 0 V$                           |                                |                                | 1     | 10        | μA     |          |  |

|                | Іінг      | VIN = VDD                                |                                |                                | 1     | 10        |        | 4        |  |

|                |           |                                          | VDD = 2.0 to 3.3 V             | 3                              | 15    |           | 1      | 5        |  |

|                | IOL1      | Vo = 1.0 V                               | VDD = 4.5 to 5.5 V             | 15                             | 25    |           | 1      |          |  |

|                |           |                                          | VDD = 2.0 to 3.3 V             | 0.2                            | 1.5   |           | - mA   |          |  |

| 0              | IOH1      | $V_0 = V_{DD} - 0.5 V$                   | V <sub>DD</sub> = 4.5 to 5.5 V | 1.0                            | 2.2   |           |        |          |  |

| Output current |           | N 05 N                                   | V <sub>DD</sub> = 2.0 to 3.3 V | 70                             | 600   |           |        |          |  |

|                | 1012      | Vo = 0.5 V                               | VDD = 4.5 to 5.5 V             | 400                            | 1 000 |           | - μA   | 6        |  |

|                |           |                                          | VDD = 2.0 to 3.3 V             | 200                            | 2 000 |           |        |          |  |

|                | Юн2       | $V_{\rm O} = V_{\rm DD} - 0.5 \ V$       | V <sub>DD</sub> = 4.5 to 5.5 V | 1 000                          | 2 400 |           |        |          |  |

|                | laa       | fosc = 2 MHz                             | V <sub>DD</sub> = 4.5 to 5.5 V |                                | 1 600 | 3 500     | Αμ<br> | <u>†</u> |  |

|                |           |                                          | Vod = 2.0 to 3.3 V             |                                | 400   | 1 100     |        |          |  |

|                |           | fosc = 1 MHz                             | V <sub>DD</sub> = 4.5 to 5.5 V |                                | 850   | 1 700     |        | 7        |  |

|                |           | fosc = 32.768 kHz                        | VDD = 2.0 to 3.3 V             |                                | 28    | 170       |        |          |  |

|                |           |                                          | Vod = 4.5 to 5.5 V             |                                | 55    | 220       |        |          |  |

|                | IHALT     | fosc = 2 MHz                             | VDD = 4.5 to 5.5 V             |                                | 900   | 1 800     |        |          |  |

|                |           | fosc = 1 MHz                             | VDD = 4.5 to 5.5 V             |                                | 500   | 1 100     |        |          |  |

| Supply current |           | 6 00 700 kit la                          | V <sub>DD</sub> = 2.0 to 3.3 V |                                | 20    | 75        |        |          |  |

|                |           | fosc = 32.768 kHz                        | V <sub>DD</sub> = 4.5 to 5.5 V |                                | 25    | 120       |        |          |  |

|                |           |                                          | Ceramic OSC mode               | V <sub>DD</sub> = 2.0 to 3.3 V |       | · · · · · | 3      | 1        |  |

|                | ISTOP     | Crystal OSC mode                         | V <sub>DD</sub> = 2.0 to 5.5 V |                                | 20    | 45        | -      |          |  |

|                |           | (32.786kHz)                              | V <sub>DD</sub> = 4.5 to 5.5 V |                                | 25    | 65        |        |          |  |

|                | lvr       | A/D active                               | V <sub>DD</sub> = 2.0 to 3.3 V |                                | 180   | 420       | μA     | 8        |  |

|                |           |                                          | V <sub>DD</sub> = 4.5 to 5.5 V |                                | 300   | 650       |        |          |  |

|                |           | A/D inactive                             | VDD = 2.0 to 5.5 V             |                                |       | 3         | μA     | 9        |  |

|                | n         | Resolution                               |                                |                                | 10    |           | bit    |          |  |

|                | Different | ial fosc = 2 MHz                         | $V_{DD} = VR = 5.0 V$          |                                | ± 2.5 | ± 4.0     | LSB    |          |  |

| A/D            | linearity | $T_{OPR} = 25^{\circ}C$                  |                                |                                |       |           |        |          |  |

| conversion     | Linoarity | fosc = 2 MHz                             | $V_{DD} = VR = 5.0 V$          |                                | ± 3.2 | ± 5.0     |        |          |  |

| CUTIVELSIUT    | Linearity | TOPR = 25°C                              |                                |                                |       |           |        |          |  |

| -              | Total err | fosc = 2 MHz                             | $V_{DD} = VR = 5.0 V$          |                                | ± 4.0 | ± 6.0     |        |          |  |

|                | rual en   | TOPR = 25°C                              |                                |                                |       |           |        |          |  |

.

•

#### SHARP

#### NOTES :

- 1. Applicable pins : P00-P03, P10-P13, P22, P23, P30-P33 (digital input mode), P41, P43 (digital input mode), P50-P53

- 2. Applicable pins : OSCIN, RESET, P20, P21, P40, P42 (digital input mode)

- 3. Applicable pins : P40-P43, P30-P33 (digital input mode), RESET, P20-P23, P50-P53, P00-P03, P10-P13

- 4. Applicable pins : P3o-P33, P4o-P43 (A/D mode)

- 5. Applicable pins : P0o-P03, P1o-P13 (High current port)

- 6. Applicable pins : P20-P23, P40-P43, P50-P53 (output mode)

- 7. Non-load condition (A/D conversion disabled) MAX. V\_DD = 5.5 V (or 3.3 V), T\_{OPR} = -20  $^{\circ}\text{C}$

- 8. Current into VR at A/D conversion mode (run enable status)

- 9. Current into VR at Non-A/D conversion mode (run disable status)

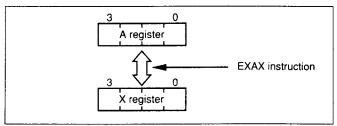

# SYSTEM CONFIGURATION A Register and X Register

The A register (accumulator : Acc) is a 4-bit general purpose register. The register is mainly used in conjunction with the ALU, C flag and RAM, to transfer numerical\_value\_and data to perform various operations. The A register is also used to transfer data between input and output pins.

The X register (auxiliary accumulator) is a 4-bit register and can be used as a temporary register.

It loads contents of the A register or its content is transferred to the A register.

When the table reference instruction PAT is used, the X and A registers load ROM data.

A pair of A and X registers can accommodate 8 bit data.

Fig. 1 Data Transfer Example between Register and X Register

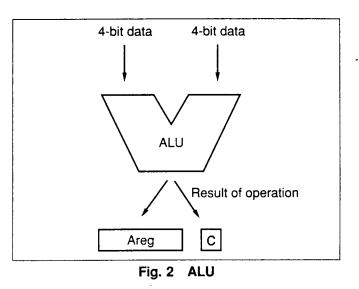

# Arithmetic and Logic Unit (ALU) and Carry Signal Cy

The ALU performs 4-bit parallel operation.

The ALU operates binary addition in conjunction with RAM, C flag and A register. Cy is the symbol for carry signal and not for C flag.

The C flag latches the carry-over as the result of arithmetic instruction. The flag can be set/clear using SC and RC instructions.

The content of C flag can be tested using the TC instruction.

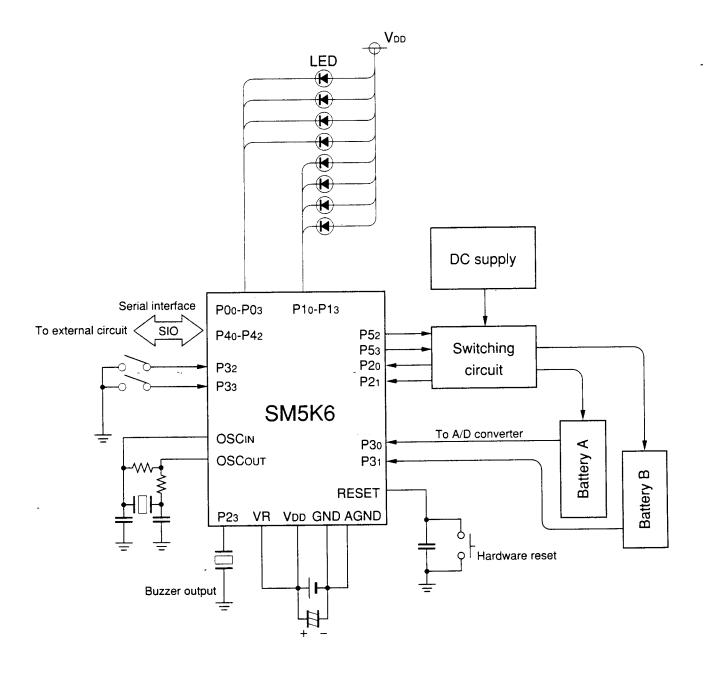

# SYSTEM CONFIGURATION EXAMPLE

Versatile charger

Singlechip LH7xxxx '790 '789 '791 SMxxxx 'K series MCU Microcontroller MPU Microprocessor ARM Advanced RISC Machines Databank LCD Controller LCD Driver Controllers Processors Portable Low Power Low Voltage High Performance Power curve MIPS MIPS/Watt Execution Cycle Multiplier High Speed Compact Handheld System on Chip System Integration Chip Integration Integration Superchip Standard Cell Core Core based IC VHDL Verilog Synthesis Chip on Board COB Chip on Flex COF Device on Board DOB Power Supply Controller Handy Products Development Tools Board Support Software Tools Tools 2.10 Software Support Emulators Evaluation Boards ICE In-Circuit Emulators ROM ICE SME Series Programmable User Configurable RTOS Real Time Operating Systems Third Party Support Software Hardware Yokogawa Digital Cosmic Compiler C Language C Like Assembler Linker Debugger Debug A/D D/A DAC Analog Digital 10-bit 4-bit 8-bit 16-bit 32-bit Address bus Data Bus