# Si5311

PRELIMINARY DATA SHEET

# PRECISION HIGH SPEED CLOCK MULTIPLIER/REGENERATOR IC

#### Features

Complete precision high speed clock multiplier and regenerator device:

- Performs Clock Multiplication to One of Four Frequency Ranges: 150–167 MHz, 600–668 MHz, 1.2–1.33 GHz, or 2.4–2.67 GHz

- Jitter Generation as low as 0.5 ps<sub>RMS</sub> for 622 MHz Output

- Accepts Input Clock from 9.4–668 MHz

- Applications

- SONET/SDH Systems

- Terabit Routers

- Digital Cross Connects

- Regenerates a "Clean", Jitter-Attenuated Version of Input Clock

- DSPLL<sup>™</sup> Technology Provides Superior Jitter Performance

- Small Footprint: 4 mm x 4 mm

- Low Power: 310 mW typical

- Optical Transceiver Modules

- Gigabit Ethernet Systems

- Hybrid VCO Modules

#### Description

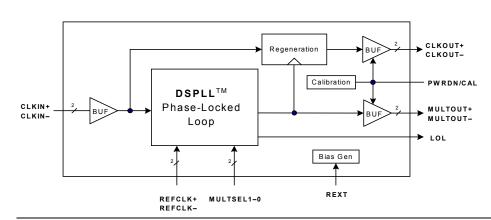

The Si5311 is a fully integrated high-speed clock multiplier and clock regenerator IC. The clock multiplier generates an output clock that is an integer multiple of the input clock. When the clock multiplier is operating in either the 150–167 MHz range or the 600–668 MHz range, the clock regenerator operates simultaneously. The clock regenerator creates a "clean" version of the input clock by using the clock synthesis phase-locked loop (PLL) to remove unwanted jitter and square up the input clock's rising and falling edges. The Si5311 uses Silicon Laboratories patented DSPLL<sup>™</sup> architecture to achieve superior jitter performance while eliminating the analog loop filter found in traditional PLL designs.

The Si5311 represents a new standard in low jitter, small size, low power, and ease-of-use for high speed clock devices. It operates from a single 2.5 V supply over the industrial temperature range ( $-40^{\circ}$ C to  $85^{\circ}$ C).

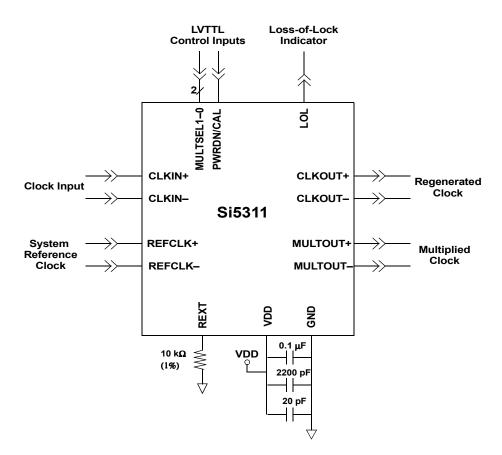

## **Functional Block Diagram**

#### Preliminary Rev. 0.6 6/01

#### Copyright © 2001 by Silicon Laboratories

Si5311-DS06

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

# TABLE OF CONTENTS

# <u>Section</u>

## <u>Page</u>

| Detailed Block Diagram              |    |

|-------------------------------------|----|

| Functional Description              |    |

| •                                   | 16 |

| Clock Multiplier                    | 16 |

| 1x Multiplication                   | 16 |

| Clock Regeneration                  | 16 |

| Reference Clock                     | 16 |

| DSPLL Lock Detection (Loss-of-Lock) | 16 |

| PLL Performance                     | 17 |

| Device Power-Down                   | 18 |

| PLL Self-Calibration                | 18 |

| Device Grounding                    | 18 |

| Bias Generation Circuitry           | 18 |

| Differential Input Circuitry        | 18 |

| Differential Output Circuitry       | 18 |

| Pin Descriptions: Si5311            | 20 |

| Ordering Guide                      | 22 |

| Package Outline                     | 23 |

| Contact Information                 | 24 |

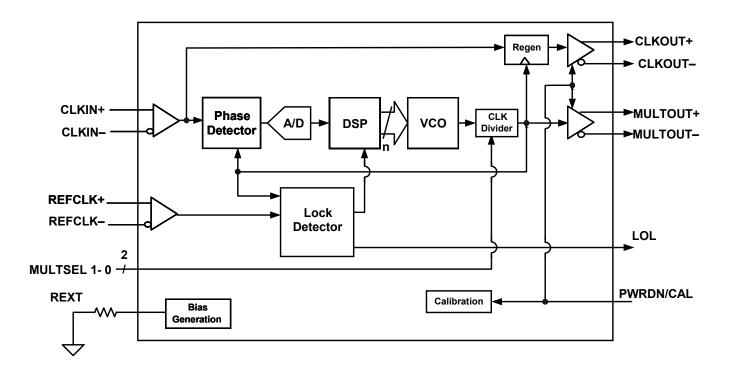

## **Detailed Block Diagram**

Figure 1. Detailed Block Diagram

## **Electrical Specifications**

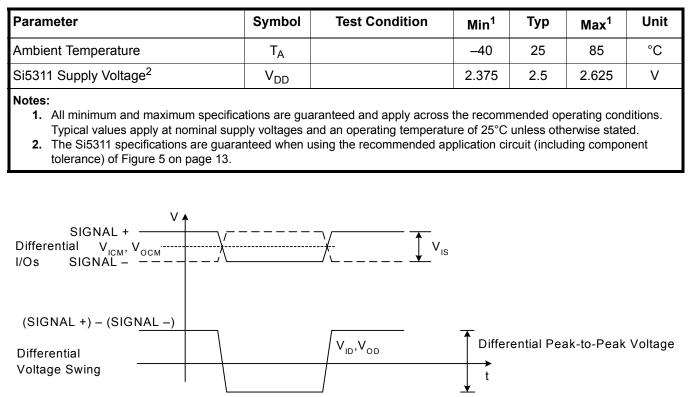

## Table 1. Recommended Operating Conditions

## Figure 2. Differential Voltage Measurement (CLKIN, REFCLK, CLKOUT, MULTOUT)

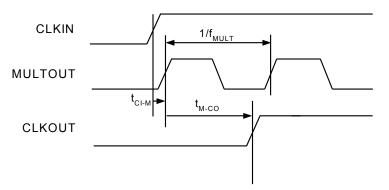

Figure 3. CLKIN to CLKOUT, MULTOUT Phase Relationship

## Table 2. DC Characteristics, V<sub>DD</sub> = 2.5 V

$(V_{DD} = 2.5 \text{ V} \pm 5\%, \text{ T}_{A} = -40^{\circ}\text{C to } 85^{\circ}\text{C})$

| Parameter                                                  | Symbol             | <b>Test Condition</b>   | Min         | Тур                   | Max         | Unit          |

|------------------------------------------------------------|--------------------|-------------------------|-------------|-----------------------|-------------|---------------|

| Supply Current                                             | I <sub>DD</sub>    |                         |             |                       |             |               |

| MULTSEL[1:0] = 00                                          |                    |                         |             | 108                   | 118         | mA            |

| MULTSEL[1:0] = 01                                          |                    |                         | —           | 113                   | 123         |               |

| MULTSEL[1:0] = 10                                          |                    |                         | —           | 117                   | 127         |               |

| MULTSEL[1:0] = 11                                          |                    |                         |             | 124                   | 134         |               |

| Power Dissipation                                          | PD                 |                         |             |                       |             |               |

| MULTSEL[1:0] = 00                                          |                    |                         | —           | 270                   | 310         | mW            |

| MULTSEL[1:0] = 01<br>MULTSEL[1:0] = 10                     |                    |                         |             | 283<br>293            | 323<br>333  |               |

| MULTSEL[1:0] = 10<br>MULTSEL[1:0] = 11                     |                    |                         | _           | 293<br>310            | 352         |               |

| Common Mode Input Voltage                                  | V                  | See Figure 2            |             | .80 • V <sub>DD</sub> | 552         | V             |

| (CLKIN, REFCLK)                                            | V <sub>ICM</sub>   | See Figure 2            | _           | .00 ° V <sub>DD</sub> |             | v             |

| Input Voltage Range*<br>(CLKIN+, CLKIN–, REFCLK+, REFCLK–) | V <sub>IS</sub>    | See Figure 2            | _           | _                     | 750         | mV            |

| Differential Input Voltage Swing*<br>(CLKIN, REFCLK)       | $V_{ID}$           | See Figure 2            | 200         | _                     | 1500        | mV<br>(pk-pk) |

| Input Impedance (CLKIN, REFCLK)                            | R <sub>IN</sub>    | Line-to-Line            | 84          | 100                   | 116         | Ω             |

| Differential Output Voltage Swing                          | V <sub>OD</sub>    | 100 Ω Load              | TBD         | 940                   | TBD         | mV            |

| (CLKOUT)                                                   |                    | Line-to-Line            |             |                       |             | (pk-pk)       |

| Differential Output Voltage Swing                          | V <sub>OD</sub>    | 100 $\Omega$ Load       | TBD         | 900                   | TBD         | mV            |

| (MULTOUT)                                                  |                    | Line-to-Line            |             |                       |             | (pk-pk)       |

| Output Common Mode Voltage                                 | V <sub>OCM</sub>   | 100 $\Omega$ Load       |             | V <sub>DD</sub> – 0.7 |             | V             |

| (CLKOUT, MULTOUT)                                          |                    | Line-to-Line            |             |                       |             |               |

| Output Impedance (CLKOUT, MULTOUT)                         | R <sub>OUT</sub>   | Single-ended            | 84          | 100                   | 116         | Ω             |

| Output Short to GND (CLKOUT, MULTOUT)                      | I <sub>SC(-)</sub> |                         |             | 25                    | TBD         | mA            |

| Output Short to V <sub>DD</sub> (CLKOUT, MULTOUT)          | I <sub>SC(+)</sub> |                         | TBD         | -15                   | —           | mA            |

| Input Voltage Low (LVTTL Inputs)                           | V <sub>IL</sub>    |                         |             |                       | .8          | V             |

| Input Voltage High (LVTTL Inputs)                          | V <sub>IH</sub>    |                         | 2.0         | —                     | —           | V             |

| Input Low Current (LVTTL Inputs)                           | ۱ <sub>IL</sub>    |                         |             | 25                    | TBD         | μA            |

| Input High Current (LVTTL Inputs)                          | I <sub>IH</sub>    |                         |             | 25                    | TBD         | μA            |

| Output Voltage Low (LVTTL Outputs)                         | V <sub>OL</sub>    | I <sub>O</sub> = 2 mA   |             | —                     | 0.4         | V             |

| Output Voltage High (LVTTL Outputs)                        | V <sub>OH</sub>    | I <sub>O</sub> = 2 mA   | 2.0         |                       |             | V             |

| Input Impedance (LVTTL Inputs)                             | R <sub>IN</sub>    |                         | 100         |                       | _           | kΩ            |

| PWRDN/CAL Internal Pulldown Current                        | I <sub>PWRDN</sub> | $V_{PWRDN} \ge 0.8 V$   | TBD         | 25                    | TBD         | μA            |

| *Note: The CLKIN and REFCLK inputs may be dr               |                    | itially or single-ended | lly. When o | driving single-       | endedly, th | ne voltage    |

\*Note: The CLKIN and REFCLK inputs may be driven differentially or single-endedly. When driving single-endedly, the voltage swing of the signal applied to the active input must exceed the specified minimum Differential Input Voltage Swing (V<sub>ID</sub> min) and the unused input must be ac-coupled to ground. When driving differentially, the difference between the positive and negative input signals must exceed V<sub>ID</sub> min. (Each individual input signal needs to swing only half of this range.) In either case, the voltage applied to any individual pin (CLKIN+, CLKIN–, REFCLK+, or REFCLK–) must not exceed the specified maximum Input Voltage Range (V<sub>IS</sub> max).

## Table 3. AC Characteristics

$(V_{DD} = 2.5 \text{ V} \pm 5\%, \text{ T}_{A} = -40^{\circ}\text{C to } 85^{\circ}\text{C})$

| Parameter                                                                                                   | Symbol            | Test Condition                     | Min                        | Тур                                  | Max                        | Unit                 |

|-------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------|----------------------------|--------------------------------------|----------------------------|----------------------|

| CLKIN Frequency Range*                                                                                      |                   |                                    | 9.375                      |                                      | 668                        | MHz                  |

| CLKIN Duty Cycle                                                                                            |                   |                                    | TBD                        |                                      | TBD                        | %                    |

| REFCLK Range <sup>*</sup>                                                                                   |                   |                                    | 9.375                      | —                                    | 167                        | MHz                  |

| REFCLK Duty Cycle                                                                                           | C <sub>DUTY</sub> |                                    | 40                         | 50                                   | 60                         | %                    |

| REFCLK Frequency<br>Tolerance                                                                               | C <sub>TOL</sub>  |                                    | -100                       |                                      | 100                        | ppm                  |

| MULTOUT Clock Rate<br>MULTSEL[1:0] = 00<br>MULTSEL[1:0] = 01<br>MULTSEL[1:0] = 10<br>MULTSEL[1:0] = 11      | f <sub>MULT</sub> |                                    | 2400<br>1200<br>600<br>150 |                                      | 2672<br>1336<br>668<br>167 | MHz                  |

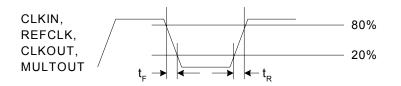

| Output Rise Time<br>(CLKOUT, MULTOUT)                                                                       | t <sub>R</sub>    | Figure 4                           |                            | 100                                  | TBD                        | ps                   |

| Output Fall Time<br>(CLKOUT, MULTOUT)                                                                       | t <sub>F</sub>    | Figure 4                           |                            | 100                                  | TBD                        | ps                   |

| Input Rise Time<br>(CLKIN, REFCLK)                                                                          | t <sub>R</sub>    | Figure 4                           |                            | —                                    | TBD                        | ps                   |

| Input Fall Time<br>(CLKIN, REFCLK)                                                                          | t <sub>F</sub>    | Figure 4                           |                            | —                                    | TBD                        | ps                   |

| CLKIN to MULTOUT Delay<br>MULTSEL[1:0] = 00<br>MULTSEL[1:0] = 01<br>MULTSEL[1:0] = 10<br>MULTSEL[1:0] = 11  | t <sub>CI-M</sub> | Figure 3                           | TBD<br>TBD<br>TBD<br>TBD   | 0<br>120<br>150<br>3.4               | TBD<br>TBD<br>TBD<br>TBD   | ps<br>ps<br>ps<br>ns |

| MULTOUT to CLKOUT Delay<br>MULTSEL[1:0] = 00<br>MULTSEL[1:0] = 01<br>MULTSEL[1:0] = 10<br>MULTSEL[1:0] = 11 | t <sub>M-CO</sub> | Figure 3                           | —<br>—<br>TBD<br>TBD       | <br>1/f <sub>MULT</sub> + 160<br>960 | —<br>—<br>TBD<br>TBD       | ps<br>ps             |

| Input Return Loss                                                                                           |                   | 100 kHz–2.5 GHz<br>2.5 GHz–4.0 GHz | 18.7<br>TBD                | _                                    |                            | dB                   |

| *Note: See Table 11.                                                                                        | 1                 |                                    | 1                          | 1                                    |                            |                      |

## Table 4. AC Characteristics (PLL Performance Characteristics)

$(V_{DD} = 2.5 \text{ V} \pm 5\%, \text{ T}_{A} = -40^{\circ}\text{C to } 85^{\circ}\text{C})$

| Parameter                                                                         | Symbol                | Test Condition                            | Min     | Тур   | Мах | Unit              |

|-----------------------------------------------------------------------------------|-----------------------|-------------------------------------------|---------|-------|-----|-------------------|

| Jitter Tolerance<br>MULTSEL[1:0] = 00,<br>MULTOUT = 2400 to 2672 MHz)             | J <sub>TOL(PP)</sub>  |                                           | See Tat | ole 5 |     | I                 |

| Jitter Tolerance<br>MULTSEL[1:0] = 01,<br>MULTOUT = 1200 to 1336 MHz)             | J <sub>TOL(PP)</sub>  |                                           | See Tat | ble 6 |     |                   |

| Jitter Tolerance<br>MULTSEL[1:0] = 10,<br>MULTOUT = 600 to 668 MHz)               | J <sub>TOL(PP)</sub>  |                                           | See Tat | ole 7 |     |                   |

| Jitter Tolerance<br>MULTSEL[1:0] = 11,<br>MULTOUT = 150 to 167 MHz)               | J <sub>TOL(PP)</sub>  |                                           | See Tat | ble 8 |     |                   |

| Jitter Generation (MULTOUT)<br>MULTSEL[1:0] = 00,<br>MULTOUT = 2400 to 2672 MHz)* | J <sub>GEN(rms)</sub> | Clock Input (MHz) =<br>600.000 to 668.000 |         | TBD   | TBD | ps <sub>RMS</sub> |

| Jitter Generation (MULTOUT)<br>MULTSEL[1:0] = 01,                                 | J <sub>GEN(rms</sub>  | Clock Input (MHz) = 300.000 to 334.000    |         | TBD   | TBD | ps <sub>RMS</sub> |

| MULTOUT = 1200 to 1336 MHz)*                                                      | -                     | Clock Input (MHz) =<br>600.000 to 668.000 |         | TBD   | TBD | ps <sub>RMS</sub> |

| Jitter Generation (MULTOUT, CLKOUT)<br>(MULTSEL[1:0] = 10,                        | J <sub>GEN(rms)</sub> | Clock Input (MHz) =<br>37.500 to 41.750   |         | 1.9   | TBD | ps <sub>RMS</sub> |

| MULTOUT = 600 to 668 MHz)*                                                        | -                     | Clock Input (MHz) =<br>75.000 to 83.500   |         | 1.2   | TBD | ps <sub>RMS</sub> |

|                                                                                   |                       | Clock Input (MHz) = 150.000 to 167.000    |         | 0.9   | TBD | ps <sub>RMS</sub> |

|                                                                                   | -                     | Clock Input (MHz) = 300.000 to 334.000    |         | 0.5   | TBD | ps <sub>RMS</sub> |

|                                                                                   | -                     | Clock Input (MHz) =<br>600.000 to 668.000 |         | 0.5   | TBD | ps <sub>RMS</sub> |

| <pre>Jitter Generation (MULTOUT, CLKOUT) MULTSEL[1:0] = 11,</pre>                 | J <sub>GEN(rms)</sub> | Clock Input (MHz) =<br>9.375 to 10.438    |         | 5.8   | TBD | ps <sub>RMS</sub> |

| MULTOUT = 150 to 167 MHz)*                                                        | _                     | Clock Input (MHz) =<br>18.750 to 20.875   |         | 3.2   | TBD | ps <sub>RMS</sub> |

|                                                                                   | -                     | Clock Input (MHz) =<br>37.500 to 41.750   |         | 2.2   | TBD | ps <sub>RMS</sub> |

|                                                                                   | _                     | Clock Input (MHz) =<br>75.000 to 83.500   |         | 1.4   | TBD | ps <sub>RMS</sub> |

|                                                                                   |                       | Clock Input (MHz) =<br>150.000 to 167.000 |         | 1.3   | TBD | ps <sub>RMS</sub> |

| Jitter Transfer Bandwidth<br>MULTSEL[1:0] = 00,<br>MULTOUT = 2400 to 2672 MHz)*   | J <sub>BW</sub>       | Clock Input (MHz) =<br>600.000 to 668.000 |         | 1360  | TBD | kHz               |

| MULTSEL[1:0] = 00,                                                                |                       | 600.000 to 668.000                        |         | 1360  |     | TBD               |

# Table 4. AC Characteristics (PLL Performance Characteristics) (Continued) ( $V_{DD}$ = 2.5 V ± 5%, $T_A$ = -40°C to 85°C)

| Parameter                                                                      | Symbol          | Test Condition                            | Min | Тур  | Мах | Unit |

|--------------------------------------------------------------------------------|-----------------|-------------------------------------------|-----|------|-----|------|

| Jitter Transfer Bandwidth<br>(MULTSEL[1:0] = 01,                               | J <sub>BW</sub> | Clock Input (MHz) = 300.000 to 334.000    |     | 680  | TBD | kHz  |

| MULTOUT = 1200 to 1336 MHz)*                                                   |                 | Clock Input (MHz) =<br>600.000 to 668.000 |     | 1360 | TBD | kHz  |

| Jitter Transfer Bandwidth<br>(MULTSEL[1:0] = 10,                               | J <sub>BW</sub> | Clock Input (MHz) =<br>37.500 to 41.750   |     | 85   | TBD | kHz  |

| MULTOUT = 600 to 668 MHz)*                                                     |                 | Clock Input (MHz) =<br>75.000 to 83.500   |     | 170  | TBD | kHz  |

|                                                                                |                 | Clock Input (MHz) = 150.000 to 167.000    |     | 340  | TBD | kHz  |

|                                                                                |                 | Clock Input (MHz) = 300.000 to 334.000    |     | 680  | TBD | kHz  |

|                                                                                |                 | Clock Input (MHz) =<br>600.000 to 668.000 |     | 1360 | TBD | kHz  |

| Jitter Transfer Bandwidth<br>(MULTSEL[1:0] = 11,<br>MULTOUT = 150 to 167 MHz)* | J <sub>BW</sub> | Clock Input (MHz) =<br>9.375 to 10.438    |     | 21   | TBD | kHz  |

|                                                                                |                 | Clock Input (MHz) =<br>18.750 to 20.875   |     | 43   | TBD | kHz  |

|                                                                                |                 | Clock Input (MHz) =<br>37.500 to 41.750   |     | 85   | TBD | kHz  |

|                                                                                |                 | Clock Input (MHz) =<br>75.000 to 83.500   |     | 170  | TBD | kHz  |

|                                                                                |                 | Clock Input (MHz) =<br>150.000 to 167.000 |     | 340  | TBD | kHz  |

| Jitter Transfer Peaking<br>(MULTSEL[1:0] = 00,<br>MULTOUT = 2400 to 2672 MHz)* | JP              | Clock Input (MHz) =<br>600.000 to 668.000 | —   | 0.03 | TBD | dB   |

| Jitter Transfer Peaking<br>(MULTSEL[1:0] = 01,                                 | JP              | Clock Input (MHz) = 300.000 to 334.000    |     | 0.03 | TBD | dB   |

| MULTOUT = 1200 to 1336 MHz)*                                                   |                 | Clock Input (MHz) =<br>600.000 to 668.000 |     | 0.02 | TBD | dB   |

| Jitter Transfer Peaking<br>(MULTSEL[1:0] = 10,                                 | J <sub>P</sub>  | Clock Input (MHz) =<br>37.500 to 41.750   |     | 0.12 | TBD | dB   |

| MULTOUT = 600 to 668 MHz)*                                                     |                 | Clock Input (MHz) =<br>75.000 to 83.500   |     | 0.06 | TBD | dB   |

|                                                                                |                 | Clock Input (MHz) = 150.000 to 167.000    |     | 0.03 | TBD | dB   |

|                                                                                |                 | Clock Input (MHz) = 300.000 to 334.000    |     | 0.02 | TBD | dB   |

|                                                                                |                 | Clock Input (MHz) =<br>600.000 to 668.000 |     | 0.01 | TBD | dB   |

| *Note: See PLL Performance section of the                                      | s document for  | test descriptions.                        |     |      |     |      |

## Table 4. AC Characteristics (PLL Performance Characteristics) (Continued)

$(V_{DD} = 2.5 \text{ V} \pm 5\%, \text{ T}_{A} = -40^{\circ}\text{C to } 85^{\circ}\text{C})$

| Parameter                                                                                                | Symbol          | Test Condition                            | Min  | Тур  | Max | Unit |

|----------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------|------|------|-----|------|

| Jitter Transfer Peaking<br>(MULTSEL[1:0] = 11,                                                           | J <sub>P</sub>  | Clock Input (MHz) =<br>9.375 to 10.438    | _    | 0.12 | TBD | dB   |

| MULTOUT = 150 to 167 MHz)*                                                                               |                 | Clock Input (MHz) =<br>18.750 to 20.875   | —    | 0.06 | TBD | dB   |

|                                                                                                          |                 | Clock Input (MHz) =<br>37.500 to 41.750   | —    | 0.03 | TBD | dB   |

|                                                                                                          |                 | Clock Input (MHz) =<br>75.000 to 83.500   | —    | 0.02 | TBD | dB   |

|                                                                                                          |                 | Clock Input (MHz) =<br>150.000 to 167.000 | —    | 0.01 | TBD | dB   |

| Acquisition Time                                                                                         | T <sub>AQ</sub> | After falling edge of<br>PWRDN/CAL        | 1.45 | 1.5  | 1.7 | ms   |

|                                                                                                          |                 | From the return of valid<br>CLKIN         | 40   | 60   | 150 | μs   |

| Frequency Difference at which PLL goes<br>out of Lock (REFCLK compared to the<br>divided down VCO clock) | LOL             |                                           | TBD  | 600  | TBD | ppm  |

| Frequency Difference at which PLL goes<br>into Lock (REFCLK compared to the<br>divided down VCO clock)   | LOCK            |                                           | TBD  | 300  | TBD | ppm  |

| *Note: See PLL Performance section of this d                                                             | ocument for     | test descriptions.                        |      |      |     |      |

## Table 5. Minimum Jitter Tolerance in Nanoseconds\* (MULTSEL[1:0] = 00, MULTOUT = 2400 to 2672 MHz)

| Frequency (Hz)                                                                 | 600-668 MHz<br>Clock Input |  |  |  |

|--------------------------------------------------------------------------------|----------------------------|--|--|--|

| < TBD                                                                          | TBD                        |  |  |  |

| TBD                                                                            | TBD                        |  |  |  |

| TBD                                                                            | TBD                        |  |  |  |

| > TBD TBD                                                                      |                            |  |  |  |

| *Note: Measured using sinusoidal jitter at stated<br>Test Condition frequency. |                            |  |  |  |

## Table 6. Minimum Jitter Tolerance in Nanoseconds\* (MULTSEL[1:0] = 01, MULTOUT = 1200 to 1336 MHz)

| Frequency (Hz)                                                                 | 300-334 MHz<br>Clock Input | 600-668 MHz<br>Clock Input |  |  |  |  |

|--------------------------------------------------------------------------------|----------------------------|----------------------------|--|--|--|--|

| < TBD                                                                          | TBD                        | TBD                        |  |  |  |  |

| TBD                                                                            | TBD                        | TBD                        |  |  |  |  |

| TBD                                                                            | TBD                        | TBD                        |  |  |  |  |

| > TBD                                                                          | TBD                        | TBD                        |  |  |  |  |

| *Note: Measured using sinusoidal jitter at stated Test<br>Condition frequency. |                            |                            |  |  |  |  |

Table 7. Minimum Jitter Tolerance in Nanoseconds\* (MULTSEL[1:0] = 10, MULTOUT = 600 to 668 MHz)

| Frequency<br>(Hz) | 37.5–<br>41.75 MHz<br>Clock Input                                          | 75–83.5 MHz<br>Clock Input | 150-167 MHz<br>Clock Input | 300–334 MHz<br>Clock Input | 600-668 MHz<br>Clock Input |  |  |

|-------------------|----------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|--|--|

| < 300             | 25.0                                                                       | 25.0                       | 25.0                       | 25.0                       | TBD                        |  |  |

| 25K               | 2.33                                                                       | 4.67                       | 9.33                       | 16.7                       | TBD                        |  |  |

| 250K              | 0.67                                                                       | 0.83                       | 1.17                       | 2.17                       | TBD                        |  |  |

| > 1M              | 0.50                                                                       | 0.58                       | 0.67                       | 0.67                       | TBD                        |  |  |

| *Note: Measured   | Note: Measured using sinusoidal jitter at stated Test Condition frequency. |                            |                            |                            |                            |  |  |

## Table 8. Minimum Jitter Tolerance in Nanoseconds\* (MULTSEL[1:0] = 11, MULTOUT = 150 to 167 MHz)

| Frequency (Hz)                                                             | 9.375–<br>10.438 MHz<br>Clock Input | 18.75–<br>20.875 MHz<br>Clock Input | 37.5–41.75 MHz<br>Clock Input | 75–83.5 MHz<br>Clock Input | 150-167 MHz<br>Clock Input |  |

|----------------------------------------------------------------------------|-------------------------------------|-------------------------------------|-------------------------------|----------------------------|----------------------------|--|

| < 300                                                                      | TBD                                 | 66.7                                | 66.7                          | 100                        | TBD                        |  |

| 6.5K                                                                       | TBD                                 | 18.0                                | 36.7                          | 66.7                       | TBD                        |  |

| 65K                                                                        | TBD                                 | 3.33                                | 4.67                          | 8.00                       | TBD                        |  |

| 325K                                                                       | TBD                                 | 2.67                                | 2.67                          | 3.33                       | TBD                        |  |

| > 1M                                                                       | TBD                                 | 2.00                                | 2.33                          | 2.67                       | TBD                        |  |

| Note: Measured using sinusoidal jitter at stated Test Condition frequency. |                                     |                                     |                               |                            |                            |  |

## Table 9. Absolute Maximum Ratings

| Parameter                                                                                          | Symbol           | Value                           | Unit     |

|----------------------------------------------------------------------------------------------------|------------------|---------------------------------|----------|

| DC Supply Voltage                                                                                  | V <sub>DD</sub>  | -0.5 to 2.8                     | V        |

| LVTTL Input Voltage                                                                                | V <sub>DIG</sub> | -0.3 to 3.6                     | V        |

| Differential Input Voltages                                                                        | V <sub>DIF</sub> | –0.3 to (V <sub>DD</sub> + 0.3) | V        |

| Maximum Current any output PIN                                                                     |                  | ±50                             | mA       |

| Operating Junction Temperature                                                                     | T <sub>JCT</sub> | -55 to 150                      | °C       |

| Storage Temperature Range                                                                          | T <sub>STG</sub> | -55 to 150                      | °C       |

| Lead Temperature (soldering 10 seconds)                                                            |                  | 300                             | °C       |

| ESD HBM Tolerance (100 pf, 1.5 k $\Omega$ )<br>CLKIN+, CLKIN–, REFCLK+, REFCLK–,<br>All other pins | _                | 1<br>1.5                        | kV<br>kV |

should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Table 10. Thermal Characteristics

| Parameter                              | Symbol | Test Condition | Value | Unit |

|----------------------------------------|--------|----------------|-------|------|

| Thermal Resistance Junction to Ambient | ΦJA    | Still Air      | 38    | °C/W |

Figure 5. Si5311 Typical Application Circuit

## **Functional Description**

The Si5311 is an integrated high speed clock multiplier and clock regenerator device based on Silicon Laboratories DSPLL<sup>™</sup> technology. The DSPLL phase locks to the clock input signal (CLKIN) and generates a phase-locked output clock (MULTOUT) at a multiple of the input clock frequency. The MULTOUT output is configured to operate in the 150–167 MHz, the 600– 668 MHz, the 1.2–1.33 GHz, or the 2.4–2.67 GHz frequency range using the MULTSEL0 and MULTSEL1 control inputs.

When the device is configured for a MULTOUT output frequency range of 150–167 MHz or 600–668 MHz, the DSPLL is also employed to regenerate an output clock (CLKOUT) that is a jitter-attenuated version of the input clock with clean rising and falling edges. The CLKOUT

output is not characterized for the MULTOUT ranges of 1.2–1.33 GHz or 2.4–2.67 GHz.

A reference clock input signal (REFCLK) is used by the DSPLL as a reference for determination of the PLL lock status. For convenience, REFCLK can be provided at any one of five frequencies, each a multiple of the CLKIN frequency. The REFCLK rate is automatically detected, so no control inputs are needed for configuration. The REFCLK input can be synchronous or asynchronous with respect to the CLKIN input. The operating ranges for the CLKIN, CLKOUT, MULTOUT, and REFCLK signals are indicated in Table 11. Values for typical applications are given in Table 12.

| MULTSEL [1:0]                  | CLKIN<br>Range (MHz)                                                                    | REFCLK = 2 <sup>n</sup> x CLKIN<br>±100 ppm<br>(see Note 2)                                                                             | CLKOUT                                                    | MULTOUT                                              |

|--------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|

| 00<br>(MULTOUT = 2.4–2.7 GHz)  | 600.00–668.00                                                                           | n = -6, -5, -4, -3, or -2                                                                                                               | See Note 1(a)                                             | 4xCLKIN                                              |

| 01<br>(MULTOUT = 1.2–1.33 GHz) | 300.00–334.00<br>600.00–668.00                                                          | n = -5, -4, -3, -2, or -1<br>n = -6, -5, -4, -3, or -2                                                                                  | See Note 1(a)<br>See Note 1(a)                            | 4xCLKIN<br>2xCLKIN                                   |

| 10<br>(MULTOUT = 600–668 MHz)  | 37.500-41.750<br>75.000-83.500<br>150.000-167.000<br>300.000-334.000<br>600.000-668.000 | n = -2, -1, 0, 1, or 2<br>n = -3, -2, -1, 0, or 1<br>n = -4, -3, -2, -1, or 0<br>n = -5, -4, -3, -2, or -1<br>n = -6, -5, -4, -3, or -2 | 1xCLKIN<br>1xCLKIN<br>1xCLKIN<br>1xCLKIN<br>See Note 1(b) | 16xCLKIN<br>8xCLKIN<br>4xCLKIN<br>2xCLKIN<br>1xCLKIN |

| 11<br>(MULTOUT = 150–167 MHz)  | 9.375–10.438<br>18.750–20.875<br>37.500–41.750<br>75.000–83.500<br>150.000–167.000      | n = 0, 1, 2, 3, or 4 $n = -1, 0, 1, 2, or 3$ $n = -2, -1, 0, 1, or 2$ $n = -3, -2, -1, 0, or 1$ $n = -4, -3, -2, -1, or 0$              | 1xCLKIN<br>1xCLKIN<br>1xCLKIN<br>1xCLKIN<br>See Note 1(b) | 16xCLKIN<br>8xCLKIN<br>4xCLKIN<br>2xCLKIN<br>1xCLKIN |

## Table 11. CLKIN, CLKOUT, MULTOUT, REFCLK Operating Ranges

Note:

1. The CLKOUT output is not valid for (a) MULTSEL[1:0] = 00 or MULTOUT[1:0] = 01

(b) MULTOUT:CLKIN ratios of 1:1 (MULTOUT = 1 x CLKIN.)

2. The REFCLK input can be set to any one of the five CLKIN multiples indicated. The REFCLK input can be asynchronous to the CLKIN input, but must be within ±100 ppm of the stated CLKIN multiple.

|                  | CLKIN (MHz) | REFCLK Input (MHz)   | MULTSEL<br>[1:0] | CLKOUT<br>(MHz) | MULTOUT output<br>(MHz) |

|------------------|-------------|----------------------|------------------|-----------------|-------------------------|

| SONET/SDH        | 9.72        | 9.72                 | 11               | 9.72            | 155.52                  |

|                  | 19.44       | 19.44                | 11               | 19.44           | 155.52                  |

|                  | 38.88       | 38.88                | 10               | 38.88           | 622.08                  |

|                  |             |                      | 11               | 38.88           | 155.52                  |

|                  | 77.76       | 77.76                | 10               | 77.76           | 622.08                  |

|                  |             |                      | 11               | 77.76           | 155.52                  |

|                  | 155.52      | 155.52               | 10               | 155.52          | 622.08                  |

|                  |             |                      | 11               |                 | 155.52                  |

|                  | 311.04      | 9.72, 19.44, 38.88,  | 01               |                 | 1244.16                 |

|                  |             | 77.76, or 155.52     | 10               | 311.04          | 622.08                  |

|                  | 622.08      | 9.72, 19.44, 38.88,  | 00               | _               | 2488.32                 |

|                  |             | 77.76, or 155.52     | 01               |                 | 1244.16                 |

|                  |             |                      | 10               |                 | 622.08                  |

| Gigabit Ethernet | 9.77        | 9.77                 | 11               | 9.77            | 156.25                  |

| 5                | 19.53       | 19.53                | 11               | 19.53           | 156.25                  |

|                  | 39.06       | 39.06                | 10               | 39.06           | 625                     |

|                  |             |                      | 11               | 39.06           | 156.25                  |

|                  | 78.125      | 78.125               | 10               | 78.125          | 625                     |

|                  |             |                      | 11               | 78.125          | 156.25                  |

|                  | 156.25      | 156.25               | 10               | 156.25          | 625                     |

|                  |             |                      | 11               |                 | 156.25                  |

|                  | 312.5       | 9.77, 19.53, 39.06,  | 01               |                 | 1250                    |

|                  |             | 78.125, or 156.25    | 10               | 312.5           | 625                     |

|                  | 625         | 9.77, 19.53, 39.06,  | 00               |                 | 2500                    |

|                  |             | 78.125, or 156.25    | 01               |                 | 1250                    |

|                  |             |                      | 10               |                 | 625                     |

| SONET/SDH FEC    | 10.41       | 10.41                | 11               | 10.41           | 166.63                  |

| (15/14)          | 20.83       | 20.83                | 11               | 20.83           | 166.63                  |

|                  | 41.66       | 41.66                | 10               | 41.66           | 666.51                  |

|                  |             |                      | 11               | 41.66           | 166.63                  |

|                  | 83.31       | 83.31                | 10               | 83.31           | 666.51                  |

|                  |             |                      | 11               | 83.31           | 166.63                  |

|                  | 166.63      | 166.63               | 10               | 166.63          | 666.51                  |

|                  |             |                      | 11               |                 | 166.63                  |

|                  | 333.26      | 10.41, 20.83, 41.66, | 01               | _               | 1333.03                 |

|                  |             | 83.31, or 166.63     | 10               | 333.26          | 666.51                  |

|                  | 666.51      | 10.41, 20.83, 41.66, | 00               |                 | 2666.06                 |

|                  |             | 83.31, or 166.63     | 01               |                 | 1333.03                 |

|                  |             |                      | 10               |                 | 666.51                  |

Table 12. Clock Values for Typical Applications

## DSPLL™

The PLL structure (shown in Figure 1 on page 4) utilizes Silicon Laboratories' DSPLL technology to produce superior jitter performance while eliminating the need for external loop filter components found in traditional PLL implementations. This is achieved by using a digital signal processing (DSP) algorithm to replace the loop filter commonly found in analog PLL designs. This algorithm processes the phase detector error term and generates a digital control value to adjust the frequency of the voltage controlled oscillator (VCO). The technology produces clocks with less jitter than is generated using traditional methods. In addition, because external loop filter components are not required, sensitive noise entry points are eliminated, thus making the DSPLL less susceptible to board-level noise sources.

## **Clock Multiplier**

The DSPLL phase locks to the clock input signal (CLKIN) and generates an output clock (MULTOUT) at a multiple of the input clock frequency. The MULTOUT output is configured to operate in the 150–167 MHz, the 600–668 MHz, the 1.2–1.33 GHz, or the 2.4–2.67 GHz frequency range using the MULTSEL0 and MULTSEL1 control inputs as indicated in Table 11. Values for typical applications are given in Table 12.

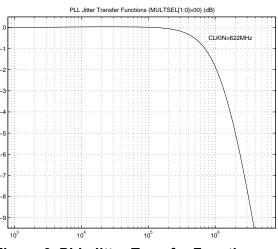

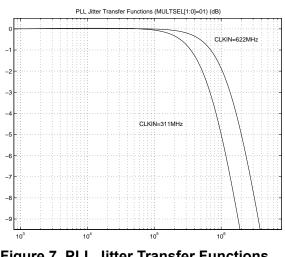

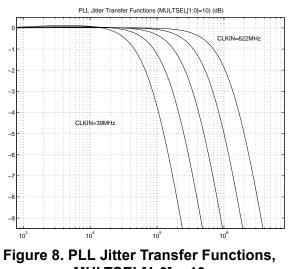

The amount of jitter present in the MULTOUT output is a function of the DSPLL jitter transfer function and jitter generation characteristic. Details are provided in the PLL Performance section of this document. (See Figures 6, 7, 8, and 9.) The amount of jitter that the DSPLL can tolerate on the CLKIN input is specified in Tables 5, 6, 7, and 8.

The DSPLL implementation in the Si5311 is insensitive to the duty cycle of the CLKIN input. The MULTOUT output will continue to exhibit a very good duty cycle characteristic even when the CLKIN input duty cycle is degraded.

## **1x Multiplication**

The Si5311 Clock Multiplier function may also be utilized as a 1x multiplier in order to provide jitter attenuation and duty cycle correction without multiplication of the input clock frequency.

**Note:** When the Si5311 is configured as a 1:1 multiplier, the CLKOUT output is not valid.

## **Clock Regeneration**

When the MULTOUT output is configured to operate in either the 150–167 MHz or the 600–667 MHz range, the Si5311 clock regeneration (CLKOUT output) is also provided. In this case, the DSPLL is used to regenerate

a jitter-attenuated version of the CLKIN input, resulting in a "clean" CLKOUT output with sharp rising and falling edges. The CLKOUT output is a resampled version of the CLKIN input with all CLKOUT transitions occurring synchronously with the rising edges of the MULTOUT output. The rising edges of CLKOUT are insensitive to the location of the falling edges of the CLKIN input. Thus the period of CLKOUT, measured rising edge to rising edge, is not affected by the CLKIN duty cycle or by jitter on the falling edge of CLKIN.

The falling edges of CLKOUT may be affected by the location of the CLKIN falling edges as follows: If the duty cycle error of CLKIN is significant relative to the period of MULTOUT, then

- 1. The CLKOUT duty cycle may deviate from 50% (the falling edge of CLKOUT will be time quantized to the nearest rising edge of MULTOUT.)

- Jitter on the falling edges of CLKIN may result in a CLKOUT duty cycle that alternates between two discrete values.

- **Note:** When the Si5310 is configured as a 1:1 multiplier, the CLKOUT output is not valid.

## **Reference Clock**

The reference clock input (REFCLK) is used to center the DSPLL and also to act as a reference for determination of the PLL lock status. REFCLK is a multiple of the CLKIN frequency, and can be provided in any one of five frequency ranges (9.375-10.438 MHz, 18.78–20.875 MHz. 37.500-41.750 MHz, 75.00-83.50 MHz, or 150-167.00 MHz). The REFCLK rate is automatically detected by the Si5311, so no control inputs are needed for REFCLK frequency selection. The REFCLK input may be synchronous or asynchronous with respect to the CLKIN input. The frequency relationship between REFCLK and CLKIN is indicated in Table 11. In many applications, it may be desirable to tie REFCLK and CLKIN together and drive them from the same clock source. The Si5311 is insensitive to the phase relationship between CLKIN and REFCLK, so these differential inputs may be driven in phase or 180° out of phase if this simplifies board layout. Values for typical applications are given in Table 12.

## DSPLL Lock Detection (Loss-of-Lock)

The Si5311 provides lock-detect circuitry that indicates whether the DSPLL has frequency locked with the incoming CLKIN signal. The circuit compares the frequency of a divided down version of the multiplier output with the frequency of the supplied reference clock. If the divided multiplier output frequency deviates from that of the reference clock by the amount specified in Table 4 on page 8, the PLL is declared out of lock, and the loss-of-lock (LOL) pin is asserted.

While out of lock, the DSPLL will try to reacquire lock

with the input clock. During reacquisition, the multiplier output (MULTOUT) will drift over a range of approximately 1% relative to the supplied reference clock. The LOL output will remain asserted until the divided multiplier output frequency differs from the REFCLK frequency by less than the amount specified in Table 4.

Note: LOL is not asserted during PWRDN/CAL.

## **PLL Performance**

The Si5311 DSPLL circuitry is designed to provide low jitter generation, high jitter tolerance, and a well-controlled jitter transfer function with low peaking. Each of these key performance parameters is described more fully in the following sections.

#### **Jitter Tolerance**

Jitter tolerance for the Si5311 is defined as the maximum peak-to-peak sinusoidal jitter that can be added to the incoming clock before the PLL exceeds its allowable operating range and loses lock. The tolerance is a function of the jitter frequency, the incoming clock rate, and the MULTSEL0/1 settings.

The jitter tolerance for specified jitter frequencies and input clock rates is given in Tables 5, 6, 7, and 8.

#### **Jitter Transfer**

Jitter transfer is defined as the ratio of output signal jitter to input signal jitter for a specified jitter frequency. The itter transfer characteristic determines the amount of input clock jitter that will be passed on to the Si5311 CLKOUT and MULTOUT outputs. The DSPLL technology used in the Si5311 provides a tightly controlled jitter transfer curve because many of the PLL gain parameters are determined by digital signal processing algorithms which do not vary over supply voltage, process, and temperature. In a system application, a well-controlled transfer curve minimizes the output clock jitter variation from board to board, providing more consistent system level iitter performance.

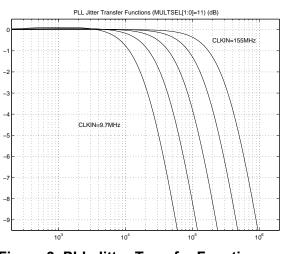

The jitter transfer characteristic is a function of the MULTSEL0/1 settings and the input clock rate. Higher input clock rates produce higher bandwidth transfer functions with lower jitter peaking. Table 4 gives the 3 dB bandwidth and peaking values for specified input clock rates and MULTSEL0/1 settings. Figures 6, 7, 8, and 9 show a family of jitter transfer curves for different input clock rates.

#### **Jitter Generation**

Jitter generation is defined as the amount of jitter produced at the output of the device with a jitter free input clock. Generated jitter arises from sources within the VCO and other PLL components. Jitter generation is a function of MULTSEL0/1 settings and input clock frequency. For clock multiplier applications, the higher

the multiplier ratio desired, the larger the jitter generation. Table 4 gives the jitter generation values for specified MULTSEL0/1 settings and input clock rates.

Figure 6. PLL Jitter Transfer Functions, MULTSEL[1:0] = 00 (MULTOUT = 2400–2672 MHz)

Figure 7. PLL Jitter Transfer Functions, MULTSEL[1:0] = 01 (MULTOUT = 1200–1336 MHz)

MULTSEL[1:0] = 10 (MULTOUT = 600–668 MHz)

Figure 9. PLL Jitter Transfer Functions, MULTSEL[1:0] = 11 (MULTOUT = 150–167 MHz)

## **Device Power-Down**

The Si5311 PWRDN/CAL input can be used to hold the device in a power-down state when not in use. When the PWRDN/CAL input is asserted (set high), the CLKOUT and MULTOUT output drivers are disabled and the positive and negative terminals of the CLKOUT and MULTOUT outputs are each tied to VDD through 100  $\Omega$  on-chip resistors. This feature is useful in reducing power consumption in applications that employ redundant clock sources. When PWRDN/CAL is released (set to low) the digital logic is reset to a known initial condition and the DSPLL circuitry is recalibrated

and will begin to lock to the incoming clock.

## **PLL Self-Calibration**

Si5311 device provides an internal self-calibration function that optimizes the loop gain parameters within the internal DSPLL. Self-calibration is initiated by a high-to-low transition of the PWRDN/CAL signal while a valid reference clock is supplied to the REFCLK input.

For optimal jitter performance, the supply voltage should be stable at 2.5 V  $\pm$ 10% when calibration is initiated. The PWRDN/CAL signal should be held high for at least 1  $\mu$ S after the supply has stabilized before transitioning low to initiate self-calibration. See Silicon Laboratories application note AN42 for suggested methods of generating the PWRDN/CAL signal for initiation of self-calibration.

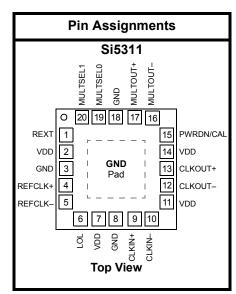

## **Device Grounding**

The Si5311 uses the GND pad on the bottom of the 20pin micro leaded package (MLP) for device ground. This pad should be connected directly to the analog supply ground. See Figures 12 and 13 for the ground (GND) pad location.

## **Bias Generation Circuitry**

The Si5311 makes use of an external resistor to set internal bias currents. The external resistor allows precise generation of bias currents which significantly reduces power consumption compared with traditional implementations that use an internal resistor. The bias generation circuitry requires a 10 k $\Omega$  (1%) resistor connected between REXT and GND.

## **Differential Input Circuitry**

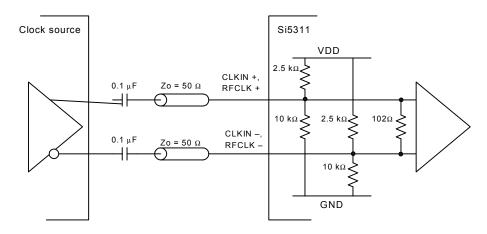

The Si5311 provides differential inputs for both the input clock (CLKIN) and the reference clock (REFCLK) inputs. An example termination for these inputs is shown in Figure 10. In applications where direct dc coupling is possible, the 0.1  $\mu$ F capacitors may be omitted. The CLKIN and REFCLK input amplifiers require input signals with minimum differential peak-to-peak voltages as specified in Table 2 on page 6.

## **Differential Output Circuitry**

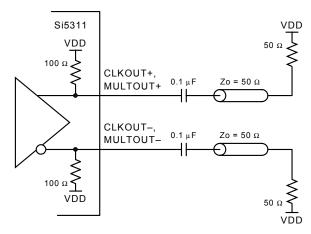

The Si5311 utilizes a current mode logic (CML) architecture to output both the regenerated clock (CLKOUT) and the multiplied clock (MULTOUT). An example of output termination with ac coupling is shown in Figure 11. For applications in which direct dc coupling is possible, the 0.1  $\mu$ F capacitors may be omitted. The differential peak-to-peak voltage swing of the CML is listed in Table 2 on page 6.

Figure 10. Input Termination for CLKIN and REFCLK (AC Coupled)

Figure 11. Output Termination for CLKOUT and MULTOUT (AC Coupled)

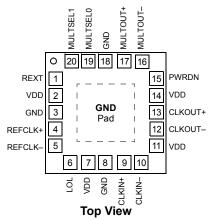

## Pin Descriptions: Si5311

Figure 12. Si5311 Pin Configuration

| Table | 13  | Si5311 | Pin   | Descri | ntions |

|-------|-----|--------|-------|--------|--------|

| Table | 15. | 010011 | F 111 | Deach  | puona  |

| Pin #                    | Pin Name            | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|---------------------|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | REXT                |     |              | External Bias Resistor.                                                                                                                                                                                                                                                                                                                                |

|                          |                     |     |              | This resistor is used by onboard circuitry to estab-<br>lish bias currents within the device. This pin must<br>be connected to GND through a 10 k $\Omega$ (1%) resis-<br>tor.                                                                                                                                                                         |

| 2, 7, 11, 14             | VDD                 |     | 2.5 V        | Supply Voltage.<br>Nominally 2.5 V.                                                                                                                                                                                                                                                                                                                    |

| 3, 8, 18, and<br>GND Pad | GND                 |     | GND          | Supply Ground.<br>Nominally 0.0 V. The GND pad found on the bottom<br>of the 20-pin micro leaded package (see Figure 13)<br>must be connected directly to supply ground.                                                                                                                                                                               |

| 4, 5                     | REFCLK+,<br>REFCLK– | I   | See Table 2  | <b>Differential Reference Clock.</b><br>The reference clock sets the initial operating fre-<br>quency used by the onboard PLL for clock regener-<br>ation and multiplication. Additionally, the reference<br>clock is used as a reference in generation of the<br>LOL output and to bound the frequency drift of<br>MULTOUT when CLKIN is not present. |

| 6                        | LOL                 | 0   | LVTTL        | <b>Loss of Lock.</b><br>This output is driven high when a divided version of the clock multiplier output deviates from the reference clock frequency by the amount specified in Table 4 on page 8.                                                                                                                                                     |

| 9, 10                    | CLKIN+,<br>CLKIN–   | I   | See Table 2  | Differential Clock Input.<br>Differential input clock from which MULTOUT is<br>derived.                                                                                                                                                                                                                                                                |

| Pin #  | Pin Name              | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|-----------------------|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12, 13 | CLKOUT–,<br>CLKOUT+   | 0   | CML          | Description           Differential Clock Output.           The clock output signal is a regenerated version of the input clock signal present on CLKIN. It is phase aligned with MULTOUT and is updated on the rising edge of MULTOUT.           Notes: The CLKOUT output is not valid for MULTSEL[1:0]           = 00 or MULTSEL[1:0] = 01. The CLKOUT output is also not valid for MULTOUT: CLKIN ratios of 1:1 (MULTOUT = 1x CLKIN).           Connection of an improperly terminated transmission line to the CLKOUT output can cause reflections that may adversely affect the performance of the MULTOUT output. If the CLKOUT output is not used, these pins should be either tied to V <sub>DD</sub> (recommended), left unconnected, or connected to a properly terminated transmission line. |

| 15     | PWRDN/CAL             | Ι   | LVTTL        | <ul> <li>Power Down.</li> <li>To shut down the high-speed outputs and reduce power consumption, hold this pin high. For normal operation, hold this pin low.</li> <li>Calibration.</li> <li>To initiate an internal self-calibration, force a high-to-low transition on this pin. (See "PLL Self-Calibration," on page 18.)</li> <li>Note: This input has a weak internal pulldown.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16, 17 | MULTOUT–,<br>MULTOUT+ | 0   | CML          | <ul> <li>Differential Multiplier Output.</li> <li>The multiplier output is generated from the signal present on CLKIN. In the absence of CLKIN, the REFCLK is used to bound the frequency of MUL-TOUT according to Table 4 on page 8.</li> <li>Note: Connection of an improperly terminated transmission line to the MULTOUT output can cause reflections that may adversely affect the CLKOUT output. If the MULTOUT output is not used, these pins should be either tied to V<sub>DD</sub> (recommended), left unconnected, or connected to a properly terminated transmission line.</li> </ul>                                                                                                                                                                                                      |

| 19     | MULTSEL1,<br>MULTSEL0 | I   | LVTTL        | Multiplier Rate Select.<br>These pins configure the onboard PLL-based clock<br>multiplier for clock generation at one of four user<br>selectable clock rates.<br>Note: These inputs have weak internal pulldowns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20     | NC                    |     |              | No Connect.<br>This pin should be tied to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 13. Si5311 Pin Descriptions (Continued)

# **Ordering Guide**

| Part Number | Package    | Temperature   |

|-------------|------------|---------------|

| Si5311-BM   | 20-pin MLP | –40°C to 85°C |

## Table 14. Ordering Guide

## Package Outline

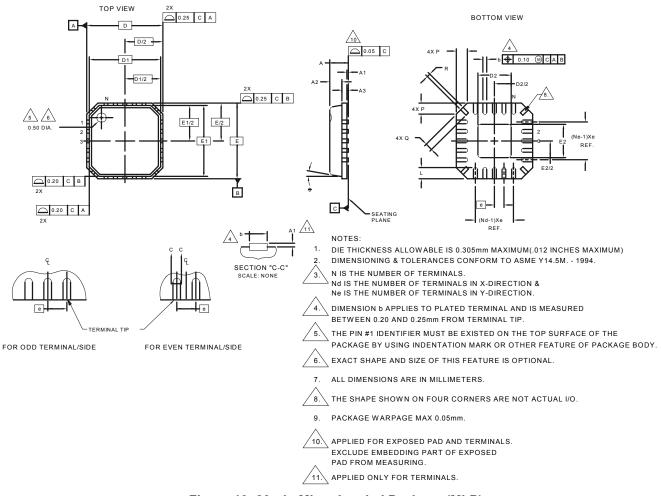

Figure 13 illustrates the package details for the Si5311. Table 15 lists the values for the dimensions shown in the illustration.

Figure 13. 20-pin Micro Leaded Package (MLP)

Table 15. Package Diagram Dimensions

| Symbol | Millimeters |      |      |  |

|--------|-------------|------|------|--|

|        | Min Nom Max |      |      |  |

| Α      | _           | 0.85 | 1.00 |  |

| A1     | 0.00        | 0.01 | 0.05 |  |

| A2     | _           | 0.65 | 0.80 |  |

| A3     | 0.20 REF    |      |      |  |

| b      | 0.18        | —    | 0.30 |  |

| D      | 4.00 BSC    |      |      |  |

| D1     | 3.75 BSC    |      |      |  |

| D2     | 1.95        | 2.10 | 2.25 |  |

| е      | 0.50 BSC    |      |      |  |

| E      | 4.00 BSC    |      |      |  |

| Symbol | Millimeters |          |      |  |  |

|--------|-------------|----------|------|--|--|

|        | Min Nom Max |          |      |  |  |

| E1     |             | 3.75 BSC |      |  |  |

| E2     | 1.95        | 2.10     | 2.25 |  |  |

| N      | 20          |          |      |  |  |

| Nd     | 5           |          |      |  |  |

| Ne     | 5           |          |      |  |  |

| L      | 0.50        | 0.60     | 0.75 |  |  |

| Р      | 0.24        | 0.42     | 0.60 |  |  |

| Q      | 0.30        | 0.40     | 0.65 |  |  |

| R      | 0.13        | 0.17     | 0.23 |  |  |

| θ      |             | —        | 12°  |  |  |

## **Contact Information**

#### Silicon Laboratories Inc.

4635 Boston Lane Austin, TX 78735 Tel: 1+(512) 416-8500 Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Email: productinfo@silabs.com Internet: www.silabs.com

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories, Silicon Labs, and DSPLL are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.