### Quad, 12-Bit, Voltage Output D/A Converter

- Low Cost

- Four 12–Bit DAC's on a Single Chip

- Low Power 80 mW (20mW/DAC)

- Double-Buffered Inputs

- ±5V Supply Operation

- Voltage Outputs, ±4.5V Range

- Midscale Preset, Zero Volts Out

- Guaranteed +0.5 LSB Max INL

- Guaranteed +0.75 LSB Max DNL

- 2MHz 4-Quadrant Multiplying Bandwidth

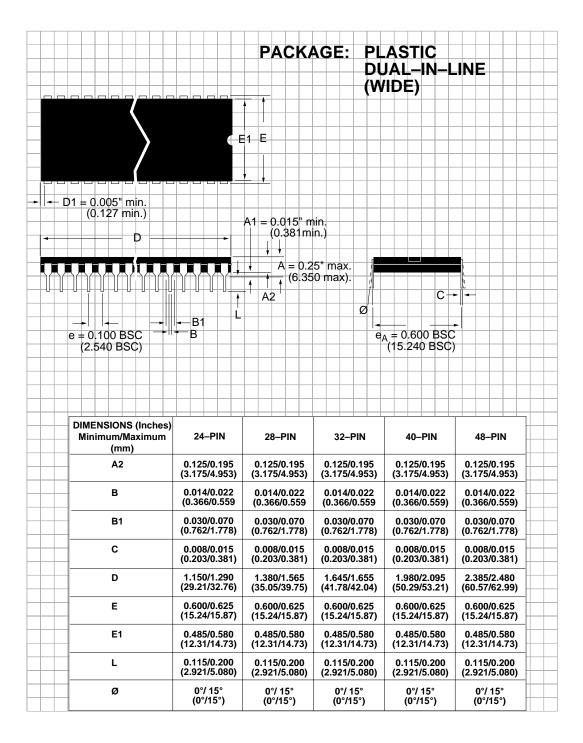

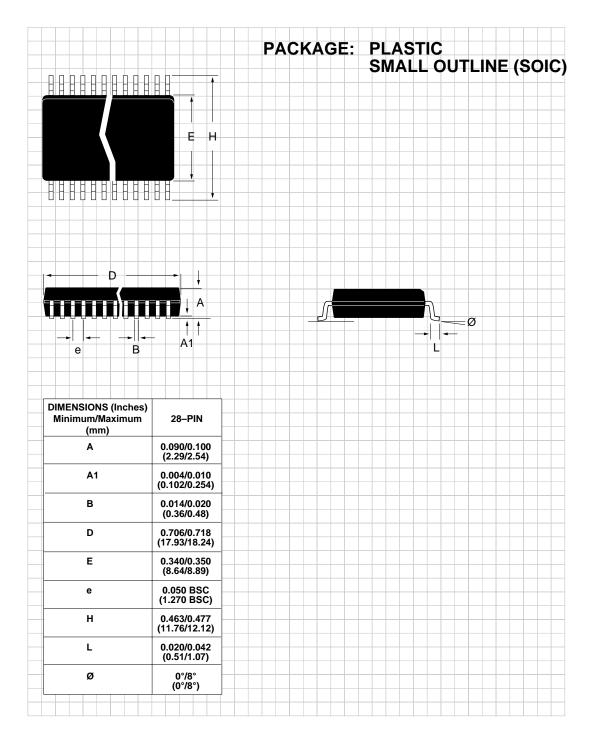

- 28-pin SOIC and Plastic DIP Packages

- Either 12 or 8 bit µP bus

#### **DESCRIPTION**

The **SP9504** is a low power replacement for the popular SP9345, Quad 12-Bit Digital-to-Analog Converter. It features  $\pm 4.5$ V output swings when using  $\pm 5$  volt supplies. The converter is double-buffered for easy microprocessor interface. Each 12-bit DAC is independently addressable and all DACs may be simultaneously updated using a single transfer command. The output settling-time is specified at  $4\mu s$ . The **SP9504** is available in 28–pin SOIC and plastic DIP packages, specified over commercial temperature range.

#### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| V <sub>DD</sub> - GND             | 0.3V, +6.0V                       |

|-----------------------------------|-----------------------------------|

| V GND                             | +0.3V6.0V                         |

| V <sub>DD</sub> - V <sub>SS</sub> | -0.3V. +12.0V                     |

| V SS                              | V V                               |

| V <sub>REF</sub> D <sub>IN</sub>  | V V                               |

| Power Dissipation                 | v <sub>SS</sub> , v <sub>DD</sub> |

| rower Dissipation                 |                                   |

| Plastic DIP                       | 375mW                             |

| (derate 7mW/°C above +70°C)       |                                   |

| Small Outline                     | 375mW                             |

| (derate 7mW/°C above +70°C)       |                                   |

CAUTION:

ESD (ElectroStatic Discharge) sensitive device. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts.

Personnel should be properly grounded prior to handling this device. The protective foam should be discharged to the destination socket before devices are removed.

#### **SPECIFICATIONS**

(Typical at 25°C;T, INN)  $\leq$  T,  $\leq$ T, INN,  $\leq$  Y,  $\leq$  T,  $\leq$  T, INN,  $\leq$  Y,  $\leq$  T,  $\leq$  T, INN,  $\leq$  T,  $\leq$  T,

| PARAMETER              | MIN.         | TYP.          | MAX.          | UNITS | CONDITIONS                        |

|------------------------|--------------|---------------|---------------|-------|-----------------------------------|

| DIGITAL INPUTS         |              |               |               |       |                                   |

| Logic Levels           |              |               |               |       |                                   |

| V <sub>IH</sub>        | 2.4          |               |               | Volts |                                   |

| $V_{\text{\tiny IL}}$  |              |               | 8.0           | Volts |                                   |

| 4 Quad, Bipolar Coding |              | Offset Bina   | ry            |       |                                   |

| REFERENCE INPUT        |              |               |               |       |                                   |

| Voltage Range          |              | <u>+</u> 3    | <u>+</u> 4.5  | Volts | Note 5                            |

| Input Resistance       | 1.5          | 2.2           |               | kΩ    | $D_{IN} = 1,877$ ; code dependent |

| ANALOG OUTPUT          |              |               |               |       |                                   |

| Gain                   |              |               |               |       |                                   |

| –K                     |              | <u>+</u> 0.5  | <u>+</u> 2.0  | LSB   | $V_{REF} = \pm 3V$ ; Note 3       |

| _J                     |              | <u>+</u> 1.0  | <u>+</u> 4.0  | LSB   | $V_{REF} = \pm 3V$ ; Note 3       |

| –K, –J                 |              | <u>+</u> 1.0  | <u>+</u> 5.0  | LSB   | $V_{REF} = \pm 4.5V$ ; Note 3     |

| Initial Offset Bipolar |              | <u>+</u> 0.25 | <u>+</u> 3.0  | LSB   | $D_{IN} = 2,048$                  |

| Voltage Range Bipolar  |              | <u>+</u> 3.0  | <u>+</u> 4.5  | Volts |                                   |

| Output Current         | <u>+</u> 5.0 |               |               | mA    | $V_{REF} = \pm 3V$                |

|                        | <u>+</u> 0.5 |               |               | mA    | $V_{REF} = \pm 4.5V$              |

| STATIC PERFORMANCE     |              |               |               |       |                                   |

| Resolution             | 12           |               |               | Bits  |                                   |

| Integral Linearity     |              |               |               |       |                                   |

| –K                     |              | <u>+</u> 0.25 | <u>+</u> 0.5  | LSB   | $V_{REF} = \pm 3V$ ; Note 3       |

| –J                     |              | <u>+</u> 0.5  | <u>+</u> 1.0  | LSB   | $V_{REF} = \pm 3V$ ; Note 3       |

| –K, –J                 |              | <u>+</u> 0.5  | <u>+</u> 3.0  | LSB   | $V_{REF} = \pm 4.5V$ ; Note 3     |

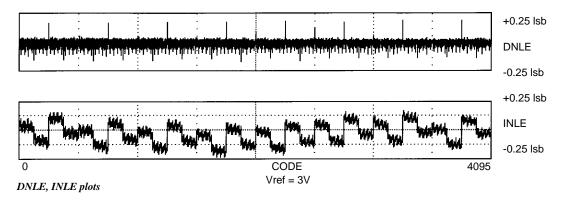

| Differential Linearity |              |               |               |       |                                   |

| -K                     |              | <u>+</u> 0.25 | <u>+</u> 0.75 | LSB   |                                   |

| -J                     |              | <u>+</u> 0.25 | <u>+</u> 1.0  | LSB   |                                   |

| Monotonicity           | •            | Guarantee     | d             |       |                                   |

| DYNAMIC PERFORMANCE    |              |               |               |       |                                   |

| Multiplying Bandwidth  |              | 2             |               | MHz   |                                   |

| Settling Time          |              |               |               |       |                                   |

| Small Signal           |              | 0.5           |               | μs    | to 0.012%                         |

| Full Scale             |              | 4             |               | μs    | to 0.012%                         |

| Slew Rate              |              | 4             |               | V/μs  |                                   |

#### **SPECIFICATIONS (CONTINUED)**

(Typical at 25°C; T<sub>MIN</sub>  $\leq$  T<sub>A</sub> $\leq$ T<sub>MAX</sub>; V<sub>DD</sub> = +5V, V<sub>SS</sub> = -5V, V<sub>REF</sub> = +3V; CMOS logic level digital inputs; specifications apply to all grades unless otherwise noted.)

| PARAMETER                              | MIN.           | TYP.      | MAX. | UNITS  | CONDITIONS                           |

|----------------------------------------|----------------|-----------|------|--------|--------------------------------------|

| SWITCHING CHARACTERIS                  | STICS          |           |      |        |                                      |

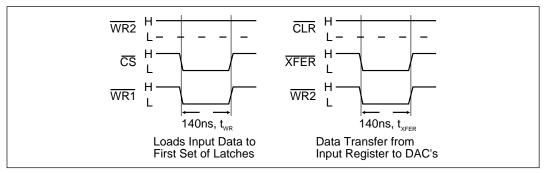

| t <sub>DS</sub> Data Set Up Time       | 140            | 100       |      | ns     | to rising edge of WR1                |

| t <sub>DN</sub> Data Hold Time         | 0              |           |      | ns     | Figure 4                             |

| t <sub>wR</sub> Write Pulse Width      | 140            | 100       |      | ns     |                                      |

| t <sub>xfer</sub> Transfer Pulse Width | 140            | 100       |      | ns     |                                      |

| t <sub>wc</sub> Total Write Command    | 280            | 200       |      | ns     |                                      |

| STABILITY                              |                |           |      |        |                                      |

| Gain                                   |                | 15        |      | ppm/°C | t <sub>min</sub> to t <sub>max</sub> |

| Bipolar Zero                           |                | 15        |      | ppm/°C | t <sub>min</sub> to t <sub>max</sub> |

| POWER REQUIREMENTS                     |                |           |      |        | Note 5                               |

| V <sub>DD</sub><br>-J, -K              |                | 8         | 11   | mA     | +5V, <u>+</u> 3%; Note 4, 5          |

|                                        |                |           | '''  | ША     | -5V, +3%; Note 4, 5                  |

| V <sub>SS</sub><br>-J, -K              |                | 8         | 11   | mA     | ,                                    |

| Power Dissipation                      |                | 80        |      | mW     |                                      |

| ENVIRONMENTAL AND ME                   | L.             |           |      |        |                                      |

| Operating Temperature                  | _              |           |      |        |                                      |

| _J, _K                                 | 0              |           | +70  | °C     |                                      |

| Storage                                | -60            |           | +150 | °C     |                                      |

| Package                                | 28-pin Plastic |           | DID  |        |                                      |

| P<br>S                                 |                | 8–pin SOI |      |        |                                      |

#### Notes:

- Integral Linearity, for the SP9504, is measured as the arithmetic mean value of the magnitudes of the greatest positive deviation and the greatest negative deviation from the theoretical value for any given input condition.

- Differential Linearity is the deviation of an output step from the theoretical value of 1 LSB for any two adjacent digital input codes.

- 3.  $1 LSB = 2*V_{REF}/4,096$ .

- 4.  $V_{RFF} = 0V$ .

- 5. The following power up sequence is recommended to avoid latch up: Vss (-5V), Vdd (+5V), REF IN.

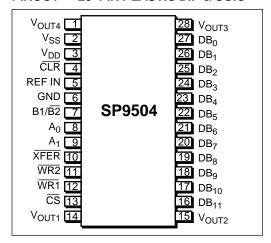

#### **PIN ASSIGNMENTS**

Pin 1 —  $V_{OUT4}$  — Voltage Output from DAC4.

Pin 2 — V<sub>ss</sub> — –5V Power Supply Input.

Pin 3 —  $V_{DD}$  — +5V Power Supply Input.

Pin 4 —  $\overline{\text{CLR}}$  —  $\overline{\text{Clear}}$ . Gated with  $\overline{\text{WR2}}$  (pin 11). Active low. Clears all DAC outputs to 0V.

Pin 5 — REF IN — Reference Input for DACs.

Pin 6 — GND — Ground.

Pin 7 — B1/B2 — Byte 1/Byte 2 — Selects Data Input Format. A logic "1" on pin 7 selects the 12-bit mode, and all 12 data bits are presented to the DAC(s) unchanged; a logic "0" selects the 8-bit mode, and the four LSBs are connected to the four MSBs, allowing an 8-bit MSB-justified interface.

Pins 8 and 9 —  $A_0$  &  $A_1$  — Address for DAC Selection.  $A_1/A_0 = 0/0 = DAC1$ ; 0/1 = DAC2; 1/0 = DAC3; 1/1 = DAC4.

Pin 10 —  $\overline{\text{XFER}}$  —  $\overline{\text{Transfer}}$ . Gated with  $\overline{\text{WR2}}$  (pin 11); loads all DAC registers simultaneously. Active low.

Pin 11 — WR2 — Write Input 2 — In conjunction with XFER (pin 10), controls the transfer of data from the input registers to the DAC registers. In conjunction with CLR (pin 4), the DAC registers are forced to 1000 0000 0000 and the DAC outputs will settle to 0V. Active low.

Pin 12 —  $\overline{WR1}$  —  $\overline{Write Input1}$  — In conjunction with  $\overline{CS}$  (pin 13), enables input register selection, and controls the transfer of data from the input bus to the input registers. Active low.

Pin 13 —  $\overline{\text{CS}}$  —  $\overline{\text{Chip Select}}$  — Enables writing data to input registers and/or transferring data from input bus to DAC registers. Active low.

#### PINOUT — 28-PIN PLASTIC DIP & SOIC

Pin 14 —  $V_{OUT1}$  — Voltage Output from DAC1.

Pin 15 — V<sub>OLT2</sub> — Voltage Output from DAC2.

Pin 16 — DB<sub>11</sub> — Data Bit 11; Most Significant Bit.

Pin 17 — DB<sub>10</sub> — Data Bit 10.

Pin  $18 - DB_{q}$  — Data Bit 9.

Pin  $19 - DB_8$  — Data Bit 8.

Pin 20 —  $DB_7$  — Data Bit 7.

Pin 21 —  $DB_6$  — Data Bit 6.

$Pin \ 22 \ --DB_{_{5}} \ --Data \ Bit \ 5.$

$Pin 23 - DB_4 - Data Bit 4.$

Pin 24 —  $DB_3$  — Data Bit 3.

Pin 25 —  $DB_2$  — Data Bit 2.

Pin 26 — DB<sub>1</sub> — Data Bit 1.

Pin 27 — DB<sub>o</sub> — Data Bit 0; LSB

Pin 28 —  $V_{OUT3}$  — Voltage Output from DAC3.

#### **FEATURES**

The **SP9504** is a low–power replacement for the popular SP9345, Quad 12-Bit Digital-to-Analog Converter. This Quad, Voltage Output, 12-Bit Digital-to-Analog Converter features ±4.5 V output swings when using ±5 volt supplies. The input coding format used is standard offset binary, *Table 1*.

The converterutilizes double-buffering on each of the 12 parallel digital inputs, for easy microprocessor interface. Each 12-bit DAC is independently addressable and all DACs may be simultaneously updated using a single  $\overline{\text{XFER}}$  command. The output settling-time is specified at 4 $\mu$ s to full 12–bit accuracy when driving a 5Kohm, 50pF load combination. The SP9504, Quad 12-Bit Digital-to-Analog Converter is ideally suited for applications such as ATE, process controllers, robotics, and instrumentation. The SP9504 is available in 28–pin plastic DIP or SOIC packages, specified over the commercial (0°C to +70°C) temperature range.

#### THEORY OF OPERATION

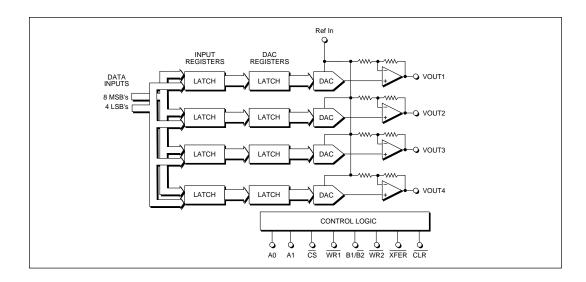

The SP9504 consists of five main functional blocks—input data multiplexer, data registers, control logic, four 12-bit D/A converters, and four bipolar output voltage amplifiers. The input data multiplexer is designed to interface to either 12- or 8-bit microprocessor data busses. The input data format is controlled by the B1/B2 signal — a logic "1" selects the 12-bit mode, while a logic "0" selects the 8-bit mode. In the 12-bit mode the data is transferred to the input registers without changes in its format. In the 8-bit mode, the four least significant bits (LSBs) are connected to the

|      | INPUT                       |      | OUTPUT          |  |  |  |  |

|------|-----------------------------|------|-----------------|--|--|--|--|

| MSB  |                             | LSB  |                 |  |  |  |  |

| 1111 | 1111                        | 1111 | VREF - 1 LSB    |  |  |  |  |

| 1111 | 1111                        | 1110 | VREF - 2 LSB    |  |  |  |  |

| 1000 | 0000                        | 0001 | 0 + 1 LSB       |  |  |  |  |

| 1000 | 0000                        | 0000 | 0               |  |  |  |  |

| 0000 | 0000                        | 0001 | -VREF + 1 LSB   |  |  |  |  |

| 0000 | 0000                        | 0000 | -VREF           |  |  |  |  |

|      | $1 LSB = \frac{2V_{REF}}{}$ |      |                 |  |  |  |  |

|      |                             |      | 2 <sup>12</sup> |  |  |  |  |

Table 1. Offset Binary Coding

four most significant bits (MSBs), allowing an 8-bit MSB-justified interface. All data inputs are enabled using the  $\overline{\text{CS}}$  signal in both modes. The digital inputs are designed to be both TTL and 5V CMOS compatible.

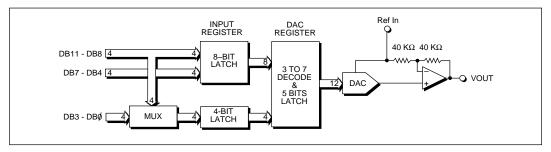

In order to reduce the DAC full scale output sensitivity to the large weighting of the MSB's found in conventional R-2R resistor ladders, the 3 MSB's are decoded into 8 equally weighted levels. This reduces the contribution of each bit by a factor of 4, thus, reducing the output sensitivity to mismatches in resistors and switches by the same amount. Linearity errors and stability are both improved for the same reasons.

Each D/A converter is separated from the data bus by two registers, each consisting of level-triggered latches, Figure 1. The first register (input register) is 12-bits wide. The input register is selected by the address input  $A_0$  and  $A_1$ , and is enabled by the  $\overline{CS}$  and  $\overline{WR1}$  signals. In the 8-bit mode, the enable signal to the 8 MSB's is disabled by a logic low on B1/ $\overline{B2}$  to allow the 4 LSB's to be updated. The second register (DAC register), accepts the decoded 3 MSB's plus the 9 LSB's. The four DAC registers are updated simultaneously for all DAC's using the  $\overline{XFER}$  and  $\overline{WR2}$  signals. Using the  $\overline{CLR}$  and  $\overline{WR2}$  signals or the power-on-reset, (enabled when the power is switched on) the DAC registers are set to 1000 0000 0000 and the DAC outputs will settle to 0V.

Using the control logic inputs, the user has full control of address decoding, chip enable, data transfer and clearing of the DAC's. The control logic inputs are level triggered, and like the data inputs, are TTL and CMOS compatible. The truth table (*Table 2*) shows the appropriate functions associated with the states of the control logic inputs.

The DACs themselves are implemented with a precision thin–film resistor network and CMOS transmission gate switches. Each D/A converter is used to convert the 12–bit input from its DAC register to a precision voltage.

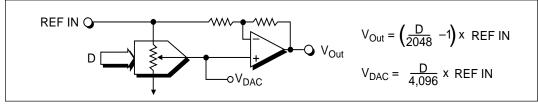

The bipolar voltage output of the **SP9504** is created on-chip from the DAC Voltage Output ( $V_{DAC}$ ) by using an operational amplifier and two feedback resistors connected as shown in *Figure 2*. This configuration produces a  $\pm 4.5 \text{V}$  bipolar output range with standard offset binary coding.

Figure 1. Detailed Block Diagram (only one DAC shown)

# USING THE SP9504 WITH DOUBLE-BUFFERED INPUTS Loading Data

To load a 12-bit word to the input register of each DAC, using a 12-bit data bus, the sequence is as follows:

- 1)  $\underline{\text{Set XFER}} = 1, \underline{\text{B1/B2}} = 1, \overline{\text{CLR}} = 1, \overline{\text{WR1}} = 1, \overline{\text{WR2}} = 1, \overline{\text{CS}} = 1.$

- 2) Set  $A_1$  and  $A_0$  (the DAC address) to the desired DAC  $-0.0 = DAC_1$ ;  $0.1 = DAC_2$   $1.0 = DAC_3$ ;  $1.1 = DAC_4$ .

- 3) Set D11 (MSB) through D0 (LSB) to the desired digital input code.

- 4) Load the word to the selected DAC by cycling WR1 and CS through the following sequence:

5) Repeat sequence for each input register.

To load a 12-bit word to the input register of each DAC, using an 8-bit data bus, the sequence is as follows:

- 1)  $\underline{\text{Set }\overline{\text{XFER}}}=1, \underline{\text{B1}}/\underline{\text{B2}}=1, \overline{\text{CLR}}=1, \overline{\text{WR1}}=1, \overline{\text{WR2}}=1, \overline{\text{CS}}=1.$

- 2) Set D11 through D4 to the 8 MSB's of the desired digital input code.

- 3) Load the 8 MSB's of the digital word to the selected input register by cycling WR1 and CS through the "1" "0" "1" sequence.

- 4) Reset B1/\overline{B2} from "1" \(---\)"

- 5) Set D11 (MSB) through D8 to the 4LSB's of the digital input code.

- 6) Load the 4LSB's by cycling WR1 and CS through the "1" "0" "1" sequence.

- 7) Repeat sequence for each input register.

| A <sub>1</sub> | A <sub>o</sub>                                                                                                                  | cs | WR1 | B1/B2 | WR2 | XFER | CLR | FUNCTION                                                          |

|----------------|---------------------------------------------------------------------------------------------------------------------------------|----|-----|-------|-----|------|-----|-------------------------------------------------------------------|

| 0              | 0                                                                                                                               | 7. | T   | 1     | 1   | Х    | Х   | Address DAC 1 and load input register                             |

| 0              | 0                                                                                                                               | v  | v   | 0     | 1   | Х    | Х   | Address DAC 1 and load 4 LSBs                                     |

| 0              | 1                                                                                                                               | v  | ъ   | 1     | 1   | Х    | Х   | Address DAC 2 and load input register                             |

| 0              | 1                                                                                                                               | T  | ъ   | 0     | 1   | Х    | Х   | Address DAC 2 and load 4 LSBs                                     |

| 1              | 0                                                                                                                               | v  | 7.  | 1     | 1   | Х    | Х   | Address DAC 3 and load input register                             |

| 1              | 0                                                                                                                               | v  | v   | 0     | 1   | Х    | Х   | Address DAC 3 and load 4 LSBs                                     |

| 1              | 1                                                                                                                               | v  | ݖ   | 1     | 1   | Х    | Х   | Address DAC 4 and load input register                             |

| 1              | 1                                                                                                                               | v  | v   | 0     | 1   | Х    | Х   | Address DAC 4 and load 4 LSBs                                     |

| Х              | Х                                                                                                                               | ** | **  | Х     | 7.  | ᅩ    | 1   | Transfer data from input registers to DAC registers               |

| Х              | Х                                                                                                                               | Х  | Х   | Х     | ᅩ   | 1    | 7   | Sets all DAC output voltages to 0V                                |

| Х              | Х                                                                                                                               | 1  | 1   | Х     | 0   | 0    | 7   | Temporarily force all DAC output voltages to 0V, while CLR is low |

| Х              | Х                                                                                                                               | 1  | Х   | Х     | Х   | Х    | Х   | Invalid state with any other control line active                  |

| Х              | Х                                                                                                                               | Х  | 1   | Х     | Х   | Х    | Х   | Invalid state with any other control line active                  |

| X =            | X = Don't care; ** = Don't care; however, $\overline{CS}$ and $\overline{WR1}$ = 1 will inhibit changes to the input registers. |    |     |       |     |      |     |                                                                   |

Table 2. Control Logic Truth Table

Figure 2. Transfer Function

#### TRANSFERRING DATA

To transfer the four 12-bit words in the four input registers to the four DAC registers:

- 1) Set  $\overline{CLR}=1$ ,  $\overline{CS}=1$ ,  $\overline{WR1}=1$ .

- 2) Cycle WR2 and XFER through the "1" "0" "1" sequence.

To set the outputs of the four DAC's to 0V, cycle  $\overline{WR2}$  and  $\overline{CLR}$  through the "1" — "0" — "1" sequence, while keeping  $\overline{XFER}$ =1.

#### ONE LATCH. OR NO LATCHES

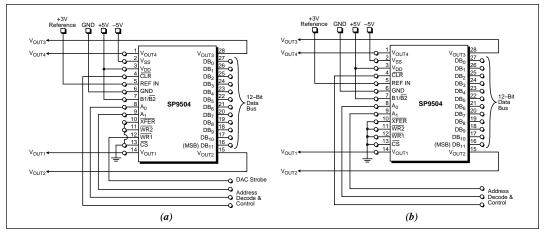

The latches that form the registers can be used in a "semi-" transparent mode, and a "fully-" transparent mode. In order to use the **SP9504** in either mode the user must be interfaced to a 12-bit bus only (B1=1).

The semi–transparent mode is set up such that the second set of latches is transparent and the first set is used to latch the incoming data. Data is latched into the first set rather than the second set, in order to minimize glitch energy induced from the data formatting. In this mode,  $\overline{XFER}$ ,  $\overline{WR2}$  and  $\overline{CS}$  are tied low, and  $\overline{WR1}$  is used to strobe the data to the addressed DAC. Each DAC is addressed using the address lines  $A_0$  and  $A_1$ . After the appropriate DAC has been selected and the data is settled at the digital inputs,

bringing  $\overline{WR1}$  low will transfer the data to the addressed DAC. The user should be sure to bring  $\overline{WR1}$  high again so that the next selected DAC will not be overwritten by the last digital code. This mode of operation may be useful in applications where preloading of the input registers is not necessary *Figure 3a*.

A fully transparent mode is realized by tying WR1, CS, WR2, and XFER all low. In this mode, anything that is written on the 12-bit data bus will be passed directly to the selected DAC. Since both latches are not being used, the previous digital word will be overwritten by the new data as soon as the address changes. This may be useful should the user want to calibrate a circuit, by taking full scale or zero scale readings for all four DAC's, *Figure 3b*.

#### ZEROING DAC OUTPUTS

While keeping  $\overline{\text{XFER}}$  pin high, the DAC outputs can be set to zero volts two different ways. The first involves the  $\overline{\text{CLR}}$  and  $\overline{\text{WR2}}$  pins. In normal operation, the  $\overline{\text{CLR}}$  pin is tied high, thus, disabling the clear function. By cycling  $\overline{\text{WR2}}$  and  $\overline{\text{CLR}}$  through "1" —"0" —"1" sequence, a digital code of 1000 0000 0000 is written to all four DAC registers, producing a half scale output or zero volts. The second utilizes the built in power-

on-reset. Using this feature, the **SP9504** can be configured such that during power-up, the second register will be digitally "zeroed", producing a zero volt output at each of the four DAC outputs. This is achieved by powering the unit up with XFER in a high state. Thus, with no external circuitry, the **SP9504** can be powered up with the analog outputs at a known, zero volt output level.

## TEMPORARILY FORCING ALL DAC OUTPUTS TO 0V

Set  $\overline{WR1}$ =1,  $\overline{CS}$ =1,  $\overline{WR2}$ =0,  $\overline{XFER}$ =0. The DAC registers can be temporarily forced to 1000 0000 0000 0000 by bringing the  $\overline{CLR}$  pin low. This will force the DAC outputs to 0V, while the  $\overline{CLR}$  pin remains low. When the  $\overline{CLR}$  pin is brought back high, the digital code at the DAC registers will again appear at the DAC's digital inputs, and the analog outputs will return to their previous values.

Figure 3. Latch Control Options — (a) Semi-Transparent Latch Mode; (b) Fully-Transparent Latch Mode

Figure 4. Timing

# ORDERING INFORMATION Model Temperature Range Package Monolithic 12-Bit Quad DAC Voltage Output: 8P9504JP 0°C to +70°C 28-pin, 0.6" Plastic DIP SP9504KP 0°C to +70°C 28-pin, 0.6" Plastic DIP SP9504JS 0°C to +70°C 28-pin, 0.35" SOIC SP9504KS 0°C to +70°C 28-pin, 0.35" SOIC

Please consult the factory for pricing and availability on a Tape-On-Reel option.

SIGNAL PROCESSING EXCELLENCE

#### Sipex Corporation

Headquarters and Sales Office 22 Linnell Circle Billerica, MA 01821 TEL: (978) 667-8700 FAX: (978) 670-9001 e-mail: sales@sipex.com

Sales Office 233 South Hillview Drive

Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.