#### INTRODUCTION

The KB8821/22/23 are high performance dual frequency synthesizers with integrated prescalers designed for RF operation up to 1.2GHz/2.0GHz/2.5GHz and IF operation up to 520MHz. The KB8821/22/23 contain dual-modulus prescalers. The RF synthesizer adopts a 64/65 or an 128/129 prescaler(32/33 or 64/65 for the KB8823) and the IF synthesizer adopts an 8/9 or a 16/17 prescaler.

Using a proprietary digital phase-locked-loop technique, the KB8821/22/23 have linear phase detector characteristic and can be used for very stable, low noise local oscillator signal. Supply voltage can range from 2.7V to 4.0V. The KB8821/22/23 are now available in a 20-TSSOP/24-QFN package.

#### **FEATURES**

- Very low current consumption(8821:3.5mA, 22:4.5mA, 23:5.5mA)

- Operating voltage range: 2.7 ~ 4.0V

- Selectable power saving mode(Icc=1uA typical @3V)

- Dual modulus prescaler :

KB8821/22 (RF) 64/65 or 128/129 KB8823 (RF) 32/33 or 64/65 KB8821/22/23 (IF) 8/9 or 16/17

- · Programmability via serial bus interface

- · No dead-zone PFD

- · Variable charge pump output current

- High speed lock mode

#### ORDERING INFORMATION

| Device       | Package      | Tem. Range  |

|--------------|--------------|-------------|

| KB8821/22/23 | 20-TSSOP-225 | -40 ~ +85°C |

| KB8821/22/23 | 24-QFN*      | -40 ~ +85°C |

<sup>\*</sup> QFN : Quad Flat Non-leaded(see Addendum).

#### **APPLICATIONS**

- · Cellular telephone systems: KB8821

- Portable wireless communications: KB8822 (PCS/PCN, cordless)

- Wireless Local Area Networks (W-LANs)

: KB8823

- Other wireless communication systems

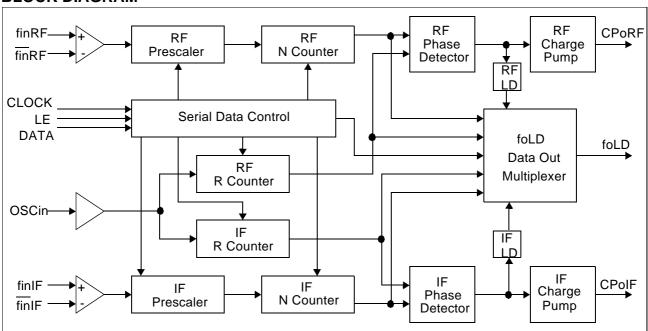

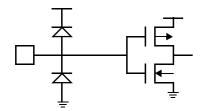

### **BLOCK DIAGRAM**

Figure 1. BLOCK DIAGRAM

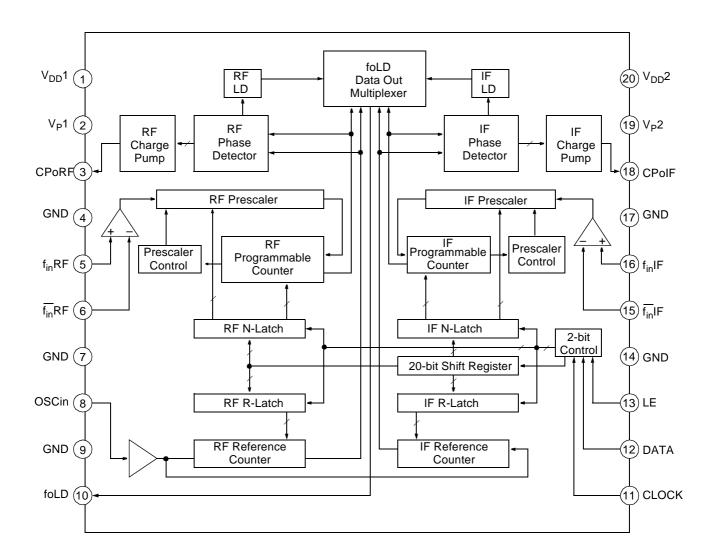

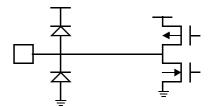

### **BLOCK DIAGRAM-** Continued

Figure 2. Detailed block diagram

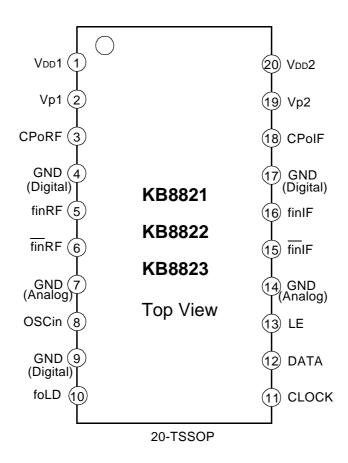

### **PIN CONFIGURATION**

20-Lead(0.173 Wide) Thin Shrink Small Outline Package(20-TSSOP)

- 1. pin #9 = pin #17(internally connected).

- 2. Do not tie up Vp and VDD

- · Vp is the source of digital noises. The power for analog part is supplied by Vbb. If Vp and Vbb are tied together, noisy Vp corrupts the power source for the analog part.

### **PIN DESCRIPTION**

| Pin No | Symbol            | 1/0 | Description                                                                                                                                                                                                                    |

|--------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | V <sub>DD</sub> 1 | -   | Power supply voltage input for the RF PLL part. Vbb1 must equal Vbb2. In order to reject supply noise, bypass capacitors must be placed as close as possible to this pin and be connected directly to the ground plane.        |

| 2      | Vp1               | -   | Power supply voltage input for RF charge pump(≥ VDD1).                                                                                                                                                                         |

| 3      | CPoRF             | 0   | Internal RF charge pump output for connection to an external loop filter whose filtered output drives an external VCO.                                                                                                         |

| 4      | GND               | -   | Ground for RF digital blocks.                                                                                                                                                                                                  |

| 5      | finRF             | I   | RF prescaler input. The signal comes from the external VCO.                                                                                                                                                                    |

| 6      | finRF             | I   | The complementary input of the RF prescaler. A bypass capacitor must be placed as close as possible to this pin and be connected directly to the ground plane. The bypass capacitor is optional with some loss of sensitivity. |

| 7      | GND               | -   | Ground for RF analog blocks.                                                                                                                                                                                                   |

| 8      | OSCin             | I   | Reference counter input. TCXO is connected via a coupling capacitor.                                                                                                                                                           |

| 9      | GND               | -   | Ground for IF digital blocks.                                                                                                                                                                                                  |

| 10     | foLD              | 0   | Multiplexed output of the RF/IF programmable counters, the reference counters, the lock detect signals and the shift registers. The output level is CMOS level. (see fout Programmable Truth Table)                            |

| 11     | CLOCK             | I   | CMOS clock input. Serial data for the various counters is transfered into the 22-bit shift register on the rising edge of the clock signal.                                                                                    |

| 12     | DATA              | I   | Binary serial data input. The MSB of CMOS input data is entered first. The control bits are on the last two bits. CMOS input.                                                                                                  |

| 13     | LE                | I   | Load enable CMOS input. When LE becomes high, the data in the shift register is loaded into one of the four latches(by the control bits).                                                                                      |

| 14     | GND               | -   | Ground for IF analog blocks.                                                                                                                                                                                                   |

| 15     | finIF             | I   | The complementary input of the IF prescaler. A bypass capacitor must be placed as close as possible to this pin and be connected directly to the ground plane. The bypass capacitor is optional with some loss of sensitivity. |

| 16     | finIF             | I   | IF prescaler input. The signal comes from the external VCO.                                                                                                                                                                    |

| 17     | GND               | -   | Ground for IF digital blocks.                                                                                                                                                                                                  |

| 18     | CPoIF             | 0   | Internal IF charge pump output for connection to an external loop filter whose filtered output drives an external VCO.                                                                                                         |

| 19     | Vp2               | -   | Power supply voltage input for IF charge pump(≥ VDD2)                                                                                                                                                                          |

| 20     | V <sub>DD</sub> 2 | -   | Power supply voltage input for the IF PLL part. Vbb1 must equal Vbb2. In order to reject supply noise, bypass capacitors must be placed as close as possible to this pin and be connected directly to the ground plane.        |

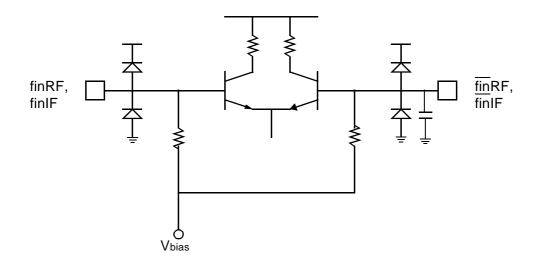

## **EQUIVALENT CIRCUIT DIAGRAM**

♦ CLOCK, DATA, LE

♦ foLD

♦ OSCin

◆ CPoRF, CPoIF

♦ finRF, finRF, finIF, finIF

KB8821/22/23

## **ABSOLUTE MAXIMUM RATINGS**

| Characteristic        | Symbol           | Value          | Unit |

|-----------------------|------------------|----------------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | 5.5            | V    |

| Power Dissipation     | P <sub>D</sub>   | 600            | mW   |

| Operating Temperature | T <sub>a</sub>   | -40°C ~ +85°C  | °C   |

| Storage Temperature   | T <sub>STG</sub> | -65°C ~ +150°C | °C   |

### **ELECTROSTATIC CHARACTERISTICS**

| Characteristic       | Pin No. | ESD level | Unit |

|----------------------|---------|-----------|------|

| Human Body Model     | All     | < ±2000   | V    |

| Machine Model        | All     | < ±300    | V    |

| Charged Device Model | All     | < ±800    | V    |

<sup>\*\*</sup> These devices are ESD sensitive. These devices must be handled in the ESD protected environment.

99-06-15 6

# $\textbf{ELECTRICAL CHARACTERISTICS}(\textit{V}_{DD}=3.0\textit{V},\textit{V}_{p}=3.0\textit{V},\textit{-}40^{\circ}\text{C}\pounds\text{T}_{a}\pounds\text{85}^{\circ}\text{C} \hspace{0.2cm} \textbf{Unless otherwise specified})$

| Chara            | acteristic        | Symbol            | Test Conditions                            | Min.                 | Тур. | Max.               | Unit |

|------------------|-------------------|-------------------|--------------------------------------------|----------------------|------|--------------------|------|

| Dawar Cumply V   | altaga            | V <sub>DD</sub>   |                                            | 2.7                  | 3.0  | 4.0                | V    |

| Power Supply V   | onage             | V <sub>P</sub>    |                                            | V <sub>DD</sub>      | 3.0  | 4.0                | V    |

|                  | KB8823 RF + IF    |                   |                                            |                      | 5.5  |                    |      |

|                  | KB8823 RF Only    |                   |                                            |                      | 4.0  |                    |      |

| Power Supply     | KB8822 RF + IF    |                   |                                            |                      | 4.5  |                    |      |

| Current          | KB8822 RF Only    | $I_{DD}$          | V <sub>DD</sub> =2.7V to 4.0V              |                      | 3.0  |                    | mA   |

|                  | KB8821 RF + IF    |                   |                                            |                      | 3.5  |                    |      |

|                  | KB8821 RF Only    |                   |                                            |                      | 2.0  |                    |      |

|                  | KB882x IF Only    |                   |                                            |                      | 1.5  |                    |      |

| Power down Cu    | rrent             | I <sub>PWDN</sub> | V <sub>DD</sub> =3.0V                      |                      | 1.0  | 10                 | μΑ   |

| Digital inputs : | CLOCK, DATA and   | LE                |                                            |                      |      |                    |      |

| High-Level Inpu  | t Voltage         | $V_{IH}$          | V <sub>DD</sub> =2.7V to 4.0V              | 0.7V <sub>DD</sub>   |      |                    | V    |

| Low-Level Input  | Voltage           | V <sub>IL</sub>   | V <sub>DD</sub> =2.7V to 4.0V              |                      |      | 0.3V <sub>DD</sub> | V    |

| High-Level Inpu  | t Current         | I <sub>IH</sub>   | V <sub>IH</sub> = V <sub>DD</sub> =4.0V    | -1.0                 |      | +1.0               | μΑ   |

| Low-Level Input  | Current           | I <sub>IL</sub>   | V <sub>IL</sub> =0V, V <sub>DD</sub> =4.0V | -1.0                 |      | +1.0               | μА   |

| Reference Divid  | der Input : OSCin |                   |                                            |                      |      |                    |      |

| Input Current    |                   | $I_{IHR}$         | V <sub>IH</sub> = V <sub>DD</sub> =4.0V    |                      |      | +100               | μΑ   |

| input Current    |                   | I <sub>ILR</sub>  | V <sub>IL</sub> =0V, V <sub>DD</sub> =4.0V | -100                 |      |                    | μА   |

| Digital Output : | foLD              |                   |                                            |                      |      |                    |      |

| High Level Outp  | ut Voltage        | V <sub>OH</sub>   | Iout = -500μA                              | V <sub>DD</sub> -0.4 |      |                    | V    |

| Low Level Outpo  | ut Voltage        | V <sub>OL</sub>   | lout = +500μA                              |                      |      | 0.4                | V    |

## $\textbf{ELECTRICAL CHARACTERISTICS} (\textit{V}_{DD} = 3.0 \textit{V}, \textit{V}_{P} = 3.0 \textit{V}, -40 ^{\circ} \textit{C} \pounds \textit{T}_{a} \pounds 85 ^{\circ} \textit{C} \hspace{0.1cm} \textbf{Unless otherwise specified)-} \hspace{0.1cm} \textbf{Continued} \\$

| Chara                               | cteristic                | Symbol                                      | Test Conditions                                            | Min. | Тур.   | Max. | Unit            |

|-------------------------------------|--------------------------|---------------------------------------------|------------------------------------------------------------|------|--------|------|-----------------|

| Charge Pump C                       | Outputs : CPoRF, C       | PolF                                        |                                                            |      |        |      | 1               |

|                                     |                          | I <sub>CP-SRC</sub>                         | V <sub>CP</sub> =V <sub>P</sub> /2, I <sub>CPo</sub> =Low  |      | -1.125 |      |                 |

|                                     |                          | I <sub>CP-SINK</sub>                        | V <sub>CP</sub> =V <sub>P</sub> /2, I <sub>CPo</sub> =Low  |      | +1.125 |      |                 |

| Charge Pump O                       | utput Current            | I <sub>CP-SRC</sub>                         | V <sub>CP</sub> =V <sub>P</sub> /2, I <sub>CPo</sub> =High |      | -4.5   |      | mA              |

|                                     |                          | I <sub>CP-SINK</sub>                        | V <sub>CP</sub> =V <sub>P</sub> /2, I <sub>CPo</sub> =High |      | +4.5   |      |                 |

| Charge Pump Le                      | eakage Current           | I <sub>CPL</sub>                            | $0.5V \le V_{CP} \le V_P - 0.5V$                           | -2.5 |        | +2.5 | nA              |

| Output Current S<br>Mismatch*       | Sink vs. Source          | I <sub>CP-SINK</sub> vs I <sub>CP-SRC</sub> | $V_{CP}=V_{P}/2$ $T_{a}=25^{\circ}C$                       |      | 3      | 10   | %               |

| Output Current M<br>vs. Temperature | lagnitude Variation **   | I <sub>CP</sub> vs T                        | V <sub>CP</sub> =V <sub>P</sub> /2                         |      | 10     |      | %               |

| Output Current Nvs. Voltage***      | lagnitude Variation      | I <sub>CP</sub> vs<br>V <sub>CP</sub>       | $0.5V \le V_{CP} \le V_{P}-0.5V$ $T_a=25^{\circ}C$         |      | 10     | 15   | %               |

| Programmable                        | Divider                  | 1                                           |                                                            |      |        |      | 1               |

| On anoting                          | KB8823                   |                                             | V <sub>DD</sub> =2.7V to 4.0V                              | 0.5  |        | 2.5  |                 |

| Operating<br>Frequency              | KB8822                   | finRF                                       |                                                            | 0.2  |        | 2.0  | GHz             |

|                                     | KB8821                   |                                             |                                                            | 0.1  |        | 1.2  |                 |

| Operating Frequ                     | ency                     | finIF                                       | V <sub>DD</sub> =3.0V                                      | 45   |        | 520  | MHz             |

| DE lasest Occupiti                  |                          | D DE                                        | V <sub>DD</sub> =3.0V                                      | -15  |        | 0    | -10             |

| RF Input Sensitiv                   | Иty                      | P <sub>fin</sub> RF                         | V <sub>DD</sub> =4.0V                                      | -10  |        | 0    | - dBm           |

| IF Input Sensitivi                  | ty                       | P <sub>fin</sub> IF                         | V <sub>DD</sub> =2.7V to 4.0V                              | -10  |        | 0    | dBm             |

| Phase Detector I                    | Phase Detector Frequency |                                             |                                                            |      |        | 10   | MHz             |

| Reference Divid                     | ler                      | 1                                           | 1                                                          |      | 1      |      |                 |

| Operating Frequ                     | ency                     | OSCin                                       |                                                            | 5    |        | 40   | MHz             |

| Input Sensitivity                   |                          | V <sub>OSCin</sub>                          |                                                            | 0.5  |        |      | V <sub>PP</sub> |

## ELECTRICAL CHARACTERISTICS(V<sub>DD</sub>=3.0V, V<sub>P</sub>=3.0V, -40°C£T<sub>a</sub>£85°C Unless otherwise specified)- Continued

| Characteristic                            | Symbol             | Test Conditions | Min. | Тур. | Max. | Unit |

|-------------------------------------------|--------------------|-----------------|------|------|------|------|

| Serial Data Control                       |                    |                 |      |      |      |      |

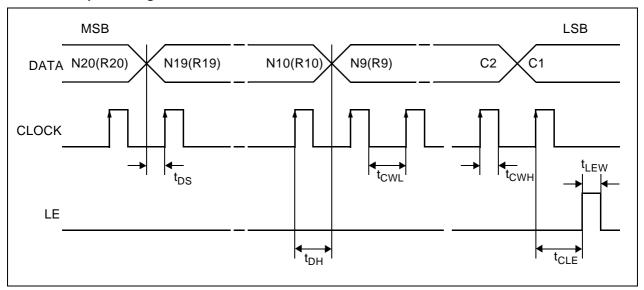

| CLOCK Frequency                           | f <sub>CLOCK</sub> |                 |      |      | 10   | MHz  |

| CLOCK Pulse Width High                    | t <sub>CWH</sub>   |                 | 50   |      |      | ns   |

| CLOCK Pulse Width Low                     | t <sub>CWL</sub>   |                 | 50   |      |      | ns   |

| DATA Set Up Time to CLOCK<br>Risng Edge   | t <sub>DS</sub>    |                 | 50   |      |      | ns   |

| DATA Hold Time after CLOCK<br>Rising Edge | t <sub>DH</sub>    |                 | 10   |      |      | ns   |

| LE Pulse Width                            | t <sub>LEW</sub>   |                 | 50   |      |      | ns   |

| CLOCK Rising Edge to LE Rising Edge       | t <sub>CLE</sub>   |                 | 50   |      |      | ns   |

#### <For Charge Pump items>

$I_a = \text{Charge pump sink current at Vcp=Vp}\Delta V, \qquad I_b = \text{Charge pump sink current at Vcp=Vp}/2, \qquad I_e = \text{Charge pump sink current at Vcp=}\Delta V \\ I_d = \text{Charge pump source current at Vcp=Vp}/2, \qquad I_e = \text{Charge pump source current at Vcp=}\Delta V \\ \Delta V = \text{Voltage offset from positive(for sink current)} \text{ and negative(for source current)} \text{ points from which the charge pump currents become flat.}$

$[|\ l_b\ @ \ any\ temp.|\ -\ |\ l_b\ @\ 25^{\circ}C|\ ]\ /\ |\ l_b\ @\ 25^{\circ}C|\ *\ 100\ (\%) \qquad and \qquad [|\ l_e\ @ \ any\ temp.|\ -\ |\ l_e\ @\ 25^{\circ}C|\ ]\ /\ |\ l_e\ @\ 25^{\circ}C|\ *\ 100\ (\%)$

$\left[0.5 * \{|I_a| - |I_c|\}\right] / \left[0.5 * \{|I_a| + |I_c|\}\right] * 100 (\%) \quad \text{and} \quad \left[0.5 * \{|I_d| - |I_f|\}\right] / \left[0.5 * \{|I_d| + |I_f|\}\right] * 100 (\%)$

<sup>\*</sup> Output Current Sink vs. Source Mismatch =  $[|b|-|l_e|]/[0.5 * {|l_b|+|l_e|}] * 100 (%)$

<sup>\*\*</sup> Output Current Magnitude Variation vs. Temperature =

<sup>\*\*\*</sup> Output Current Magnitude Variation vs. Voltage =

### **FUNCTIONAL DESCRIPTION**

The Samsung KB882x are dual PLL frequency synthesizer ICs. KB882x combined with external LPFs and and VCOs form PLL frequency synthesizers. They include serial data control, R counter, N counter, prescaler, phase detector, charge pump, and etc. (Figure 1).

Serial data is moved into 20-bit shift register on the rising edge of the clock(Figure 2). These data enters MSB first. When LE becomes HIGH, data in the shift register is moved into one of the 4 latches(by the 2-bit control). The divide ratios of the prescaler and the counters are determined by the data stored in the latches. The external VCO output signal is divided by the prescaler and the N counter. External reference signal is divided by the R counter. These two signals are the two input signals to the phase detector. The phase detector drives the charge pump by comparing frequencies and phases of the above two signals. The charge pump and the external LPF make the control voltage for the external VCO and finally the VCO generates the appropriate frequency signal.

#### **Serial Data Input Timing**

#### **Control Bits**

| Contr | ol Bits | 5.7.1         |  |  |  |

|-------|---------|---------------|--|--|--|

| C1    | C2      | DATA Location |  |  |  |

| 0     | 0       | IF R Counter  |  |  |  |

| 0     | 1       | RF R Counter  |  |  |  |

| 1     | 0       | IF N Counter  |  |  |  |

| 1     | 1       | RF N Counter  |  |  |  |

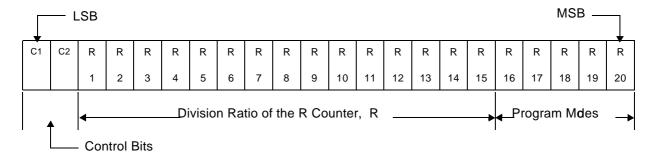

### **Programmable Reference Counter(IF / RF R Counter)**

If the Control Bits are 00(IF) or 01(RF), data is moved from the 20-bit shift register into the R-latch which sets the reference counter. Serial data format is shown in the table below.

### ♦ 15-Bit Programmable Reference Counter Ratio

| Division | R  | R  | R  | R  | R  | R  | R | R | R | R | R | R | R | R | R |

|----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| Ratio    | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 3        | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4        | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| •        | •  | •  | •  | •  | •  | •  | • | • | • | • | • | • | • | • | • |

| 32767    | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Division ratio: 3 to 32767 Data are shifted in MSB first

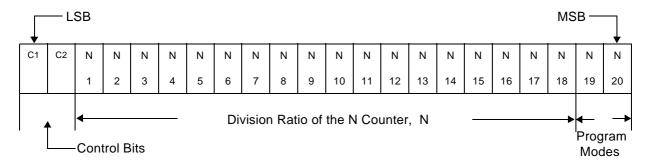

#### **Programmable Counter(N Counter)**

If the Control Bits are 10(IF) or 11(RF), data is transferred from the 20-bit shift register into the N-latch. N Counter consists of 7-bit swallow counter(A counter) and 11-bit main counter(B counter). Serial data format is shown below.

♦ 7-Bit Swallow Counter Division Ratio(A Counter)

RF

| Division | N | N | N | N | N | N | N |

|----------|---|---|---|---|---|---|---|

| Ratio(A) | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1        | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| •        | • | • | • | • | • | • | • |

| 127      | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

IF

| Division | N | N | N | N | N | N | N |

|----------|---|---|---|---|---|---|---|

| Ratio(A) | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0        | Х | Х | Х | 0 | 0 | 0 | 0 |

| 1        | Х | Х | Х | 0 | 0 | 0 | 1 |

| •        | • | • | • | • | • | • | • |

| 15       | Χ | Χ | Х | 1 | 1 | 1 | 1 |

Division ratio: 0 to 127

$B \ge A$

Division ratio : 0 to 15 B≥ A

X = DONT CARE condition

◆ 11-Bit Main Counter Division Ratio(B Counter)

| Division | N  | N  | N  | N  | N  | N  | N  | N  | N  | N | N |

|----------|----|----|----|----|----|----|----|----|----|---|---|

| Ratio    | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 3        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1 | 1 |

| 4        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0 | 0 |

| •        | •  | •  | •  | •  | •  | •  | •  | •  | •  | • | • |

| 2047     | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 |

Division ratio: 3 to 2047

#### **Pulse Swallow Function**

$f_{VCO}=[(PXB)+A]xf_{OSCin}/R$

f<sub>VCO</sub>: External VCO output frequency

P: Preset modulus of dual modulus prescaler

(for KB8821/22 RF:P=64 or 128, for KB8823 RF:P=32 or 64, for IF: P=8 or 16)

B: 11-bit main counter division ratio ( $3 \le B \le 2047$ )

A: 7-bit swallow counter division ratio

(for RF:  $0 \le A \le 127$ , for IF:  $0 \le A \le 15$ ,  $A \le B$ )

foscin: External reference frequency(from external oscillator)

R: 15-bit reference counter division ratio ( $3 \le R \le 32767$ )

### **Program Mode**

| C1 | C2 | R16                           | R17                 | R18                        | R19      | R20      |

|----|----|-------------------------------|---------------------|----------------------------|----------|----------|

| 0  | 0  | IF Phase<br>Detector Polarity | IF I <sub>CPo</sub> | IF CPoIF<br>High Impedance | IF<br>LD | IF<br>Fo |

| 0  | 1  | RF Phase<br>Detector Polarity | RF I <sub>CPo</sub> | RF CPoIF<br>High Impedance | RF<br>LD | RF<br>Fo |

| C1 | C2 | N19          | N20     |

|----|----|--------------|---------|

| 1  | 0  | IF Prescaler | Pwdn IF |

| 1  | 1  | RF Prescaler | Pwdn RF |

#### ◆ Mode Select Truth Table

|   | Phase Detector Polarity | CPoIF High Impedance | I <sub>CPo</sub> | IF Prescaler | RF Prescaler<br>KB8821/22<br>(KB8823) | Pwdn   |

|---|-------------------------|----------------------|------------------|--------------|---------------------------------------|--------|

| 0 | Negative                | Normal Operation     | Low              | 8/9          | 64/65<br>(32/33)                      | Pwr Up |

| 1 | Positive                | High Impedance       | High             | 16/17        | 128/129<br>(64/65)                    | Pwr Dn |

<sup>\*</sup> The charge pump output current of  $\[ \]_{CPo}\]$  LOW = 1/4× $\[ \]_{CPo}\]$  HIGH.

### **FUNCTIONAL DESCRIPTION Continued**

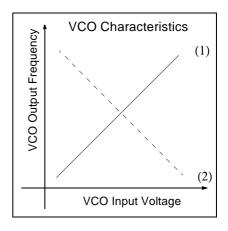

♦ Phase Detector Polarity

Depending on VCO characteristics, R16 bit should be set as follows :

VCO characteristics are positive like (1): R16 HIGH

VCO characteristics are negative like (2): R16 LOW

### ♦ foLD (Pin10) Output Truth Table

| RF R19<br>(RF LD) | IF R19<br>(IF LD) | RF R20<br>(RF fo) | IF R20<br>(IF fo) | foLD Output State              |

|-------------------|-------------------|-------------------|-------------------|--------------------------------|

| 0                 | 0                 | 0                 | 0                 | Disabled (default LOW)         |

| 0                 | 1                 | 0                 | 0                 | IF Lock Detect                 |

| 1                 | 0                 | 0                 | 0                 | RF Lock Detect                 |

| 1                 | 1                 | 0                 | 0                 | RF and IF Lock Detect          |

| 0                 | 0                 | 0                 | 1                 | IF Reference Divider Output    |

| 0                 | 0                 | 1                 | 0                 | RF Reference Divider Output    |

| 0                 | 1                 | 0                 | 1                 | IF Programmable Divider Output |

| 0                 | 1                 | 1                 | 0                 | RF Programmable Divider Output |

| 0                 | 0                 | 1                 | 1                 | High Speed Lock mode           |

| 0                 | 1                 | 1                 | 1                 | IF Counter Reset               |

| 1                 | 0                 | 1                 | 1                 | RF Counter Reset               |

| 1                 | 1                 | 1                 | 1                 | RF and IF Counter Reset        |

- When the PLL is locked and a lock detect mode is selected, the foLD output is HIGH, with narrow pulses LOW.

- Counter Reset mode resets R & N counters.

- The high speed lock mode sets the foLD output pin to be connected to ground with a low impedance ( $\leq 110\Omega$ ).

99-06-15 14

#### ◆ Powerdown mode operation

There are synchronous and asynchronous powerdown modes for KB8821/22/23.

Synchronous powerdown mode occurs if R18 bit is LOW, N20 bit is HIGH and charge pump output is in high impedance state. In the synchronous power down mode, the powerdown function is activated by the charge pump to diminish unwanted frequency jumps. Asynchronous powerdown mode occurs if R18 bit is HIGH and N20 bit is HIGH.

When the PLL goes to either synchronous or asynchronous powerdown mode, preamp becomes debiased, R & N counters keeps their load conditions and the charge pump becomes high impedance state. The oscillator circuitry function becomes disabled only when both IF and RF powerdown bits are activated, i.e. N20 HIGH.

The PLL returns to an active powerup mode when N20 bit becomes LOW(either in synchronous or asynchronous modes).

| R18 | N20 | Powerdown mode status                       |

|-----|-----|---------------------------------------------|

| 0   | 0   | PLL active                                  |

| 1   | 0   | PLL active, only charge pump high impedance |

| 0   | 1   | Synchronous powerdown                       |

| 1   | 1   | Asynchronous powerdown                      |

### **Phase Detector and Charge pump Characteristics**

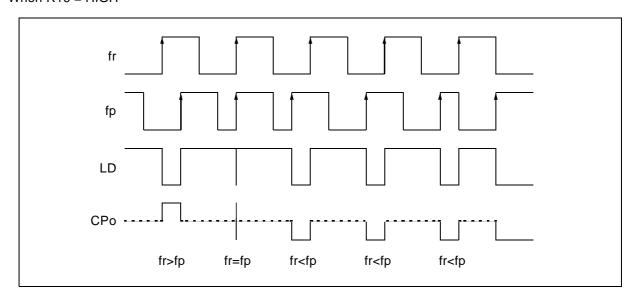

Phase difference detection range : -2 $\pi$  ~ +2 $\pi$  When R16 = HIGH

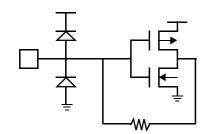

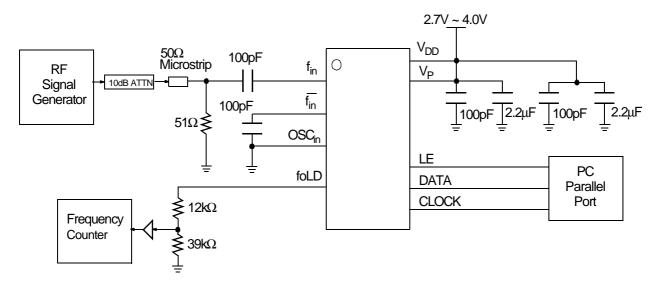

### RF SENSITIVITY MEASUREMENT CIRCUIT

- \*\* N=10,000 R=50 P=64

- \*\* Sensitivity limit is determined when the error of the divided RF output( foLD) becomes  $\geq$ 1 Hz.

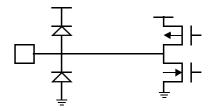

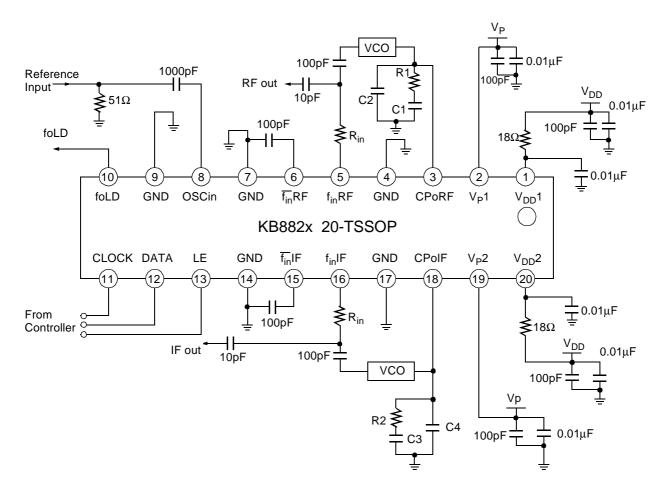

### **TYPICAL APPLICATION CIRCUIT**

\*\* The role of Rin : Rin makes VCO output power go to the load rather than the PLL.

The value of Rin depends on the VCO power level.

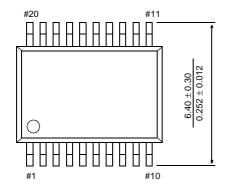

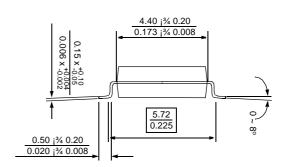

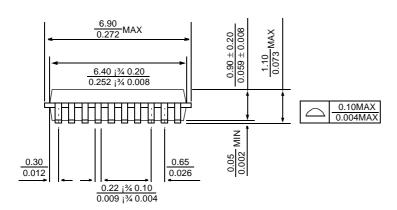

## **PACKAGE DIMENSIONS**

20-Lead TSSOP Package (Samsung 20-TSSOP-225)

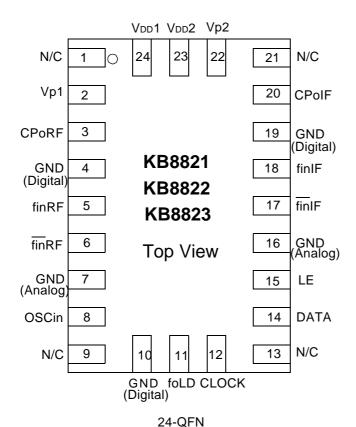

# Addendum(for 24-QFN package)

## PIN CONFIGURATION(24-QFN, not to scale)

\* N/C pins must be connected to GND(to Analog GND if possible).

24 PIN Quad Flat Non-leaded (24-QFN) Package

- 1. pin #10 = pin #19(internally connected).

- 2. Do not tie up Vp and VDD

- : Vp is the source of digital noises. The power for analog part is supplied by Vbb. If Vp and Vbb are tied together, noisy Vp corrupts the power source for the analog part.

# PIN DESCRIPTION(24-QFN)

| Pin No<br>( 20-<br>TSSOP) | Pin No<br>(24QFN) | Symbol            | 1/0 | Description                                                                                                                                                                                                                    |

|---------------------------|-------------------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                         | 24                | V <sub>DD</sub> 1 | -   | Power supply voltage input for the RF PLL part. Vbb1 must equal Vbb2. In order to reject supply noise, bypass capacitors must be placed as close as possible to this pin and be connected directly to the ground plane.        |

| -                         | 1                 | -                 | N/C | No connection.                                                                                                                                                                                                                 |

| 2                         | 2                 | Vp1               | -   | Power supply voltage input for RF charge pump(≥ VDD1).                                                                                                                                                                         |

| 3                         | 3                 | CPoRF             | 0   | Internal RF charge pump output for connection to an external loop filter whose filtered output drives an external VCO.                                                                                                         |

| 4                         | 4                 | GND               | -   | Ground for RF digital blocks.                                                                                                                                                                                                  |

| 5                         | 5                 | finRF             | ı   | RF prescaler input. The signal comes from the external VCO.                                                                                                                                                                    |

| 6                         | 6                 | finRF             | l   | The complementary input of the RF prescaler. A bypass capacitor must be placed as close as possible to this pin and be connected directly to the ground plane. The bypass capacitor is optional with some loss of sensitivity. |

| 7                         | 7                 | GND               | -   | Ground for RF analog blocks.                                                                                                                                                                                                   |

| 8                         | 8                 | OSCin             | I   | Reference counter input. TCXO is connected via a coupling capacitor.                                                                                                                                                           |

| -                         | 9                 | -                 | N/C | No connection.                                                                                                                                                                                                                 |

| 9                         | 10                | GND               | -   | Ground for IF digital blocks.                                                                                                                                                                                                  |

| 10                        | 11                | foLD              | 0   | Multiplexed output of the RF/IF programmable counters, the reference counters, the lock detect signals and the shift registers. The output level is CMOS level. (see fut Programmable Truth Table)                             |

| 11                        | 12                | CLOCK             | I   | CMOS clock input. Serial data for the various counters is transfered into the 22-bit shift register on the rising edge of the clock signal.                                                                                    |

| -                         | 13                | -                 | N/C | No connection.                                                                                                                                                                                                                 |

| 12                        | 14                | DATA              | I   | Binary serial data input. The MSB of CMOS input data is entered first. The control bits are on the last two bits. CMOS input.                                                                                                  |

| 13                        | 15                | LE                | I   | Load enable CMOS input. When LE becomes high, the data in the shift register is loaded into one of the four latches(by the control bits).                                                                                      |

| 14                        | 16                | GND               | -   | Ground for IF analog blocks.                                                                                                                                                                                                   |

| 15                        | 17                | finIF             | I   | The complementary input of the IF prescaler. A bypass capacitor must be placed as close as possible to this pin and be connected directly to the ground plane. The bypass capacitor is optional with some loss of sensitivity. |

| 16                        | 18                | finIF             | I   | IF prescaler input. The signal comes from the external VCO.                                                                                                                                                                    |

| 17                        | 19                | GND               | -   | Ground for IF digital blocks.                                                                                                                                                                                                  |

| 18                        | 20                | CPoIF             | 0   | Internal IF charge pump output for connection to an external loop filter whose filtered output drives an external VCO.                                                                                                         |

| -                         | 21                | -                 | N/C | No connection.                                                                                                                                                                                                                 |

| 19                        | 22                | Vp2               | -   | Power supply voltage input for IF charge pump(≥ VDD2)                                                                                                                                                                          |

KB8821/22/23

| 20 | 23 | V <sub>DD</sub> 2 | - | Power supply voltage input for the IF PLL part. Vbb1 must equal Vbb2. In order to reject supply noise, bypass capacitors must be |

|----|----|-------------------|---|----------------------------------------------------------------------------------------------------------------------------------|

|    |    |                   |   | placed as close as possible to this pin and be connected directly to the ground plane.                                           |

99-06-15 21