1 CHIP CODECS KT8554B/7B

#### **INTRODUCTION**

The KT8554B/7B are single-chip PCM encoders and decoders (PCM CODECs) and PCM line filters. These devices provide all the functions required to interface a full-duplex voice telephone circuit with a time-division-multiplex (TDM) system.

These devices are designed to perform the transmit encoding and receive decoding as well as the transmit and receive filtering functions in PCM system. They are intended to be used at the analog termination of a PCM line or trunk.

These devices provide the bandpass filtering of the analog signals prior to encoding and after decoding. These combination devices perform the encoding and decoding of voice and call progress tones as well as the signalling and supervision information.

#### **FEATURES**

- Complete CODEC and filtering system

- Meets or exceeds AT&T D3/D4 and CCITT specifications

- μ-Law : KT8554B, A-Law : KT8557B

- On-chip auto zero, sample and hold, and precision voltage references

- Low power dissipation : 60mW (operating) 3mW (standby)

- ± 5V operation

TTL or CMOS compatible

- Automatic power down

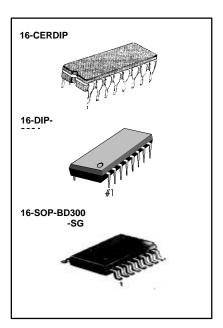

#### ORDERING INFORMATION

| Device   | Package      | Operating Temperature |  |  |  |  |

|----------|--------------|-----------------------|--|--|--|--|

| KT8554BJ | 16-CERDIP    | - 25 ~ 125°C          |  |  |  |  |

| KT8557BJ | 10-CENDIF    | - 25 ~ 125 0          |  |  |  |  |

| KT8557BN | 16-DIP-300A  | - 25 ~ 70°C           |  |  |  |  |

| KT8554BN | 10-DIF-300A  | - 23 ~ 70 0           |  |  |  |  |

| KT8554BD | 16-SOP-BD300 | - 25 ~ 70°C           |  |  |  |  |

| KT8557BD | -SG          | - 25 ~ 70 C           |  |  |  |  |

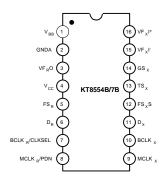

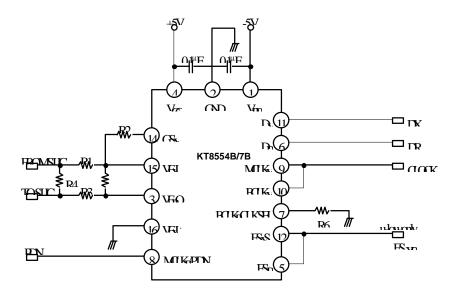

### **PIN CONFIGURATION**

Fig. 1

# PIN DESCRIPTION

| Pin No | Symbol                        | Description                                                                                                                                                                                                                              |

|--------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | V <sub>BB</sub>               | $V_{BB} = -5V \pm 5\%$ .                                                                                                                                                                                                                 |

| 2      | GNDA                          | Analog ground.                                                                                                                                                                                                                           |

| 3      | VF <sub>R</sub> O             | Analog output of the receive power Amp.                                                                                                                                                                                                  |

| 4      | V <sub>cc</sub>               | $V_{CC} = +5V \pm 5\%$ .                                                                                                                                                                                                                 |

| 5      | FS <sub>R</sub>               | Receive frame sync pulse. 8KHz pulse train.                                                                                                                                                                                              |

| 6      | $D_R$                         | PCM data input.                                                                                                                                                                                                                          |

| 7      | BCLK <sub>R</sub> /<br>CLKSEL | Logic input which selects either 1.536MHz/1.544MHz or 2.048MHz for master clock in normal operation and BCLK <sub>x</sub> is used for both TX and RX directions.  Alternately direct clock input available, very from 64KHz to 2.048MHz. |

| 8      | MCLK <sub>R</sub> /<br>PDN    | When MCLK $_R$ is connected continuously high, the device is powered down. Normally connected continusously low, MCLK $_X$ is selected for all DAC timing. Alternately direct 1.536MHz/1.544MHz or 2.048MHz clock input available.       |

| 9      | MCLK <sub>x</sub>             | Must be1.536MHz/1.544MHz or 2.048MHz.                                                                                                                                                                                                    |

| 10     | BCLK <sub>x</sub>             | May be vary from 64KHz to 2.048MHz but $\mathrm{BCLK}_{\mathrm{X}}$ is externally tied with $\mathrm{MCLK}_{\mathrm{X}}$ in normal operation.                                                                                            |

| 11     | D <sub>x</sub>                | PCM data output.                                                                                                                                                                                                                         |

| 12     | FS <sub>x</sub>               | TX frame sync pulse. 8KHz pulse train.                                                                                                                                                                                                   |

| 13     | TS <sub>x</sub>               | Changed from high to low during the encoder timeslot. Open drain output.                                                                                                                                                                 |

| 14     | GS <sub>x</sub>               | Analog output of the TX input amplifier. Used to set gain through external resistor.                                                                                                                                                     |

| 15     | VF <sub>x</sub> I ·           | Inverting input stage of the TX analog signal.                                                                                                                                                                                           |

| 16     | VF <sub>x</sub> I +           | Non-inverting input stage of the TX analog signal.                                                                                                                                                                                       |

# **ABSOLUTE MAXIMUM RATINGS** (Ta = 25°C)

| Characteristic                         | Symbol             | Value                               | Unit |

|----------------------------------------|--------------------|-------------------------------------|------|

| Positive Supply Voltage                | V <sub>cc</sub>    | 7                                   | V    |

| Negative Supply Voltage                | $V_{BB}$           | - 7                                 | V    |

| Voltage at Any Analog Input or Output  | V <sub>I (A)</sub> | $V_{CC}$ + 0.3 to $V_{BB}$ - 0.3    | V    |

| Voltage at Any Digital Input or Output | V <sub>I (D)</sub> | V <sub>cc</sub> + 0.3 to GNDA - 0.3 | V    |

| Operating Temperature Range            | Та                 | - 25 to + 125                       | °C   |

| Storage Temperature Range              | T <sub>STG</sub>   | - 65 to + 150                       | °C   |

| Lead Temperature (Soldering, 10 secs)  | $T_LEAD$           | 300                                 | °C   |

1 CHIP CODECS KT8554B/7B

| Characteristic                                        | Symbol                 | Test Conditions                                                      | Min   | Тур  | Max | Unit |

|-------------------------------------------------------|------------------------|----------------------------------------------------------------------|-------|------|-----|------|

| Power Dissipation                                     | I                      |                                                                      |       |      | I   |      |

| Power-Down Current                                    | I <sub>CC (DOWN)</sub> | No Load                                                              |       | 0.5  | 1.5 | mA   |

| Power-Down Current                                    | I <sub>BB (DOWN)</sub> | No Load                                                              |       | 0.05 | 0.3 | mA   |

| Active Current                                        | I <sub>CC (A)</sub>    | No Load                                                              |       | 6.0  | 9.0 | mA   |

| Active Current                                        | I <sub>BB (A)</sub>    | No Load                                                              |       | 6.0  | 9.0 | mA   |

| Digital Interface                                     |                        |                                                                      |       |      |     |      |

| Input Low Voltage                                     | V <sub>IL</sub>        |                                                                      |       |      | 0.6 | V    |

| Input High Voltage                                    | V <sub>IH</sub>        |                                                                      | 2.2   |      |     | V    |

| Input Low Current                                     | I <sub>IL</sub>        | $GNDA \le V_{IN} \le V_{IL}$ , all digital inputs                    | -10   |      | 10  | μΑ   |

| Input High Current                                    | I <sub>IH</sub>        | $V_{IH} \le V_{IN} \le V_{CC}$                                       | -10   |      | 10  | μΑ   |

|                                                       |                        | $D_X,I_L = 3.2mA$                                                    |       |      | 0.4 | V    |

| Output Low Voltage                                    | V <sub>OL</sub>        | $SIG_R$ , $I_L = 1.0 mA$                                             |       |      | 0.4 | V    |

|                                                       |                        | $\overline{TS}_X$ , $I_L = 3.2 \text{mA,open drain}$                 |       |      | 0.4 | V    |

| Output High Voltage                                   | V <sub>OH</sub>        | $D_{x}$ , $I_{H} = -3.2 \text{mA}$                                   | 2.4   |      |     | V    |

| Output Flight Voltage                                 | VOH                    | $SIG_R$ , $I_H = -1.0 \text{ mA}$                                    | 2.4   |      |     | V    |

| Output Current in High Impedance<br>State (TRI-STATE) | I <sub>O (HZ)</sub>    | $D_x$ , GNDA $\leq V_O \leq V_{CC}$                                  | -10   |      | 10  | μΑ   |

| Analog Interface with Receive Filt                    | er                     |                                                                      | I     |      |     | .1   |

| Output Resistance                                     | Ro                     | Pin VF <sub>R</sub> O                                                |       | 1    | 3   | Ω    |

| Load Resistance                                       | $R_L$                  | $VF_RO = \pm 2.5V$                                                   | 600   |      |     | Ω    |

| Load Capacitance                                      | C <sub>L</sub>         |                                                                      |       |      | 500 | pF   |

| Output DC Offset Voltage                              | V <sub>OO (RX)</sub>   |                                                                      | -200  |      | 200 | mV   |

| Analog Interface with Transmit in                     | out Amplifie           | er                                                                   |       |      |     |      |

| Input Leakage Current                                 | I <sub>LKG</sub>       | $-2.5V \le V \le +2.5V$ , VF <sub>x</sub> I + or VF <sub>x</sub> I - | -200  |      | 200 | nA   |

| Input Resistance                                      | R <sub>i</sub>         | -2.5V≤V≤+2.5V, VF <sub>x</sub> I + or VF <sub>x</sub> I -            | 10    |      |     | МΩ   |

| Output Resistance                                     | Ro                     | Closed loop, unity gain                                              |       | 1    | 3   | Ω    |

| Load Resistance                                       | Rı                     | GS <sub>x</sub>                                                      | 10    |      |     | ΚΩ   |

| Load Capacitance                                      | Cı                     | GS <sub>x</sub>                                                      |       |      | 50  | pF   |

| Output Dynamic Range                                  | V <sub>OD (TX)</sub>   | GS <sub>x</sub> , R₁≤10KW                                            | ±2.8  |      |     | V    |

| Voltage Gain                                          | G <sub>V</sub>         | VF <sub>x</sub> I + to GS <sub>x</sub>                               | 5,000 |      |     | V/V  |

| Unity Gain Bandwidth                                  | BW                     |                                                                      | 1     | 2    |     | MHz  |

| Offset Voltage                                        | V <sub>IO (TX)</sub>   |                                                                      | -20   |      | 20  | mV   |

| Common-Mode Voltage                                   | V <sub>CM (TX)</sub>   | CMRRXA > 60dB                                                        | -2.5  |      | 2.5 | V    |

| Common-Mode Rejection Ratio                           | CMRR                   | DC Test                                                              | 60    |      |     | dB   |

| Power Supply Rejection Ratio                          | PSRR                   | DC Test                                                              | 60    |      |     | dB   |

## TIMING CHARACTERISTICS

(Unless otherwise noted,  $V_{CC}$  = 5.0 ±5%,  $V_{BB}$  = -5.0V ±5%, GNDA = 0V, Ta = 0°C to 70 °C; typical characteristics specified at  $V_{CC}$  = 5.0V,  $V_{BB}$  = -5.0V, Ta = 25 °C; all signals referenced to GNDA.)

| Characteristic                                                                                                                            | Symbol                  | Test Conditions                                                                                           | Min | Тур                     | Max        | Unit              |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------|-----|-------------------------|------------|-------------------|

| Frequency of Master Clocks                                                                                                                | f <sub>MCK</sub>        | Depends on the device used and the BCLK <sub>R</sub> /CLKSEL Pin. MCLK <sub>X</sub> and MCLK <sub>R</sub> |     | 1.536<br>1.544<br>2.048 |            | MHz<br>MHz<br>MHz |

| Rise Time of Bit Clock                                                                                                                    | t <sub>R (BCK)</sub>    | t <sub>PB</sub> = 488ns                                                                                   |     |                         | 50         | ns                |

| Fall Time of Bit Clock                                                                                                                    | t <sub>F (BCK)</sub>    | t <sub>PB</sub> = 488ns                                                                                   |     |                         | 50         | ns                |

| Holding Time from Bit Clock<br>Low to Frame Sync                                                                                          | t <sub>H (LFS)</sub>    | Long frame only                                                                                           | 0   |                         |            | ns                |

| Holding Time from Bit Clock High to Frame Sync                                                                                            | t <sub>H (HFS)</sub>    | Short frame only                                                                                          | 0   |                         |            | ns                |

| Set-Up Time from Frame Sync to Bit Clock Low                                                                                              | t <sub>SU (FBCL)</sub>  | Long frame only                                                                                           | 80  |                         |            | ns                |

| Delay Time from $\mathrm{BCLK}_{X}$ High to Data Valid                                                                                    | t <sub>D (HDV)</sub>    | Load = 150pF plus 2 LSTTL loads                                                                           | 0   |                         | 180        | ns                |

| Delay Time to $\overline{TS_{X}}$ Low                                                                                                     | t <sub>D (TSXL)</sub>   | Load = 150pF plus 2 LSTTL loads                                                                           |     |                         | 140        | ns                |

| Delay Time from BCLK <sub>x</sub> Low to Data Output Disabled                                                                             | t <sub>D (LDD)</sub>    |                                                                                                           | 50  |                         | 165        | ns                |

| Delay Time to Valid Data from FS <sub>x</sub> or BCLK <sub>x</sub> , Whichever Comes Later                                                | t <sub>D (VD)</sub>     | C <sub>L</sub> = 0pF to 150pF                                                                             | 20  |                         | 165        | ns                |

| Set-Up Time from $D_R$ Valid to $BCLK_{R/X}$ Low                                                                                          | t <sub>SU (DR BL)</sub> |                                                                                                           | 50  |                         |            | ns                |

| Hold Time from $BCLK_{R/X}$ Low to $D_R$ Invalid                                                                                          | t <sub>H (BL DR)</sub>  |                                                                                                           | 50  |                         |            | ns                |

| Set-Up Time from $FS_{XR}$ to $BCLK_{XR}$ Low                                                                                             | t <sub>SU (FBLS)</sub>  | Short frame sync pulse (1 or 2 bit clock periods long) (Note1)                                            | 50  |                         |            | ns                |

| Width of Master Clock High                                                                                                                | t <sub>w (MCKH)</sub>   | MCLK <sub>x</sub> and MCLK <sub>R</sub>                                                                   | 160 |                         |            | ns                |

| Width of Master Clock Low                                                                                                                 | t <sub>w (MCKL)</sub>   | MCLK <sub>x</sub> and MCLK <sub>R</sub>                                                                   | 160 |                         |            | ns                |

| Rise Time of Master Clock                                                                                                                 | t <sub>R (MCK)</sub>    | MCLK <sub>x</sub> and MCLK <sub>R</sub>                                                                   |     |                         | 50         | ns                |

| Fall Time of Master Clock                                                                                                                 | t <sub>F(MCK)</sub>     | MCLK <sub>x</sub> and MCLK <sub>R</sub>                                                                   |     |                         | 50         | ns                |

| Set-Up Time from $\operatorname{BCLK}_X$ High (and $\operatorname{FS}_X$ In Long Frame Sync Mode) to $\operatorname{MCLK}_X$ Falling Edge | t <sub>SU (BHMF)</sub>  | First bit clock after the leading edge of FS <sub>x</sub>                                                 |     |                         |            |                   |

| Period of Bit Clock                                                                                                                       | t <sub>CK</sub>         |                                                                                                           | 485 | 488                     | 15,72<br>5 | ns                |

| Width of Bit Clock High                                                                                                                   | t <sub>w (BCKH)</sub>   | V <sub>IH</sub> = 2.2V                                                                                    | 160 |                         |            | ns                |

| Width of Bit Clock Low                                                                                                                    | t <sub>w (BCKL)</sub>   | V <sub>IL</sub> = 0.6V                                                                                    | 160 |                         |            | ns                |

## TIMING CHARACTERISTICS (Continued)

| Characteristic                                                                                       | Symbol                | Test Conditions                                                 | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| Hold Time from BCLK <sub>X/R</sub> Low to FS <sub>X/R</sub> Low                                      | t <sub>H (BLFL)</sub> | Short frame sync pulse (1 or 2 bit clock periods long) (Note 1) | 100 |     |     | ns   |

| Hold Time from 3rd Period of<br>Bit Clock Low to Frame Sync<br>(FS <sub>x</sub> or FS <sub>R</sub> ) | t <sub>H (3rd )</sub> | Long frame sync pulse (from 3 to 8 bit clock periods long)      | 100 |     |     | ns   |

| Minimum Width of the Frame<br>Sync Pulse (Low Level)                                                 | t <sub>WFL</sub>      | 64K bit/s operating mode                                        | 160 |     |     | ns   |

Note 1 : For short frame sync timing,  $FS_x$  and  $FS_R$  must go high while their respective bit clocks are high.

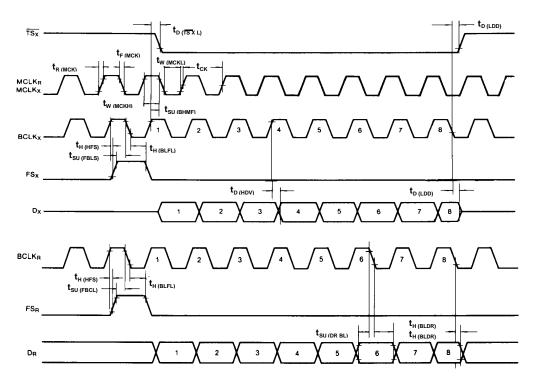

#### **TIMING DIAGRAM**

Fig. 2. Short Frame Sync Timing

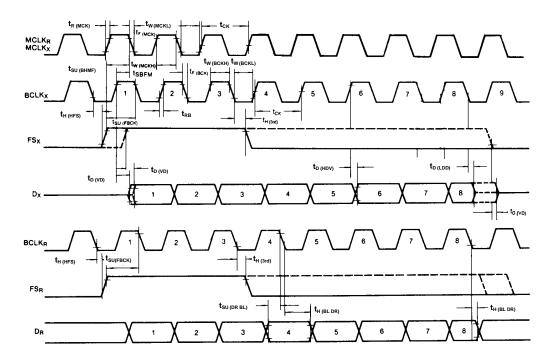

# TIMING DIAGRAM (Continued)

Fig. 3 Long Frame Sync Timing

# TRANSMISSION CHARACTERISTICS

(Unless otherwise specified : Ta = 0°C to 70 °C,  $V_{CC}$  = 5V ±5%,  $V_{BB}$  = -5V ±5%, GNDA = 0V, f = 1.02KHz,  $V_{IN}$  = 0dBm0, transmit input amplifier connected for unity-gain non-inverting.)

| Characteristic                                       | Symbol                          | Test Conditions                                                                                                                                                                                | Min                            | Тур    | Max                                                          | Unit                                   |

|------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------|--------------------------------------------------------------|----------------------------------------|

| Amplitude Respons                                    |                                 |                                                                                                                                                                                                |                                |        |                                                              |                                        |

| Receive Gain, Absolute                               | G <sub>V (ARX)</sub>            | Ta = 25 °C, $V_{CC}$ = 5V, $V_{BB}$ = -5V<br>Input = Digital code sequence for<br>0dBm0 signal at 1020Hz                                                                                       | -0.15                          |        | 0.15                                                         | dB                                     |

| Receive Gain, Relative to $G_{V\text{(ARX)}}$        | G <sub>V (RRX)</sub>            | f = 0Hz to 3000Hz<br>f = 3300Hz<br>f = 3400Hz<br>f = 4000Hz                                                                                                                                    | -0.15<br>-0.35<br>-0.7         |        | 0.15<br>0.05<br>0<br>-14                                     | dB<br>dB<br>dB<br>dB                   |

| Absolute Receive Gain Variation with Temperature     | $\Delta G_{V (ARX)} / \Delta T$ | Ta = 0 °C to 70 °C                                                                                                                                                                             |                                |        | ±0.1                                                         | dB                                     |

| Absolute Receive Gain Variation with Supply Voltage  | $\Delta G_{V (ARX)} / \Delta V$ | $V_{CC} = 5V \pm 5\%, V_{BB} = -5V \pm 5\%$                                                                                                                                                    |                                |        | ±0.05                                                        | dB                                     |

| Receive Gain Variations with Level                   | $\Delta G_{V  (RXL)}$           | Sinusoidal test method; reference input PCM code corresponds to an Ideally encoded -10dBm0 signal PCM level = -40dBm0 to -40dBm0 PCM level = -50dBm0 to -40dBm0 PCM level = -55dBm0 to -50dBm0 | -0.2<br>-0.4<br>-1.2           |        | 0.2<br>0.4<br>1.2                                            | dB<br>dB<br>dB                         |

| Receive Output Drive Level                           | V <sub>o (RX)</sub>             | $R_L = 600\Omega$                                                                                                                                                                              | -2.5                           |        | 2.5                                                          | V                                      |

| Absolute Levels                                      | $V_{AL}$                        | Nominal 0dBm0 level is 4dBm (600 $\Omega$ ) 0dBm0                                                                                                                                              |                                | 1.2276 |                                                              | $V_{\rm rms}$                          |

| Max Overload Level                                   | V <sub>OL (MAX)</sub>           | Max overload level (3.17dBm0):<br>KT8554B<br>Max overload level (3.14dBm0):<br>KT8557B                                                                                                         |                                | 2.501  |                                                              | $V_{PK}$                               |

| Transmit Gain, Absolute                              | G <sub>v (ATX)</sub>            | Ta = 25 °C, $V_{CC}$ = 5V, $V_{BB}$ = -5V<br>Input at $GS_X$ = 0dBm0 at 1020Hz                                                                                                                 | -0.15                          |        | 0.15                                                         | dB                                     |

| Transmit Gain, Relative to $G_{\text{V (ATX)}}$      | G <sub>v (RTX)</sub>            | f = 16Hz<br>f = 50Hz<br>f = 60Hz<br>f = 200Hz<br>f = 300Hz - 3000Hz<br>f = 3300Hz<br>f = 3400Hz<br>f = 4000Hz<br>f = 4600Hz and up, measure<br>response from 0Hz to 4000Hz                     | -1.8<br>-0.15<br>-0.35<br>-0.7 |        | -40<br>-30<br>-26<br>-0.1<br>0.15<br>0.05<br>0<br>-14<br>-32 | 99 99 99 99 99 99 99 99 99 99 99 99 99 |

| Absolute Transmit Gain Variation with Temperature    | $\Delta G_{V(ATX)} / \Delta T$  | Ta = 0 °C to 70 °C                                                                                                                                                                             |                                |        | ±0.1                                                         | dB                                     |

| Absolute Transmit Gain Variation with Supply Voltage | $\Delta G_{V (ATX)} / \Delta V$ | $V_{CC} = 5V \pm 5\%, V_{BB} = -5V \pm 5\%$                                                                                                                                                    |                                |        | ±0.05                                                        | dB                                     |

| Transmit Gain Variations with Level                  | $\Delta G_{V  (TXL)}$           | Sinusoldal test method Reference level = - 10dBm0 VF <sub>x</sub> I + = - 40dBm0 to + 3dBm0 VF <sub>x</sub> I + = - 50dBm0 to - 40dBm0 VF <sub>x</sub> I + = - 55dBm0 to - 50dBm0              | - 0.2<br>- 0.4<br>- 1.2        |        | 0.2<br>0.4<br>1.2                                            | dB<br>dB<br>dB                         |

# TRANSMISSION CHARACTERISTICS (Continued)

| Characteristic                                  | Symbol               | Test Conditions                                                                                                                                                                    | Min            | Тур | Max | Unit            |

|-------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-----|-----------------|

| Envelope Delay Distortion with F                | requency             |                                                                                                                                                                                    |                | •   |     | •               |

| Receive Delay, Absolute                         | t <sub>D (ARX)</sub> | f = 1600Hz                                                                                                                                                                         |                | 180 | 200 | μs              |

|                                                 |                      | f = 500Hz - 1000Hz                                                                                                                                                                 | -40            | -25 |     | μs              |

| Bassiya Dalay, Balatiya ta t                    |                      | f = 1000Hz - 1600Hz                                                                                                                                                                | -30            | -20 |     | μs              |

| Receive Delay, Relative to t <sub>D (ARX)</sub> | t <sub>D (RRX)</sub> | f = 1600Hz - 2600Hz                                                                                                                                                                |                | 70  | 90  | μs              |

|                                                 |                      | f = 2600Hz - 2800Hz                                                                                                                                                                |                | 100 | 125 | μs              |

|                                                 |                      | f = 2800Hz - 3000Hz                                                                                                                                                                |                | 145 | 175 | μs              |

| Transmit Delay, Absolute                        | t <sub>D (ATX)</sub> | f = 1600Hz                                                                                                                                                                         |                | 290 | 315 | μs              |

|                                                 | , ,                  | f = 500Hz - 600Hz                                                                                                                                                                  |                | 195 | 220 | μs              |

|                                                 |                      | f = 600Hz - 800Hz                                                                                                                                                                  |                | 120 | 145 | μs              |

|                                                 |                      | f = 800Hz - 1000Hz                                                                                                                                                                 |                | 50  | 75  | μs              |

| Transmit Delay, Relative to $t_{D (ATX)}$       | t <sub>D (RTX)</sub> | f = 1000Hz - 1600Hz                                                                                                                                                                |                | 20  | 40  | μs              |

|                                                 |                      | f = 1600Hz - 2600Hz                                                                                                                                                                |                | 55  | 75  | μs              |

|                                                 |                      | f = 2600Hz - 2800Hz                                                                                                                                                                |                | 80  | 105 | μs              |

|                                                 |                      | f = 2800Hz - 3000Hz                                                                                                                                                                |                | 130 | 155 | μs              |

| Noise                                           |                      |                                                                                                                                                                                    | l              |     |     | 1               |

| Receive Noise, C Message<br>Weighted            | N <sub>RXC</sub>     | PCM code equals alternating positive and negative zero, KT8554B                                                                                                                    |                | 8   | 11  | dBrnc0          |

| Receive Noise, P Message<br>Weighted            | $N_{RXP}$            | PCM code equals, positive zero,<br>KT8557B                                                                                                                                         |                | -82 | -79 | dBm0p           |

| Transmit Noise, C Message<br>Weighted           | N <sub>TXC</sub>     | KT8554B                                                                                                                                                                            |                | 12  | 15  | dBrnc0          |

| Transmit Noise, P Message<br>Weighted           | $N_{TXP}$            | KT8557B                                                                                                                                                                            |                | 74  | -67 | dBm0p           |

| Noise, Single Frequency                         | $N_{\text{SF}}$      | f = 0KHz to 100KHz, loop around<br>measurement, VF <sub>x</sub> I+ = 0V <sub>rms</sub>                                                                                             |                |     | -53 | dBm0            |

| Positive Power Supply Rejection,                | PSRR                 | $VF_XI += 0V_{rms}$                                                                                                                                                                |                |     |     |                 |

| Transmit                                        | (PTX)                | $V_{CC} = 5.0V_{DC} + 100 \text{mV}_{ms}$<br>f = 0KHz - 50KHz                                                                                                                      | 40             |     |     | dBC             |

| Negative Power Supply Rejection,                | PSRR                 | $VF_XI += 0V_{rms}$                                                                                                                                                                |                |     |     | 10.0            |

| Transmit                                        | (NTX)                | $V_{BB} = -5.0V_{DC} + 100 \text{mV}_{ms}$<br>f = 0KHz - 50KHz                                                                                                                     | 40             |     |     | dBC             |

| Positive Power Supply Rejection,<br>Receive     | PSRR<br>(PRX)        | PCM code equals positive zero $V_{CC} = 5.0V_{DC} + 100 \text{mV}_{ms}$ $f = 0 \text{Hz} - 4000 \text{Hz}$ $f = 4 \text{KHz} - 25 \text{KHz}$ $f = 25 \text{KHz} - 50 \text{KHz}$  | 40<br>40<br>36 |     |     | dBC<br>dB<br>dB |

| Negative Power Supply Rejection,<br>Receive     | PSRR<br>(NRX)        | PCM code equals positive zero $V_{BB} = 5.0V_{DC} + 100 \text{mV}_{rms}$ $f = 0 \text{Hz} - 4000 \text{Hz}$ $f = 4 \text{KHz} - 25 \text{KHz}$ $f = 25 \text{KHz} - 50 \text{KHz}$ | 40<br>40<br>36 |     |     | dBC<br>dB<br>dB |

# TRANSMISSION CHARACTERISTICS (Continued)

| Characteristic                          | Symbol                 | Test Conditions                            | Min | typ | Max     | Unit           |

|-----------------------------------------|------------------------|--------------------------------------------|-----|-----|---------|----------------|

|                                         |                        | Loop around measurement, 0dBm0,            |     |     |         |                |

|                                         |                        | 300Hz - 3400Hz input PCM applied to        |     |     |         |                |

| Spurious Out-of-Band Signals            |                        | D <sub>R</sub> , Measure individual image  |     |     |         |                |

| at the Channel Output                   | SOS                    | signals at VF <sub>R</sub> O               |     |     |         |                |

|                                         |                        | 4600Hz - 760Hz                             |     |     | -32     | dB             |

|                                         |                        | 7600Hz - 8400Hz                            |     |     | -40     | dB             |

|                                         |                        | 8400Hz - 100,000Hz                         |     |     | -32     | dB             |

| Distortion                              |                        |                                            |     |     |         |                |

|                                         |                        | Sinusoidal test method                     |     |     |         |                |

|                                         |                        | Level = 3.0dBm0                            | 33  |     |         | dBC            |

| Signal to Total Distortion              | $THD_TX$               | = 0dBm0 to 30dBm0                          | 26  |     |         | dBC            |

| Transmit or Receive                     | $THD_RX$               | = -40dBm0 XMT                              | 29  |     |         | dBC            |

| Half-Channel                            |                        | RCV                                        | 30  |     |         | dBC            |

|                                         |                        | = -55dBm0 XMT                              | 14  |     |         | dBC            |

|                                         |                        | RCV                                        | 15  |     |         | dBC            |

| Single Frequency Distortion,            | THD <sub>SF (TX)</sub> |                                            |     |     | -46     | dB             |

| Transmit                                | 01 (171)               |                                            |     |     |         |                |

| Single Frequency Distortion,<br>Receive | THD <sub>SF (RX)</sub> |                                            |     |     | -46     | dB             |

|                                         |                        | Loop around measurement,                   |     |     |         |                |

| Intermodulation Distortion              | THD <sub>IMD</sub>     | $VF_XI + = -4dBm0$ to $-21dBm0$ , two      |     |     | -41     | dB             |

|                                         | IIVID                  | frequencies in the range                   |     |     |         | u <sub>D</sub> |

|                                         |                        | 300Hz - 3400Hz                             |     |     |         |                |

| Crosstalk                               | I                      |                                            |     |     |         |                |

| Transmit to Receive Crosstalk,          | CT                     | f = 300Hz - 3400Hz                         |     | -90 | -75     | dB             |

| 0dBm0 Transmit Level                    | CT <sub>(TX-RX)</sub>  | D <sub>R</sub> = Steady PCM code           |     | -30 | -13     | ub             |

| Receive to Transmit Crosstalk,          | CT <sub>(RX-TX)</sub>  | f = 300Hz - 3400Hz, VF <sub>x</sub> I = 0V |     | -90 | -70     | dB             |

| 0dBm0 Receive Level                     | (RX-TX)                | 1 - 3001 12 - 34001 12, VI XI = 0V         |     |     | (Note1) |                |

Note 1.  $CT_{(RX-TX)}$  is measured with a - 40dBm0 activating signal applied at VF<sub>X</sub>I +

## **ENCODING FORMAT AT Dx OUTPUT**

|                                             | m <b>Law KT8554B</b> | A-Law KT8557B |

|---------------------------------------------|----------------------|---------------|

| $V_{IN}$ (at $GS_X$ ) = + Full Scale        | 1000000              | 10101010      |

| $V_{IN}$ (at $GS_x$ ) = 0V                  | 1111111              | 11010101      |

| V <sub>IN</sub> (at CO <sub>X</sub> ) = 0 V | 0111111              | 01010101      |

| $V_{IN}$ (at $GS_X$ ) = - Full Scale        | 0000000              | 00101010      |

## **APPLICATION CIRCUIT**

Fig. 4

NOTE 1 : Supposing Desired Line Termination Impedance  $R_L$  = 600ohm It is 0dBm = 0.77459Vrms NOTE 2 :  $T_X$  Gain 20 log (R2/R1), R1 + R2 < 100Kohm, or The Correspondence of 1-CHIP CODEC 0dBm 0 = 4dBm.

## **SELECTION OF MASTER CLOCK FREQUENCY**

| BCLKR/CLKSEL | KT 8554           | KT 8557           |

|--------------|-------------------|-------------------|

| Clocked      | 1.536 / 1.544 MHz | 2.048MHz          |

| 0            | 2.048 MHz         | 1.536 / 1.544 MHz |

| 1 (or open)  | 1.536 / 1.544 MHz | 2.048MHz          |