# 10-bit 80MSPS 1ch D/A Converter (Ultra-low Glitch Version)

## **Description**

The CXD2315Q is a 1-ch 10-bit 80MSPS D/A converter for monitor and video. This IC achieves high specifications for the industrial and information equipment due to the reduction of the glitch energy.

#### **Features**

- 10-bit resolution

- Maximum conversion rate 80MSPS

- Differential linearity error ±0.5LSB

- Low power consumption 150 mW (Max., When 80MSPS 200  $\Omega$  load, 2 Vp-p is output)

- Pin-compatible with CXD2306Q

- Single 5 V power supply

- Built-in independent constant-voltage source

- Ultra-low glitch

- Stand-by function

#### Structure

Silicon gate CMOS IC

# Absolute Maximum Ratings (Ta=25 °C)

- Supply voltage AVDD, DVDD 7 V

- Input voltage (All pins)

- VIN VDD +0.5 to Vss -0.5 V

- · Output voltage (for each channel)

| Іоит | 0 to 15 | mΑ |

|------|---------|----|

|      |         |    |

• Storage temperature

Tstg -55 to +150 °C

## **Recommended Operating Conditions**

- Supply voltage AV<sub>DD</sub>, AVss  $5.0 \pm 0.25$  V DV<sub>DD</sub>, DVss  $5.0 \pm 0.25$  V

- Reference input voltage

VREF 0.5 to 2.0

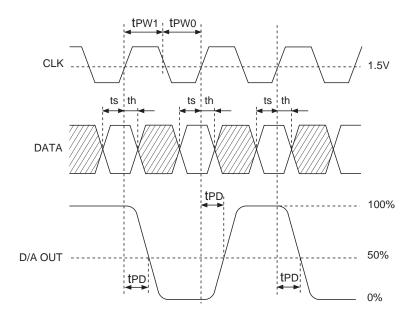

- Clock pulse width tpw1, tpw0 5.6 (min.) ns

- · Operating temperature

Topr -20 to +85 °C

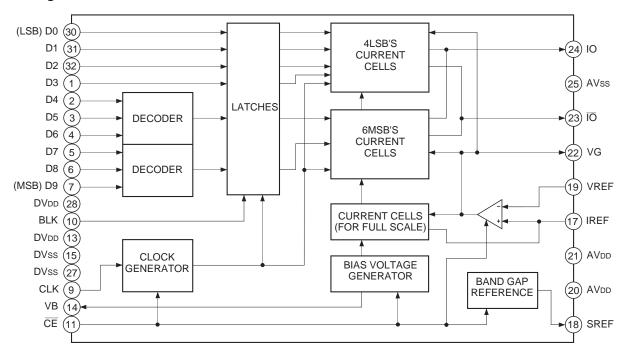

# **Block Diagram**

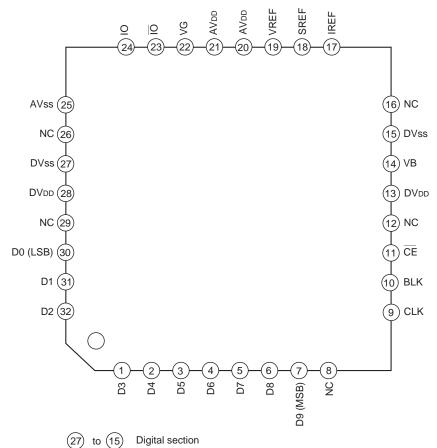

# **Pin Configuration**

17) to 25) Analog section

# Pin Description and Equivalent Circuit

| Pin No.            | Symbol           | I/O | Equivalent circuit | Description                                                                                                                              |

|--------------------|------------------|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 30 to 32<br>1 to 7 | D0 to D9         | I   | DVbb<br>to DVss    | Digital input. 30 pin D0 (LSB) to 7 pin D9 (MSB)                                                                                         |

| 8, 12, 16, 26, 29  | NC               | _   |                    | No connection.                                                                                                                           |

| 9                  | CLK              |     |                    | Clock input.                                                                                                                             |

| 10                 | BLK              | I   | 9                  | Blanking input. This is synchronized with the clock input signal. No signal (0 V output) at high and output state at low.                |

| 11                 | CE               |     | (11) DVss          | Chip enable input. This is not synchronized with the clock input signal. No signal (0 V output) at high makes power consumption minimum. |

| 13, 28             | DV <sub>DD</sub> |     |                    | Digital power supply.                                                                                                                    |

| 14                 | VB               | 0   | DVDD DVSS          | Connect a capacitor of approximately 0.1 µF.                                                                                             |

| 15, 27             | DVss             | _   |                    | Digital ground.                                                                                                                          |

| 17                 | IREF             | 0   | AVDD AVDD          | Reference current output. Connect resistance "RIR" which is 16 times output resistance "Rout".                                           |

| 19                 | VREF             | I   | AVDD AVSS AVDD     | Reference voltage input. Sets output full scale value.                                                                                   |

| 22                 | VG               | 0   | AVss d             | Connect a capacitor of approximately 0.1 µF.                                                                                             |

| Pin No. | Symbol | I/O | Equivalent circuit | Description                                                                                                                                                                                                        |

|---------|--------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | SREF   | 0   | AVDD AVSS AVSS     | Independent constant-voltage source output pin using band gap reference. Stable voltage independent of the fluctuation for supply voltage can be get by connecting to VREF. See Application Circuit 2 for details. |

| 20, 21  | AVDD   | _   |                    | Analog VDD                                                                                                                                                                                                         |

| 23      | ĪŌ     | 0   | 24<br>AVSS 0       | Inverted current output. Connect to GND normally.                                                                                                                                                                  |

| 24      | Ю      |     | AVss o             | Current output. Output can be retrieved by connecting resistance. The standard is 200 $\Omega$ .                                                                                                                   |

| 25      | AVss   | _   |                    | Analog ground.                                                                                                                                                                                                     |

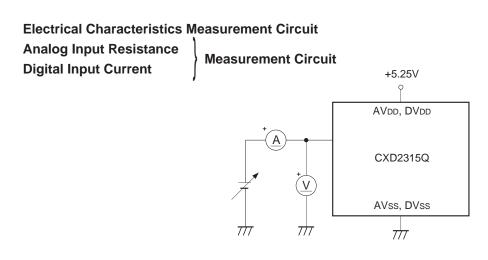

# **Electrical Characteristics**

(Fclk=80 MHz, AVdd=DVdd=5 V, Rout=200  $\Omega,$  Rir=3.3 k $\Omega,$  Vref=2.0 V, Ta=25 °C)

| Item                                      | Symbol | Measurement conditions                       | Min. | Тур. | Max. | Unit |

|-------------------------------------------|--------|----------------------------------------------|------|------|------|------|

| Resolution                                | n      |                                              |      | 10   |      | bit  |

| Conversion speed                          | Fclk   | AVDD=DVDD=4.75 to 5.25 V<br>Ta=-20 to +85 °C | 0    |      | 80   | MSPS |

| Integral non-linearity error              | EL     | - Endpoint                                   | -1.5 |      | 1.5  | LSB  |

| Differential non-linearity error          | Ed     | Enapoint                                     | -0.5 |      | 0.5  | LSB  |

| Precision guaranteed output voltage range | Voc    |                                              | 1.8  | 1.94 | 2.0  | V    |

| Output full-scale voltage                 | VFS    |                                              | 1.8  | 1.94 | 2.0  | V    |

| Output full-scale current                 | IFS    |                                              | 9.0  | 9.7  | 10   | mA   |

| Output offset voltage                     | Vos    | When D0 to D9= "000000000" input             |      |      | 1    | mV   |

| Glitch energy                             | GE     |                                              |      |      | 30   | pV•s |

| Differential gain                         | DG     |                                              |      |      | 1.0  | %    |

| Differential phase                        | DP     |                                              |      |      | 1.0  | deg  |

| Supply current                            | IDD    | CE= "L"                                      |      |      | 30   | - mA |

| Supply current                            | Іѕтв   | CE= "H"                                      |      |      | 1    |      |

| Analog input resistance                   | Rin    | VREF                                         | 1    |      |      | MΩ   |

| Input capacitance                         | Сі     |                                              |      |      | 9    | pF   |

| Digital input voltage                     | ViH    | AVDD=DVDD=4.75 to 5.25 V                     | 2.45 |      |      | V    |

| Digital input voltage                     | VIL    | Ta=-20 to +75 °C                             |      |      | 0.85 | V    |

| Digital input current                     | Іін    | AVDD=DVDD=4.75 to 5.25 V                     | -5   | 5    | μA   |      |

| Digital input current                     | lı∟    | Ta=-20 to +75 °C                             |      |      | 3    | μΛ   |

| SREF output voltage                       | Vsr    |                                              | 1.0  | 1.2  | 1.45 | V    |

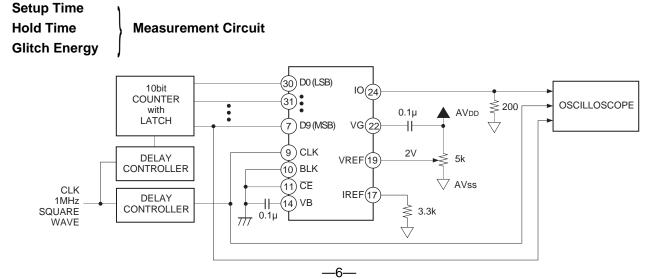

| Setup time                                | ts     |                                              | 3.0  |      |      | ns   |

| Hold time                                 | th     |                                              | 3.0  |      |      | ns   |

| Rise time                                 | tr     |                                              | 5    |      |      | ns   |

| Propagation delay time                    | tpD    |                                              |      | 5    |      | ns   |

| CE enable time *                          | tE     | CE= H→L                                      |      | 1    | 2    | ms   |

| CE disable time *                         | to     | CE= L→H                                      |      | 1    | 2    | ms   |

$<sup>\</sup>ast~$  When the external capacitor for the VGR,VGG and VGB pins are 0.1  $\mu F.$

SONY CXD2315Q

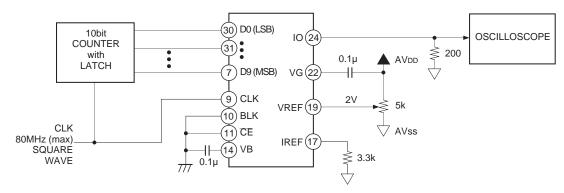

#### **Maximum Conversion Rate Measurement Circuit**

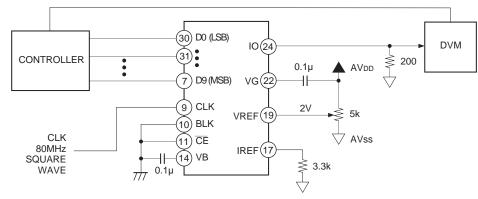

## **DC Characteristics Measurement Circuit**

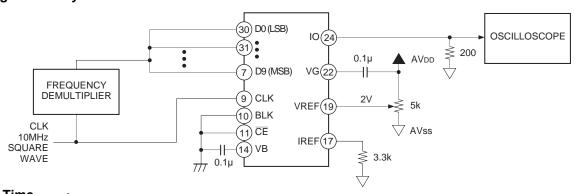

# **Propagation Delay Time Measurement Circuit**

# **Description of Operation Timing Chart**

# I/O Correspondence Table

(When 2.00 V output full-scale voltage)

| Input code          | Output voltage |

|---------------------|----------------|

| MSB LSB             |                |

| 1 1 1 1 1 1 1 1 1 1 | 2.0 V          |

| :<br>10000000000    | 1.0 V          |

| : 0 0 0 0 0 0 0 0 0 | 0 V            |

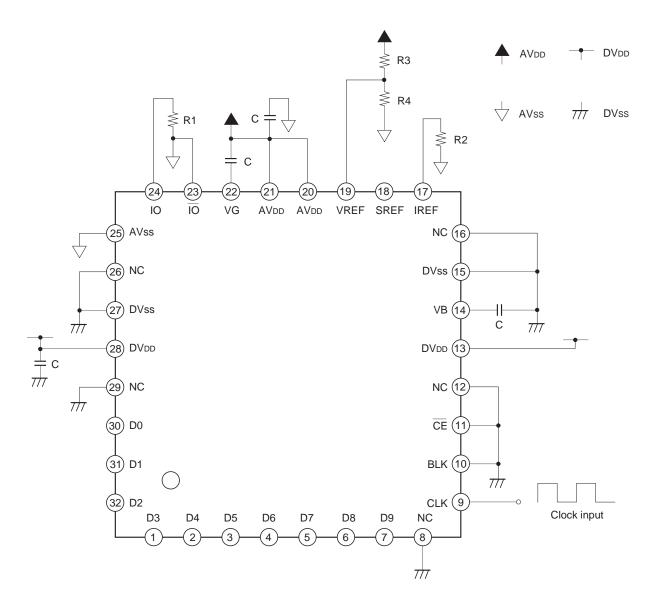

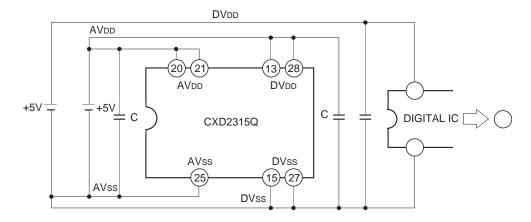

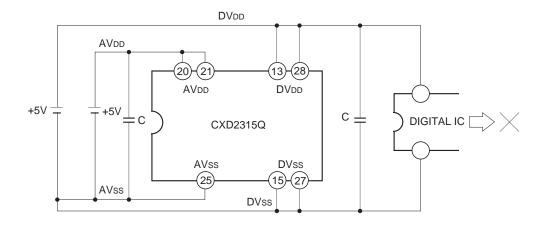

# **Application Circuit 1**

- When 5.0V supply voltage (DVpp and AVpp)

- Digital input from Pins 30 to 32 and Pins 1 to 7

- Pin 18 is left open when using normally

- R1=200Ω

- R2=3.3k $\Omega$  (resistance 16 times R1) (RIR)

- R3=3.0kΩ

- R4=2.0kΩ

- C=0.1µF

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

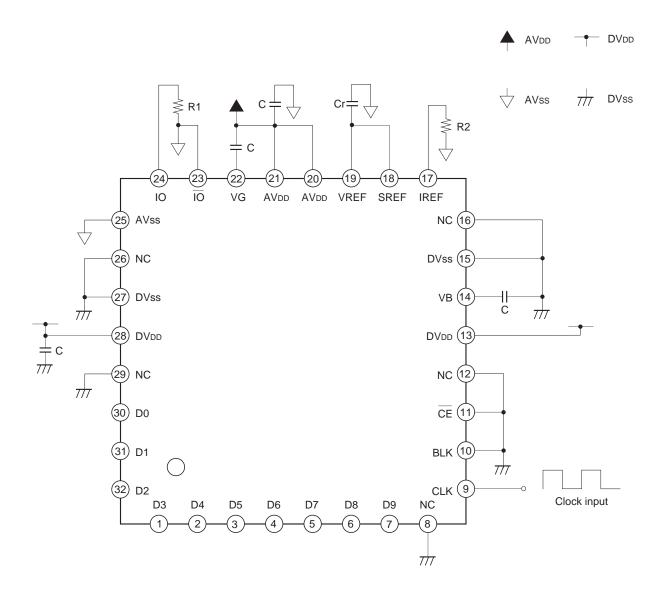

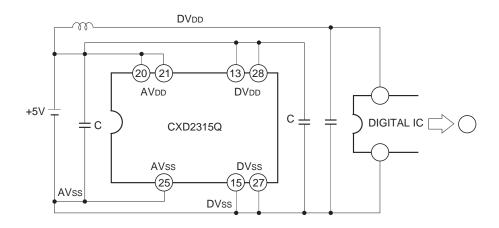

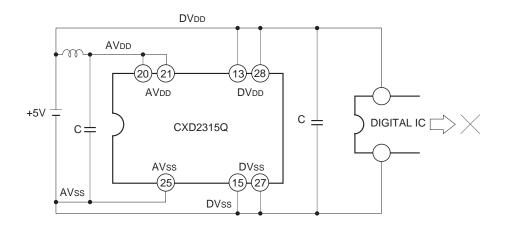

# **Application Circuit 2**

- When 5.0V supply voltage (DVDD and AVDD)

- Digital input from Pins 30 to 32 and Pins 1 to 7

- R1=200Ω

- R2=2.0kΩ

- C =0.1µF

- Cr =4.7μF

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

## **Notes on Operation**

## • Selecting the Output Resistance

CXD2315Q is a current output type D/A converter. To create the output voltage, connect the resistor to the current output pin IO.

Specifications: Output full-scale voltage VFS = 1.8 to 2.0 [V]

Output full-scale current IFs = 10 or less [mA]

Calculate the output resistance from  $V_{FS} = I_{FS} \times R_{OUT}$ . Connect a resistance sixteen times the output resistance to the reference current pin IREF. In some cases, as this value may not exist, a similar value can be used instead.

Note that the VFs will be the following.  $VFS = VREF \times 16 \text{ Rout/R}$

VREF is the voltage set at the VREF pin, ROUT is the resistor to be connected to the current output pin IO and RIR is the resistor to be connected to the IREF. Power consumption can be reduced by increasing the resistance, but this will on the contrary increase the glitch energy and data settling time. Set the best values according to the purpose of use.

#### Correlation between Data and Clock

For the CXD2315Q to display the desired performance as a D/A converter, the data transmitted from outside and the clock must be synchronized properly. Adjust the setup time (ts) and hold time (th) as specified in "Electrical Characteristics".

#### · Power supply and ground

Separate the analog and digital power supplies and grounds around the device to reduce noise effects. Bypass the power supply pin to each ground with a 0.1 µF ceramics capacitor as near to the pin as possible for both the digital and analog signals.

#### Latch up

Analog and digital power supply must be able to share the same power supply of the board. This is to prevent latch up caused by potential difference between the two pins when the power is turned on.

#### • IREF pin

The IREF pin is very sensitive to improve the AC characteristics. Pay attention for capacitance component not to attach to this pin because its output may become unstable.

# • VG pin

It is recommended to use a 1  $\mu F$  capacitor to improve the AC characteristics though the typical capacitance value externally connected to the VG pin is 0.1  $\mu F$ .

## SREF

SREF is an independent regulated voltage source. By connecting the SREF pin and the VREF pin, stable output amplitudes that do not depend on fluctuations in the power supply can be obtained.

In this case, as described above,  $VFS = VSR \times 16ROUT/RIR$ , set the VFS according to RIR. VSR is the output voltage of the SREF pin.

Do not use this pin as a reference power supply for other ICs because this is dedicated for the VG pin of the CXD2315Q.

# • IO pin

The  $\overline{\text{IO}}$  pin is the inverted current output pin described in the Pin Description. The sum of the currents output from the IO pin and the  $\overline{\text{IO}}$  pin becomes the constant value for any input data.

However, the performances such as the linearity error of the  $\overline{10}$  pin output current is not guaranteed.

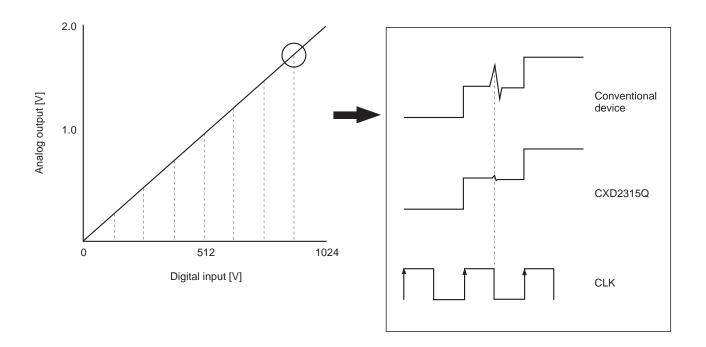

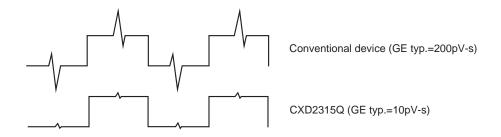

# **GE (Glitch energy)**

GE, described in the CXD2315Q, is a spike noise which appears synchronizing with the clock falling edge when the input data (for 1 to 1024 input) changes to 128, 256, 384, 512, 640, 768, 896, and 1024. Fig. 1 shows the change state of GE for the staircase wave output, and Fig. 2 shows the repetitive output waveform where the GE appears. These figures exhibit the difference of this IC from the conventional device.

Fig. 1. Change of GE for staircase wave output

Fig. 2. Repetitive output waveform where GE appears (for 200  $\Omega$ , 2 Vp-p output)

The CXD2315Q reduces the GE much shown in Fig.s 1 and 2.

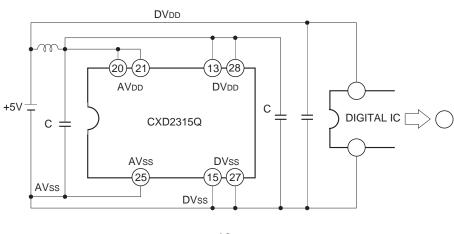

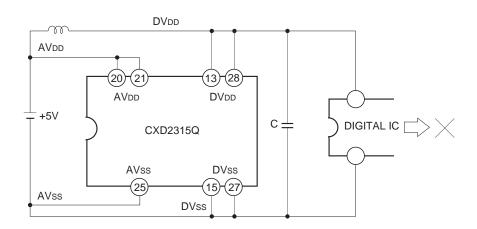

# **Latch Up Prevention**

The CXD2315Q is a CMOS IC which requires latch up precautions. Latch up is mainly generated by the lag in the voltage rising time of AVDD (Pins 20 and 21) and DVDD (Pins 13 and 28), when power supply is ON.

# 1. Correct usage

# a. When analog and digital supplies are from different sources

# b. When analog and digital supplies are from a common source

(i)

(ii)

- 2. Example when latch up easily occurs

- a. When analog and digital supplies are from different sources

# b. When analog and digital supplies are from common source

(i)

(ii)

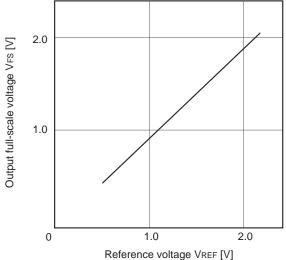

# **Example of Representative Characteristics**

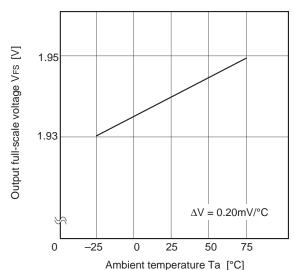

Fig. 3. Reference voltage vs.Output full-scale voltage

Fig. 4. Ambient temperature vs. Output full-scale voltage

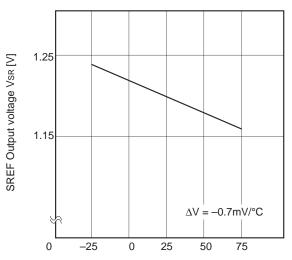

Ambient temperature Ta [°C] Fig. 5. Ambient temperature vs. SREF output voltage

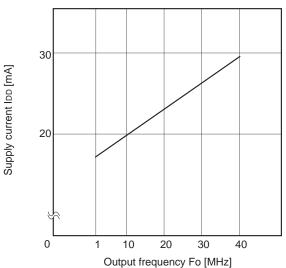

Fig. 6. Output frequency vs. Supply current

Standard Measurement Conditions and Description

- ADDD=DVDD=5V

- VREF=2.0V

- Rout=200 $\Omega$

- RIR= $3.3k\Omega$ • FCLK=80MHz

- Ta=25°C

- Fig. 4 includes the temperature characteristics of external metal film resistor.

- Input data in Fig. 6=all "0" and "1" of rectangular wave; clock frequency=80MHz.

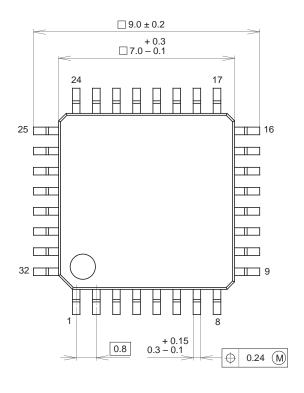

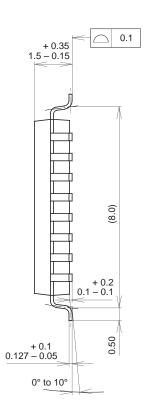

# Package Outline Unit: mm

# 32PIN QFP (PLASTIC)

| SONY CODE  | QFP-32P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP032-P-0707 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42 ALLOY       |

| PACKAGE MASS     | 0.2g           |