# **RGB** Decoder

#### Description

The CXA1585Q is an IC which converts Y/C separation signals into RGB signals, and can be used with both NTSC and PAL systems.

#### **Features**

- Filter for sharpness

- APL circuit

- Low carrier leak

(3.58MHz component, 5mVp-p or less Typ.)

- . Compatible with both NTSC and PAL systems

- Low power consumption (120mV, Vcc=5V)

#### **Applications**

General-purpose RGB decoders, color liquid crystal viewfinders, liquid crystal TVs, etc.

#### Structure

Bipolar silicon monolithic IC

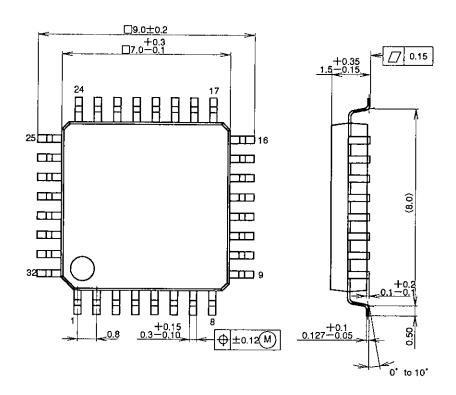

# 32 pin QFP (Plastic)

# Absolute Maximum Ratings (Ta=25°C)

| <ul> <li>Supply voltage</li> </ul> | Vcc   | 7           | ٧  |

|------------------------------------|-------|-------------|----|

| • Operating temperature            | Topr  | -20 to +75  | °C |

| Storage temperature                | Tstg  | -65 to +150 | °C |

| • Allowable power dissip           | ation |             |    |

|                                    | PD    | 500         | mW |

## **Recommended Operating Conditions**

Supply voltage 4.6 to 5.25 (Typ. 5V)

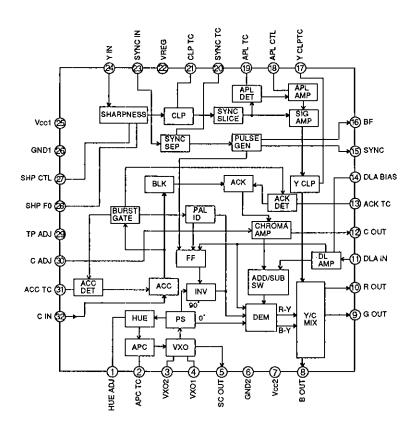

#### **Block Diagram**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# **Pin Description**

|            | Description |                |                               |                                                                                                                                                                                             |

|------------|-------------|----------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Symbol      | Pin<br>voltage | Equivalent circuit            | Description                                                                                                                                                                                 |

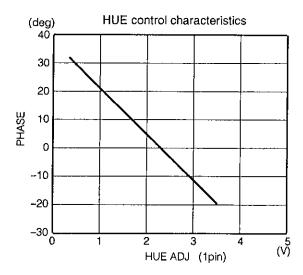

| 1          | HUE ADJ     | 2.0V           | 1                             | Hue adjustment. The hue can be adjusted by ±10° or more by applying a voltage ranging from 0.5 to 3.5 V to this pin.                                                                        |

| 2          | APC TC      | 3.4V           | ② 100k 100k 3.4V 1000 μA 3.4V | APC (color sync) time constant and free-<br>running frequency adjustment. The VXO free-running frequency can be<br>adjusted by varying the DC voltage applied<br>to this pin for no signal. |

| 3          | VXO2        | 3.1V           | 3 10k 100 µ A 100 µ A         | Crystal oscillator                                                                                                                                                                          |

| 4          | VXO1        | 3.2V           | 4<br>300 μ A                  | Crystal oscillator                                                                                                                                                                          |

| Pin<br>No. | Symbol | Pin<br>voltage                | Equivalent circuit                                            | Description                                                                                                                  |

|------------|--------|-------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 5          | SC OUT | 1.6V                          | 5<br>200 μ A                                                  | Subcarrier output  600mVP-P (Typ.)                                                                                           |

| 6          | GND2   | OV                            |                                                               | GND for chroma                                                                                                               |

| 7          | Vcc2   | 5V                            |                                                               | Vcc for chroma                                                                                                               |

| 9          | G OUT  | 2.0V                          | 8<br>10k<br>10k<br>4k<br>9<br>10<br>0.5p<br>364 μ Α<br>92 μ Α | B output  * With 75% color bar reference level input  0.75VP-P  R output  0.75VP-P  0.75VP-P                                 |

| 11         | DLA IN | 0V<br>(NTSC)<br>2.3V<br>(PAL) | 1129<br>5k<br>5k<br>W<br>4k<br>112 \( \mu A \) \( 4k          | Delay line amplifier input.  Connects to GND for NTSC mode; connects the 1H delay line output for PAL mode.  Approx. 10mVP-P |

| Pin<br>No. | Symbol   | Pin<br>voltage                             | Equivalent circuit                    | Description                                                                                                                               |

|------------|----------|--------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 12         | COUT     | 3.15V                                      | ②———————————————————————————————————— | Chroma output for PAL.  Connects to Vcc for NTSC mode; connects to the 1H delay line input for PAL mode.  Approx. 45mVP-P                 |

| 13         | ACK TC   | 3.1V                                       | 13 100k                               | ACK (automatic color killer) time constant                                                                                                |

| 14         | DLA BIAS | 0V<br>(NTSC)<br>2.3V<br>(PAL)              | 30 μA  10k 5k 5k 7k 4k 30 μA          | NTSC/PAL mode switching and delay line amplifier gain control  NTSC mode: V14≤0.8V  PAL mode: 2.0V≤V14≤2.6V  Variable range: ±2dB or more |

| 15         | SYNC     | H<br>4V or<br>more<br>L<br>0.5V or<br>less | \$32k \$2k \$2k \$1k \$5k             | Composite sync output. This polarity is positive. (Typ.)  -4.7μs (Typ.)  1H                                                               |

| Pin<br>No. | Symbol  | Pin<br>voltage                             | Equivalent circuit               | Description                                                                                                                                   |

|------------|---------|--------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 16         | BF      | H<br>4V or<br>more<br>L<br>0.5V or<br>less | \$32k \$2k \$2k \$1k \$5k        | Burst flag output. This polarity is negative. (Typ.)  2.6µs (Typ.)                                                                            |

| 17         | YCLPTC  | 3.1V                                       | 1k \$1k<br>60k<br>100 μ A 60 μ A | Pedestal clamp time constant                                                                                                                  |

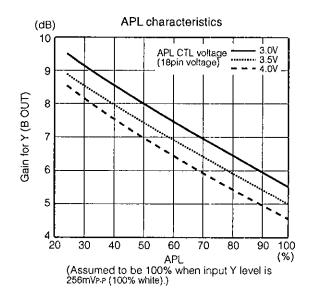

| 18         | APL CTL | 3.0V                                       | 8k 8k 8k 8k                      | APL sensitivity control. The control range is 3 to 5V. When APL control is not performed, connects this pin to GND.                           |

| 19         | APL TC  | 2.5V                                       | 164 μ A 50 μ A                   | Time constant for detecting APL (average picture level) of luminance signal APL 0% V19=2.0V (Typ.) APL 100% V19=3.2V (Typ.)  256mV≡100% white |

| Pin<br>No. | Symbol  | Pin<br>voltage | Equivalent circuit                  | Description                                                                                                           |

|------------|---------|----------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 20         | SYNC TC | 3.1V           | 20<br>3.4V 60k<br>3.4V 60μ<br>60 μΑ | Sync tip clamp time constant for sync separation                                                                      |

| 21         | CLP TC  | 3.1V           | ②<br>3.4V 60k<br>100 μΑ<br>60 μΑ    | Pedestal clamp time constant                                                                                          |

| 22         | VREG    | 4.2V           |                                     | 4.2V regulator output. Decoupling capacitance is provided. It cannot be used as an external power supply.             |

| 23         | SYNC IN | 2.5V           | 23 129 Solk T2.5V 60 $\mu$ A        | Signal input pin for sync separation.  Standard sync level is 103mVp-p.  Normally shorted with Y IN (Pin 24) for use. |

| Pin<br>No. | Symbol  | Pin<br>voltage | Equivalent circuit         | Description                                                                                                                                 |

|------------|---------|----------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 24         | YIN     | 2.5V           | 24 129                     | Y signal input. Standard input level SYNC=103mVp-p 100% white=256mVp-p Do not supply the burst signal.                                      |

| 25         | Vcc1    | 5V             |                            | Vcc for Y                                                                                                                                   |

| 26         | GND1    | OV             |                            | GND for Y                                                                                                                                   |

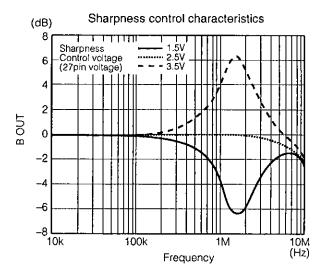

| 27         | SHP CTL | 2.5V           | 32k<br>32k<br>32k<br>72.5V | Sharpness gain control  Variable range: –4.5dB to +4.5dB  (1.5V≤V27≤3.5V)  Adjusts the sharpness level by the voltage supplied to this pin. |

| 28         | SHP F0  | 2.1V           | 2.1V π 46 μ A              | Sharpness filter frequency adjustment. Adjusts the filter fo by varying the current took out from this pin.                                 |

| Pin<br>No. | Symbol | Pin<br>voltage | Equivalent circuit                                               | Description                                                                                                                                              |

|------------|--------|----------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29         | TPADJ  | 1.23V          | 129 10k 2.5k                                                     | Sets the timing of the pulses used in the IC. Connects a 27kW resistor between this pin and GND.  * Use a metal film resistor with an accuracy of ±1%.   |

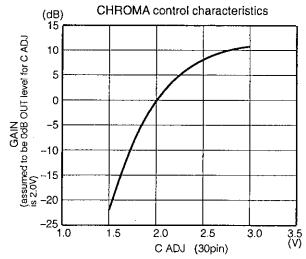

| 30         | C ADJ  | 2.5V           | 30 - W 25k | Chroma amplifier gain adjustment. Adjusts the gain of chroma amplifier by the voltage (1.5 to 3V) supplied to this pin. Gain variable range: -20 to +8dB |

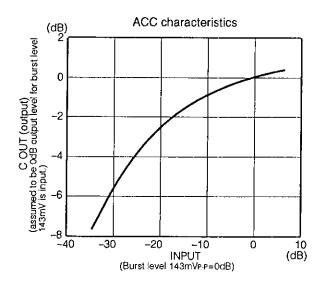

| 31         | ACC TC | 2.2V           | 31 → S220 → 97 μA                                                | ACC (automatic color control) time constant                                                                                                              |

| 32         | CIN    | 2.3V           | 2.5k 2.5k 8k 2.3V 8k 2.3V 2.3V                                   | Chroma signal input. The standard input level is 143mVp-p of burst amplitude.                                                                            |

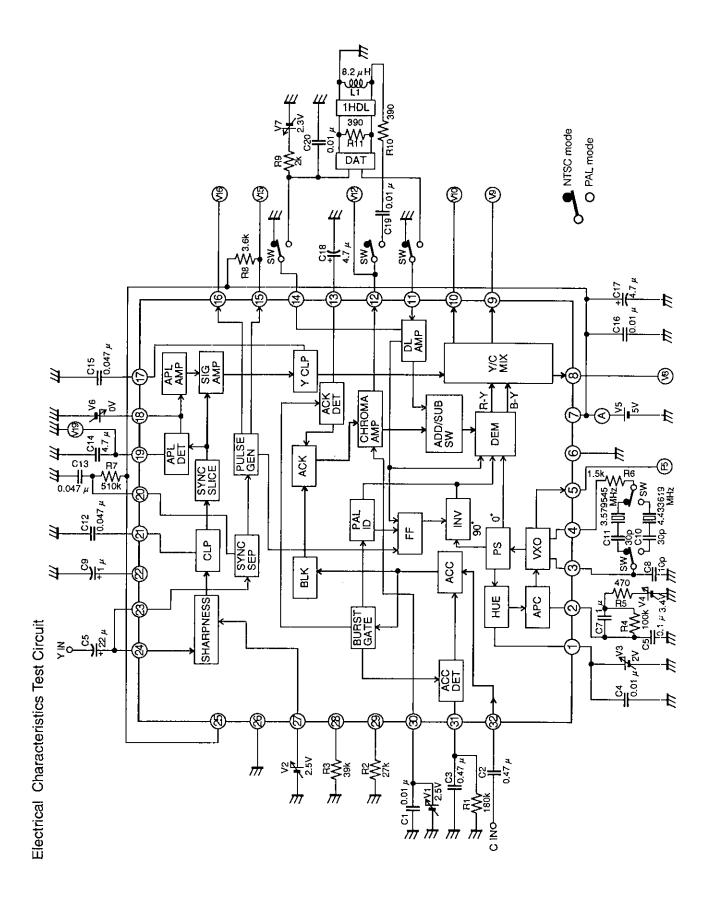

# **Electrical Characteristics**

(Ta=25°C, Vcc=5V Refer to the Electrical Characteristics Test Circuit)

| Item                                    | Symbol         | Conditions                                                                                                    | Input s | ignals<br>C IN | Test<br>point | Min    | Тур. | Max          | Unit     |

|-----------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------|---------|----------------|---------------|--------|------|--------------|----------|

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                |                                                                                                               | 24pin   |                | l '           | '*'''' | γp.  | I WILLY.     | `````    |

| Power consumption                       | lcc1           | Sum of currents flowing to Vcc1 and Vcc2                                                                      | SIG1    |                | 7, 25         | 17.0   | 24.0 | 32.0         | mA       |

| Gain for Y                              | Vo             | F=300kHz, Va=160mVp-p,<br>VL=160mV<br>Measure gain between input<br>(=VL) and output.                         | SIG2    | _              | 8             | 10.0   | 11.5 | 13.0         | dB       |

| Cut-off frequency<br>for Y              | VFC            | F=3.5MHz, Va=160mVp-p,<br>VL=160mV<br>Gain difference between 300kHz<br>and 3.5MHz                            |         |                | 8             | -3.0   |      |              | dB       |

| Sharpness characteristics Max.          | VSHP<br>(Max.) | F=1.5MHz, Va=50mVp-p,<br>VL=160mV<br>Ratio of 300kHz and 1.5MHz<br>when SHP CTL (Pin 27) is 3.5V.             | SIG2    |                | 8             | 4.5    |      |              | dΒ       |

| Sharpness characteristics Min.          | VSHP<br>(Min.) | F=1.5MHz, VA=160mVp-p,<br>VL=160mV<br>Ratio of 300kHz and 1.5MHz<br>when SHP CTL (Pin 27) is 1.5V.            | SIG2    | _              | 8             |        |      | <b>-4.</b> 5 | dΒ       |

| AGC characteristics<br>APL 100%         | Vagc1          | F=300kHz, Va=160mVp-p,<br>VL=256mV<br>Measures gain between input<br>(=VL) and output.                        | SIG2    |                | 8             | 3.6    | 4.9  | 6.2          | dΒ       |

| AGC characteristics<br>APL 50%          | VAGC2          | F=300kHz, VA=160mVp-p,<br>VL=128mV<br>APL CTL(18pin)=3.0V<br>Measures gain between input<br>(=VL) and output. | SIG2    |                | 8             | 3.9    | 5.5  | 7.0          | dВ       |

| AGC characteristics<br>APL 35%          | VAGC3          | F=300kHz, Va=160mVp-p,<br>VL=90mV<br>APL CTL(18pin)=3.0V<br>Measures gain between input<br>(=VL) and output.  | SIG2    |                | 8             | 6.3    | 8.0  | 9.7          | dΒ       |

| AGC OUT<br>APL 100%                     | VAGC4          | VL=256mV Measures DC voltage at APL TC (Pin 19).                                                              | SIG3    |                | 19            | 3.0    | 3.2  | 3.5          | <b>V</b> |

| AGC OUT<br>APL 0%                       | Vagc5          | 1 ` '                                                                                                         | SIG3    | _              | 19            | 1.9    | 2.0  | 2.2          | V        |

| RGB output<br>pedestal level            | VDC            | Measures pedestal voltage at<br>Pins 8, 9 and 10.                                                             | SIG1    |                | 8<br>9<br>10  | 1.4    | 2.0  | 2.4          | <b>V</b> |

| _              |        | _                                                               |      | signals       | Test           |      |         | -            |     |

|----------------|--------|-----------------------------------------------------------------|------|---------------|----------------|------|---------|--------------|-----|

| Item           | Symbol | Conditions                                                      | Y IN | C IN<br>32pin | point<br>(pin) | Min. | Тур.    | Мах.         | Uni |

| APC pull-in    | Fpu    | Inputs fsc+250Hz sine wave and                                  | +    | SIG5          | 5              | 250  |         | i            | Hz  |

| upper range    |        | confirms that it is locked with SC                              | 1    | /SIG8         |                |      | ŀ       |              |     |

|                |        | OUT (Pin 5).                                                    |      |               |                |      |         |              |     |

| APC pull-in    | Fpd    | Inputs fsc-250Hz sine wave and                                  | SIG1 | SIG5          | 5              |      |         | -250         | Hz  |

| lower range    |        | confirms that it is locked with SC                              |      | /SIG8         |                | ļ    |         |              |     |

|                |        | OUT (Pin 5).                                                    |      |               |                |      |         |              |     |

| ACC cover      | Acc1   | C OUT (6dB : \/a=296m\/o n)                                     | SIG1 | SIG4          | 12             |      | 0.5     | 3.0          | dΒ  |

| upper range    |        | Acc1= C OUT (6dB : VA=286mVp-p)<br>C OUT (0dB : VA=143mVp-p)    |      | /SIG7         |                |      |         |              |     |

| ACC cover      | Acc2   | C OUT ( 14dB : \/a=28 6m\/n n)                                  | SIG1 | SIG4          | 12             | -3.0 | -1.5    |              | dΒ  |

| lower range    |        | Acc2= C OUT (-14dB : Va=28.6mVp-p)<br>C OUT (0dB : Va=143mVp-p) |      | /SIG7         |                |      |         |              |     |

| Output D range | VDL    | C ADJ (30pin)=3.0V                                              | SIG1 | SIG6          | 8              | 1.0  |         |              | ٧   |

|                |        | Measures<br>B OUT Level.                                        |      | /SIG9         |                |      |         |              |     |

| Carrier leak   | CL     | Input signal: SYNC only                                         | SIG1 | _             | 8              |      | 5       | 20           | mV  |

|                |        | Measures 3.58MHz component                                      |      |               |                |      |         |              |     |

| NTSC ACK       | Ack    | of output. With Va=143mVp-p as 0dB,                             | SIG1 | SIG4          | 12             | -50  |         | -30          | dB  |

| operation      | , ion  | measures input level (VA) when                                  | l    | /SIG7         | -              |      |         |              | uD  |

|                | İ      | C OUT chroma signal is no                                       | l    |               |                |      |         |              |     |

|                |        | longer output, and calculates the                               | 1    |               | •              |      |         |              |     |

|                |        | ratio of this to when the level is                              |      |               |                |      |         |              |     |

|                |        | 143mVp-p.                                                       |      |               |                |      |         |              |     |

| C.SYNC         | Vон    |                                                                 | SIG1 | _             | 15             | 4.0  |         |              | ٧   |

| High level     |        |                                                                 |      |               |                |      |         |              |     |

| C.SYNC         | Vol    |                                                                 | SIG1 |               | 15             |      |         | 0.5          | V   |

| Low level      |        |                                                                 |      | :             |                |      |         |              |     |

| Burst flag     | Vон    |                                                                 | SIG1 | -             | 16             | 4.0  |         |              | ٧   |

| High level     |        |                                                                 |      |               |                |      |         |              |     |

| Burst flag     | Vон    |                                                                 | SIG1 |               | 16             |      | <u></u> | 0.5          | ٧   |

| Low level      |        |                                                                 |      |               |                |      |         |              |     |

| Subcarrier     | Vo(sc) | Amplitude when frequency at Pin                                 | SIG1 |               | 5              | 500  | 600     | <del> </del> | mV  |

| output voltage |        | 5 is adjusted to 3.579545MHz<br>±20Hz.                          |      |               |                |      |         |              |     |

Vcc1=5V, Vcc2=5V, Ta=25°C

<sup>\*</sup> Default conditions for pin settings SHP F0=39k $\Omega$ , SHP CTL=2.5V, APL CTL=0V

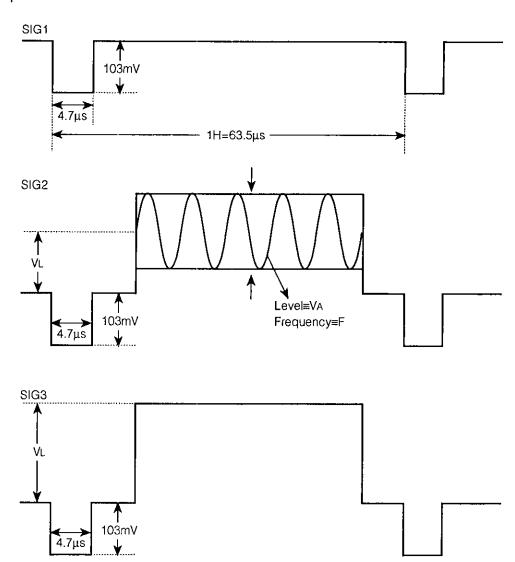

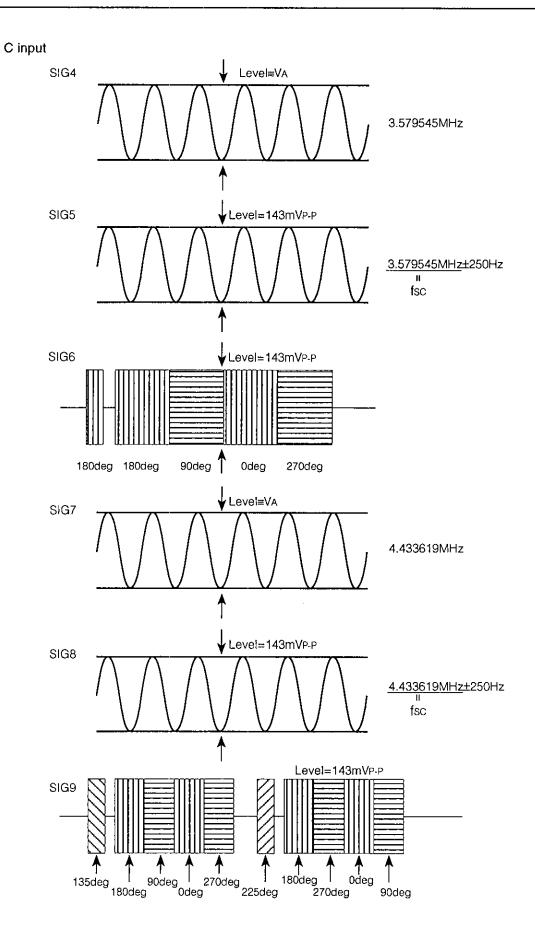

# Input signals (electrical characteristic input signals)

# Y input

#### **Description of Operation**

#### (1) Luminance signal regeneration system

#### <1> Sharpness filter

The video (luminance and sync) signals input from Pin 24 (VIDEO IN) are boosted near 1.5MHz by the sharpness filter. The 1.5MHz component can be varied from -4.5 to +4.5dB (as compared to the 300kHz) according to the voltage of Pin 27 (SHP CTL). Approximately 0dB (as compared to the 300kHz) when Pin 27 (SHP CTL) is 2.5 V.

Keep Pin 27 open when sharpness is not operated. Since the DC bias in the IC is 2.5V, the frequency response characteristics are almost the same as the characteristics applied 2.5V to Pin 27 externally.

#### <2> APL circuit

The Y AMP gain is controlled by the APL (average picture level) function, and the gain is reduced as the APL increases.

The APL circuit is operated when the voltage at Pin 18 (APL CTL) is between 3.0V and 5.0V. It is OFF when APL CTL is 0V.

#### (2) Chrominance signal regeneration system

#### <1> ACC circuit

The chroma signal input from Pin 32 (C IN) is controlled so that the burst signal is detected by ACC DET, feedback is applied to ACC AMP in accordance with the detective output, and the burst level is controlled to be constant.

The chroma signal level (Pin 12) is approximately 45mVp-p for ACC operations.

#### <2> APC circuit

Only the burst signal among the signals whose level has been made constant by ACC AMP enters the APC circuit at the burst gate circuit. 0°, 90° and 180° signals are generated in the phase circuit for the VXO output, and their composite waves (90° carrier) enter the APC circuit passing through the hue circuit.

Here their phase is compared with that of the burst signal and feedback is applied to VXO to obtain a phase difference of 90°. The 0° and 90° carriers created in this way are supplied to B-Y, R-Y and DEM. This means that the demodulation axis can be changed by rotating the phase of the composite waves by the DC voltage at Pin 1 (HUE ADJ).

#### <3> DEM circuit (NTSC)

The chroma signal whose level has been made constant by ACC AMP is amplified by CHROMA AMP, demodulated by B-Y DEM and R-Y DEM, applied to the Y/C MIX circuit with G-Y created by the resistance matrix, mixed with the luminance signal and then output as the R, G and B primary colors.

#### <4> DEM circuit (PAL)

The processing is the same as for NTSC until CHROMA AMP. The chroma signal output to Pin 12 (C OUT) enters DL AMP from Pin 11 (DLA IN) via 1HDL (1H delay line), its level is controlled, and the signal is applied to the ADD/SUB circuit. The original signal is added or subtracted in this circuit: the addition signal is applied to B-Y DEM and the subtraction signal to R-Y DEM, and they are demodulated by the 90° carrier whose phase is inverted every 1H and the 0° carrier.

The signals are then mixed with the luminance signal and output as the R, G and B primary colors.

#### <5> PAL ID

In PAL mode, the phase of the 90° carrier is inverted in synchronization with H.SYNC. Sync detection is conducted to establish whether this matches the input burst. When there is an error, it is corrected by applying feedback to FF (flip-flop).

# (3) Sync separation system

The sync tip of the video signals input from Pin 23 (SYNC IN) is clamped and the sync signals are separated. On the basis of the SYNC pulse created here, BF (burst flag), BLK pulse and other timing pulses are generated and supplied to the circuits. The SYNC and BF (burst flag) pulses are output to Pins 15 and 16 via a buffer.

## **Adjustment Procedure**

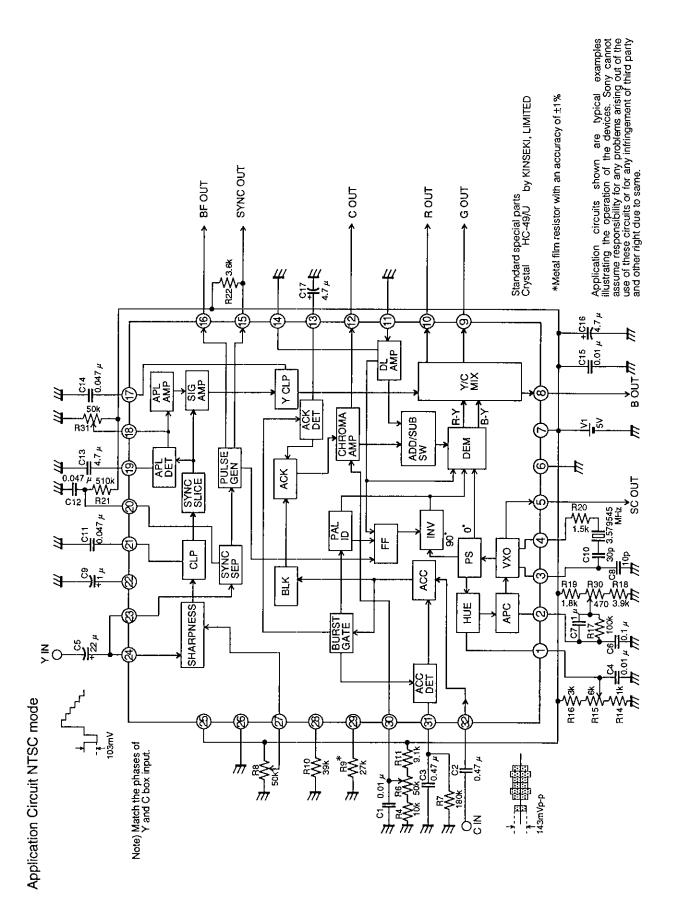

#### **NTSC** mode

Input signal: 75% color bar

## 1) Free-running f0 adjustment

Adjust (R30) the DC voltage at Pin 2 (APC TC) so that the oscillation frequency (subcarrier) fsc=3.579545MHz at Pin 5 (SC OUT) is within ±20Hz under inputting sync condition.

# 2) Input level adjustment

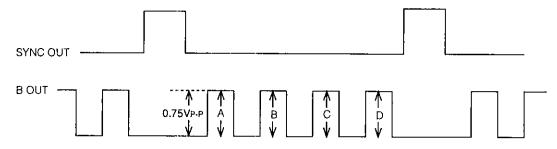

Adjust (R13) the input level so that the white peak (75% white) is set to 0.75Vp-p at the B output. Connect Pin 18 (APL CTL) to GND at this time.

### 3) HUE ADJ, C ADJ adjustment

Adjust (R15, R6) HUE ADJ (Pin 1) and C ADJ (Pin 30) so that the colors (A, B, C and D in the figure below) of the B output amplitude are set to the same amplitude.

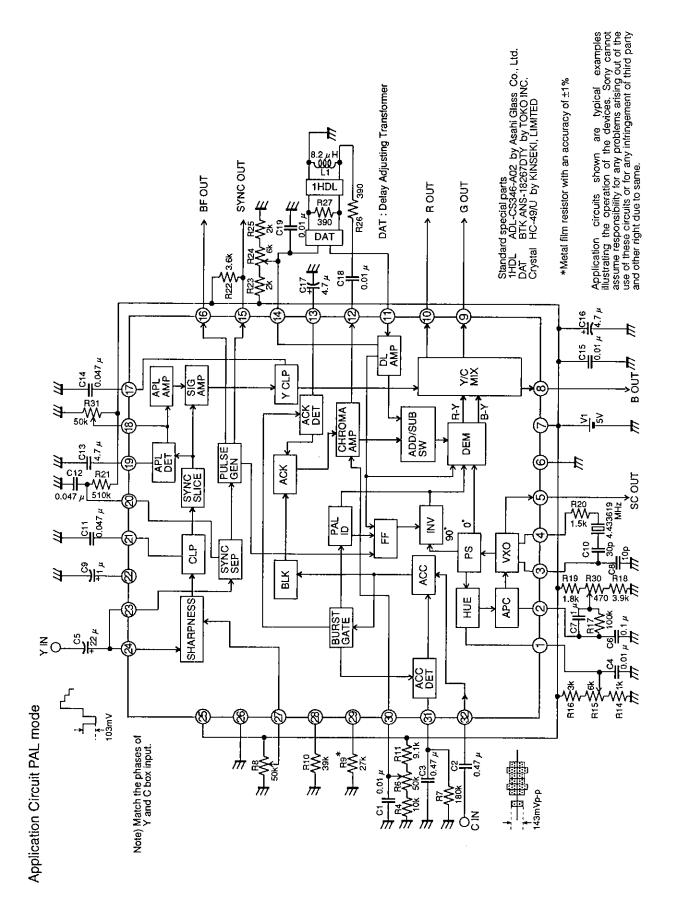

#### PAL mode

Input signal: 75% color bar

#### 1) Free-running f0 adjustment

Adjust (R30) the DC voltage at Pin 2 (APC TC) so that the oscillation frequency (subcarrier) fsc=4.433619MHz at Pin 5 (SC OUT) is within ±20Hz under inputting sync condition.

- 2) Input level adjustment (same as for NTSC)

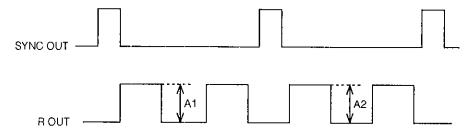

- 3) DL AMP and DAT (delay adjusting transformer) adjustment

Adjust (R24, DAT) Pin 14 (DLA BIAS) and DAT alternately so that the R output amplitudes (A1 and A2) are equal for the H periods before and after.

#### 4) C ADJ adjustment

Adjust (R6) C ADJ so that the colors of the R output amplitude are set to 0.75Vp-p.

#### **Applications**

1) The input dynamic range is 0.36Vp-p (max.). The breakdown is given as follows.

Y IN (Pin 24) Sync signal: 0.103Vp-p

Luminance signal: 0.256Vp-p (100% white)

C IN (Pin 32) Burst signal: 0.143Vp-p

Note that when the input signal exceeds the value of 0.36Vp-p from sync tip to white peak, the output may be clipped and flattened.

This applies the case for the APL circuit OFF (Pin 18 APL CTL=0V).

- 2) The center frequency for the sharpness varies according to the resistor connected to Pin 28. The variation is -40 kHz/kW, and the standard value is approximately 1.5MHz for 39kW.

- 3) The voltage of Pin 19 (APL TC) is the following values according to the APL (average picture level).

APL 0% (all black) : 2.0V APL 100% (all white) : 3.2V

- 4) Pin 23 (SYNC IN) is normally connected to Pin 24 (Y IN) for use. To cope with weak electric fields, however, its level can be increased or a low-pass filter inserted to provide a separate input.

- 5) The amount of delay for luminance and chroma signals in the IC is the same.

- 6) Demodulation axis and detective output ratio

The standard values are given below as referenced to the B-Y axis.

|          | Demodulation axis | Detective output ratio |

|----------|-------------------|------------------------|

| R-Y axis | 88°               | 0.57                   |

| G-Y axis | 235°              | 0.37                   |

7) Notes on Operation

Be sure to wire X'tal (crystal oscillator) as close to the IC and as short as possible since F0 varies depending on floating capacitance and other factors. Also, take particular care with the routing of the Vcc and GND leads. Use a decoupling capacitor for Vcc and others with a superior performance and attach it as close to the IC as possible.

# Package Outline Unit: mm

# 32PIN QFP(PLASTIC)

# PACKAGE STRUCTURE

| SONY CODE  | QFP-32P-L01      |

|------------|------------------|

| EIAJ CODE  | *QFP032-P-0707-A |

| JEDEC CODE |                  |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42ALLOY        |

| PACKAGE WEIGHT   | 0.29           |