# 10-bit 33MSPS A/D Converter

# Description

The CXA1844Q is a 10-bit 33MSPS 2-step parallel type A/D converter for video signal processing.

This A/D converter operates on ± 5V power supplies. The analog signal can be converted to the digital signal by using this IC in conjunction with the Sample-and-hold IC (CXA1843Q).

#### **Features**

Maximum operating speed

: 33MSPS (Min.)

Resolution

: 10-bit

Low power dissipation

: 320mW (Typ.)

Wide-band analog input

: 15MHz

Low input capacitance

: 50 pF (Typ.)

Built-in digital correction

(Compensation within ± 16 LSB)

TTL input (Except CLK which is ECL LIKE)

TTL output

Output code

: binary/2S complement/

1S complement

## **Function**

10-bit 33MSPS 2-step parallel type A/D converter

### Structure

Bipolar silicon monolithic IC

# **Applications**

High resolution video signal processing

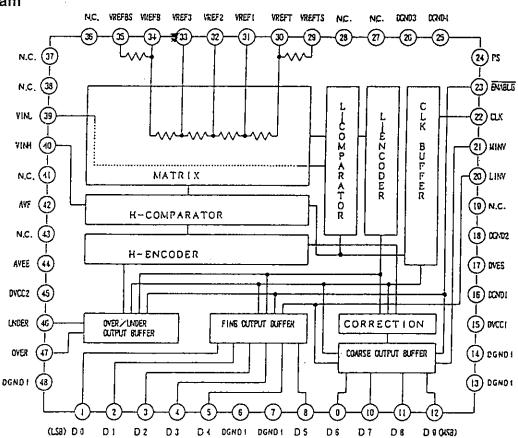

# **Block Diagram**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

|                                                                   |                                                                 |                                                                      | _                                        |                                               |                       |

|-------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------|-----------------------------------------------|-----------------------|

| Absolute Maximum Rat                                              | lings (Ta=:                                                     | 25℃)                                                                 |                                          |                                               |                       |

| Supply voltage                                                    | DVcc1                                                           | •                                                                    | 0 to +6                                  | 8                                             | V                     |

|                                                                   | DVcc2                                                           |                                                                      | 0 to +6                                  | <b>3</b> .                                    | V                     |

|                                                                   | AVEE                                                            |                                                                      | 6 to €                                   | )                                             | V                     |

|                                                                   | DVEE                                                            |                                                                      | 6 to 0                                   | )                                             | V                     |

| Analog input voltage                                              | VINH                                                            |                                                                      | AVEE to AV                               | F+0.3                                         | V                     |

|                                                                   | VINL                                                            |                                                                      | AVEE to AV                               | F+0.3                                         | ٧                     |

| Reference voltage                                                 | VREFT                                                           |                                                                      | AVEE to AVI                              | F+0.3                                         | V                     |

| -                                                                 | VREFB                                                           |                                                                      | AVEE to AV                               | F+0.3                                         | ٧                     |

| Digital input voltage                                             | CLK                                                             |                                                                      | DGND1-0.5 to                             | DVcc1                                         | V                     |

|                                                                   | MINV                                                            |                                                                      | DGND1-0.5 to                             | DVcc1                                         | ٧                     |

|                                                                   | LINV                                                            |                                                                      | DGND10.5 to                              | DVcc1                                         | ٧                     |

|                                                                   | PS                                                              |                                                                      | DGND10.5 to                              |                                               | V                     |

|                                                                   | ENABLE                                                          |                                                                      | DGND10.5 to                              | DVcc1                                         | V                     |

| Digital output voltage                                            | Vo                                                              |                                                                      | DGND1-0.51                               | o +3.6                                        | V                     |

|                                                                   | (Vo: The v                                                      | oltage is appli                                                      | ed to the output                         | pin for high impeda                           | ance outpi            |

| Storage temperature                                               | Tstg                                                            |                                                                      | -65 to 15                                |                                               | °C                    |

| Allowable power dissipation                                       | Po                                                              |                                                                      | 0.62                                     |                                               | W                     |

| Recommended Operating                                             | na Condit                                                       | tions                                                                |                                          |                                               |                       |

|                                                                   | 3                                                               | Min.                                                                 | Тур.                                     | Max.                                          | Unit                  |

| Supply voltage                                                    | DVcc1                                                           | +4.75                                                                | +5                                       | +5.25                                         | V                     |

| - 1.7                                                             | DVcc2                                                           | +4.75                                                                | +5                                       | +5.25                                         | v                     |

|                                                                   | DGND1                                                           | •                                                                    | 0                                        | 10.20                                         | v                     |

|                                                                   | DGND2                                                           |                                                                      | 0                                        |                                               | v                     |

|                                                                   | DGND3                                                           | <b>5</b>                                                             | Ō                                        |                                               | v                     |

|                                                                   | DGND4                                                           |                                                                      | 0                                        |                                               | v                     |

|                                                                   | AVF                                                             | +0.5                                                                 | +0.7                                     | +0.9                                          | v                     |

|                                                                   |                                                                 |                                                                      | . • • •                                  |                                               |                       |

|                                                                   | AVEE                                                            | -5.25                                                                | -5                                       | -4.75                                         |                       |

|                                                                   | AVEE<br>DVEE                                                    | 5.25<br>5.25                                                         | -5<br>-5                                 | -4.75<br>-4.75                                | V                     |

| <ul> <li>Analog input voltage</li> </ul>                          | DVEE                                                            | 5.25                                                                 | -5<br>-5                                 | -4.75                                         | V<br>V                |

| <ul> <li>Analog input voltage</li> </ul>                          | DVEE<br>VINH                                                    | 5.25<br>2                                                            |                                          | -4.75<br>0                                    | V<br>V<br>V           |

| • • •                                                             | DVEE<br>VINH<br>VINL                                            | 5.25<br>2<br>2                                                       | <del></del> 5                            | -4.75<br>0<br>0                               | V<br>V<br>V           |

| <ul><li>Analog input voltage</li><li>Reference voltage</li></ul>  | DVEE<br>VINH<br>VINL<br>VREFT                                   | 5.25<br>2<br>2<br>0.1                                                | 5<br>0                                   | -4.75<br>0<br>0<br>+0.1                       | V<br>V<br>V           |

| • • •                                                             | DVEE<br>VINH<br>VINL<br>VREFT<br>VREFB<br>(CLK)                 | 5.25<br>2<br>2                                                       | <del></del> 5                            | -4.75<br>0<br>0                               | V<br>V<br>V           |

| Reference voltage                                                 | DVEE<br>VINH<br>VINL<br>VREFT<br>VREFB                          | 5.25<br>2<br>2<br>0.1                                                | 5<br>0                                   | -4.75<br>0<br>0<br>+0.1                       | V<br>V<br>V           |

| Reference voltage                                                 | DVEE<br>VINH<br>VINL<br>VREFT<br>VREFB<br>(CLK)                 | -5.25<br>-2<br>-2<br>-0.1<br>-2.1                                    | 5<br>0<br>2                              | -4.75<br>0<br>0<br>+0.1                       | V<br>V<br>V<br>V      |

| Reference voltage                                                 | DVEE<br>VINH<br>VINL<br>VREFT<br>VREFB<br>(CLK)<br>VIH1<br>VIL1 | -5.25<br>-2<br>-2<br>-0.1<br>-2.1                                    | -5<br>0<br>-2<br>DVcc1-0.75<br>DVcc1-1.5 | -4.75<br>0<br>0<br>+0.1<br>-1.9               | V<br>V<br>V<br>V      |

| Reference voltage                                                 | DVEE<br>VINH<br>VINL<br>VREFT<br>VREFB<br>(CLK)<br>VIH1<br>VIL1 | -5.25<br>-2<br>-2<br>-0.1<br>-2.1<br>DVcc1-0.9                       | -5<br>0<br>-2<br>DVcc1-0.75<br>DVcc1-1.5 | -4.75<br>0<br>0<br>+0.1<br>-1.9               | V<br>V<br>V<br>V      |

| Reference voltage                                                 | DVEE VINH VINL VREFT VREFB (CLK) VIH1 VIL1 (MINV, LIN           | -5.25<br>-2<br>-2<br>-0.1<br>-2.1<br>DVcc1-0.9<br>V, PS, ENABL       | -5<br>0<br>-2<br>DVcc1-0.75<br>DVcc1-1.5 | -4.75<br>0<br>0<br>+0.1<br>-1.9               | V<br>V<br>V<br>V      |

| Reference voltage                                                 | DVEE VINH VINL VREFT VREFB (CLK) VIH1 VIL1 (MINV, LIN VIH2      | -5.25<br>-2<br>-2<br>-0.1<br>-2.1<br>DVcc1-0.9<br>V, PS, ENABL       | -5<br>0<br>-2<br>DVcc1-0.75<br>DVcc1-1.5 | -4.75<br>0<br>0<br>+0.1<br>-1.9<br>DVcc1-1.35 | V<br>V<br>V<br>V<br>V |

| <ul><li>Reference voltage</li><li>Digital input voltage</li></ul> | DVEE VINH VINL VREFT VREFB (CLK) VIH1 VIL1 (MINV, LIN VIH2 VIL2 | -5.25<br>-2<br>-2<br>-0.1<br>-2.1<br>DVcc1-0.9<br>V, PS, ENABL<br>+2 | -5<br>0<br>-2<br>DVcc1-0.75<br>DVcc1-1.5 | -4.75<br>0<br>0<br>+0.1<br>-1.9<br>DVcc1-1.35 | <pre></pre>           |

Pin Description

| 1 111 20                 | escriptio | •   |             |                                                 |                                                                                                                                                         |

|--------------------------|-----------|-----|-------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No.               | Symbol    | 1/0 | Pin voltage | Equivalent circuit                              | Description                                                                                                                                             |

| 1 to 5<br>8 to 12        | D0 to D9  | 0   |             | 7 () 00-√304<br>→ 304mz                         | Digital output<br>D0 (LSB) to D9 (MSB)                                                                                                                  |

| 46                       | UNDER     | 0   | ΤΤL         | @umoen @umoen                                   | Underflow output                                                                                                                                        |

| 47                       | OVER      | 0   |             | (a) 06 Mg 1                                     | Overflow output                                                                                                                                         |

| 15                       | DVcc1     |     | +5V         |                                                 | D:-3-1                                                                                                                                                  |

| 45                       | DVcc2     | —   | Тур.        |                                                 | Digital power supply                                                                                                                                    |

| 6, 7<br>13, 14<br>16, 48 | DGND1     |     |             |                                                 |                                                                                                                                                         |

| 18                       | DGND2     |     | GND         |                                                 | Digital ground                                                                                                                                          |

| 26                       | DGND3     |     |             |                                                 |                                                                                                                                                         |

| 25                       | DGND4     |     |             |                                                 |                                                                                                                                                         |

| 17                       | DVEE      |     | -5V         |                                                 | Digital negative power supply                                                                                                                           |

| 44                       | AVEE      |     | Тур.        |                                                 | Analog negative power supply                                                                                                                            |

| 20                       | LINV      | i   | TTL         | <b>₹</b>                                        | This input can invert output form of D0 to D8. In open condition, this pin turns to high level input. (For details, refer to the Output Formula Chart.) |

| 21                       | MINV      | ī   | ΊΤL         | ENABLE & SO | This input can invert output form of D9 (MSB). In open condition, this pin turns to high level input. (For details, refer to the Output Formula Chart.) |

| 23                       | ENABLE    | 1   | TTL         | DVEE (I) (B) DGND1                              | 3-state control. Turns to enable when low is input. In open condition, this pin turns to high level input.                                              |

| 24                       | PS        | l   | TTL         |                                                 | Power save input. Power save condition is entered when high level is input. In open condition, this pin turns to high level input.                      |

| 22                       | CLK       | 1   | ECL LIKE    | DVec 1  DVec 1  1.2  OVER (1)  OGNO 1           | Clock input                                                                                                                                             |

| Гъ:                        | <del></del> | <del></del> | <del>                                     </del> | 1                                               |                                                                                                  |

|----------------------------|-------------|-------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Pin<br>No.                 | Symbol      | 1/0         | Pin voltage                                      | Equivalent circuit                              | Description                                                                                      |

| 29                         | VREFTS      |             | CAID                                             |                                                 | Reference voltage sense<br>(Top)                                                                 |

| 30                         | VREFT       | 1           | GND                                              | VREFTS (2)                                      | Reference voltage force (Top)                                                                    |

| 31                         | VREF1       |             | -0.5V                                            | VREF1 (5) 7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                                                                                  |

| 32                         | VREF2       |             | -1.0V                                            | VREF3 (3)                                       |                                                                                                  |

| 33                         | VREF3       |             | -1.5V                                            | VAEFBS S W                                      |                                                                                                  |

| 34                         | VREFB       | ı           | _2V                                              | AVEZ @                                          | Reference voltage force (Bottom)                                                                 |

| 35                         | VREFBS      |             | -2V                                              | <u>-</u>                                        | Reference voltage sense (Bottom)                                                                 |

| 39                         | VINL        | 1           | –2V to 0V                                        | VINL SAVEY                                      | Analog input<br>(Lower comparator input)                                                         |

| 40                         | VINH        | 1           | –2V to 0V                                        | VINH @ #EF                                      | Analog input<br>(Upper comparator input)                                                         |

| 42                         | AVF         |             | +0.7V                                            |                                                 | Analog power supply                                                                              |

| 19, 27                     | N.C.        |             |                                                  |                                                 | Open. Not connected to internal circuit, but connection to DGND (digital ground) is recommended. |

| 28, 36<br>37, 38<br>41, 43 | N.C.        |             |                                                  |                                                 | Open. Not connected to internal circuit, but connection to AGND (analog ground) is recommended.  |

# **Electrical Characteristics**

(Ta=25 °C , DVcc1, 2=+5V, DGND1 to 4=0V, AVF=0.7V, AVEE, DVEE=-5V, VREFB=-2V, VREFT=0V)

| Item                          | Symbol           | Ţ     | Measure    | ment Conditions                       | Min.        | Тур. | Max.                                  | Unit |

|-------------------------------|------------------|-------|------------|---------------------------------------|-------------|------|---------------------------------------|------|

| Resolution                    | n                |       |            |                                       | 10          | 10   | 10                                    | bit  |

| DC characteristics            | •                | • • • | •          |                                       |             |      | · · · · · · · · · · · · · · · · · · · |      |

| Integral linearity error      | Ец               |       |            |                                       | -1.5        |      | +1.5                                  | LSB  |

| Differential linearity error  | Ept              | VIN   | i=-2 to 0' | V                                     | -1          |      | +1                                    | LSB  |

| Analog input                  |                  |       |            |                                       |             |      |                                       |      |

| Analog input current          | lін              | VIN   | =0         |                                       | 0           | 25   | 120                                   | μА   |

| Analog input capacitance      | Cin              | VIN   | =-1V+0.    | 07Vrms                                |             | 50   |                                       | pF   |

| Analog input band width       | BW               | -10   | dB         |                                       | 15          |      |                                       | MHz  |

| Reference voltage input       | •                |       |            |                                       | ····        |      | <del>_</del>                          |      |

| Reference current             | REF              | VRI   | FB=-2V     | ·                                     | 16          | -10  | -7                                    | mA   |

| Reference resistance          | RREF             |       |            | · · · · · · · · · · · · · · · · · · · | 120         | 200  | 280                                   | Ω    |

| Offset voltage                | Еот              |       |            |                                       | 5           | 10   | 25                                    | mV   |

| Onset voltage                 | Еов              |       |            |                                       | 5           | 10   | 25                                    | mV   |

|                               | VREF1            |       |            |                                       |             | -0.5 |                                       |      |

| Reference voltage             | VREF2            |       |            |                                       |             | -1.0 |                                       | V    |

|                               | VREF3            |       | <b>3</b> * |                                       |             | -1.5 |                                       | ٧    |

| Digital input                 |                  |       |            |                                       | <del></del> |      |                                       |      |

|                               | V <sub>tH1</sub> | *1    |            |                                       | DVcc1-0.9   |      |                                       | V    |

| Digital input voltage         | VIL1             |       | ĺ          |                                       |             |      | DVcc1-1.35                            | V    |

| Digital hiput voltage         | ViH2             | *2    |            |                                       | 2           |      |                                       | V    |

|                               | VIL2             |       | į          |                                       |             |      | 0.8                                   | V    |

|                               | litt             | *1    |            | ViH=DVcc1-0.8V                        | <b>–</b> 10 |      | +15                                   | μА   |

| Digital input current         | liLi             |       | DVcc1      | ViL=DVcc1-1.6V                        | 15          |      | +10                                   | μА   |

| Signal input current          | lıн2             | *2    | =Max.      | ViH=2.7V                              | <b>-</b> 15 |      | +15                                   | μA   |

|                               | 1112             | ~ ~   |            | VIL=0.5V                              | <b>–25</b>  |      | 0                                     | μA   |

| Digital input characteristics |                  |       |            |                                       |             | 2    |                                       | рF   |

| ltem                           | Symbol       | Massurame                           | ent Conditions | B.din.                                | <b>T</b> | 1    | 1                   |

|--------------------------------|--------------|-------------------------------------|----------------|---------------------------------------|----------|------|---------------------|

| <del> </del>                   | Symbol       | Weasureme                           | ent Conditions | Min.                                  | Тур.     | Max. | Uni                 |

| Switching characteristics      | T            | <del>,</del>                        |                |                                       |          |      |                     |

| Maximum operating speed        | Fc           |                                     |                | 33                                    |          | ļ    | MSPS                |

| Clock pulse width              | tрwн         |                                     |                | 14                                    |          |      | ns                  |

| Olook palso waar               | tpwl         | *3                                  | •              | 13                                    |          |      | ns                  |

| Sampling delay                 | tsн          |                                     |                | -2                                    | 1        | 2    | ns                  |

|                                | tsı          |                                     |                | -3                                    | -2.5     | 1    | ns                  |

| Output delay time              | <b>t</b> DLH | *3 Ct=30pF                          |                | 4                                     |          | 18   | ns                  |

| Output delay lime              | tonu         | *5                                  | 4              |                                       | 18       | ns   |                     |

| 3-state output disable time    | tpHZ         |                                     |                |                                       |          | 150  | ns                  |

| 3-state output disable time    | tplz         | *4                                  |                |                                       | 100      | ns   |                     |

| 3-state output enable time     | tрzн         | *6                                  |                |                                       | 300      | ns   |                     |

| 3-state output enable time     | tezu         |                                     |                |                                       |          | 150  | ns                  |

| Digital output                 |              |                                     |                | · · · · · · · · · · · · · · · · · · · |          |      |                     |

| Digital output voltage         | Voн          | Іон=-500 μ А                        | D) ( 14        | 2.7                                   | 3.4      |      | ٧                   |

| Digital output voltage         | Vol          | lot=1mA                             | DVccz=Min.     |                                       |          | 0.5  | V                   |

| Leak current during output off | loz          | DVccz=Max., Vo=3.6V (Max.)          |                | -20                                   |          | 150  | μА                  |

| Dynamic characteristics        |              |                                     |                | <del></del>                           |          |      |                     |

| Differential gain error        | DG           | NTSC 40IRE mod ramp,<br>Fc=14.3MSPS |                |                                       | 0.5      |      | %                   |

| Differential phase error       | DP           |                                     |                |                                       | 0.3      |      | deg                 |

|                                |              | Fc=33MSPS F                         | Fin=1kHz       | 1 1                                   | 57       |      | _ <del></del><br>₫B |

| SNR                            | SNR          | Fc=33MSPS                           | 1MHz           |                                       | 53       |      | dB                  |

|                                |              | Fc=33MSPS F                         | Fin=8MHz       |                                       | 50       |      | dB                  |

| Item                                                                         | Symbol             | Measurement Conditions | Min.  | Тур.    | Max.  | Unit |

|------------------------------------------------------------------------------|--------------------|------------------------|-------|---------|-------|------|

| Power supply                                                                 |                    | <u> </u>               |       | <b></b> |       |      |

| DVcc1 current                                                                | I== .              | DVcc1=5V               | 9     | 20      | 30    | mA   |

| Dvcci current                                                                | lovec <sub>1</sub> | *7 During power save   | 7.5   | 14.5    | 21.5  | mA   |

| DVcc2 current                                                                | laura              | DVcc2=5V               | 0.001 | 0.3     | 1     | mA   |

| DVCC2 current                                                                | lovcc2             | *7 During power save   | 0     | 0       | 0.1   | mA   |

| AVEE current + DVEE current                                                  | luss               | AVEE=-5V, DVEE=-5V     | -57.5 | -38     | -20.8 | mA   |

| Avee corrent + Dvee corrent                                                  | IVEE               | *7 During power save   | -4.4  | -2.8    | -1.6  | mA   |

| AVF current                                                                  | lave               | AVF=0.7V               | 3.5   | 6.8     | 10.5  | mA   |

| Avi cuiteit                                                                  | IAVF               | *7 During power save   | 30    | 55      | 85    | μА   |

| Power dissipation Pd=A+B+C<br>A=(lbvcc1+lbvcc2+ lvEE ) × 5V<br>B=lavF × 0.7V | Pd                 |                        | 178   | 316     | 482   | mW   |

| C= IREF  × 2V                                                                |                    | *7 During power save   | 59    | 107     | 163   | mW   |

- \*1 CLK input

- \*2 MINV, LINV, ENABLE, and PS inputs

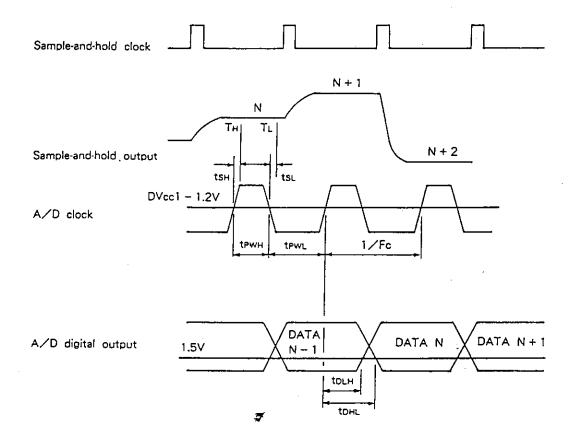

- \*3 Refer to Timing Diagram (1)

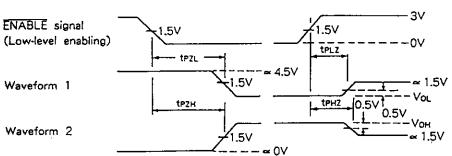

- \*4 Refer to Timing Diagram (2)

- \*5 The load is a bi-state totem-pole output delay time test load circuit.

- \*6 The load is a 3-state output test load circuit.

- \*7 When PS and ENABLE inputs are in high level.

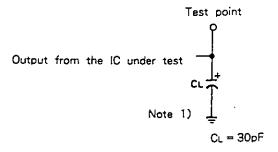

# Bi-state Totem-pole Output Delay Time Test Load Circuit

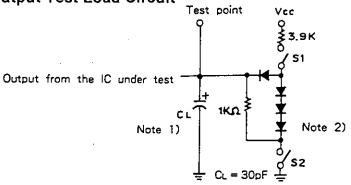

3-state Output Test Load Circuit

| Test condition | S1    | S2    |

|----------------|-------|-------|

| tpzl_          | Close | Open  |

| tрzн           | Open  | Close |

| tpuz<br>tpuz   | Close | Close |

Note 1) CL includes probe capacitance and parasitic capacitance in Test Board.

Note 2) All diodes are IS2076.

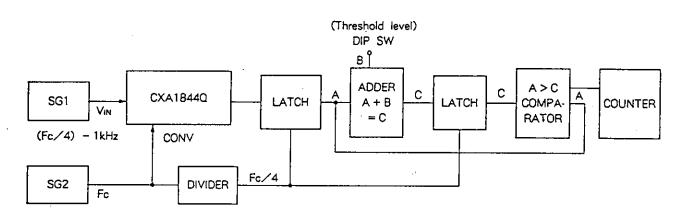

## **Error Rate Test Circuit**

# Notes on Operation

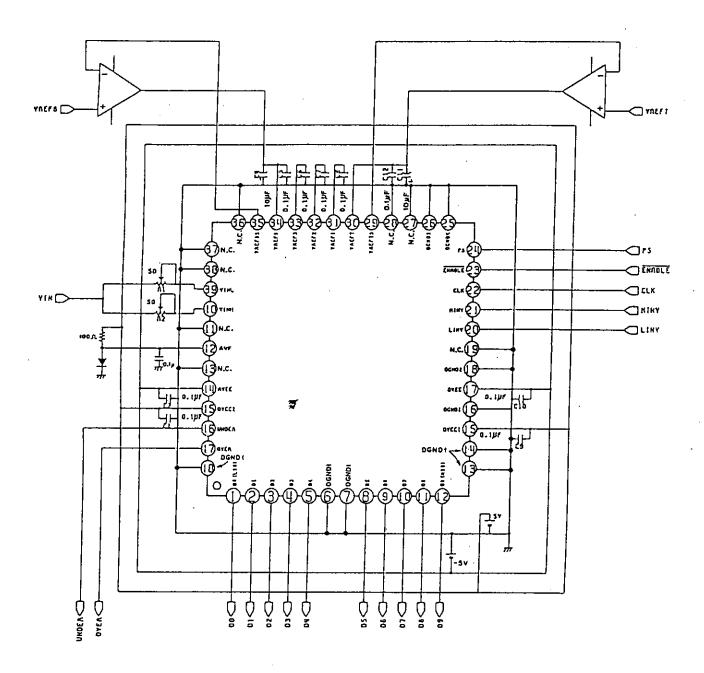

Analog ground (Analog ground on PCB)

Keep analog ground surface on PCB as wide as possible with impedance and resistance as low as possible.

# 2. Digital ground (DGND1, DGND2, DGND3, DGND4)

Upon mounting to PCB keep ground surface as wide as possible with impedance and resistance as low as possible.

Moreover, a common analog and digital ground immediately near ADC will help obtain characteristics smoothly.

# 3. Digital positive power supply (DVcc1, DVcc2)

Connect to the digital ground with a ceramic capacitor over 0.1 µF and as close to the pins as possible. Insert a ceramic capacitor between DVcc2 and DGND1 of TTL output power supply as shortly as possible because noise tends to occur.

# 4. Analog positive power supply (AVF)

As shown in the Standard Circuit, make the positive power supply about +0.7V by connecting to the analog ground with a diode and +5V with a pull-up resister respectively.

Connect to the analog ground on PCB with a ceramic capacitor over 0.1 µF as close to the pin as possible.

# 5. Analog negative power supply (AVEE)

Connect to the analog ground on PCB with a ceramic capacitor over 0.1 µF as close to the pin as possible.

# 6. Digital negative power supply (DVEE)

Connect to the digital ground with a ceremic capacitor over 0.1 µF as close to the pin as possible.

When VEE is divided into digital and analog, there is continuity because of about  $4\Omega$  resistance between the two inside the IC. Accordingly, if an excessive potential difference (more than 100mV) is applied continuously, this may destroy the IC. To prevent the IC destruction, connect AVEE and DVEE with a inductance having good high frequency characteristics. Prevent noise mixing and the generation of potential difference between analog and digital.

# 7. Reference voltage (VREFTS, VREF1, VREF1, VREF2, VREF3, VREFB, VREFBS)

These pins provide reference voltage to upper and lower comparators. Voltage between VREFT and VREFB corresponds to input dynamic range.

There is a  $200\Omega$  resistance between VREFT and VREFB. By applying 2V to both pins a current of about 10 mA flows. When the reference voltage is destabilized by the clock, ADC characteristics are adversely affected. Connect VREFT and VREFB to the analog ground on PCB by means of a tantalum capacitor over  $10\,\mu\text{F}$  and a ceramic capacitor over  $0.1\,\mu\text{F}$  respectively. Also, connect each of VREF1, VREF2 and VREF3 to the analog ground on PCB using a ceramic capacitor over  $0.1\,\mu\text{F}$ . This will provide stability to the characteristics of high frequency. Strictly speaking on reference voltage VREFT side and VREFB side there is a respective about 10mV offset.

When there is no problem with the usage of those offset voltages, voltage is applied directly to VREFT, VREFB. In case the reference voltage is to be strictly applied, adjust to obtain an offset voltage of 0V, keeping VREFTS and VREFBS as sense pins and VREFB as force pins to form a feedback loop circuit. For details, see the Standard Circuit.

#### 8. Analog input (VINH, VINL)

VINH is the input pin for the upper comparator while VINL is the input pin for the lower comparator.

Keep the input signal level within the level between VREFT and VREFB.

As this IC's analog input capacitance stands at about 50pF, it is necessary to drive with an buffer amplifier having sufficient driving capability. Also, when driving is done with the buffer amplifier of a low output impedance, as A/D converter input capacitance is large, ringing is generated and settling time grows longer. Here a small resistance of about 5 to  $30\Omega$  is connected in series between the buffer amplifier and each of A/D converter's VINH and VINL, as a dumping resistance. This eliminates ringing and shortens settling time. Also keep wiring between buffer amplifier and A/D converter as short as possible.

#### Clock input (CLK)

ECL LIKE input. Adds the signal of Vcc1 (5V) –0.8V at high level and Vcc1 (5V) –1.6V at low level. Clock line wiring should be the shortest possible while distanced from other signal lines to avoid affecting them.

This IC is 2-step parallel type A/D converter. Accordingly an external sample-and-hold circuit (SH) is necessary. However the timing between this SH circuit output waveform (A/D converter analog input waveform) and the A/D converter clock timing requires attention. In the relation between A/D converter clock and the A/D converter analog input signal, with the timing TH of the rising edge of A/D converter clock, the upper comparator compares the input signal and the reference voltage to latch the results. After that, with the timing TL of the falling edge of A/D converter clock, the lower comparator compares the input signal and reference signal to latch the results. (Strictly speaking, the sampling delay tsh is in TH and the sampling delay tsl is in TL.)

In this A/D converter, the lower comparator features a length of ±32mV (±16 LSB) redundance in relation to the upper comparator. At the timing when the lower comparator compares input signal and reference signal to latch at the timing TL, it is necessary to have the SH output settling performed. But at the timing when the upper comparator compares input signal and reference voltage to latch at the timing TH, as long as the SH output is within the ±32mV range to the final settling value, digital correction applies, A/D conversion precisely occurs. As seen from the above, A/D converter clock rise and fall timing versus SH output waveform should be duly considered. For the clock high level time tpwH and low level time tpwL, set to a value in excess of the time indicated for the respective operating conditions.

Output data is synchronously with the clock rising edge.

For details on timing, refer to the Timing Chart.

#### 10. MINV input (MINV)

Digital output polarity inversion control pin of D9 (MSB).

TTL input. At open, turns to high level input.

For correspondence with analog input voltage and output data code, refer to the Output Formula Chart.

### 11. LINV input (LINV)

Digital output polarity inversion control pin of D8 to D0 (LSB).

TTL input. At open, turns to high level input.

For correspondence with analog input voltage and output data code, refer to the Output Formula Chart.

#### 12. Output enable (ENABLE)

3-state control pin of digital output (D0 to D9, UNDER, OVER)

TTL input. At open, turns to high level input. At that time digital output turns all to high impedance.

#### 13. Power save input (PS)

Power save control pin of internal circuit.

TTL input. At open, turns to high level input.

To set to power save mode, turn both PS and ENABLE to high level input.

### 14. Digital output (D0 to D9)

Output pin of D9 (MSB) to D0 (LSB).

TTL output.

Output data polarity inversion is executed by means of MINV and LINV signals. Can output in binary, 1S complement and 2S complement.

Also, by turning ENABLE signal to high level, the output can be turned into high impedance output.

However, when the output level is for high impedance output or is in power save mode, the voltage of 3.6V or more must not be applied to prevent the distruction of IC.

For correspondence with analog input voltage and output data code, refer to the Output Formula Chart. For the timing, refer to the Timing Chart.

#### 15. Overflow output (OVER)

When the input signal exceeds VREFT, overflow signal is output.

MINV and LINV have no effect on this pin.

Also by turning ENABLE signal to high level, the output can be turned into high impedance output.

However, when the output level is for high impedance output or is in power save mode, the voltage of 3.6V or more must not be applied to prevent the distruction of IC.

For correspondence with analog input voltage and output data code, refer to the Output Formula Chart.

For the timing, refer to the Timing Chart.

## 16. Underflow output (UNDER)

When the input signal turns below VREFB, underflow signal is output.

MINV and LINV have no effect on this pin.

Also by turning ENABLE signal to high level, the output can be turned into high impedance output.

However, when the output level is for high impedance output or is in power save mode, the voltage of 3.6V or more must not be applied to prevent the sistruction of IC.

For correspondence with analog input voltage and output data code, refer to the Output Formula Chart.

For the timing, refer to the Timing Chart.

| Chart |

|-------|

| ā     |

| ᅩ     |

| ပ     |

| Ø     |

| Ξ     |

| Ē     |

| orm   |

| 6     |

| -     |

| 5     |

| Ω     |

| utp   |

| ō     |

|             |           | ,——      |                               |              |              |              |              |     |               |     |               |              |               |              |              |

|-------------|-----------|----------|-------------------------------|--------------|--------------|--------------|--------------|-----|---------------|-----|---------------|--------------|---------------|--------------|--------------|

| 1<br>(OPEN) |           |          |                               | 7            | 7            | Z            | 7            |     | 2             |     | Z             | 7            | z             | Z            | Z            |

| 0           | 0         | 0        | 0F9876543210UF<br>(MSB) (LSB) | 11111111110  | 011111111100 | 011111111010 | 01111111000  |     | 001111111110  |     | 000000001000  | 00000000110  | 0000000000000 | 00000000010  | 000000000000 |

| 0           | 0         | 1 (OPEN) | 0F9876543210UF<br>(MSB)       | 110000000000 | 0100000010   | 01000000100  | 01000000110  |     | 0000000000000 | ••• | 001111110110  | 001111111000 | 001111111010  | 001111111100 | 001111111111 |

| 0           | 1 (OPEN)  | 0        | 0F9876543210UF<br>(MSB) (LSB) | 10111111110  | 00111111100  | 001111111010 | 001111111000 |     | 01111111110   | ••• | 01000001000   | 01000000110  | 01000000100   | 01000000010  | 010000000001 |

| 0           | 1 (OPEN)  | 1 (OPEN) | 0F9876543210UF<br>(MSB) (LSB) | 100000000000 | 00000000000  | 00000000100  | 00000000110  | ••• | 010000000000  | ••• | 0111111110110 | 011111111000 | 011111111010  | 01111111100  | 01111111111  |

| 3 <u>LE</u> | <b>^!</b> | >        | TUc                           | 0            | -            | 2            | ო            |     | 512           | ••• | 1019          | 1020         | 1021          | 1022         | 1023         |

| ENABLE      | NIM       | TINA     | OUTPUT                        | 8            | •••          |              |              |     |               |     |               |              |               |              | -2V          |

OF: OVER FLOW UF: UNDER FLOW 0: VOLTAGE LEVEL-LOW 1: VOLTAGE LEVEL-HIGH 2: HIGH IMPEDANCE

# Timing Chart (1)

TH is the timing of latching result for the comparator of VIN and VREF in the upper comparators. TL is the timing of latching result for the comparator of VIN and VREF in the lower comparators.

# Timing Chart (2)

Output waveform of 3-state enable and disable time \*. (\* Enable time=tpzL/tpzH, disable time=tptz/tpHz)

**Notes)** Waveform 1 indicates the output waveform when internal conditions are set to obtain a low level output, with the exception of when output is disabled by means of the **ENABLE** signal.

Ø

Waveform 2 indicates the output waveform when internal conditions are set to obtain a high level output, with the exception of when output is disabled by means of the ENABLE signal.

# Standard Circuit

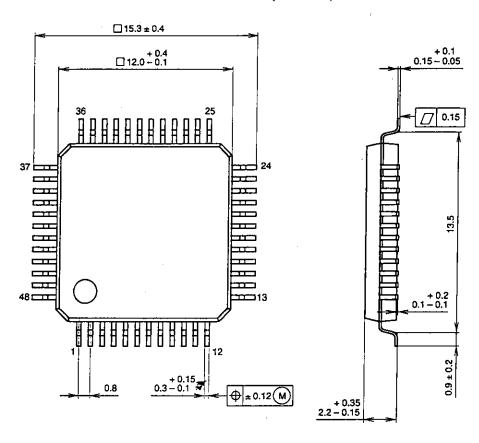

**Package Outline**

Unit: mm

# 48PIN QFP (PLASTIC)

## PACKAGE STRUCTURE

| SONY CODE  | QFP-48P-L04      |

|------------|------------------|

| EIAJ CODE  | -QFP048-P-1212-8 |

| JEDEC CODE |                  |

| PACKAGE MATERIAL | EPOXY RESIN                   |

|------------------|-------------------------------|

| LEAD TREATMENT   | SOLDER / PALLADIUM<br>PLATING |

| LEAD MATERIAL    | COPPER / 42 ALLOY             |

| PACKAGE WEIGHT   | 0.7g                          |

**NOTE: PALLADIUM PLATING**

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).