# SONY

# LCX038AST

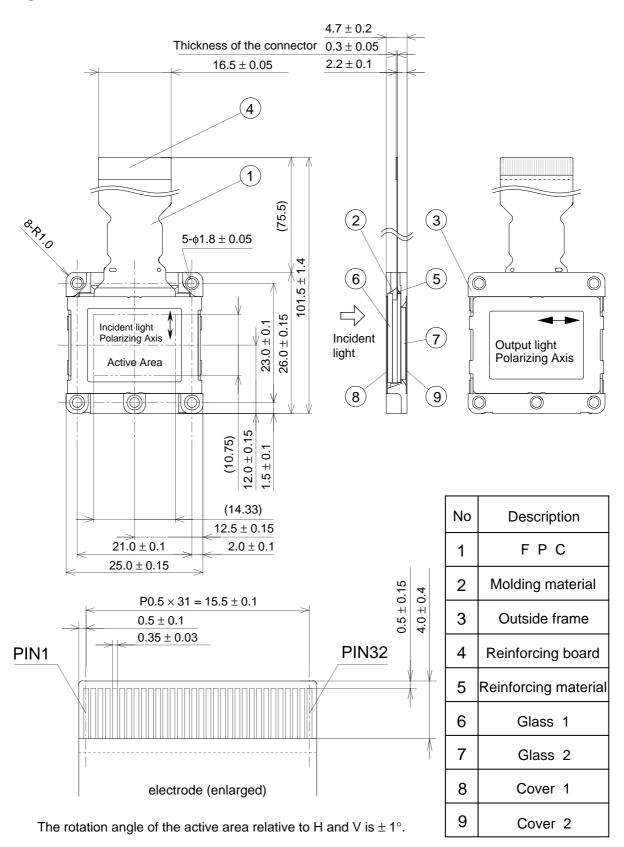

# 1.8cm (0.7 Type) Black-and-White LCD Panel

#### Description

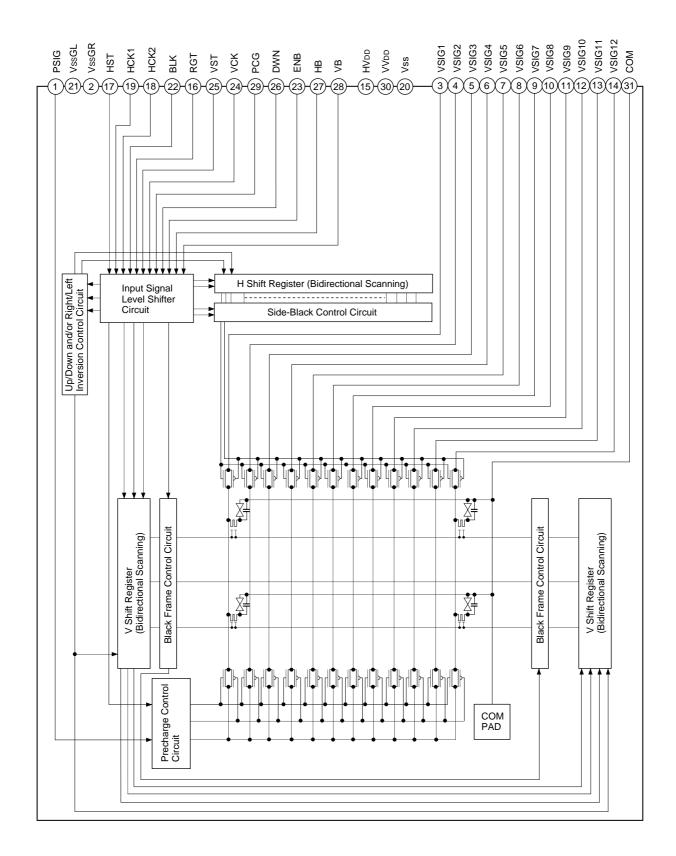

The LCX038AST is a 1.8cm diagonal active matrix TFT-LCD panel addressed by polycrystalline silicon super thin film transistors with a built-in peripheral driving circuit. Use of three LCX038AST panels provides a full-color representation. The striped arrangement suitable for data projectors is capable of displaying fine text and vertical lines.

The adoption of DMS<sup>\*1</sup> structure and high light resistance structure realize a high luminance screen. And cross talk free circuit and ghost free circuit contribute to high picture quality.

This panel has a polysilicon TFT high-speed scanner and built-in function to display images up/down and/or right/left inverse. The built-in 5V interface circuit leads to lower voltage of timing and control signals.

The panel contains an active area variable circuit which supports S-XGA 5:4 and PC-98 8:5 data signals by changing the active area according to the type of input signal.

\*1 Dual Metal Shield

#### Features

- Number of active dots: 786,432 (0.7 Type, 1.8cm in diagonal)

- XGA, SVGA, VGA, NTSC, PAL display

- SXGA display with simple display

- High optical transmittance: 21% (typ.)

- · Built-in cross talk free circuit and ghost free circuit

- High contrast ratio with normally white mode: 350 (typ.)

- Built-in H and V drivers (built-in input level conversion circuit, 5V driving possible)

- Up/down and/or right/left inverse display function

- Antidust glass package

- Left twist liquid crystal

#### **Element Structure**

- Dots: 1024 (H) × 768 (V) = 786,432

- · Built-in peripheral driver using polycrystalline silicon super thin film transistors

#### Applications

- Liquid crystal data projectors

- · Liquid crystal multimedia projectors

- Liquid crystal rear-projector TVs, etc.

\* The company's name and product's name in this data sheet is a trademark or a registered trademark of each company.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

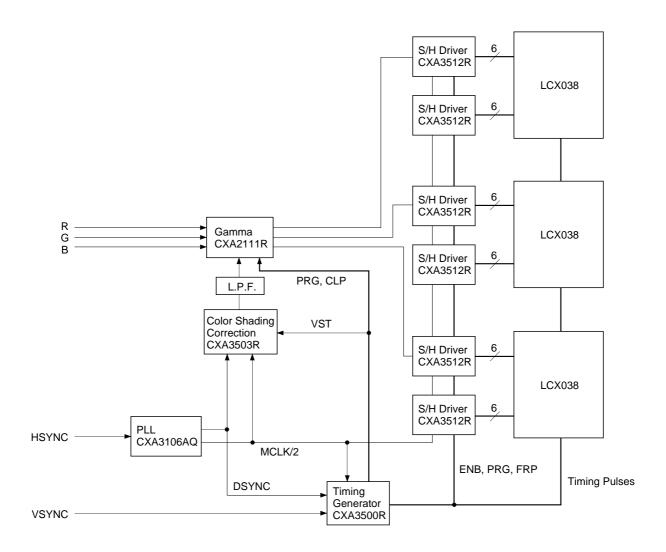

#### **Block Diagram**

# Absolute Maximum Ratings (Vss = 0V)

| <ul> <li>H driver supply voltage</li> </ul>        | HVdd                    | -1.0 to +20 | V  |

|----------------------------------------------------|-------------------------|-------------|----|

| <ul> <li>V driver supply voltage</li> </ul>        | VVdd                    | -1.0 to +20 | V  |

| <ul> <li>Common pad voltage</li> </ul>             | COM                     | -1.0 to +17 | V  |

| • H shift register input pin voltage               | HST, HCK1, HCK2,<br>RGT | -1.0 to +17 | V  |

| • V shift register input pip voltage               | VST, VCK, PCG,          | -1.0 to +17 | V  |

| V shift register input pin voltage                 | BLK, ENB, DWN           | -1.0 10 +17 | v  |

|                                                    | HB, VB                  |             |    |

| <ul> <li>Video signal input pin voltage</li> </ul> | VSIG1 to 12, PSIG       | -1.0 to +15 | V  |

| <ul> <li>Operating temperature*</li> </ul>         | Topr                    | -10 to +70  | °C |

| <ul> <li>Storage temperature</li> </ul>            | Tstg                    | -30 to +85  | °C |

|                                                    |                         |             |    |

\* Panel temperature inside the antidust glass

## **Operating Conditions (Vss = 0V)**

- Supply voltage

- HVDD 13.5 ± 0.5V

- VVDD  $15.5 \pm 0.5V$

- Input pulse voltage (Vp-p of all input pins except video signal and uniformity improvement signal input pins)

Vin 5.0 ± 0.5V

# **Pin Description**

| Pin<br>No. | Symbol | Description                                                        |

|------------|--------|--------------------------------------------------------------------|

| 1          | PSIG   | Uniformity improvement signal                                      |

| 2          | VssGR  | GND for right V gate                                               |

| 3          | VSIG1  | Video signal 1 to panel                                            |

| 4          | VSIG2  | Video signal 2 to panel                                            |

| 5          | VSIG3  | Video signal 3 to panel                                            |

| 6          | VSIG4  | Video signal 4 to panel                                            |

| 7          | VSIG5  | Video signal 5 to panel                                            |

| 8          | VSIG6  | Video signal 6 to panel                                            |

| 9          | VSIG7  | Video signal 7 to panel                                            |

| 10         | VSIG8  | Video signal 8 to panel                                            |

| 11         | VSIG9  | Video signal 9 to panel                                            |

| 12         | VSIG10 | Video signal 10 to panel                                           |

| 13         | VSIG11 | Video signal 11 to panel                                           |

| 14         | VSIG12 | Video signal 12 to panel                                           |

| 15         | HVdd   | Power supply for H driver                                          |

| 16         | RGT    | Drive direction pulse for H shift register (H: normal, L: reverse) |

| 17         | HST    | Start pulse for H shift register drive                             |

| 18         | HCK2   | Clock pulse for H shift register drive 2                           |

| 19         | HCK1   | Clock pulse for H shift register drive 1                           |

| 20         | Vss    | GND (H, V drivers)                                                 |

| 21         | VssGL  | GND for left V gate                                                |

| 22         | BLK    | Input for PC98 mode                                                |

| 23         | ENB    | Enable pulse for gate selection                                    |

| 24         | VCK    | Clock pulse for V shift register drive                             |

| 25         | VST    | Start pulse for V shift register drive                             |

| 26         | DWN    | Drive direction pulse for V shift register (H: normal, L: reverse) |

| 27         | HB     | Display switch for S-XGA                                           |

| 28         | VB     | Display switch for PC98 mode                                       |

| 29         | PCG    | Improvement pulse for uniformity                                   |

| 30         | VVdd   | Power supply for V driver                                          |

| 31         | СОМ    | Common voltage of panel                                            |

| 32         | TEST   | Test pin, leave this pin open                                      |

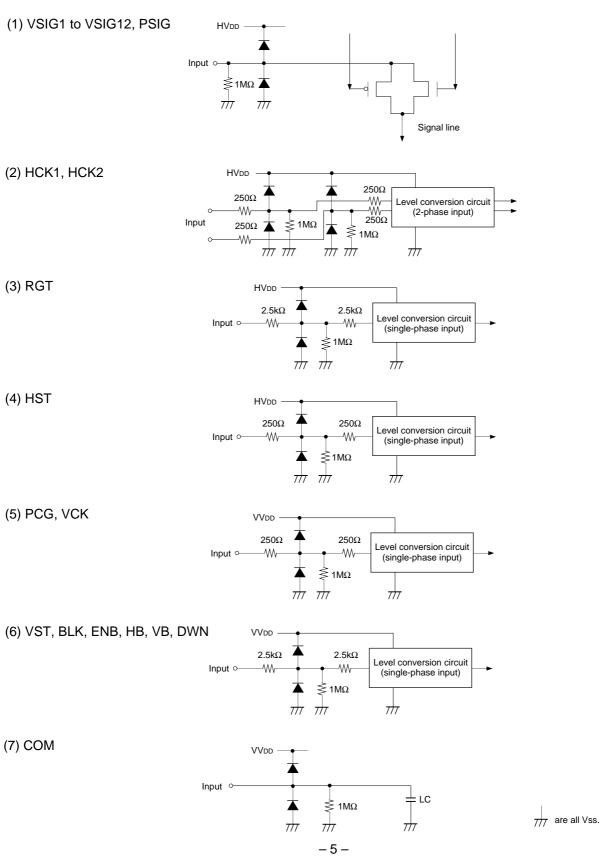

#### Input Equivalent Circuit

To prevent static charges, protective diodes are provided for each pin except the power supplies. In addition, protective resistors are added to all pins except the video signal inputs. All pins are connected to Vss with a high resistor of  $1M\Omega$  (typ.). The equivalent circuit of each input pin is shown below: (Resistance value: typ.)

## **Input Signals**

| Item                                    |        | Symbol | Min.      | Тур.      | Max.      | Unit |

|-----------------------------------------|--------|--------|-----------|-----------|-----------|------|

| H shift register input voltage          | (Low)  | VHIL   | -0.5      | 0.0       | 0.4       | V    |

| HST, HCK1, HCK2, RGT                    | (High) | VHIH   | 4.5       | 5.0       | 5.5       | V    |

| V shift register input voltage          | (Low)  | VVIL   | -0.5      | 0.0       | 0.4       | V    |

| HB, VB, BLK, VST, VCK,<br>PCG, ENB, DWN | (High) | VVIH   | 4.5       | 5.0       | 5.5       | V    |

| Video signal center voltage             |        | VVC    | 7.4       | 7.5       | 7.6       | V    |

| Video signal input range*1              |        | Vsig   | VVC – 5.0 | 7.0       | VVC + 5.0 | V    |

| Common voltage of panel*                | 2      | Vcom   | VVC - 0.5 | VVC - 0.4 | VVC - 0.3 | V    |

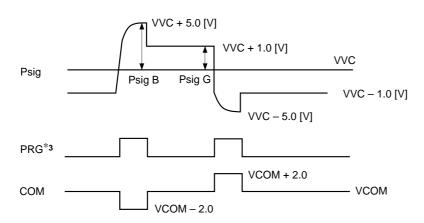

| Uniformity improvement sig              | Inal   | VpsigB | VVC ± 4.9 | VVC ± 5.0 | VVC ± 5.1 | V    |

| input voltage (PSIG)*3                  |        | VpsigG | VVC ± 1.8 | VVC ± 1.9 | VVC ± 2.0 | V    |

#### 1. Input signal voltage conditions (Vss = 0V)

\*1 Input video signal shall be symmetrical to VVC.

\*2 The typical value of the common pad voltage may lower its suitable voltage according to the set construction to use. In this case, use the voltage of which has maximum contrast as typical value. When the typical value is lowered, the maximum and minimum values may lower.

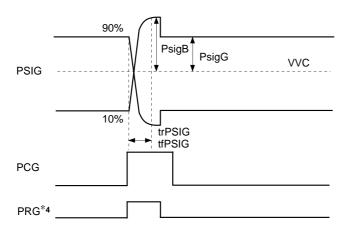

\*3 Input a uniformity improvement signal PSIG in the same polarity with video signals VSIG1 to VSIG12 and which is symmetrical to VVC. PSIG wave form is 2 steps like below, in the upper chart, upper shows signal level of the 1st step, lower shows signal level of the 2nd step. Also, the rising and falling of PSIG are synchronized with the rising of PCG pulse, and the rise time trPSIG and fall time tfPSIG are suppressed within 450ns (as shown in a diagram below).

The optimum input voltage of PSIG may be changed according as drive conditions of the drive side.

#### Input waveform of uniformity improvement signal PSIG

<sup>\*4</sup> PRG shows the time of the 1st step of PSIG signal, and it is not input to the panel.

#### **Level Conversion Circuit**

The LCX038AST has a built-in level conversion circuit in the clock input unit on the panel. The input signal level increases to HVDD or VVDD. The Vcc of external ICs are applicable to  $5 \pm 0.5$ V.

# **2. Clock timing conditions** (Ta = $25^{\circ}$ C)

(XGA mode: fHckn = 3.9MHz, fVck = 34.3kHz)

|       |                                                    |         |      |      | 1    | 1    |

|-------|----------------------------------------------------|---------|------|------|------|------|

|       | Item                                               | Symbol  | Min. | Тур. | Max. | Unit |

|       | Hst rise time                                      | trHst   | _    | _    | 30   |      |

| HST   | Hst fall time                                      | tfHst   |      |      | 30   |      |

| 1101  | Hst data set-up time                               | tdHst   | 55   | 65   | 75   |      |

|       | Hst data hold time                                 | thHst   | 55   | 65   | 75   |      |

|       | Hckn rise time <sup>*5</sup>                       | trHckn  | _    | —    | 30   | ns   |

| нск   | Hckn fall time <sup>*5</sup>                       | tfHckn  |      | _    | 30   | 113  |

| TION  | Hck1 fall to Hck2 rise time                        | to1Hck  | -15  | 0    | 15   |      |

|       | Hck1 rise to Hck2 fall time                        | to2Hck  | -15  | 0    | 15   |      |

|       | Vst rise time                                      | trVst   | _    |      | 100  |      |

| VST   | Vst fall time                                      | tfVst   |      |      | 100  |      |

| v31   | Vst data set-up time                               | tdVst   | 2    | 7    | 12   |      |

|       | Vst data hold time                                 | thVst   | 2    | 7    | 12   | - µs |

| VCK   | Vck rise time                                      | trVck   | _    |      | 100  |      |

| VCK   | Vck fall time                                      | tfVck   | _    |      | 100  |      |

|       | Enb rise time                                      | trEnb   |      |      | 100  |      |

|       | Enb fall time                                      | tfEnb   |      |      | 100  | -    |

|       | Horizontal video period completed to Enb fall time | tdEnb   | 760  | 800  |      |      |

| ENB   | Enb rise to PRG <sup>*4</sup> fall time            | toPRG*4 | 110  | 120  | 130  |      |

|       | Enb fall to Pcg rise time                          | toPcg   | 830  | 1000 |      |      |

|       | Enb pulse width                                    | twEnb   | 1650 |      |      |      |

|       | Pcg rise time                                      | trPcg   |      |      | 30   |      |

|       | Pcg fall time                                      | tfPcg   |      |      | 30   | ns   |

| PCG   | Pcg rise to Vck rise/fall time                     | toVck   | -100 | 0    | 100  |      |

|       | Pcg fall to horizontal video period start time     | toVideo | 170  | 200  |      |      |

|       | Pcg pulse width                                    | twPcg   | 1400 | 1700 |      |      |

|       | PRG <sup>*4</sup> rise to Pcg rise time            | toPcgr  | -10  | 0    | 10   | ]    |

| PRG*4 | PRG <sup>*4</sup> fall to Pcg fall time            | toPcgf  | 570  | 700  | _    | ]    |

|       | PRG <sup>*4</sup> pulse width                      | twPRG*4 | 830  | 1000 | _    | ]    |

|       | Blk rise time                                      | trBlk   |      |      | 100  |      |

| BLK*6 | Blk fall time                                      | tfBlk   |      | _    | 100  | ]    |

| DLV.  | Blk rise to Enb fall time                          | toEnb   | 2    | 1    | 0    |      |

|       | Blk fall to Pcg rise time                          | toPcg   | -1   | 0    | 1    | μs   |

\*5 Hckn means Hck1 and Hck2.

$^{*6}$  Blk is the timing during PC98 mode, which keeps "H" level in other modes.

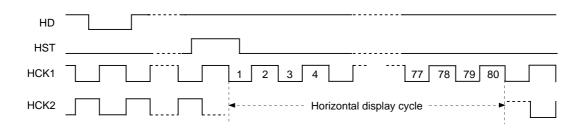

# <Horizontal Shift Register Driving Waveform>

|        | Item                         | Symbol | Waveform                        | Conditions                             |

|--------|------------------------------|--------|---------------------------------|----------------------------------------|

|        | Hst rise time                | trHst  | Hst 10%                         | Hckn <sup>*5</sup> duty cycle 50%      |

|        | Hst fall time                | tfHst  | trHst tfHst                     | to1Hck = 0ns<br>to2Hck = 0ns           |

| HST    | Hst data set-up time         | tdHst  | *7<br>Hst                       | • Hckn*5<br>duty cycle 50%             |

| Hst da | Hst data hold time           | thHst  | Hck1<br>tdHst thHst             | to1Hck = 0ns<br>to2Hck = 0ns           |

|        | Hckn rise time <sup>*5</sup> | trHckn | 90%<br>*5<br>Hckn<br>90%<br>10% | • Hckn <sup>*5</sup><br>duty cycle 50% |

|        | Hckn fall time <sup>*5</sup> | tfHckn | trHckn tfHckn                   | to1Hck = 0ns<br>to2Hck = 0ns           |

| НСК    | Hck1 fall to Hck2 rise time  | to1Hck | *7 50%<br>Hck1 50%              |                                        |

|        | Hck1 rise to Hck2 fall time  | to2Hck | Hck2<br>to2Hck to1Hck           |                                        |

\*7 Definitions: The right-pointing arrow ( •• ) means +.

The left-pointing arrow (  $\checkmark$  ) means –.

The black dot at an arrow ( • ) indicates the start of measurement.

# <Vertical Shift Register Driving Waveform>

|     | Item                                                  | Symbol  | Waveform                                            | Conditions |

|-----|-------------------------------------------------------|---------|-----------------------------------------------------|------------|

|     | Vst rise time                                         | trVst   | 90% 90%                                             |            |

|     | Vst fall time                                         | tfVst   | Vst 10%                                             |            |

| VST | Vst data set-up time                                  | tdVst   | *7 50%<br>Vst 50% 50%                               |            |

|     | Vst data hold time                                    | thVst   | Vck                                                 |            |

| VCK | Vck rise time                                         | trVck   | 90%<br>90%<br>10%<br>90%                            |            |

|     |                                                       | tfVck   | trVck tfVck                                         |            |

|     | Enb rise time                                         | trEnb   | 90% 10% 10% 90%                                     |            |

|     | Enb fall time                                         | tfEnb   | Enb<br>tfEnb trEnb                                  |            |

| ENB | Horizontal video period<br>completed to Enb fall time | tdEnb   | H. Video period H. Blanking period                  |            |

|     | Enb rise to PRG <sup>*4</sup> fall time               | toPRG*4 |                                                     |            |

|     | Enb fall to Pcg rise time                             | toPcg   | PRG <sup>*4</sup> tdEnb 50% 50% toPRG <sup>*4</sup> |            |

|     | Enb pulse width                                       | twEnb   | PCG/ 50%                                            |            |

|                   | Item                                           | Symbol  | Waveform                              | Conditions |

|-------------------|------------------------------------------------|---------|---------------------------------------|------------|

|                   | Pcg rise time                                  | trPcg   | Pcg 10%                               |            |

|                   | Pcg fall time                                  | tfPcg   | trpcg tfpcg                           |            |

| PCG <sup>*8</sup> | Pcg rise to Vck rise/fall<br>time              | toVck   | *7 H. blanking period H. video period |            |

|                   | Pcg fall to horizontal video period start time | toVideo | Pcg 50% 50%<br>toVck                  |            |

|                   | Pcg pulse width twPcg                          | Vck 50% |                                       |            |

|                   | PRG <sup>*4</sup> rise to Pcg rise time        | toPcgr  | *7 twPRG <sup>*4</sup> toPcgf         |            |

| *8<br>PRG*4       | PRG <sup>*4</sup> fall to Pcg fall time        | toPcgf  | PRG <sup>*4</sup> 50% 50%             |            |

|                   | PRG*4 pulse width                              | twPRG*4 | Pcg 50%                               |            |

|                   | Blk rise time                                  | trBlk   | tfBlk trBlk                           |            |

|                   | Blk fall time                                  | tfBlk   | 90%                                   |            |

| BLK               | Blk rise to Enb fall time                      | toEnb   | *7 toPcg toEnb                        |            |

|                   | Blk fall to Pcg rise time                      | toPcg   | Pcg50%                                |            |

\*8 PCG input pin and PRG\*4 should be "H" level during the horizontal 1H period, where the above BLK is low more than 10ns.

# **Electrical Characteristics** (Ta = $25^{\circ}$ C, HVDD = 13.5V, VVDD = 15.5V)

#### 1. Horizontal drivers

| ltem                      |            | Symbol | Min.  | Тур. | Max. | Unit | Condition                 |

|---------------------------|------------|--------|-------|------|------|------|---------------------------|

| Input pin capacitance     | HCKn       | CHckn  | _     | 15   | 20   | pF   |                           |

|                           | HST        | CHst   | —     | 15   | 20   | pF   |                           |

| Input pin current         | HCK1       |        | -500  | -200 | _    | μA   | HCK1 = GND                |

|                           | HCK2       |        | -1000 | -300 | _    | μA   | HCK2 = GND                |

|                           | HST        |        | -500  | -150 | _    | μA   | HST = GND                 |

|                           | RGT        |        | -150  | -40  |      | μA   | RGT = GND                 |

| Video signal input pin ca | apacitance | Csig   | _     | 50   | 200  | pF   |                           |

| Current consumption       |            | IH     |       | 10.0 | 15.0 | mA   | HCKn: HCK1, HCK2 (3.9MHz) |

#### 2. Vertical drivers

| Item                          |          | Symbol | Min.  | Тур. | Max. | Unit | Condition                           |

|-------------------------------|----------|--------|-------|------|------|------|-------------------------------------|

| Input pin capacitance         | VCK      | CVck   |       | 15   | 20   | pF   |                                     |

|                               | VST      | CVst   | _     | 15   | 20   | pF   |                                     |

| Input pin current             | VCK, PCG |        | -1000 | -150 | _    | μA   | VCK = GND, PCG = GND                |

| VST, ENB, DWN, BLK, HB,<br>VB |          |        | -150  | -30  |      | μA   | VST, ENB, DWN, BLK, HB,<br>VB = GND |

| Current consumption           |          | IV     |       | 3.0  | 6.0  | mA   | VCK: (34.3kHz)                      |

# 3. Total power consumption of the panel

| Item                                 | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------------|--------|------|------|------|------|

| Total power consumption of the panel | PWR    | —    | 200  | 350  | mW   |

#### 4. Pin input resistance

| Item                       | Symbol | Min. | Тур. | Max. | Unit |

|----------------------------|--------|------|------|------|------|

| Pin – Vss input resistance | Rpin   | 0.4  | 1    | _    | MΩ   |

# 5. Uniformity improvement signal

| Item                                                    | Symbol | Тур.   | Max. | Unit |

|---------------------------------------------------------|--------|--------|------|------|

| Input pin capacitance for uniformity improvement signal | CPSIGo | <br>11 | 16   | nF   |

#### 6. COM pin capacitance

| Item                | Symbol | Min. | Тур. | Max. | Unit |

|---------------------|--------|------|------|------|------|

| COM pin capacitance | СОМ    |      | 17   | 25   | nF   |

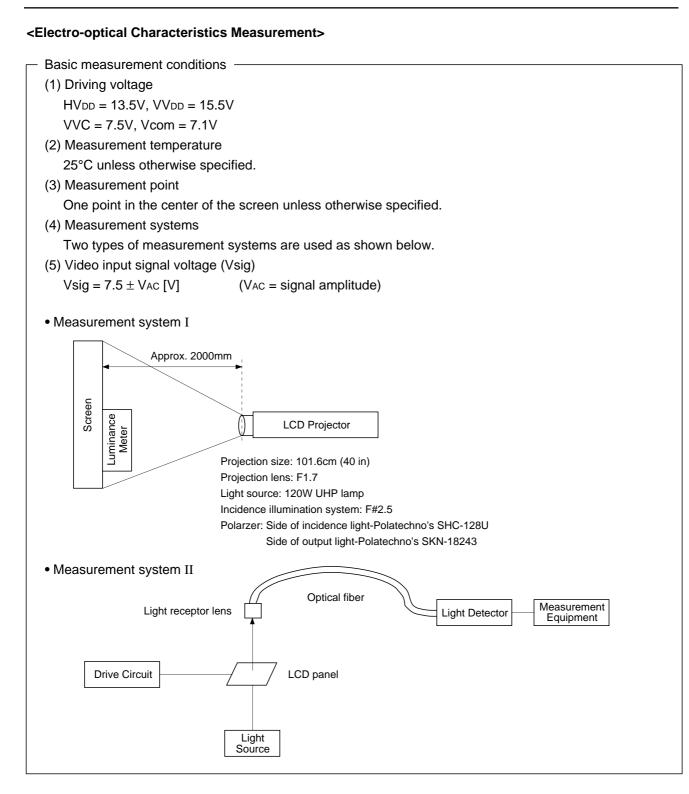

#### **Electro-optical Characteristics**

(XGA mode)

| Item                   |             | Symbol | Measurement method | Min. | Тур. | Max.  | Unit  |    |

|------------------------|-------------|--------|--------------------|------|------|-------|-------|----|

| Contrast ratio         |             | 25°C   | CR                 | 1    | 250  | 350   | —     | —  |

| Optical transmittance  |             | 25°C   | Т                  | 2    | 17   | 21    | _     | %  |

|                        | V90         | 25°C   | RV90-25            | -    | 0.9  | 1.2   | 1.5   |    |

|                        |             |        | GV90-25            |      | 1.0  | 1.3   | 1.6   |    |

|                        |             |        | BV90-25            |      | 1.1  | 1.4   | 1.7   |    |

|                        | <b>V</b> 90 |        | RV90-60            |      | 0.8  | 1.1   | 1.4   |    |

|                        |             | 60°C   | GV90-60            |      | 0.9  | 1.2   | 1.5   |    |

|                        |             |        | BV90-60            |      | 1.0  | 1.3   | 1.6   |    |

| V-T<br>characteristics |             |        | RV50-25            |      | 1.2  | 1.5   | 1.8   |    |

|                        | V50 ·       | 25°C   | GV50-25            | 3    | 1.3  | 1.6   | 1.9   |    |

|                        |             |        | BV50-25            |      | 1.4  | 1.7   | 2.0   |    |

|                        |             | 60°C   | RV50-60            |      | 1.2  | 1.5   | 1.8   |    |

|                        |             |        | GV50-60            |      | 1.3  | 1.6   | 1.9   |    |

|                        |             |        | BV50-60            |      | 1.4  | 1.7   | 2.0   |    |

|                        | V10         | 25°C   | RV10-25            |      | 1.6  | 1.9   | 2.2   |    |

|                        |             |        | GV10-25            |      | 1.7  | 2.0   | 2.3   |    |

|                        |             |        | BV10-25            |      | 1.8  | 2.1   | 2.4   |    |

|                        |             | 60°C   | RV10-60            |      | 1.6  | 1.9   | 2.2   |    |

|                        |             |        | GV10-60            |      | 1.7  | 2.0   | 2.3   |    |

|                        |             |        | BV10-60            |      | 1.8  | 2.1   | 2.4   |    |

| Response time          | ON time     | 0°C    | ton0               | 4    |      | 28.0  | 80.0  | ms |

|                        |             | 25°C   | ton25              |      |      | 14.0  | 40.0  |    |

|                        | OFF time    | 0°C    | toff0              | 4    |      | 72.0  | 200.0 |    |

|                        |             | 25°C   | toff25             |      |      | 34.0  | 70.0  |    |

| Flicker                |             | 60°C   | F                  | 5    |      | -67.0 | -40.0 | dB |

| Image retention time 2 |             | 25°C   | YT60               | 6    | _    | 0     |       | S  |

| Cross talk 25          |             | 25°C   | СТК                | 7    |      | _     | 5     | %  |

# **Reflection Preventive Processing**

When a phase substrate which rotates the polarization axis is used to adjust to the polarization direction of a polarization screen or prism, use a phase substrate with reflection preventive processing on the surface. This prevents characteristic deterioration caused by luminous reflection.

## 1. Contrast Ratio

Contrast Ratio (CR) is given by the following formula (1).

$$CR = \frac{L \text{ (White)}}{L \text{ (Black)}} \dots (1)$$

L (White): Surface luminance of the center of the screen at the input signal amplitude  $V_{AC} = 0.5V$ .

L (Black): Surface luminance of the center of the screen at VAC = 5.0V.

Both luminosities are measured by System I.

#### 2. Optical Transmittance

Optical Transmittance (T) is given by the following formula (2).

$$T = \frac{\text{White luminance}}{\text{Luminance of light source}} \times 100 \,[\%] \dots (2)$$

"White luminance" means the maximum luminance on the screen at the input signal amplitude  $V_{AC} = 0.5V$  on Measurement System I.

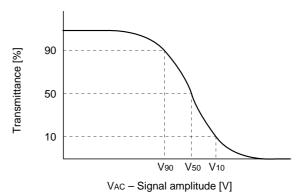

#### 3. V-T Characteristics

V-T characteristics, or the relationship between signal amplitude and the transmittance of the panels, are measured by System II by inputting the same signal amplitude V<sub>AC</sub> to each input pin. V<sub>90</sub>, V<sub>50</sub>, and V<sub>10</sub> correspond to the voltages which define 90%, 50%, and 10% of transmittance respectively.

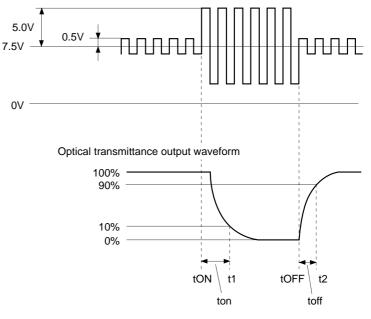

#### 4. Response Time

Response time ton and toff are defined by formulas (3) and (4) respectively.

ton = t1 - tON ...(3)

- toff = t2 tOFF ...(4)t1: time which gives 10% transmittance of the panel.

- t2: time which gives 90% transmittance of the panel.

The relationships between t1, t2, tON and tOFF are shown in the right figure.

Input signal voltage (Waveform applied to the measured pixels)

## 5. Flicker

Flicker (F) is given by formula (5). DC and AC (XGA/NTSC: 30Hz, rms, PAL: 25Hz, rms) components of the panel output signal for gray raster<sup>\*</sup> mode are measured by a DC voltmeter and a spectrum analyzer in System II.

$$F [dB] = 20 \log \left\{ \frac{AC \text{ component}}{DC \text{ component}} \right\} ...(5)$$

\* Each input signal voltage for gray raster mode is given by Vsig = 7.5 ± V<sub>50</sub> [V] where: V<sub>50</sub> is the signal amplitude which gives 50% of transmittance in V-T characteristics.

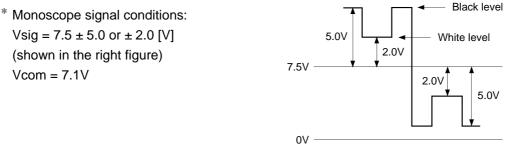

#### 6. Image Retention Time

Apply the monoscope signal to the LCD panel for 60 minutes and then change this signal to the gray scale of Vsig =  $7.5 \pm Vac$  (Vac: 3 to 4V). Judging by sight at the Vac that holds the maximum image retention, measure the time till the residual image becomes indistinct.

Vsig waveform

#### 7. Cross Talk

Cross talk is determined by the luminance differences between adjacent areas represented by Wi' and Wi (i = 1 to 4) around a black window (Vsig = 5.0V/1V).

| W2 W1 | W1' | W4  |

|-------|-----|-----|

| W2'   |     | W4' |

| W3    | W3' |     |

Cross talk value CTK =

$$\left|\frac{Wi' - Wi}{Wi}\right| \times 100$$

[%]

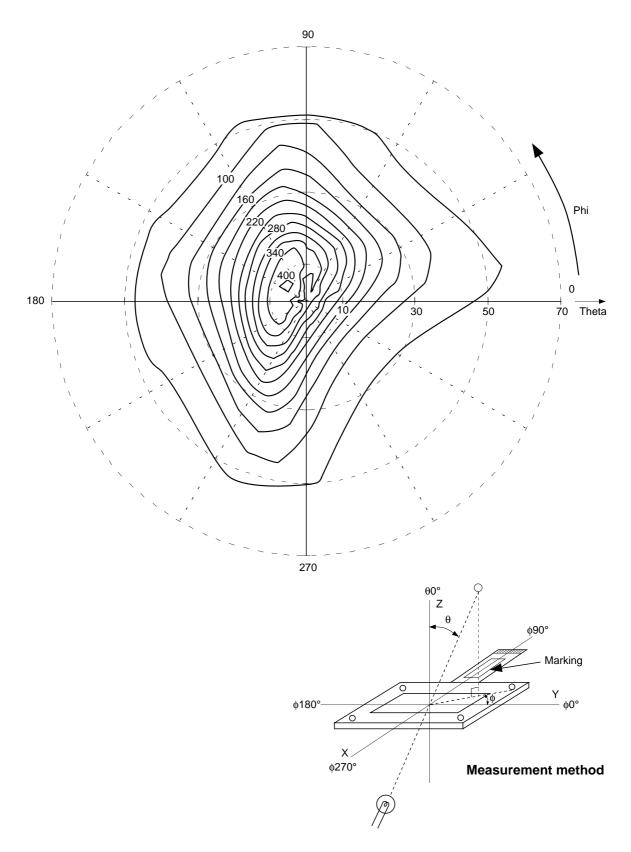

# Viewing angle characteristics (Typical value)

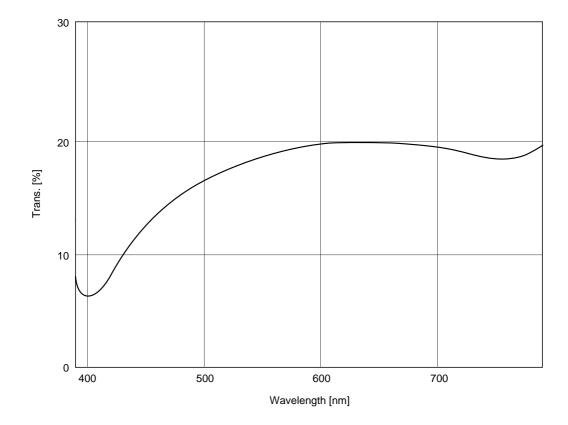

# Optical transmittance of LCD panel (Typical value)

Measurement method: Measurement system II

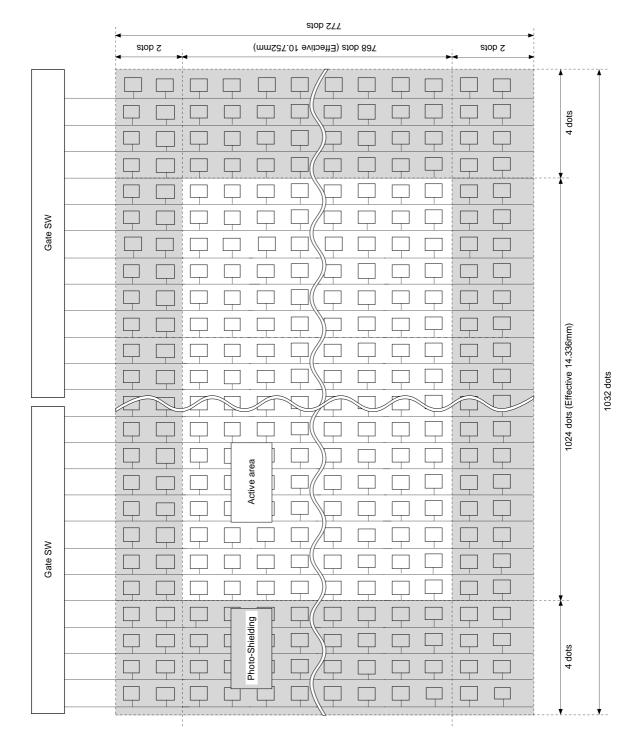

The dots are arranged in a stripe. The shaded area is used for the dark border around the display.

– 18 –

#### 2. LCD Panel Operations

#### [Description of basic operations]

- A vertical driver, which consists of vertical shift registers, enable-gates and buffers, applies a selected pulse to every 768 gate lines sequentially in a single horizontal scanning period. (XGA mode)

- A horizontal driver, which consists of horizontal shift registers, gates and CMOS sample-and-hold circuits, applies selected pulses to every 1024 signal electrodes sequentially in a single horizontal scanning period. These pulses are used to supply the sampled video signal to the row signal lines.

- Vertical and horizontal shift registers address one pixel, and then Thin Film Transistors (TFTs; two TFTs) turn on to apply a video signal to the dot. The same procedures lead to the entire 1024 × 768 dots to display a picture in a single vertical scanning period.

- The data and video signals shall be input with the 1H-inverted system.

#### [Description of operating mode]

This LCD panel can change the active area by displaying a black frame to support various computer or video signals. The active area is switched by HB, VB and BLK. However, the center of the screen is not changed. The active area setting modes are shown below.

| НВ | VB | BLK | Screen aspect ratio        |

|----|----|-----|----------------------------|

| Н  | Н  | Н   | 4:3<br>1024 × 768          |

| L  | Н  | Н   | 5:4* <b>2</b><br>960 × 768 |

| Н  | L  | *1  | 8:5<br>1024 × 640          |

\*1 Input BLK pulse (refer to drive waveform and vertical blanking period of PC98 made).

\*2 For only aspect ratio 5:4 mode, set Psig and COM voltage as shown below. The value of PsigG and COM voltage is typical value. It is necessary to optimize the voltage for each set construction.

\*3 PRG shows the time of the 1st step of Psig signal, and it is not input to the panel.

This LCD panel has the following functions to easily apply to various uses, as well as various broadcasting systems.

- Right/left inverse mode

- Up/down inverse mode

These modes are controlled by two signals (RGT and DWN). The right/left and/or up/down setting modes are shown below.

| RGT | Mode       |

|-----|------------|

| н   | Right scan |

| L   | Left scan  |

| DWN | Mode      |

|-----|-----------|

| Н   | Down scan |

| L   | Up scan   |

Right/left and/or up/down mean the direction when the Pin 1 marking is located at the right side with the pin block upside.

To locate the active area in the center of the panel in each mode, polarity of the start pulse and clock phase for both the H and V systems must be varied. The phase relationship between the start pulse and the clock for each mode is shown below.

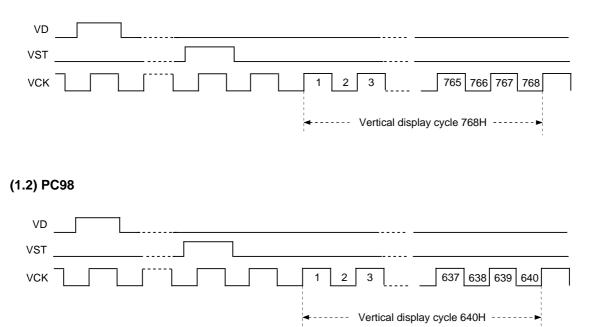

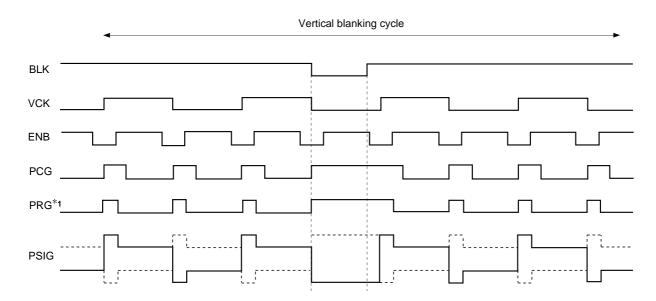

# (1) Vertical direction display cycle (DWN = H, L)

#### (1.1) XGA, SXGA

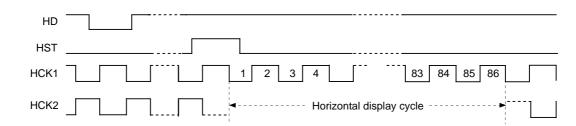

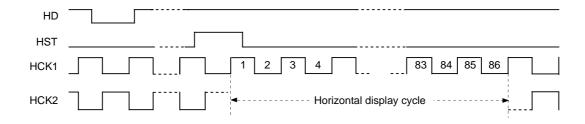

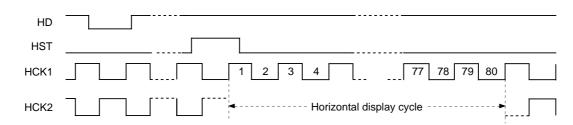

## (2) Horizontal direction display cycle

#### (2.1.1) XGA, PC98 (RGT = H)

# (2.1.2) XGA, PC98 (RGT = L)

#### (2.2.1) SXGA (RGT = H)

# (2.2.2) SXGA (RGT = L)

# (3) Vertical blanking cycle of PC98 mode

The input waveforms of PCG, PRG<sup>\*1</sup> and PSIG should be changed as shown below when BLK pulse is input.

\*1 PRG shows the period of PSIG black level, it is not input to the panel.

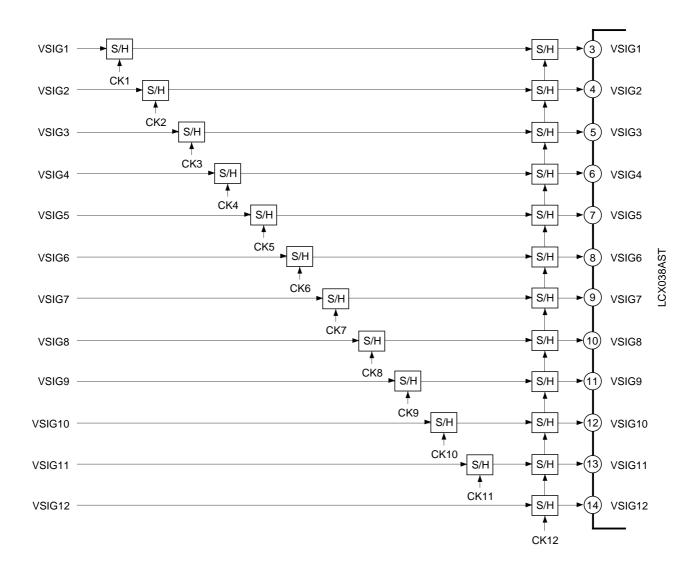

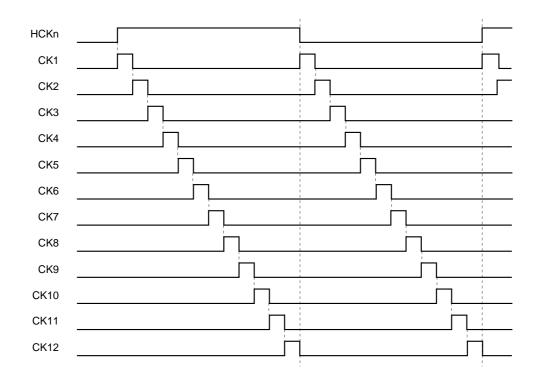

#### 3. 12-dot Simultaneous Sampling

The horizontal shift register samples signals VSIG1 to VSIG12 simultaneously. This requires phase matching between signals VSIG1 to VSIG12 to prevent the horizontal resolution from deteriorating. Thus, phase matching between each signal is required using an external signal delaying circuit before applying the video signal to the LCD panel.

The block diagram of the delaying procedure using the sample-and-hold method is as follows. The following phase relationship diagram indicates the phase setting for right scan (RGT = High level). For left scan (RGT = Low level), the phase settings for signals VSIG1 to VSIG12 are exactly reversed.

# <Phase relationship of delaying sample-and-hold pulses> (right scan)

#### **Display System Block Diagram**

An example of display system is shown below.

# **Notes on Handling**

(1) Static charge prevention

Be sure to take the following protective measures. TFT-LCD panels are easily damaged by static charges.

- a) Use non-chargeable gloves, or simply use bare hands.

- b) Use an earth-band when handling.

- c) Do not touch any electrodes of a panel.

- d) Wear non-chargeable clothes and conductive shoes.

- e) Install conductive mats on the working floor and working table.

- f) Keep panels away from any charged materials.

- g) Use ionized air to discharge the panels.

- (2) Protection from dust and dirt

- a) Operate in a clean environment.

- b) When delivered, the panel surface (glass panel) is covered by a protective sheet. Peel off the protective sheet carefully so as not to damage the glass panel.

- c) Do not touch the glass panel surface. The surface is easily scratched. When cleaning, use a cleanroom wiper with isopropyl alcohol. Be careful not to leave a stain on the surface.

- d) Use ionized air to blow dust off the glass panel.

- (3) Light resistance

Orientation film and organic matter such as liquid crystal used inside of the LCD panel deteriorate by the light chemical reaction. As a result, its indication characteristics may irreversible change. The progress of its chemical reaction is influenced by short wavelength side's light (characteristics of UV cut filter) and temperature when quantity of light is constant. To control its progress, attach suitable UV cut filter between light source and LCD panel. (Sharp characteristic's filter of  $\lambda > 425$ nm is recommended.) Also, use suitable IR cut filter to lower the temperature of LCD panel and cool the panel carefully.

- (4) Other handling precautions

- a) Do not twist or bend the flexible PC board especially at the connecting region because the board is easily deformed.

- b) Do not drop the panel.

- c) Do not twist or bend the panel or panel frame.

- d) Keep the panel away from heat sources.

- e) Do not dampen the panel with water or other solvents.

- f) Avoid storing or using the panel at a high temperature or high humidity, which may result in panel damages.

- g) Minimum radius of bending curvature for a flexible substrate must be 1mm.

- h) Torque required to tighten screws on a panel must be 0.098N · m (measurement screw: JCIS Type 1, M1.7 flat head screw) or less.

- i) Do not pressure the portion other than mounting hole (cover).

Mass 5.6g

Sony Corporation