# *SPT7871*

## 10-BIT, 100 MSPS TTL A/D CONVERTER

#### **FEATURES**

- 10-Bit, 100 MSPS Analog-to-Digital Converter

- · Monolithic Bipolar

- Single-Ended Bipolar Analog Input

- -1.0 V to +1.0 V Analog Input Range

- Internal Sample-and-Hold

- Internal Voltage Reference

- Programmable Data Output Formats

- Single Ended TTL Outputs

- Differential ECL Clock Input

- ECL Version Available as the SPT7870

## **APPLICATIONS**

- Professional Video

- HDTV

- Communications

- Imaging

- Digital Oscilloscopes

### **GENERAL DESCRIPTION**

The SPT7871 is a 10-bit, 100 MSPS analog-to-digital converter, with a two stage subranging flash/folder architecture. The bipolar, single-ended analog input provides an easy interface for most applications. Programmable data output formats provide additional ease of implementation and flexibility. The device supports high speed TTL outputs.

The resolution and performance of this device makes it well suited for professional video and HDTV applications. The onchip track-and-hold provides for excellent AC performance enabling this device to be a converter of choice for RF communications and digital sampling oscilloscopes. The SPT7871 is available in a 44L cerquad package in the industrial temperature range and in die form.

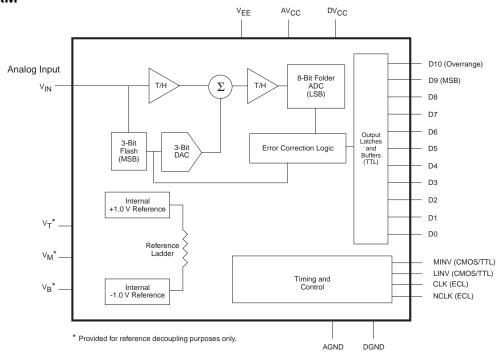

#### **BLOCK DIAGRAM**

# Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

## ABSOLUTE MAXIMUM RATING (Beyond which damage may occur)<sup>1</sup>

| Supply Voltages  | , ,                             | Output                       |                |

|------------------|---------------------------------|------------------------------|----------------|

|                  | 0 to +6.5 V                     | Digital Outputs              | +30 to -30 mA  |

|                  | 0 to +6.5 V<br>0 to -6.5 V      | Temperature                  |                |

| * CC             |                                 | Operating Temperature        | 40 to + 85 °C  |

| Input Voltages   |                                 | Junction Temperature         | + 175 °C       |

| Analog Input     | VEE≤VIN≤VCC                     | Lead, Soldering (10 seconds) | + 300 °C       |

| LINV/MINV Inputs | 0.5 V to V <sub>CC</sub> +0.5 V | Storage                      | 60 to + 150 °C |

| CLK/NCLK Inputs  | V <sub>EE</sub> to 0 V          | _                            |                |

**Note**: 1. Operation at any Absolute Maximum Ratings is not implied. See Electrical Specifications for proper nominal applied conditions in typical applications.

## **ELECTRICAL SPECIFICATIONS**

$T_{A} = +25 \, ^{\circ}\text{C} \text{ , DV}_{CC} = \text{AV}_{CC} = +5.0 \, \text{ V}, \\ V_{EE} = -5.2 \, \text{ V}, \\ V_{IN} = \pm 1.0 \, \text{ V}, \\ f_{clock} = 80 \, \text{MHz}, \\ 50\% \, \text{ clock duty cycle, unless otherwise specified.} \\ \text{APP}_{A} = +25 \, ^{\circ}\text{C} \, \text{ APP}_{CC} = +5.0 \, \text{ V}, \\ V_{EE} = -5.2 \, \text{ V}, \\ V_{IN} = \pm 1.0 \, \text{ V}, \\ f_{clock} = 80 \, \text{MHz}, \\$

| PARAMETERS                             | TEST<br>CONDITIONS           | TEST<br>LEVEL | MIN  | TYP        | MAX   | UNITS    |

|----------------------------------------|------------------------------|---------------|------|------------|-------|----------|

| DC Performance                         |                              |               |      |            |       |          |

| Resolution                             |                              |               |      | 10         |       | Bits     |

| Differential Linearity                 | f <sub>Clock</sub> = 6.4 MHz |               | -1.0 | ±0.5       | ±1.25 | LSB      |

| Integral Linearity, Best Fit           | f <sub>Clock</sub> = 6.4 MHz |               |      | ±1.0       | ±2.0  | LSB      |

|                                        | Full Temperature             | V             |      | ±2.5       |       | LSB      |

| No Missing Codes                       | f <sub>Clock</sub> = 6.4 MHz | I             |      | Guaranteed |       |          |

| Analog Input                           |                              |               |      |            |       |          |

| Input Voltage Range                    |                              | V             |      | ±1.0       |       | V        |

| Input Bias Current                     |                              |               | -100 | 25         | 100   | μΑ       |

| Input Resistance                       |                              |               | 50   | 150        |       | kΩ       |

| •                                      | Full Temperature             | V             |      | 100        |       | kΩ       |

| Input Capacitance                      |                              | V             |      | 5          |       | pF       |

| Input Bandwidth                        | Full Power                   | IV            | 150  | 180        |       | MHz      |

| ±FS Offset Error                       |                              | 1             |      | ±20        | ±100  | mV       |

| Timing Characteristics                 |                              |               |      |            |       | _        |

| Minimum Conversion Rate                |                              | V             |      |            | 2     | MSPS     |

| Maximum Conversion Rate                |                              | IV            | 100  |            |       | MSPS     |

| Pipeline Delay (Latency)               |                              | IV            |      | 2          |       | Clock    |

| Transient Response                     |                              | V             |      | 10         |       | ns       |

| Overvoltage Recovery Time              |                              | V             |      | 10         |       | ns       |

| Output Delay (t <sub>d</sub> )         |                              | V             |      | 3          |       | ns       |

| Aperture Delay Time                    |                              | V             |      | 1          |       | ns       |

| Aperture Jitter Time                   |                              | V             |      | 5          |       | ps (rms) |

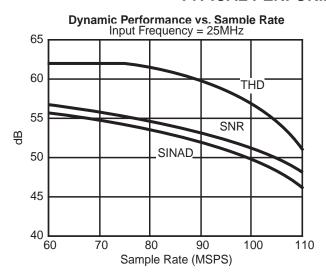

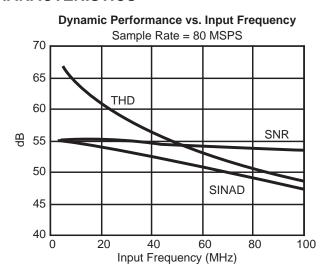

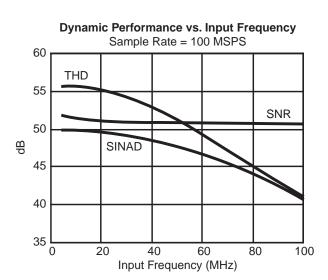

| Dynamic Performance                    |                              |               |      |            |       |          |

| Effective Number of Bits               |                              |               |      |            |       |          |

| $f_{IN} = 10 MHz$                      |                              |               | 8.1  | 8.5        |       | Bits     |

| $f_{IN} = 25 \text{ MHz}$              |                              |               | 8.1  | 8.5        |       | Bits     |

| $f_{IN} = 25 \text{ MHz}$              | f <sub>clock</sub> = 100 MHz | V             |      | 8.0        |       | Bits     |

| $f_{IN} = 50 \text{ MHz}$              |                              |               | 7.5  | 7.8        |       | Bits     |

| $f_{IN} = 50 \text{ MHz}$              | f <sub>clock</sub> = 100 MHz | V             |      | 7.5        |       | Bits     |

| Signal-To-Noise Ratio                  |                              |               |      |            |       |          |

| f <sub>IN</sub> = 10 MHz               |                              |               | 52   | 54         |       | dB       |

| $f_{IN} = 25 \text{ MHz}$              |                              |               | 52   | 54         |       | dB       |

| f <sub>IN</sub> = 25 MHz               | f <sub>clock</sub> = 100 MHz | V             |      | 51         |       | dB       |

| f <sub>IN</sub> = 50 MHz               | 0.00.0                       |               | 52   | 54         |       | dB       |

| $f_{IN} = 50 \text{ MHz}$              | f <sub>clock</sub> = 100 MHz | V             |      | 50         |       | dB       |

| Total Harmonic Distortion <sup>1</sup> |                              |               |      | -          |       |          |

| $f_{IN} = 10 \text{ MHz}$              |                              | 1             | -56  | -62        |       | dBc      |

| f <sub>IN</sub> = 25 MHz               |                              | 1 1           | -56  | -60        |       | dBc      |

| f <sub>IN</sub> = 25 MHz               | f <sub>clock</sub> = 100 MHz | V             |      | -56        |       | dBc      |

| $f_{IN} = 50 \text{ MHz}$              | 5.50K                        | l i           | -48  | -51        |       | dBc      |

| $f_{IN} = 50 \text{ MHz}$              | f <sub>clock</sub> = 100 MHz | V             |      | -50        |       | dBc      |

2

## **ELECTRICAL SPECIFICATIONS**

$T_{A} = +25~^{\circ}\text{C} \text{ , DV}_{CC} = +5.0~\text{V}, \text{ V}_{EE} = -5.2~\text{V}, \text{ V}_{IN} = \pm 1.0~\text{V}, \\ f_{clock} = 80~\text{MHz}, \\ 50\%~\text{clock duty cycle, unless otherwise specified.}$

| PARAMETERS                                            | TEST<br>CONDITIONS           | TEST<br>LEVEL | MIN          | TYP        | MAX        | UNITS           |

|-------------------------------------------------------|------------------------------|---------------|--------------|------------|------------|-----------------|

| Dynamic Performance                                   |                              |               |              |            |            |                 |

| Signal-to-Noise + Distortion (SINAD)                  |                              |               |              |            |            |                 |

| f <sub>IN</sub> =10 MHz                               |                              | I             | 51           | 53         |            | dB              |

| $f_{IN} = 25 \text{ MHz}$                             |                              | I             | 51           | 53         |            | dB              |

| $f_{IN} = 25 \text{ MHz}$                             | f <sub>clock</sub> = 100 MHz | V             |              | 50         |            | dB              |

| $f_{IN} = 50 \text{ MHz}$                             |                              | I             | 47           | 49         |            | dB              |

| $f_{IN} = 50 \text{ MHz}$                             | f <sub>clock</sub> = 100 MHz | V             |              | 47         |            | dB              |

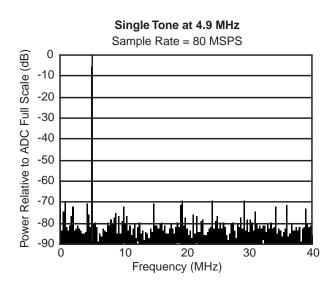

| Spurious Free Dynamic Range                           |                              |               |              |            |            |                 |

| f <sub>IN</sub> = 10 MHz                              |                              | V             |              | 65         |            | dB FS           |

| f <sub>IN</sub> = 25 MHz                              |                              | V             |              | 63         |            | dB FS           |

| f <sub>IN</sub> = 50 MHz                              |                              | l v           |              | 52         |            | dB FS           |

| Two-Tone IMD Rejection <sup>2</sup>                   |                              | l v           |              | -65        |            | dBc             |

| Differential Phase                                    |                              | V             |              | 0.5        |            | Degree          |

| Differential Gain                                     |                              | V             |              | 1          |            | %               |

| Power Supply Requirements                             |                              |               |              |            |            |                 |

| AV <sub>CC</sub> Supply Voltage                       |                              | IV            | 4.75         | 5.0        | 5.25       | V               |

| DV <sub>CC</sub> Supply Voltage                       |                              | IV            | 4.75         | 5.0        | 5.25       | V               |

| V <sub>EE</sub> Supply Voltage                        |                              | IV            | -4.95        | -5.2       | -5.45      | V               |

| V <sub>CC</sub> Supply Current                        | Full Temperature             | VI            | 1.00         | 210        | 248        | mA              |

| V <sub>EE</sub> Supply Current                        | Full Temperature             | VI            |              | 128        | 151        | mA              |

| Power Dissipation                                     | Full Temperature             | VI            |              | 1.7        | 2.0        | W               |

| Power Supply Rejection Ratio                          | T un Temperature             | IV            |              | 30         | 2.0        | dB              |

| Digital Inputs                                        |                              | 1 0           |              |            |            | ub              |

| LINV, MINV                                            |                              | V             |              | CMOS/TTL   |            | Logic           |

| Clock Inputs                                          |                              | V             |              | OIVIOO/TTL |            | Logic           |

| Logic 1 Voltage (ECL)                                 |                              | VI            | -1.1         |            |            | V               |

| Logic 1 Voltage (ECL)                                 |                              | VI            | -1.1         |            | -1.5       | V               |

| Maximum Input Current Low                             |                              | VI            | -100         |            | +100       |                 |

| Maximum Input Current Low  Maximum Input Current High |                              | VI            | -100<br>-100 |            | +100       | μ <b>Α</b><br>^ |

|                                                       |                              |               |              |            |            | μA              |

| Pulse Width Ligh (CLK)                                |                              | IV<br>IV      | 4.0<br>4.0   |            | 250        | ns              |

| Pulse Width High (CLK)<br>Rise/Fall Time              | 200/ to 900/                 | I IV          | 4.0          |            | 250<br>1.5 | ns              |

|                                                       | 20% to 80%                   | IV            |              |            | 1.5        | ns              |

| Digital Outputs                                       | 0 4                          | ,,,           | 0.4          | 0.0        |            |                 |

| Logic 1 Voltage (TTL)                                 | 2 mA                         | VI            | 2.4          | 2.8        | 0.0        | V               |

| Logic 0 Voltage (TTL)                                 | 2 mA                         | VI            |              | 0.5        | 0.8        | V               |

| t <sub>Rise</sub>                                     | 10% to 90%                   | V             |              | 2.0        |            | ns              |

| t <sub>Fall</sub>                                     | 10% to 90%                   | V             |              | 2.0        |            | ns              |

<sup>12048</sup> pt FFT using distortion harmonics 2 through 10.

<sup>&</sup>lt;sup>2</sup>Measured as a second order (f1-f2) intermodulation product from a two-tone test with each input tone at 0 dBm.

| <b>TEST LEVEL CODES</b> All electrical characteristics are subject to the                      | TEST LEVEL | TEST PROCEDURE 100% production tested at the specified temperature.                        |

|------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------|

| following conditions:                                                                          | II         | 100% production tested at $T_A$ = +25 °C, and sample tested at the specified temperatures. |

| All parameters having min/max specifications are guaranteed. The Test Level column indi-       | III        | QA sample tested only at the specified temperatures.                                       |

| cates the specific device testing actually per-<br>formed during production and Quality Assur- | IV         | Parameter is guaranteed (but not tested) by design and characterization data.              |

| ance inspection. Any blank section in the data column indicates that the specification is not  | V          | Parameter is a typical value for information purposes only.                                |

| tested at the specified condition.                                                             | VI         | 100% production tested at $T_A = +25$ °C. Parameter is                                     |

| Unless otherwise noted, all tests are pulsed tests; therefore, $T_J = T_C = T_A$ .             |            | guaranteed over specified temperature range.                                               |

3

**SPT7871**9/7/98

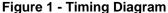

**Table I - Data Output Timing Parameters**

| Timing Parameter                  | Minimum | Typical        | Maximum |

|-----------------------------------|---------|----------------|---------|

| f <sub>clock</sub>                | 2 MHz   |                | 100 MHz |

| Clock Pulse Width High (tpwh)     | 4.0 ns  |                | 250 ns  |

| Clock Pulse Width Low (tpwl)      | 4.0 ns  |                | 250 ns  |

| Switching Delay (t <sub>d</sub> ) |         | 3 ns           |         |

| Clock Latency                     |         | 2 clock cycles |         |

## THEORY OF OPERATION

The SPT7871 uses a two stage subranging architecture incorporating a 3-bit flash MSB conversion stage followed by an 8-bit interpolating folder conversion stage. Digital error correction logic combines the results of both stages to produce a 10-bit data conversion digital output.

The analog signal is input directly to the 3-bit flash converter which performs a 3-bit conversion and in turn drives an internal DAC used to set the second stage voltage reference level. The 3-bit result from the flash conversion is input to the digital error correction logic and used in calculation of the upper most significant bits of the data output.

The analog input is also input directly to an internal track-and-hold amplifier. The signal is held and amplified for use in the second stage conversion. The output of the track-and-hold is input into a summing junction that takes the difference between the track-and-hold amplifier and the 3-bit DAC output. The residual is captured by a second track-and-hold which holds and amplifies this residual voltage.

The residual held by the track-and-hold amplifier is input to an 8-bit interpolating folder stage for data conversion. The 8-bit converted data from the folder stage is input into the digital error correction logic and used in calculation of the lower significant bits.

The error correction logic incorporates a proprietary scheme for compensation of any internal offset and gain errors that might exist to determine the 10-bit conversion result. The

resultant 10-bit data conversion is internally latched and presented on the data output pins via buffered output drivers.

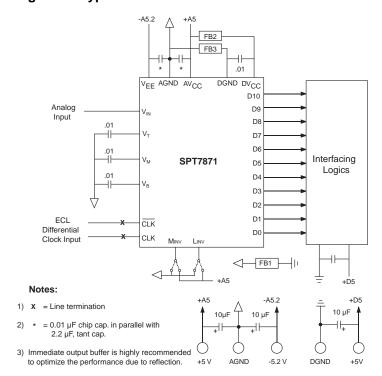

#### TYPICAL INTERFACE CIRCUIT

The SPT7871 requires few external components to achieve the stated operation and performance. Figure 2 shows the typical interface requirements when using the SPT7871 in normal circuit operation. The following section is a description of the pin functions and outlines critical performance criteria to consider for achieving the optimal device performance.

#### POWER SUPPLIES AND GROUNDING

The SPT7871 requires the use of three supply voltages: VEE, AV<sub>CC</sub> and DV<sub>CC</sub>. The VEE and AV<sub>CC</sub> supplies should be treated as analog supply sources. This means the VEE and V<sub>CC</sub> ground returns of the device should both be connected to the analog ground plane. Each power supply pin should be bypassed as closely as possible to the device with .01  $\mu F$  and 2.2  $\mu F$  capacitors as shown in figure 2.

The two grounds available on the SPT7871 are AGND and DGND. DGND is used only for TTL outputs and is to be referenced to the output pullup voltage. These grounds are not tied together internal to the device. The use of ground planes is recommended to achieve the best performance of the SPT7871. The AGND and the DGND ground planes should be separated from each other and only connected together at the device through an inductance or ferrite bead. Doing this will minimize the ground noise pickup.

SPT7871

4

#### **ANALOG INPUT**

The SPT7871 has a single-ended analog input with a bipolar input range from -1 V to +1 V. The bipolar input allows for easier interface by external op amps when compared to unipolar input devices. Because the input common mode is 0 V, the external op amp can operate without a voltage offset on the output, thereby maximizing op amp head room and minimizing distortion.

In addition, the 0 V common mode allows for a very simple DC coupled analog input connection if desired. The current drive requirements for the analog input are minimal when compared to conventional flash converters due to the SPT7871's low input capacitance of only 5 pF and very high input impedance of 150 k $\Omega$ .

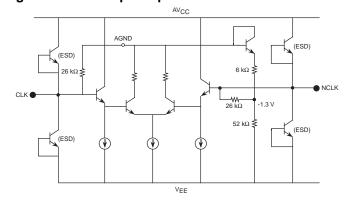

#### **CLOCK INPUTS**

The clock inputs are designed to be driven differentially with ECL levels. For optimal noise performance, the clock input rise time should be a maximum of 1.5 ns. Because of this, the use of *fast* logic is recommended. The analog input signal is latched on the rising edge of the CLK.

The clock may be driven single-ended since the NCLK pin is internally biased to -1.3 V. NCLK may be left open but a .01  $\mu$ F bypass capacitor from NCLK to AGND is recommended. NOTE: System performance may be degraded due to increased clock noise or jitter.

The performance of the SPT7871 is specified and tested with a 50% clock duty cycle. However, at sample rates greater than 80 MSPS, additional gains in the dynamic performance of the device may be obtained by adjusting the clock duty cycle. Typically, operation near 55% duty cycle will yield improved results.

#### INTERNAL VOLTAGE REFERENCE

The SPT7871 incorporates an on-chip voltage reference. The top and bottom reference voltages are each internally tied to their respective top and bottom of the internal reference ladder. The pins for the voltage references and the ladder (including the center of the ladder) are brought out to pins on the device for decoupling purposes only (pins  $V_{\mathsf{T}}, V_{M},$  and  $V_{\mathsf{B}})$ . A .01  $\mu \mathsf{F}$  capacitor should be used on each pin and tied to AGND. See the typical interface circuit (figure 2).

The internal voltage reference and the internal error correction logic eliminate the need for driving externally the voltage reference ladder. In fact, the voltage reference ladder should not be driven with an external voltage reference source as the internal error correction circuitry already compensates for the internal voltage and no improvement will result.

#### **DIGITAL OUTPUTS**

#### **DIGITAL OUTPUT DATA FORMAT - D0 - D9**

D0 is the least-significant bit for the digital data output, and D9 is the most-significant bit. Four data output formats are

available and are controlled by the MINV and LINV pins. Table III shows the four possible output formats possible as a function of MINV and LINV. Table II shows the output coding data format versus analog input voltage relationship.

**Table II - Output Coding Data Format**

| •               |     | •              |                  |

|-----------------|-----|----------------|------------------|

| V <sub>IN</sub> | D10 | D9D0 (Binary*) | D9D0 (2's Comp*) |

| >+1.0 V         | 1   | 11 1111 1111   | 01 1111 1111     |

| (+FS)           | 0   | 11 1111 1111   | 01 1111 1111     |

| +1.0 V -1 LSB   | 0   | 11 1111 1110   | 01 1111 1110     |

| 0.0 V           | 0   | 10 0000 0000   | 00 0000 0000     |

|                 | 0   | 01 1111 1111   | 11 1111 1111     |

| -1.0 V +1 LSB   | 0   | 00 0000 0001   | 10 0000 0001     |

| (-FS)           | 0   | 00 0000 0000   | 10 0000 0000     |

| <-1.0 V         | 0   | 00 0000 0000   | 10 0000 0000     |

<sup>\*</sup>Refer to table III for possible output formats.

#### **OVERRANGE BIT - D10**

D10 is the overrange bit which is asserted whenever the analog input signal exceeds the positive full scale input by 1 LSB. When this condition occurs the D10 bit will be asserted to logic high and remain high continuously until the overrange condition is removed from the input.

All other output signals will also stay at their maximum encoded output throughout this condition. D10 is not asserted for an underscale condition when the input exceeds the negative full scale.

#### **DIGITAL OUTPUT DATA TIMING**

The data is presented on the output pins two clock cycles after the input is sampled with an additional output delay of typically 3 ns. The data is held valid for one clock cycle. Refer to the timing diagram shown in figure 1.

#### **DIGITAL OUTPUT CONTROL PINS - MINV, LINV**

Two digital output control pins control the digital output format. See table III. The MINV pin is a CMOS/TTL-compatible input. It inverts the most-significant bit (D9) when tied to +5 V. The most-significant bit (D9) is noninverted when MINV is tied to ground or floated. The MINV pin is internally pulled down to ground.

The LINV pin is a CMOS/TTL-compatible input. It inverts the least-significant bits (D8 through D0) when tied to +5 V. The least-significant bits (D8 through D0) are noninverted when LINV is tied to ground or floated. The LINV pin is internally pulled down to ground.

Table III - Data Output Bits

| MINV | LINV | Description of Data            |

|------|------|--------------------------------|

| 0 V  | 0 V  | Binary (Noninverted)           |

| 0 V  | +5 V | Two's Complement (Inverted)    |

| +5 V | 0 V  | Two's Complement (Noninverted) |

| +5 V | +5 V | Binary (Inverted)              |

SPT7871

5

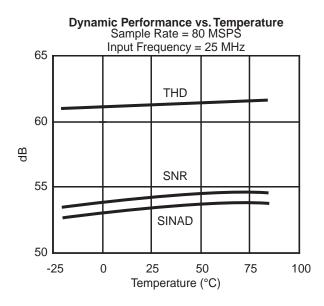

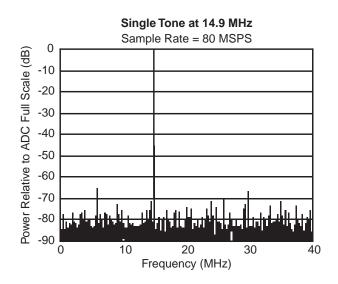

#### TYPICAL PERFORMANCE CHARACTERISTICS

**SPT7871**

6 9/7/98

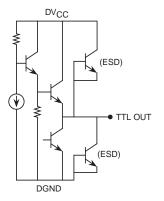

#### TTL DIGITAL OUTPUT LEVELS

The SPT7871 supports TTL and some CMOS logic levels. (Refer to minimum high voltage level for selected digital parts that will interface with the SPT7871.) It has single-ended outputs that are driven off a separate +5 V digital supply (DV $_{CC}$ ).

#### THERMAL MANAGEMENT

SPT recommends that a heat sink be used for this device to ensure rated performance. A heat sink in still air provides

Figure 2 - Typical Interface Circuit

adequate thermal performance under laboratory tests. Air flow may be required for operation at elevated ambient temperature. SPT recommends that the junction temperature be maintained under +150 °C.

The thermal impedance values for the cerquad package are  $\theta_{JC} = 3.3$  °C/W and  $\theta_{JA} = 70$  °C/W (junction to ambient in still air with no heat sink).

Figure 3 - Clock Input Equivalent Circuit

Figure 4 - Digital Outputs Equivalent Circuit

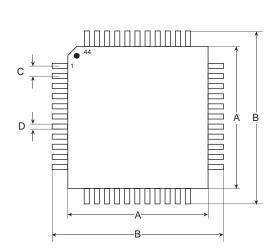

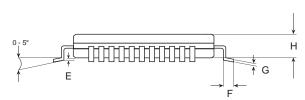

#### **PACKAGE OUTLINE**

## 44L Cerquad

|        | INCHES    |       | MILLIME   | TERS  |

|--------|-----------|-------|-----------|-------|

| SYMBOL | MIN       | MAX   | MIN       | MAX   |

| Α      | 0.550 typ |       | 13.97 typ |       |

| В      | 0.685     | 0.709 | 17.40     | 18.00 |

| С      | 0.037     | 0.041 | 0.94      | 1.04  |

| D      | 0.016 typ |       | 0.41 typ  |       |

| Е      | 0.008 typ |       | 0.20 typ  |       |

| F      | 0.027     | 0.051 | 0.69      | 1.30  |

| G      | 0.006 typ |       | 0.15 typ  |       |

| Н      | 0.080     | 0.150 | 2.03      | 3.81  |

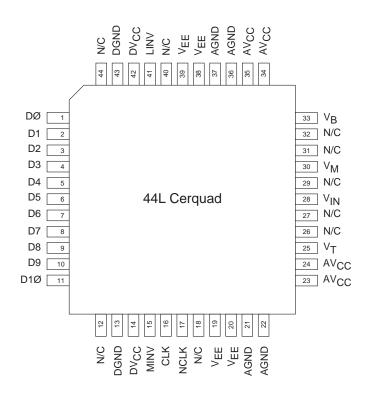

#### **PIN ASSIGNMENTS**

#### **PIN FUNCTIONS**

| Name                           | I/O | Function                                                         |

|--------------------------------|-----|------------------------------------------------------------------|

| VIN                            | I   | Analog Input                                                     |

| D <sub>0</sub> -D <sub>9</sub> | 0   | Digital Output Data (D <sub>0</sub> = LSB) (TTL)                 |

| D <sub>10</sub>                | 0   | Overflow (TTL)                                                   |

| CLK                            | I   | Clock (Internal Pull-Down to Ground)                             |

| NCLK                           | ı   | Inverted Clock (ECL)                                             |

|                                |     | (Internal Pull-Down to -1.3 V)                                   |

| LINV                           | I   | Invert Least Significant Bits (D <sub>0</sub> -D <sub>8</sub> ); |

|                                |     | CMOS/TTL Level; Invert=+5 V;                                     |

|                                |     | Internal Pull-Down to Ground                                     |

| MINV                           | I   | Invert MSB (D <sub>9</sub> );                                    |

|                                |     | CMOS/TTL Level; Invert=+5 V;                                     |

|                                |     | Internal Pull-Down to Ground                                     |

| VT                             | N/A | Internal Top Reference Decoupling                                |

|                                |     | (+1 V typical)                                                   |

| V <sub>M</sub>                 | N/A | Internal Mid-Point Reference Decoupling                          |

|                                |     | (0 V typical)                                                    |

| V <sub>B</sub>                 | N/A | Internal Bottom Reference Decoupling                             |

|                                |     | (-1 V typical)                                                   |

| AV <sub>CC</sub>               | I   | +5 V Analog Supply                                               |

| DV <sub>CC</sub>               | I   | +5 V Digital Supply                                              |

| VEE                            | 1   | -5.2 V Supply                                                    |

| N/C                            | -   | Not Connected                                                    |

| AGND                           | I   | Analog Ground                                                    |

| DGND                           | I   | Digital Ground                                                   |

## ORDERING INFORMATION

| PART NUMBER | TEMPERATURE RANGE | PACKAGE     |

|-------------|-------------------|-------------|

| SPT7871SIQ  | -40 to +85 °C     | 44L Cerquad |

| SPT7871SCU  | +25 °C            | Die*        |

<sup>\*</sup>Please see the die specification for guaranteed electrical performance.

Signal Processing Technologies, Inc. reserves the right to change products and specifications without notice. Permission is hereby expressly granted to copy this literature for informational purposes only. Copying this material for any other use is strictly prohibited.

WARNING - LIFE SUPPORT APPLICATIONS POLICY - SPT products should not be used within Life Support Systems without the specific written consent of SPT. A Life Support System is a product or system intended to support or sustain life which, if it fails, can be reasonably expected to result in significant personal injury or death.

Signal Processing Technologies believes that ultrasonic cleaning of its products may damage the wire bonding, leading to device failure. It is therefore not recommended, and exposure of a device to such a process will void the product warranty.