## M29W800T M29W800B

NOT FOR NEW DESIGN

### 8 Mbit (1Mb x8 or 512Kb x16, Boot Block) Low Voltage Single Supply Flash Memory

#### M29W800T and M29W800B are replaced respectively by the M29W800AT and M29W800AB

- 2.7V to 3.6V SUPPLY VOLTAGE for PROGRAM, ERASE and READ OPERATIONS

- FASTACCESS TIME: 90ns

- FAST PROGRAMMING TIME

- 10μs by Byte / 20μs by Word typical

- PROGRAM/ERASE CONTROLLER (P/E.C.)

- Program Byte-by-Byte or Word-by-Word

- Status Register bits and Ready/Busy Output

- MEMORY BLOCKS

- Boot Block (Top or Bottom location)

- Parameter and Main blocks

- BLOCK, MULTI-BLOCK and CHIP ERASE

- MULTI BLOCK PROTECTION/TEMPORARY UNPROTECTION MODES

- ERASE SUSPEND and RESUME MODES

- Read and Program another Block during Erase Suspend

- LOW POWER CONSUMPTION

- Stand-by and Automatic Stand-by

- 100,000 PROGRAM/ERASE CYCLES per BLOCK

- 20 YEARS DATA RETENTION

- Defectivity below 1ppm/year

- ELECTRONIC SIGNATURE

- Manufacturer Code: 0020h

- Device Code, M29W800T: 00D7h

- Device Code, M29W800B: 005Bh

#### DESCRIPTION

The M29W800 is a non-volatile memory that may be erased electrically at the block or chip level and programmed in-system on a Byte-by-Byteor Word-by-Word basis using only a single 2.7V to 3.6V V<sub>CC</sub> supply. For Program and Erase operations the necessary high voltages are generated internally. The device can also be programmed in standard programmers.

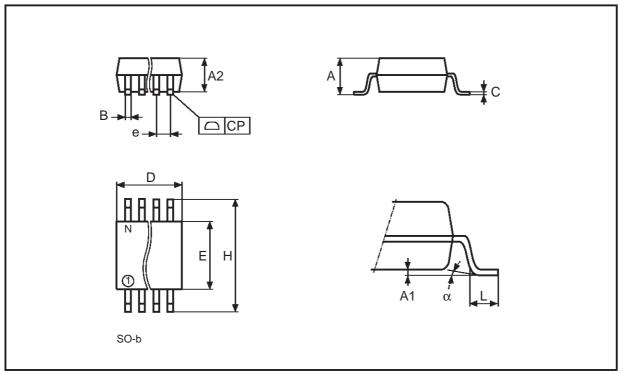

The array matrix organisation allows each block to be erased and reprogrammed without affecting other blocks. Blocks can be protected against programing and erase on programming equipment, TSOP48 (N) 12 x 20 mm

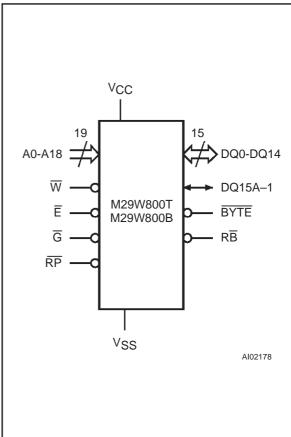

#### Figure 1. Logic Diagram

June 1999

This is information on a product still in production but not recommended for new designs.

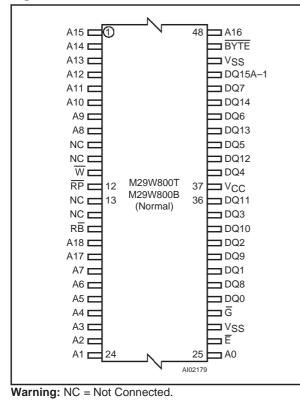

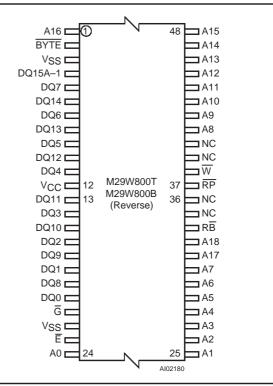

Figure 2B. TSOP Reverse Pin Connections

Warning: NC = Not Connected.

Table 1. Signal Names

| A0-A18          | Address Inputs                     |  |  |  |  |

|-----------------|------------------------------------|--|--|--|--|

| DQ0-DQ7         | Data Input/Outputs, Command Inputs |  |  |  |  |

| DQ8-DQ14        | Data Input/Outputs                 |  |  |  |  |

| DQ15A-1         | Data Input/Output or Address Input |  |  |  |  |

| Ē               | Chip Enable                        |  |  |  |  |

| G               | Output Enable                      |  |  |  |  |

| W               | Write Enable                       |  |  |  |  |

| RP              | Reset / Block Temporary Unprotect  |  |  |  |  |

| RB              | Ready/Busy Output                  |  |  |  |  |

| BYTE            | Byte/Word Organisation             |  |  |  |  |

| V <sub>CC</sub> | Supply Voltage                     |  |  |  |  |

| V <sub>SS</sub> | Ground                             |  |  |  |  |

| Symbol                                                    | Parameter                                    | Value        | Unit |

|-----------------------------------------------------------|----------------------------------------------|--------------|------|

| T <sub>A</sub>                                            | Ambient Operating Temperature <sup>(3)</sup> | -40 to 85    | °C   |

| T <sub>BIAS</sub>                                         | Temperature Under Bias                       | –50 to 125   | °C   |

| T <sub>STG</sub>                                          | Storage Temperature                          | –65 to 150   | °C   |

| V <sub>IO</sub> <sup>(2)</sup>                            | Input or Output Voltages                     | –0.6 to 5    | V    |

| V <sub>CC</sub>                                           | Supply Voltage                               | –0.6 to 5    | V    |

| $V_{(A9, \overline{E}, \overline{G}, \overline{RP})}$ (2) | A9, E, G, RP Voltage                         | -0.6 to 13.5 | V    |

Table 2. Absolute Maximum Ratings <sup>(1)</sup>

Notes: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

2. Minimum Voltage may undershoot to -2V during transition and for less than 20ns.

3. Depends on range.

#### DESCRIPTION (Cont'd)

and temporarily unprotected to make changes in the application. Each block can be programmed and erased over 100,000 cycles.

Instructions for Read/Reset, Auto Select for reading the Electronic Signature or Block Protection status, Programming, Block and Chip Erase, Erase Suspend and Resume are written to the device in cycles of commands to a Command Interface using standard microprocessor write timings.

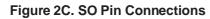

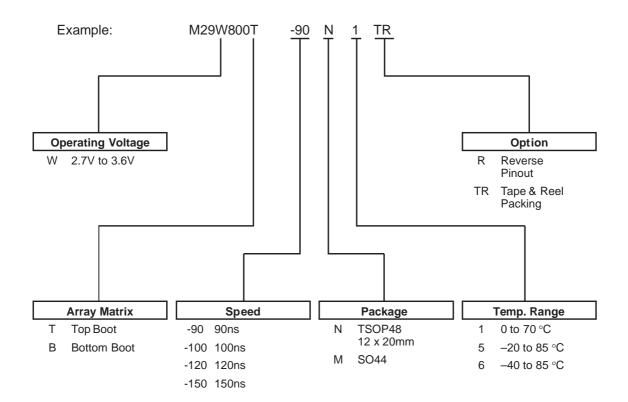

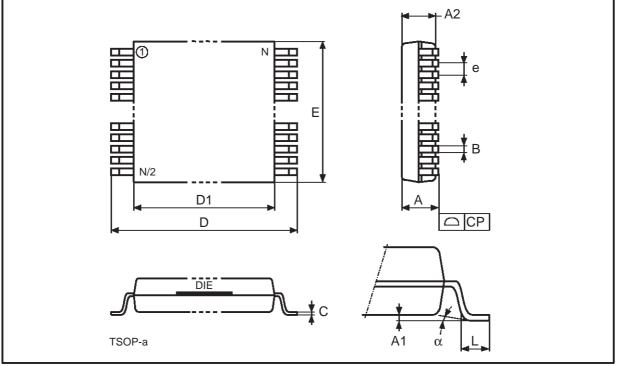

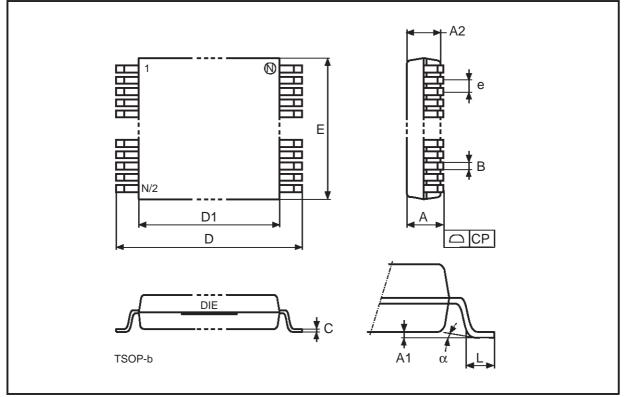

The device is offered in TSOP48 (12 x 20mm) and SO44 packages. Both normal and reverse pinouts are available for the TSOP48 package.

#### Organisation

The M29W800 is organised as 1 M x8 or 512K x16 bits selectable by the BYTE signal. When BYTE is Low the Byte-wide x8 organisation is selected and the address lines are DQ15A–1 and A0-A18. The Data Input/Output signal DQ15A–1 acts as address line A–1 which selects the lower or upper Byte of the memory word for output on DQ0-DQ7, DQ8-DQ14 remain at High impedance. When BYTE is High the memory uses the address inputs A0-A18 and the Data Input/Outputs DQ0-DQ15. Memory control is provided by Chip Enable E, Output Enable G and Write Enable W inputs.

A Reset/Block Temporary Unprotection  $\overline{RP}$  tri-level input provides a hardware reset when pulled Low, and when held High (at V<sub>ID</sub>) temporarily unprotects blocks previously protected allowing them to be programed and erased. Erase and Program operations are controlled by an internal Program/Erase Controller (P/E.C.). Status Register data output on DQ7 provides a Data Polling signal, and DQ6 and DQ2 provide Toggle signals to indicate the state of the P/E.C operations. A Ready/Busy R $\overline{B}$  output indicates the completion of the internal algorithms.

#### **Memory Blocks**

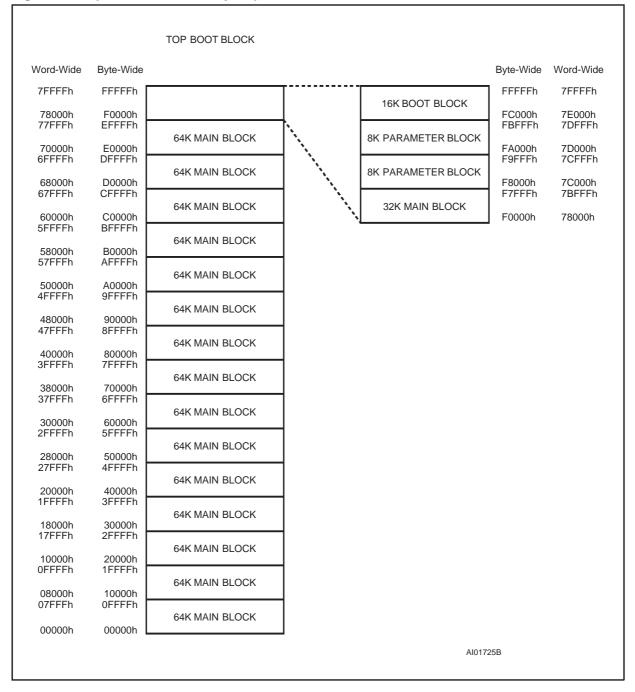

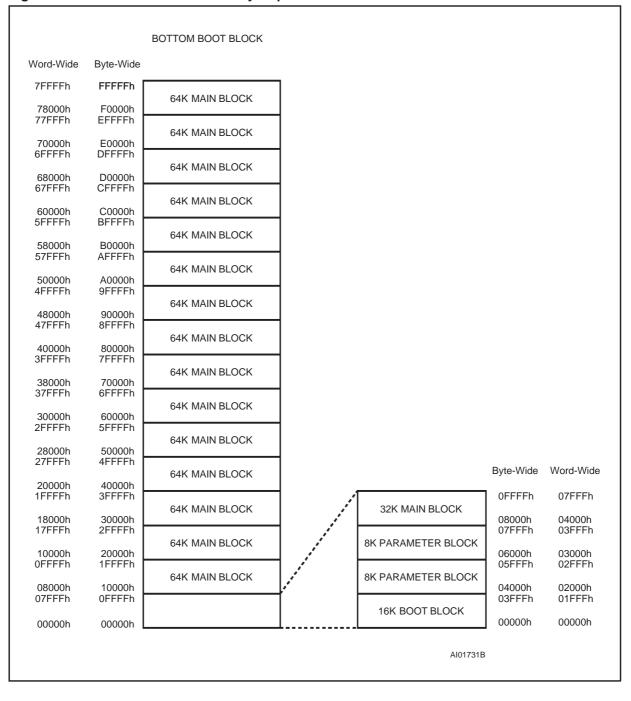

The devices feature asymmetrically blocked architecture providing system memory integration. Both M29W800T and M29W800B devices have an array of 19 blocks, one Boot Block of 16 KBytes or 8 KWords, two Parameter Blocks of 8 KBytes or 4 KWords, one Main Block of 32 KBytes or 16 KWords and fifteen Main Blocks of 64 KBytes or 32 KWords. The M29W800T has the Boot Block at the top of the memory address space and the M29W800B locates the Boot Block starting at the bottom. The memory maps are showed in Figure 3.

Each block can be erased separately, any combination of blocks can be specified for multi-block erase or the entire chip may be erased. The Erase operations are managed automatically by the P/E.C. The block erase operation can be suspended in order to read from or program to any block not being ersased, and then resumed.

Block protection provides additional data security. Each block can be separately protected or unprotected against Program or Erase on programming equipment. All previously protected blocks can be temporarily unprotected in the application.

#### **Bus Operations**

The following operations can be performed using the appropriate bus cycles: Read (Array, Electronic Signature, Block Protection Status), Write command, Output Disable, Standby, Reset, Block Protection, Unprotection, Protection Verify, Unprotection Verify and Block Temporary Unprotection. See Tables 4 and 5.

#### M29W800T, M29W800B

57

#### Figure 3A. Top Boot Block Memory Map and Block Address Table

Figure 3B. Bottom Boot Block Memory Map and Block Address Table

| Address Range (x8) | Address Range (x16) | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

|--------------------|---------------------|-----|-----|-----|-----|-----|-----|-----|

| 00000h-0FFFFh      | 00000h-07FFFh       | 0   | 0   | 0   | 0   | Х   | Х   | Х   |

| 10000h-1FFFFh      | 08000h-0FFFFh       | 0   | 0   | 0   | 1   | Х   | Х   | Х   |

| 20000h-2FFFFh      | 10000h-17FFFh       | 0   | 0   | 1   | 0   | Х   | Х   | Х   |

| 30000h-3FFFFh      | 18000h-1FFFFh       | 0   | 0   | 1   | 1   | Х   | Х   | Х   |

| 40000h-4FFFFh      | 20000h-27FFFh       | 0   | 1   | 0   | 0   | Х   | Х   | Х   |

| 50000h-5FFFFh      | 28000h-2FFFFh       | 0   | 1   | 0   | 1   | Х   | Х   | Х   |

| 60000h-6FFFFh      | 30000h-37FFFh       | 0   | 1   | 1   | 0   | Х   | Х   | Х   |

| 70000h-7FFFFh      | 38000h-3FFFFh       | 0   | 1   | 1   | 1   | Х   | Х   | Х   |

| 80000h-8FFFFh      | 40000h-47FFFh       | 1   | 0   | 0   | 0   | Х   | Х   | Х   |

| 90000h-9FFFFh      | 48000h-4FFFFh       | 1   | 0   | 0   | 1   | Х   | Х   | Х   |

| A0000h-AFFFFh      | 50000h-57FFFh       | 1   | 0   | 1   | 0   | Х   | Х   | Х   |

| B0000h-BFFFFh      | 58000h-5FFFFh       | 1   | 1   | 1   | 1   | Х   | Х   | Х   |

| C0000h-CFFFFh      | 60000h-67FFFh       | 1   | 1   | 0   | 0   | Х   | Х   | Х   |

| D0000h-DFFFFh      | 68000h-6FFFFh       | 1   | 1   | 0   | 1   | Х   | Х   | Х   |

| E0000h-EFFFFh      | 70000h-77FFFh       | 1   | 1   | 1   | 0   | Х   | Х   | Х   |

| F0000h-F7FFFh      | 78000h-7BFFFh       | 1   | 1   | 1   | 1   | 0   | Х   | Х   |

| F8000h-F9FFFh      | 7C000h-7CFFFh       | 1   | 1   | 1   | 1   | 1   | 0   | 0   |

| FA000h-FBFFFh      | 7D000h-7DFFFh       | 1   | 1   | 1   | 1   | 1   | 0   | 1   |

| FC000h-FFFFFh      | 7E000h-7FFFFh       | 1   | 1   | 1   | 1   | 1   | 1   | Х   |

Table 3A. M29W800T Block Address Table

#### **Command Interface**

Instructions, made up of commands written in cycles, can be given to the Program/Erase Controller through a Command Interface (C.I.). For added data protection, program or erase execution starts after 4 or 6 cycles. The first, second, fourth and fifth cycles are used to input Coded cycles to the C.I. This Coded sequence is the same for all Program/Erase Controller instructions. The 'Command' itself and its confirmation, when applicable, are given on the third, fourth or sixth cycles. Any incorrect command or any improper command sequence will reset the device to Read Array mode.

| Address Range (x8) | Address Range (x16) | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

|--------------------|---------------------|-----|-----|-----|-----|-----|-----|-----|

| 00000h-03FFFh      | 00000h-01FFFh       | 0   | 0   | 0   | 0   | 0   | 0   | Х   |

| 04000h-05FFFh      | 02000h-02FFFh       | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

| 06000h-07FFFh      | 03000h-03FFFh       | 0   | 0   | 0   | 0   | 0   | 1   | 1   |

| 08000h-0FFFFh      | 04000h-07FFFh       | 0   | 0   | 0   | 0   | 1   | Х   | Х   |

| 10000h-1FFFFh      | 08000h-0FFFFh       | 0   | 0   | 0   | 1   | Х   | Х   | Х   |

| 20000h-2FFFFh      | 10000h-17FFFh       | 0   | 0   | 1   | 0   | Х   | Х   | Х   |

| 30000h-3FFFFh      | 18000h-1FFFFh       | 0   | 0   | 1   | 1   | Х   | Х   | Х   |

| 40000h-4FFFFh      | 20000h-27FFFh       | 0   | 1   | 0   | 0   | Х   | Х   | Х   |

| 50000h-5FFFFh      | 28000h-2FFFFh       | 0   | 1   | 0   | 1   | Х   | Х   | Х   |

| 60000h-6FFFFh      | 30000h-37FFFh       | 0   | 1   | 1   | 0   | Х   | Х   | Х   |

| 70000h-7FFFFh      | 38000h-3FFFFh       | 0   | 1   | 1   | 1   | Х   | Х   | Х   |

| 80000h-8FFFFh      | 40000h-47FFFh       | 1   | 0   | 0   | 0   | Х   | Х   | Х   |

| 90000h-9FFFFh      | 48000h-4FFFFh       | 1   | 0   | 0   | 1   | Х   | Х   | Х   |

| A0000h-AFFFFh      | 50000h-57FFFh       | 1   | 0   | 1   | 0   | Х   | Х   | Х   |

| B0000h-BFFFFh      | 58000h-5FFFFh       | 1   | 0   | 1   | 1   | Х   | Х   | Х   |

| C0000h-CFFFFh      | 60000h-67FFFh       | 1   | 1   | 0   | 0   | Х   | Х   | Х   |

| D0000h-DFFFFh      | 68000h-6FFFFh       | 1   | 1   | 0   | 1   | Х   | Х   | Х   |

| E0000h-EFFFFh      | 70000h-77FFFh       | 1   | 1   | 1   | 0   | Х   | Х   | Х   |

| F0000h-FfFFFh      | 78000h-7FFFFh       | 1   | 1   | 1   | 1   | Х   | Х   | Х   |

Table 3B. M29W800B Block Address Table

#### Instructions

Seven instructions are defined to perform Read Array, Auto Select (to read the Electronic Signature or Block Protection Status), Program, Block Erase, Chip Erase, Erase Suspend and Erase Resume. The internal P/E.C. automatically handles all timing and verification of the Program and Erase operations. The Status Register Data Polling, Toggle, Error bits and the RB output may be read at any time, during programming or erase, to monitor the progress of the operation.

Instructions are composed of up to six cycles. The first two cycles input a Coded sequence to the Command Interface which is common to all instructions (see Table 8).

The third cycle inputs the instruction set-up command. Subsequent cycles output the addressed data, Electronic Signature or Block Protection Status for Read operations. In order to give additional data protection, the instructions for Program and Block or Chip Erase require further command inputs. For a Program instruction, the fourth command cycle inputs the address and data to be programmed. For an Erase instruction (Block or Chip), the fourth and fifth cycles input a further Coded sequence before the Erase confirm command on the sixth cycle. Erasure of a memory block may be suspended, in order to read data from another block or to program data in another block, and then resumed.

When power is first applied or if V<sub>CC</sub> falls below  $V_{LKO}$ , the command interface is reset to Read Array.

#### SIGNAL DESCRIPTIONS

See Figure 1 and Table 1.

Address Inputs (A0-A18). The address inputs for the memory array are latched during a write operation on the falling edge at Chip Enable  $\overline{E}$  or Write Enable  $\overline{W}$ . In Word-wide organisation the address lines are A0-A18, in Byte-wide organisation DQ15A–1 acts as an additional LSB address line. When A9 is raised to V<sub>ID</sub>, either a Read Electronic Signature Manufacturer or Device Code, Block Protection Status or a Write Block Protection or Block Unprotection is enabled depending on the combination of levels on A0, A1, A12 and A15.

**Data Input/Outputs (DQ0-DQ7).** These Inputs/Outputs are used in the Byte-wide and Wordwide organisations. The input is data to be programmed in the memory array or a command to be written to the C.I. Both are latched on the rising edge of Chip Enable  $\overline{E}$  or Write Enable  $\overline{W}$ . The output is data from the Memory Array, the Electronic Signature Manufacturer or Device codes, the Block Protection Status or the Status register Data Polling bit DQ7, the Toggle Bits DQ6 and DQ2, the Error bit DQ5 or the Erase Timer bit DQ3. Outputs are valid when Chip Enable  $\overline{E}$  and Output Enable  $\overline{G}$  are active. The output is high impedance when the chip is deselected or the outputs are disabled and when  $\overline{RP}$  is at a Low level.

**Data Input/Outputs (DQ8-DQ14 and DQ15A–1).** These Inputs/Outputs are additionally used in the Word-wide organisation. When BYTE is High DQ8-DQ14 and DQ15A–1 act as the MSB of the Data Input or Output, functioning as described for DQ0-DQ7 above, and DQ8 - DQ15 are 'don't care' for command inputs or status outputs. When BYTE is Low, DQ0-DQ14 are high impedance, DQ15A–1 is the Address A–1 input.

Chip Enable (E). The Chip Enable input activates the memory control logic, input buffers, decoders and sense amplifiers. E High deselects the memory and reduces the power consumption to the standby level. E can also be used to control writing to the command register and to the memory array, while  $\overline{W}$  remains at a low level. The Chip Enable must be forced to V<sub>ID</sub> during the Block Unprotection operation.

**Output Enable (G).** The Output Enable gates the outputs through the data buffers during a read operation. When  $\overline{G}$  is High the outputs are High

impedance.  $\overline{G}$  must be forced to V<sub>ID</sub> level during Block Protection and Unprotection operations.

Write Enable ( $\overline{W}$ ). This input controls writing to the Command Register and Address and Data latches.

**Byte/Word Organization Select (BYTE).** The BYTE input selects the output configuration for the device: Byte-wide (x8) mode or Word-wide (x16) mode. When BYTE is Low, the Byte-wide mode is selected and the data is read and programmed on DQ0-DQ7. In this mode, DQ8-DQ14 are at high impedance and DQ15A–1 is the LSB address. When BYTE is High, the Word-wide mode is selected and the data is read and programmed on DQ0-DQ15.

**Ready/Busy Output (RB).** Ready/Busy is an open-drainoutput and gives the internal state of the P/E.C. of the device. When RB is Low, the device is Busy with a Program or Erase operation and it will not accept any additional program or erase instructions except the Erase Suspend instruction. When RB is High, the device is readyfor any Read, Program or Erase operation. The RB will also be High when the memory is put in Erase Suspend or Standby modes.

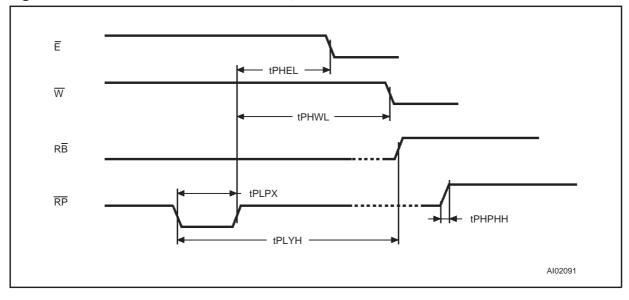

**Reset/Block Temporary Unprotect Input (RP).** The RP Input provides hardware reset and protected block(s) temporary unprotection functions. Reset of the memory is acheived by pulling RP to  $V_{IL}$  for at least  $t_{PLPX}$ . When the reset pulse is given, if the memory is in Read or Standby modes, it will be available for new operations in  $t_{PHEL}$  after the rising edge of RP. If the memory is in Erase, Erase Suspend or Program modes the reset will take  $t_{PLYH}$  during which the RB signal will be held at  $V_{IL}$ . The end of the memory reset will be indicated by the rising edge of RB. A hardware reset during an Erase or Program operation will corrupt the data being programmed or the sector(s) being erased. See Table 14 and Figure 9.

Temporary block unprotection is made by holding  $\overline{RP}$  at V<sub>ID</sub>. In this condition previously protected blocks can be programmed or erased. The transition of  $\overline{RP}$  from V<sub>IH</sub> to V<sub>ID</sub> must slower than t<sub>PHPHH</sub>. See Table 15 and Figure 9. When  $\overline{RP}$  is returned from V<sub>ID</sub> to V<sub>IH</sub> all blocks temporarily unprotected will be again protected.

Vcc Supply Voltage. The power supply for all operations (Read, Program and Erase).

$V_{\text{SS}}$  Ground.  $V_{\text{SS}}$  is the reference for all voltage measurements.

#### **DEVICE OPERATIONS**

See Tables 4, 5 and 6.

**Read.** Read operations are used to output the contents of the Memory Array, the Electronic Signature, the Status Register or the Block Protection Status. Both Chip Enable  $\overline{E}$  and Output Enable  $\overline{G}$  must be low in order to read the output of the memory.

**Write.** Write operations are used to give Instruction Commands to the memory or to latch input data to be programmed. A write operation is initiated when Chip Enable  $\overline{E}$  is Low and Write Enable  $\overline{W}$  is Low with Output Enable  $\overline{G}$  High. Addresses are latched on the falling edge of  $\overline{W}$  or  $\overline{E}$  whichever occurs last. Commands and Input Data are latched on the rising edge of  $\overline{W}$  or  $\overline{E}$  whichever occurs first.

**Output Disable.** The data outputs are high impedance when the Output Enable  $\overline{G}$  is High with Write Enable  $\overline{W}$  High.

**Standby.** The memory is in standby when Chip Enable E is High and the P/E.C. is idle. The power consumption is reduced to the standby level and the outputs are high impedance, independent of the Output Enable G or Write Enable W inputs.

Automatic Standby. After 150ns of bus inactivity and when CMOS levels are driving the addresses, the chip automatically enters a pseudo-standby mode where consumption is reduced to the CMOS standby value, while outputs still drive the bus.

**Electronic Signature.** Two codes identifying the manufacturer and the device can be read from the memory. The manufacturer's code for STMicroelectronics is 20h, the device code is D7h for the M29W800T (Top Boot) and 5Bh for the M29W800B (Bottom Boot). These codes allow programming equipment or applications to automatically match their interface to the characteristics of the M29W800. The Electronic Signature is output by a Read operation when the voltage applied to A9 is at V<sub>ID</sub> and address inputs A1 is Low. The manufacturer code is output when the Address input A0 is Low and the device code when this input is High. Other Address inputs are ignored. The codes are output on DQ0-DQ7.

The Electronic Signature can also be read, without raising A9 to  $V_{1D}$ , by giving the memory the Instruction AS. If the Byte-wide configuration is selected

the codes are output on DQ0-DQ7 with DQ8-DQ14 at High impedance; if the Word-wide configuration is selected the codes are output on DQ0-DQ7 with DQ8-DQ15 at 00h.

**Block Protection.** Each block can be separately protected against Program or Erase on programming equipment. Block protection provides additional data security, as it disables all program or erase operations. This mode is activated when both A9 and  $\overline{G}$  are raised to V<sub>ID</sub> and an address in the block is applied on A12-A18. Block protection is initiated on the edge of  $\overline{W}$  falling to V<sub>IL</sub>. Then after a delay of 100µs, the edge of  $\overline{W}$  rising to V<sub>IL</sub> and A1 to V<sub>IH</sub> ends the protection operations. Block protection verify is achieved by bringing  $\overline{G}$ ,  $\overline{E}$ , A0 and A6 to V<sub>IL</sub> and A1 to V<sub>IH</sub>, while  $\overline{W}$  is at V<sub>IH</sub> and A9 at V<sub>ID</sub>. Under these conditions, reading the data output will yield 01h if the block defined by the inputs on A12-A18 is protected. Any attempt to program or erase a protected block will be ignored by the device.

**Block Temporary Unprotection.** Any previously protected block can be temporarily unprotected in order to change stored data. The temporary unprotection mode is activated by bringing RP to V<sub>ID</sub>. During the temporary unprotection mode the previously protected blocks are unprotected. A block can be selected and data can be modified by executing the Erase or Program instruction with the RP signal held at V<sub>ID</sub>. When RP is returned to V<sub>IH</sub>, all the previously protected blocks are again protected.

**Block Unprotection.** All protected blocks can be unprotected on programming equipment to allow updating of bit contents. All blocks must first be protected before the unprotection operation. Block unprotection is activated when A9,  $\overline{G}$  and  $\overline{E}$  are at VID and A12, A15 at VIH. Unprotection is initiated by the edge of  $\overline{W}$  falling to  $V_{\text{IL}}.$  After a delay of 10ms, the unprotection operation will end. Unprotection verify is achieved by bringing  $\overline{G}$  and  $\overline{E}$  to V<sub>IL</sub> while A0 is at  $V_{IL}$ , A6 and A1 are at  $V_{IH}$  and A9 remains at V<sub>ID</sub>. In these conditions, reading the output data will yield 00h if the block defined by the inputs A12-A18 has been succesfully unprotected. Each block must be separately verified by giving its address in order to ensure that it has been unprotected.

| Operation                                        | Ē   | G   | w                     | RP              | BYTE | A0  | A1  | A6  | A9  | A12 | A15 | DQ15<br>A-1      | DQ8-<br>DQ14   | DQ0-DQ7                                   |

|--------------------------------------------------|-----|-----|-----------------------|-----------------|------|-----|-----|-----|-----|-----|-----|------------------|----------------|-------------------------------------------|

| Read Word                                        | VIL | VIL | Vih                   | Vih             | Vih  | A0  | A1  | A6  | A9  | A12 | A15 | Data<br>Output   | Data<br>Output | Data<br>Output                            |

| Read Byte                                        | VIL | VIL | V <sub>IH</sub>       | VIH             | VIL  | A0  | A1  | A6  | A9  | A12 | A15 | Address<br>Input | Hi-Z           | Data<br>Output                            |

| Write Word                                       | VIL | Vih | Vil                   | VIH             | Vih  | A0  | A1  | A6  | A9  | A12 | A15 | Data Input       | Data Input     | Data<br>Input                             |

| Write Byte                                       | VIL | Vih | Vil                   | VIH             | VIL  | A0  | A1  | A6  | A9  | A12 | A15 | Address<br>Input | Hi-Z           | Data<br>Input                             |

| Output Disable                                   | VIL | VIH | V <sub>IH</sub>       | VIH             | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Hi-Z             | Hi-Z           | Hi-Z                                      |

| Standby                                          | VIH | Х   | Х                     | VIH             | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Hi-Z             | Hi-Z           | Hi-Z                                      |

| Reset                                            | Х   | Х   | Х                     | VIL             | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Hi-Z             | Hi-Z           | Hi-Z                                      |

| Block<br>Protection <sup>(2,4)</sup>             | VIL | VID | V <sub>IL</sub> Pulse | Vін             | х    | х   | х   | х   | VID | х   | х   | х                | х              | х                                         |

| Blocks<br>Unprotection <sup>(4)</sup>            | VID | VID | Vı∟ Pulse             | VIH             | х    | х   | х   | х   | VID | VIH | VIH | х                | х              | х                                         |

| Block<br>Protection<br>Verify <sup>(2,4)</sup>   | VIL | VIL | Vih                   | Vih             | х    | VIL | Vih | VIL | Vid | A12 | A15 | х                | х              | Block<br>Protect<br>Status <sup>(3)</sup> |

| Block<br>Unprotection<br>Verify <sup>(2,4)</sup> | VIL | VIL | Vih                   | Vih             | х    | VIL | Vih | Vін | Vid | A12 | A15 | х                | х              | Block<br>Protect<br>Status <sup>(3)</sup> |

| Block<br>Temporary<br>Unprotection               | х   | х   | х                     | V <sub>ID</sub> | х    | х   | х   | х   | х   | х   | х   | х                | х              | х                                         |

#### Table 4. User Bus Operations <sup>(1)</sup>

Notes:1.  $X = V_{IL}$  or  $V_{IH}$ 2. Block Address must be given on A12-A18 bits.3. See Table 6.4. Operation performed on programming equipment.

| Org.        | Code              | Device   | Ē   | G               | W   | BYTE            | A0  | A1              | Other<br>Addresses | DQ15<br>A-1   | DQ8-<br>DQ14 | DQ0-<br>DQ7 |

|-------------|-------------------|----------|-----|-----------------|-----|-----------------|-----|-----------------|--------------------|---------------|--------------|-------------|

| Word-       | Manufact.<br>Code |          | VIL | VIL             | VIH | Vih             | VIL | VIL             | Don't Care         | 0             | 00h          | 20h         |

| wide Device | M29W800T          | VIL      | VIL | VIH             | VIH | VIH             | VIL | Don't Care      | 0                  | 00h           | D7h          |             |

|             | Code              | M29W800B | VIL | VIL             | VIH | VIH             | VIH | VIL             | Don't Care         | 0             | 00h          | 5Bh         |

|             | Manufact.<br>Code |          | VIL | V <sub>IL</sub> | VIH | VIL             | VIL | V <sub>IL</sub> | Don't Care         | Don't<br>Care | Hi-Z         | 20h         |

|             | Device            | M29W800T | VIL | VIL             | VIH | V <sub>IL</sub> | VIH | V <sub>IL</sub> | Don't Care         | Don't<br>Care | Hi-Z         | D7h         |

|             | Code              | M29W800B | VIL | VIL             | VIH | VIL             | ViH | VIL             | Don't Care         | Don't<br>Care | Hi-Z         | 5Bh         |

Table 5. Read Electronic Signature (following AS instruction or with A9 =  $V_{ID}$ )

#### Table 6. Read Block Protection with AS Instruction

| Code              | Ē               | G               | W               | A0              | A1              | A12-A18       | Other<br>Addresses | DQ0-DQ7 |

|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------|--------------------|---------|

| Protected Block   | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Block Address | Don't Care         | 01h     |

| Unprotected Block | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | VIH             | Block Address | Don't Care         | 00h     |

#### INSTRUCTIONS AND COMMANDS

The Command Interface latches commands written to the memory. Instructions are made up from one or more commands to perform Read Memory Array, Read Electronic Signature, Read Block Protection, Program, Block Erase, Chip Erase, Erase Suspend and Erase Resume. Commands are made of address and data sequences. The instructions require from 1 to 6 cycles, the first or first three of which are always write operations used to initiate the instruction. They are followed by either further write cycles to confirm the first command or execute the command immediately. Command sequencing must be followed exactly. Any invalid combination of commands will reset the device to Read Array. The increased number of cycles has been chosen to assure maximum data security. Instructions are initialised by two initial Coded cycles which unlock the Command Interface. In addition, for Erase, instruction confirmation is again preceded by the two Coded cycles.

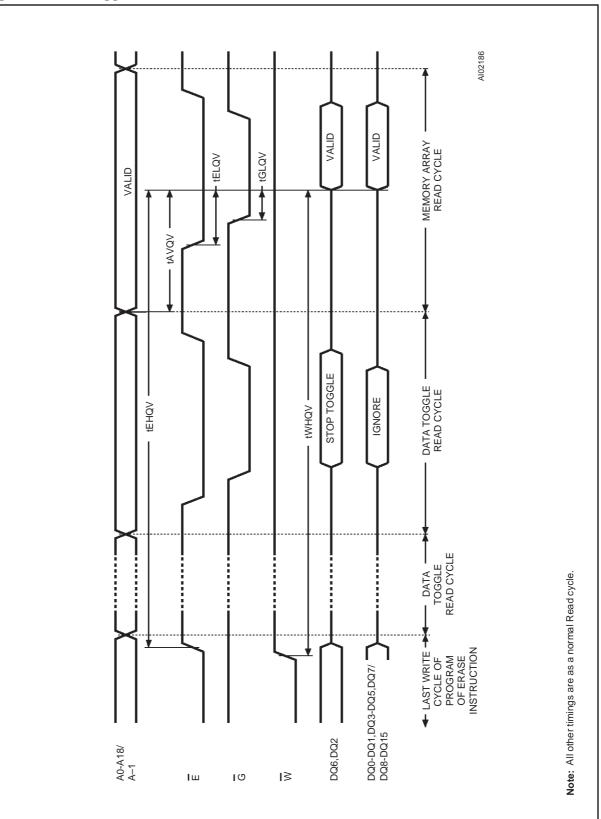

#### **Status Register Bits**

P/E.C. status is indicated during execution by Data Polling on DQ7, detection of Toggle on DQ6 and DQ2, or Error on DQ5 and Erase Timer DQ3 bits. Any read attempt during Program or Erase command execution will automatically output these five Status Register bits. The P/E.C. automatically sets bits DQ2, DQ3, DQ5, DQ6 and DQ7. Other bits (DQ0, DQ1 and DQ4) are reserved for future use and should be masked. See Tables 9 and 10.

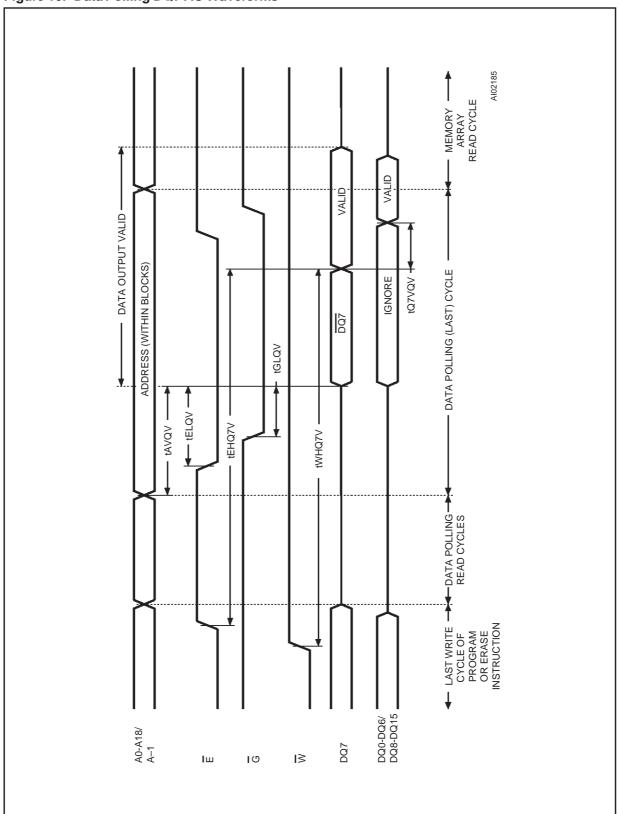

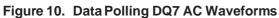

Data Polling Bit (DQ7). When Programming operations are in progress, this bit outputs the complement of the bit being programmed on DQ7. During Erase operation, it outputs a '0'. After completion of the operation, DQ7 will output the bit last programmed or a '1' after erasing. Data Polling is valid and only effective during P/E.C. operation, that is after the fourth  $\overline{W}$  pulse for programming or after the sixth  $\overline{W}$  pulse for erase. It must be performed at the address being programmed or at an address within the block being erased. If all the blocks selected for erasure are protected, DQ7 will be set to '0' for about  $100\mu s$ , and then return to the previous addressed memory data value. See Figure 11 for the Data Polling flowchart and Figure 10 for the Data Polling waveforms. DQ7 will also flag the Erase Suspend mode by switching from '0' to '1' at the start of the Erase Suspend. In order to

monitor DQ7 in the Erase Suspend mode an address within a block being erased must be provided. For a Read Operation in Erase Suspend mode, DQ7 will output '1' if the read is attempted on a block being erased and the data value on other blocks. During Program operation in Erase Suspend Mode, DQ7 will have the same behaviour as in the normal program execution outside of the suspend mode.

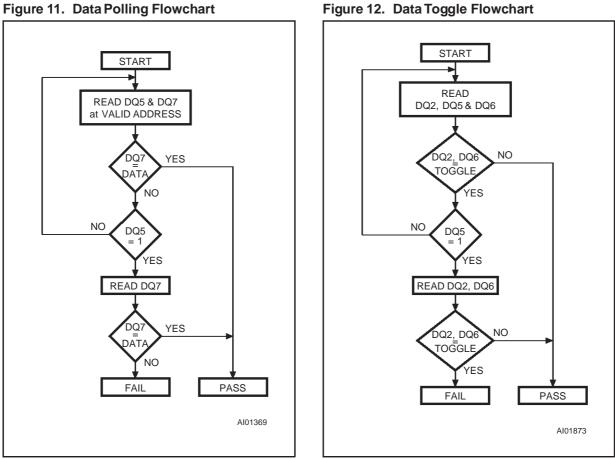

Toggle Bit (DQ6). When Programming or Erasing operations are in progress, successive attempts to read DQ6 will output complementary data. DQ6 will toggle following toggling of either  $\overline{G}$ , or  $\overline{E}$  when  $\overline{G}$ is low. The operation is completed when two successive reads yield the same output data. The next read will output the bit last programmed or a '1' after erasing. The toggle bit DQ6 is valid only during P/E.C. operations, that is after the fourth  $\overline{W}$  pulse for programming or after the sixth W pulse for Erase. If the blocks selected for erasure are protected, DQ6 will toggle for about 100µs and then return back to Read. DQ6 will be set to '1' if a Read operation is attempted on an Erase Suspendblock. When erase is suspended DQ6 will toggle during programming operations in a block different to the block in Erase Suspend. Either E or G toggling will cause DQ6 to toggle. See Figure 12 for Toggle Bit flowchart and Figure 13 for Toggle Bit waveforms.

| Hex Code | Command                                               |  |  |  |  |

|----------|-------------------------------------------------------|--|--|--|--|

| 00h      | Invalid/Reserved                                      |  |  |  |  |

| 10h      | Chip Erase Confirm                                    |  |  |  |  |

| 20h      | Reserved                                              |  |  |  |  |

| 30h      | Block Erase Resume/Confirm                            |  |  |  |  |

| 80h      | Set-up Erase                                          |  |  |  |  |

| 90h      | Read Electronic Signature/<br>Block Protection Status |  |  |  |  |

| A0h      | Program                                               |  |  |  |  |

| B0h      | Erase Suspend                                         |  |  |  |  |

| F0h      | Read Array/Reset                                      |  |  |  |  |

| Table 7. | Commands |  |

|----------|----------|--|

|----------|----------|--|

#### Table 8. Instructions<sup>(1)</sup>

| Mne.                | Instr.       | Cyc.        |             |       | 1st Cyc. | 2nd Cyc.                                                | 3rd Cyc.     | 4th Cyc.                                                         | 5th Cyc.                                 | 6th Cyc.      | 7th Cyc.   |  |

|---------------------|--------------|-------------|-------------|-------|----------|---------------------------------------------------------|--------------|------------------------------------------------------------------|------------------------------------------|---------------|------------|--|

|                     |              | 1+          | Addr. (3,7) |       | X        | ReadMerr                                                | ory Array u  | ntil a new w                                                     | rite cycle is                            | initiated     |            |  |

| RD <sup>(2,4)</sup> | Read/Reset   |             | Data        |       | F0h      | Read Memory Array until a new write cycle is initiated. |              |                                                                  |                                          |               |            |  |

| ΚD                  | Memory Array |             | Addr. (3,7) | Byte  | AAAAh    | 5555h                                                   | AAAAh        | DoodMor                                                          |                                          |               | rita avala |  |

|                     |              | 3+          | , luuri     | Word  | 5555h    | 2AAAh                                                   | 5555h        | is initiated.                                                    |                                          | intil a new v | Inte cycle |  |

|                     |              |             | Data        | -     | AAh      | 55h                                                     | F0h          |                                                                  |                                          |               |            |  |

|                     |              |             | Addr. (3,7) | Byte  | AAAAh    | 5555h                                                   | AAAAh        | Read Electronic Signature or Block                               |                                          |               | ck         |  |

| AS (4)              | Auto Select  | 3+          | , luuri     | Word  | 5555h    | 2AAAh                                                   | 5555h        | Protection Status until a new write initiated. See Note 5 and 6. |                                          |               |            |  |

|                     |              |             | Data        |       | AAh      | 55h                                                     | 90h          |                                                                  |                                          |               |            |  |

|                     |              | Addr. (3,7) | Byte        | AAAAh | 5555h    | AAAAh                                                   | Program      |                                                                  | a Polling or Toggle Bit<br>am completes. |               |            |  |

| PG                  | PG Program   | 4           | , laun      | Word  | 5555h    | 2AAAh                                                   | 5555h        |                                                                  |                                          |               |            |  |

|                     |              |             | Data        |       | AAh      | 55h                                                     | A0h          | Program<br>Data                                                  |                                          |               |            |  |

|                     |              |             | Addr. (3,7) | Byte  | AAAAh    | 5555h                                                   | AAAAh        | AAAAh                                                            | 5555h                                    | Block         | Additional |  |

| BE                  | Block Erase  | 6           | Addr.       | Word  | 5555h    | 2AAAh                                                   | 5555h        | 5555h                                                            | 2AAAh                                    | Address       | Block (8)  |  |

|                     |              |             | Data        | •     | AAh      | 55h                                                     | 80h          | AAh                                                              | 55h                                      | 30h           | 30h        |  |

|                     |              |             | Addr. (3,7) | Byte  | AAAAh    | 5555h                                                   | AAAAh        | AAAAh                                                            | 5555h                                    | AAAAh         |            |  |

| CE                  | Chip Erase   | 6           |             | Word  | 5555h    | 2AAAh                                                   | 5555h        | 5555h                                                            | 2AAAh                                    | 5555h         | Note 9     |  |

|                     |              |             | Data        | •     | AAh      | 55h                                                     | 80h          | AAh                                                              | 55h                                      | 10h           | ]          |  |

| ES (10)             | Erase        | 1           | Addr. (3,7) |       | Х        |                                                         | Toggle stop  |                                                                  |                                          |               | om any     |  |

| 20                  | Suspend      |             | Data        |       | B0h      | Block(s) no                                             | ot being era | sed then Re                                                      | esume Eras                               | е.            |            |  |

| ER                  | Erase        | 1           | Addr. (3,7) |       | х        | Read Data                                               | Polling or 1 | Γoggle Bits ι                                                    | until Erase o                            | completes o   | r Erase is |  |

| LIX                 | Resume       | '           | Data        |       |          | suspended                                               | another tin  | ne                                                               |                                          |               |            |  |

Notes: 1. Commands not interpreted in this table will default to read array mode.

2. A wait of t<sub>PLYH</sub> is necessary after a Read/Reset command if the memory was in an Erase or Program mode before starting any new operation (see Table 14 and Figure 9).

3. X = Don't Care.

4. The first cycles of the RD or AS instructions are followed by read operations. Any number of read cycles can occur after the command cycles.

5. Signature Address bits A0, A1, at VIL will output Manufacturer code (20h). Address bits A0 at VIH and A1, at VIL will output Device code.

Block Protection Address: A0, at V<sub>IL</sub>, A1 at V<sub>IH</sub> and A15-A18 within the Block will output the Block Protection status.

For Coded cycles address inputs A15-A18 are don't care.

8. Optional, additional Blocks addresses must be entered within the erase timeout delay after last write entry, timeout status

can be verified through DQ3 value (see Erase Timer Bit DQ3 description). When full command is entered, read Data Polling or Toggle bit until Erase is completed or suspended. 9. Read Data Polling, Toggle bits or RB until Erase completes. 10.During Erase Suspend, Read and Data Program functions are allowed in blocks not being erased.

| DQ | Name                     | Logic Level     | Definition                                                                                                                                             | Note                                                                                        |

|----|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|    |                          | '1'             | Erase Complete or erase block in Erase Suspend                                                                                                         |                                                                                             |

| 7  | Data                     | '0'             | Erase On-going                                                                                                                                         | Indicates the P/E.C. status, check during<br>Program or Erase, and on completion            |

| 7  | Polling                  | DQ              | Program Complete or data<br>of non erase block during<br>Erase Suspend                                                                                 | before checking bits DQ5 for Program or Erase Success.                                      |

|    |                          | DQ              | Program On-going                                                                                                                                       |                                                                                             |

|    |                          | '-1-0-1-0-1-'   | Erase or Program On-going                                                                                                                              | Successive reads output complementary                                                       |

| 6  | Toggle Bit               | DQ              | Program Complete                                                                                                                                       | data on DQ6 while Programming or Erase operations are on-going. DQ6 remains at              |

| 0  |                          | '-1-1-1-1-1-1-' | Erase Complete or Erase<br>Suspend on currently<br>addressed block                                                                                     | constant level when P/Ĕ.C. operations are<br>completed or Erase Suspend is<br>acknowledged. |

| 5  | Error Bit '1'<br>'0'     |                 | Program or Erase Error                                                                                                                                 | This bit is set to '1' in the case of                                                       |

| 0  |                          |                 | Program or Erase On-going                                                                                                                              | Programming or Erase failure.                                                               |

| 4  | Reserved                 |                 |                                                                                                                                                        |                                                                                             |

| 3  | Erase<br>Time Bit        | '1'             | Erase Timeout Period Expired                                                                                                                           | P/E.C. Erase operation has started. Only possible command entry is Erase Suspend (ES).      |

|    |                          | ,0,             | Erase Timeout Period<br>On-going                                                                                                                       | An additional block to be erased in parallel can be entered to the P/E.C.                   |

| 2  | '-1-0-1-0-<br>Toggle Bit |                 | Chip Erase, Erase or Erase<br>Suspend on the currently<br>addressed block.<br>Erase Error due to the<br>currently addressed block<br>(when DQ5 = '1'). | Indicates the erase status and allows to identify the erased block                          |

|    |                          | 1               | Program on-going, Erase<br>on-going on another block or<br>Erase Complete                                                                              | Identity the elased block                                                                   |

|    |                          | DQ              | Erase Suspend read on<br>non Erase Suspend block                                                                                                       |                                                                                             |

| 1  | Reserved                 |                 |                                                                                                                                                        |                                                                                             |

| 0  | Reserved                 |                 |                                                                                                                                                        |                                                                                             |

#### Table 9. Status Register Bits

Notes: Logic level '1' is High, '0' is Low. -0-1-0-0-0-1-1-1-0- represent bit value in successive Read operations.

57

| Mode                                                   | DQ7 | DQ6    | DQ2    |  |  |  |  |  |  |  |

|--------------------------------------------------------|-----|--------|--------|--|--|--|--|--|--|--|

| Program                                                | DQ7 | Toggle | 1      |  |  |  |  |  |  |  |

| Erase                                                  | 0   | Toggle | Note 1 |  |  |  |  |  |  |  |

| Erase Suspend Read<br>(in Erase Suspend<br>block)      | 1   | 1      | Toggle |  |  |  |  |  |  |  |

| Erase Suspend Read<br>(outside Erase Suspend<br>block) | DQ7 | DQ6    | DQ2    |  |  |  |  |  |  |  |

| Erase Suspend Program                                  | DQ7 | Toggle | N/A    |  |  |  |  |  |  |  |

| Table 10. Polling and Toggle | le Bits |  |

|------------------------------|---------|--|

|------------------------------|---------|--|

Note: 1. Toggle if the address is within a block being erased. '1' if the address is within a block not being erased.

**Toggle Bit (DQ2).** This toggle bit, together with DQ6, can be used to determine the device status during the Erase operations. It can also be used to identify the block being erased. During Erase or Erase Suspend a read from a block being erased will cause DQ2 to toggle. A read from a block not being erased will set DQ2 to '1' during erase and to DQ2 during Erase Suspend. During Chip Erase a read operation will cause DQ2 to toggle as all blocks are being erased. DQ2 will be set to '1' during program operation and when erase is complete. After erase completion and if the error bit DQ5 is set to '1', DQ2 will toggle if the faulty block is addressed.

**Error Bit (DQ5).** This bit is set to '1' by the P/E.C. when there is a failure of programming, block erase, or chip erase that results in invalid data in the memory block. In case of an error in block erase or program, the block in which the error occured or to which the programmed data belongs, must be discarded. The DQ5 failure condition will also appear if a user tries to programa '1' to a location that is previously programmed to '0'. Other Blocks may still be used. The error bit resets after a Read/Reset (RD) instruction. In case of success of Program or Erase, the error bit will be set to '0'.

**Erase Timer Bit (DQ3).** This bit is set to '0' by the P/E.C. when the last block Erase command has been entered to the Command Interface and it is awaiting the Erase start. When the erase timeout period is finished, after  $50\mu s$  to  $90\mu s$ , DQ3 returns to '1'.

#### **Coded Cycles**

The two Coded cycles unlock the Command Interface. They are followed by an input command or a confirmation command. The Coded cycles consist of writing the data AAh at address AAAAh in the Byte-wide configuration and at address 5555h in the Word-wide configuration during the first cycle. During the second cycle the Coded cycles consist of writing the data 55h at address 5555h in the Byte-wide configuration and at address 2AAAh in the Word-wide configuration. In the Byte-wide configuration the address lines A–1 to A14 are valid, in Word-wide A0 to A15 are valid, other address lines are 'don't care'. The Coded cycles happen on first and second cycles of the command write or on the fourth and fifth cycles.

#### Instructions

See Table 8.

**Read/Reset (RD) Instruction.** The Read/Reset instruction consists of one write cycle giving the command F0h. It can be optionally preceded by the two Coded cycles. Subsequent read operations will read the memory array addressed and output the data read. A wait state of 10µs is necessary after Read/Reset prior to any valid read if the memory was in an Erase mode when the RD instruction is given.

Auto Select (AS) Instruction. This instruction uses the two Coded cycles followed by one write cycle giving the command 90h to address AAAAh in the Byte-wide configuration or address 5555h in the Word-wide configuration for command set-up. A subsequent read will output the manufacturer code and the device code or the block protection status depending on the levels of A0 and A1. The manufacturer code, 20h, is output when the addresses lines A0 and A1 are Low, the device code, EEh for Top Boot, EFh for Bottom Boot is output when A0 is High with A1 Low.

The AS instruction also allows access to the block protection status. After giving the AS instruction, A0 is set to  $V_{IL}$  with A1 at  $V_{IH}$ , while A12-A18 define the address of the block to be verified. A read in these conditions will output a 01h if the block is protected and a 00h if the block is not protected.

Program (PG) Instruction. This instruction uses four write cycles. Both for Byte-wide configuration and for Word-wide configuration. The Program command A0h is written to address AAAAh in the Byte-wide configuration or to address 5555h in the Word-wide configuration on the third cycle after two Coded cycles. A fourth write operation latches the Address on the falling edge of  $\overline{W}$  or  $\overline{E}$  and the Data to be written on the rising edge and starts the P/E.C. Read operations output the Status Register bits after the programming has started. Memory programming is made only by writing '0' in place of '1'. Status bits DQ6 and DQ7 determine if programming is on-going and DQ5 allows verification of any possible error. Programming at an address not in blocks being erased is also possible during erase suspend. In this case, DQ2 will toggle at the address being programmed.

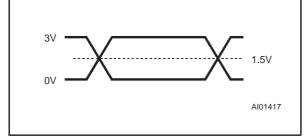

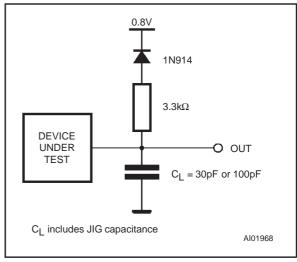

#### Table 11. AC Measurement Conditions

| Input Rise and Fall Times             | ≤ 10ns  |

|---------------------------------------|---------|

| Input Pulse Voltages                  | 0 to 3V |

| Input and Output Timing Ref. Voltages | 1.5V    |

#### Figure 4. AC Testing Input Output Waveform

#### Figure 5. AC Testing Load Circuit

#### Table 12. Capacitance<sup>(1)</sup> ( $T_A = 25 \circ C$ , f = 1 MHz)

| Symbol           | Parameter          | Test Condition | Min | Мах | Unit |

|------------------|--------------------|----------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0V$  |     | 6   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{OUT} = 0V$ |     | 12  | pF   |

Note: 1. Sampled only, not 100% tested.

#### Table 13. DC Characteristics

$(T_A = 0 \text{ to } 70^{\circ}C, -20 \text{ to } 85^{\circ}C \text{ or } -40 \text{ to } 85^{\circ}C; V_{CC} = 2.7 \text{V to } 3.6 \text{V})$

| Symbol              | Parameter                                      | Test Condition                                           | Min                   | Мах                   | Unit |

|---------------------|------------------------------------------------|----------------------------------------------------------|-----------------------|-----------------------|------|

| ILI                 | Input Leakage Current                          | $0V \leq V_{IN} \leq V_{CC}$                             |                       | ±1                    | μA   |

| I <sub>LO</sub>     | Output Leakage Current                         | $0V \le V_{OUT} \le V_{CC}$                              |                       | ±1                    | μA   |

| I <sub>CC1</sub>    | Supply Current (Read) Byte                     | $\overline{E} = V_{IL}, \overline{G} = V_{IH}, f = 6MHz$ |                       | 10                    | mA   |

| I <sub>CC1</sub>    | Supply Current (Read) Word                     | $\overline{E} = V_{IL}, \overline{G} = V_{IH}, f = 6MHz$ |                       | 10                    | mA   |

| I <sub>CC3</sub>    | Supply Current (Standby)                       | $\overline{E} = V_{CC} \pm 0.2V$                         |                       | 100                   | μΑ   |

| Icc4 <sup>(1)</sup> | Supply Current (Program or Erase)              | Byte program, Block or<br>Chip Erase in progress         |                       | 20                    | mA   |

| VIL                 | Input Low Voltage                              |                                                          | -0.5                  | 0.8                   | V    |

| V <sub>IH</sub>     | Input High Voltage                             |                                                          | 0.7 V <sub>CC</sub>   | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OL</sub>     | Output Low Voltage                             | I <sub>OL</sub> = 1.8mA                                  |                       | 0.45                  | V    |

| V <sub>OH</sub>     | Output High Voltage CMOS                       | I <sub>OH</sub> = −100μA                                 | V <sub>CC</sub> –0.4V |                       | V    |

| V <sub>ID</sub>     | A9 Voltage (Electronic Signature)              |                                                          | 11.5                  | 12.5                  | V    |

| I <sub>ID</sub>     | A9 Current (Electronic Signature)              | $A9 = V_{ID}$                                            |                       | 100                   | μA   |

| V <sub>LKO</sub>    | Supply Voltage (Erase and<br>Program lock-out) |                                                          | 2.0                   | 2.3                   | V    |

Note: 1. Sampled only, not 100% tested.

#### Table 14A. Read AC Characteristics

$(T_A = 0 \text{ to } 70^{\circ}C, -20 \text{ to } 85^{\circ}C \text{ or } -40 \text{ to } 85^{\circ}C)$

|                                        |                                        | e Parameter                                  |                                                               | M29W800T / M29W800B                       |                   |                                         |     |      |

|----------------------------------------|----------------------------------------|----------------------------------------------|---------------------------------------------------------------|-------------------------------------------|-------------------|-----------------------------------------|-----|------|

| Symbol                                 | Alt                                    |                                              | Test                                                          | -90                                       |                   | -1                                      | 00  | Unit |

| Symbol                                 |                                        |                                              | Condition                                                     | V <sub>CC</sub> = 3.0<br>C <sub>L</sub> = | V to 3.6V<br>30pF | $V_{CC} = 2.7V$ to 3.6V<br>$C_L = 30pF$ |     |      |

|                                        |                                        |                                              |                                                               | Min                                       | Max               | Min                                     | Max |      |

| t <sub>AVAV</sub>                      | t <sub>RC</sub>                        | Address Valid to Next<br>Address Valid       | $\frac{\overline{E}}{G} = V_{IL},$<br>$\overline{G} = V_{IL}$ | 90                                        |                   | 100                                     |     | ns   |

| t <sub>AVQV</sub>                      | t <sub>ACC</sub>                       | Address Valid to Output<br>Valid             | $\frac{\overline{E}}{G} = V_{IL},$<br>$\overline{G} = V_{IL}$ |                                           | 90                |                                         | 100 | ns   |

| t <sub>ELQX</sub> <sup>(1)</sup>       | t <sub>LZ</sub>                        | Chip Enable Low to<br>Output Transition      | $\overline{G} = V_{IL}$                                       | 0                                         |                   | 0                                       |     | ns   |

| t <sub>ELQV</sub> <sup>(2)</sup>       | t <sub>CE</sub>                        | Chip Enable Low to<br>Output Valid           | $\overline{G} = V_{IL}$                                       |                                           | 90                |                                         | 100 | ns   |

| $t_{GLQX}$ <sup>(1)</sup>              | t <sub>OLZ</sub>                       | Output Enable Low to<br>Output Transition    | $\overline{E} = V_{IL}$                                       | 0                                         |                   | 0                                       |     | ns   |

| t <sub>GLQV</sub> <sup>(2)</sup>       | t <sub>OE</sub>                        | Output Enable Low to<br>Output Valid         | $\overline{E} = V_{IL}$                                       |                                           | 35                |                                         | 40  | ns   |

| t <sub>EHQX</sub>                      | t <sub>OH</sub>                        | Chip Enable High to<br>Output Transition     | $\overline{G} = V_{IL}$                                       | 0                                         |                   | 0                                       |     | ns   |

| t <sub>EHQZ</sub> <sup>(1)</sup>       | t <sub>HZ</sub>                        | Chip Enable High to<br>Output Hi-Z           | $\overline{G} = V_{IL}$                                       |                                           | 30                |                                         | 30  | ns   |

| t <sub>GHQX</sub>                      | t <sub>OH</sub>                        | Output Enable High to<br>Output Transition   | $\overline{E} = V_{IL}$                                       | 0                                         |                   | 0                                       |     | ns   |

| t <sub>GHQZ</sub> <sup>(1)</sup>       | t <sub>DF</sub>                        | Output Enable High to<br>Output Hi-Z         | $\overline{E} = V_{IL}$                                       |                                           | 30                |                                         | 30  | ns   |

| t <sub>AXQX</sub>                      | t <sub>OH</sub>                        | Address Transition to<br>Output Transition   | $\frac{\overline{E}}{G} = V_{IL},$<br>$\overline{G} = V_{IL}$ | 0                                         |                   | 0                                       |     | ns   |

| t <sub>PLYH</sub> <sup>(1,3)</sup>     | t <sub>RRB</sub><br>t <sub>READY</sub> | RP Low to Read Mode                          |                                                               |                                           | 10                |                                         | 10  | μs   |

| t <sub>PHEL</sub>                      | t <sub>RH</sub>                        | RP High to Chip Enable<br>Low                |                                                               | 50                                        |                   | 50                                      |     | ns   |

| t <sub>PLPX</sub>                      | t <sub>RP</sub>                        | RP Pulse Width                               |                                                               | 500                                       |                   | 500                                     |     | ns   |

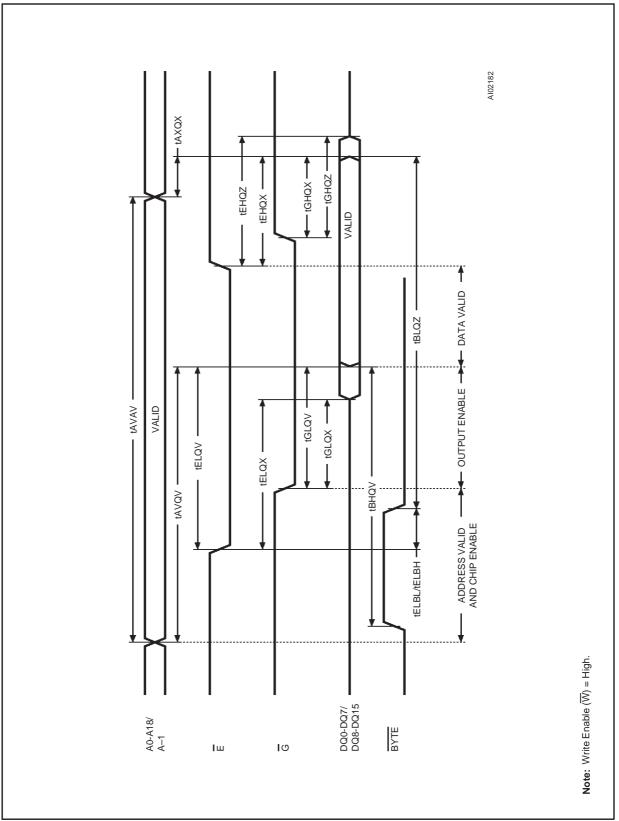

| t <sub>ELBL</sub><br>t <sub>ELBH</sub> | t <sub>ELFL</sub><br>t <sub>ELFH</sub> | Chip Enable to BYTE<br>Switching Low or High |                                                               |                                           | 5                 |                                         | 5   | ns   |

| <b>t</b> BLQZ                          | <b>t</b> FLQZ                          | BYTE Switching Low to<br>Output High Z       |                                                               |                                           | 50                |                                         | 50  | ns   |

| t <sub>BHQV</sub>                      | t <sub>FHQV</sub>                      | BYTE Switching High to<br>Output Valid       |                                                               |                                           | 50                |                                         | 50  | ns   |

Notes: 1. Sampled only, not 100% tested.

2. G may be delayed by up to t<sub>ELQV</sub> - t<sub>GLQV</sub> after the falling edge of E without increasing t<sub>ELQV</sub>.

3. To be considered only if the Reset pulse is given while the memory is in Erase or Program mode.

## Table 14B. Read AC Characteristics $(T_A = 0 \text{ to } 70^{\circ}\text{C}, -20 \text{ to } 85^{\circ}\text{C} \text{ or } -40 \text{ to } 85^{\circ}\text{C})$

|                                        |                                        | Parameter                                    |                                                     | M29W800T / M29W800B                      |     |                                                          |     |      |

|----------------------------------------|----------------------------------------|----------------------------------------------|-----------------------------------------------------|------------------------------------------|-----|----------------------------------------------------------|-----|------|

| Symbol                                 | Alt                                    |                                              | Test                                                | -120                                     |     | -1                                                       | 50  | Unit |

| Symbol                                 | AII                                    | Falameter                                    | Condition                                           | $V_{CC}$ = 2.7V to 3.6V<br>$C_L$ = 100pF |     | V <sub>CC</sub> = 2.7V to 3.6V<br>C <sub>L</sub> = 100pF |     |      |

|                                        |                                        |                                              |                                                     | Min                                      | Мах | Min                                                      | Мах |      |

| t <sub>AVAV</sub>                      | t <sub>RC</sub>                        | Address Valid to Next<br>Address Valid       | $\overline{E} = V_{IL},$<br>$\overline{G} = V_{IL}$ | 120                                      |     | 150                                                      |     | ns   |

| t <sub>AVQV</sub>                      | t <sub>ACC</sub>                       | Address Valid to Output<br>Valid             | $\overline{E} = V_{IL},$<br>$\overline{G} = V_{IL}$ |                                          | 120 |                                                          | 150 | ns   |

| t <sub>ELQX</sub> <sup>(1)</sup>       | t <sub>LZ</sub>                        | Chip Enable Low to<br>Output Transition      | $\overline{G} = V_{IL}$                             | 0                                        |     | 0                                                        |     | ns   |

| t <sub>ELQV</sub> <sup>(2)</sup>       | t <sub>CE</sub>                        | Chip Enable Low to<br>Output Valid           | $\overline{G} = V_{IL}$                             |                                          | 120 |                                                          | 150 | ns   |

| t <sub>GLQX</sub> <sup>(1)</sup>       | t <sub>OLZ</sub>                       | Output Enable Low to<br>Output Transition    | $\overline{E} = V_{IL}$                             | 0                                        |     | 0                                                        |     | ns   |

| $t_{GLQV}$ <sup>(2)</sup>              | t <sub>OE</sub>                        | Output Enable Low to<br>Output Valid         | $\overline{E} = V_{IL}$                             |                                          | 50  |                                                          | 55  | ns   |

| t <sub>EHQX</sub>                      | t <sub>OH</sub>                        | Chip Enable High to<br>Output Transition     | $\overline{G} = V_{IL}$                             | 0                                        |     | 0                                                        |     | ns   |

| t <sub>EHQZ</sub> <sup>(1)</sup>       | t <sub>HZ</sub>                        | Chip Enable High to<br>Output Hi-Z           | $\overline{G} = V_{IL}$                             |                                          | 30  |                                                          | 40  | ns   |

| t <sub>GHQX</sub>                      | t <sub>он</sub>                        | Output Enable High to<br>Output Transition   | $\overline{E} = V_{IL}$                             | 0                                        |     | 0                                                        |     | ns   |

| t <sub>GHQZ</sub> <sup>(1)</sup>       | t <sub>DF</sub>                        | Output Enable High to<br>Output Hi-Z         | $\overline{E} = V_{IL}$                             |                                          | 30  |                                                          | 40  | ns   |

| t <sub>AXQX</sub>                      | t <sub>ОН</sub>                        | Address Transition to<br>Output Transition   | $\overline{E} = V_{IL},$<br>$\overline{G} = V_{IL}$ | 0                                        |     | 0                                                        |     | ns   |

| t <sub>PLYH</sub> <sup>(1,3)</sup>     | t <sub>RRB</sub><br>t <sub>READY</sub> | RP Low to Read Mode                          |                                                     |                                          | 10  |                                                          | 10  | μs   |

| t <sub>PHEL</sub>                      | t <sub>RH</sub>                        | RP High to Chip Enable<br>Low                |                                                     | 50                                       |     | 50                                                       |     | ns   |

| t <sub>PLPX</sub>                      | t <sub>RP</sub>                        | RP Pulse Width                               |                                                     | 500                                      |     | 500                                                      |     | ns   |

| t <sub>ELBL</sub><br>t <sub>ELBH</sub> | t <sub>ELFL</sub><br>t <sub>ELFH</sub> | Chip Enable to BYTE<br>Switching Low or High |                                                     |                                          | 5   |                                                          | 5   | ns   |

| t <sub>BLQZ</sub>                      | t <sub>FLQZ</sub>                      | BYTE Switching Low to<br>Output High Z       |                                                     |                                          | 60  |                                                          | 60  | ns   |

| t <sub>BHQV</sub>                      | t <sub>FHQV</sub>                      | BYTE Switching High to<br>Output Valid       |                                                     |                                          | 60  |                                                          | 60  | ns   |

Notes: 1. Sampled only, not 100% tested.

2. G may be delayed by up to t<sub>ELQV</sub> - t<sub>GLQV</sub> after the falling edge of E without increasing t<sub>ELQV</sub>.

3. To be considered only if the Reset pulse is given while the memory is in Erase or Program mode.

#### M29W800T, M29W800B

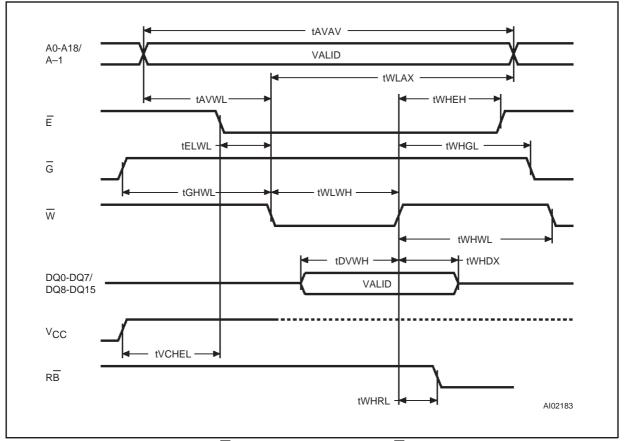

## Table 15A. Write AC Characteristics, Write Enable Controlled (T<sub>A</sub> = 0 to 70°C, -20 to 85°C or -40 to 85°C)

|                                     |                   |                                         |                                                         | M29W800T / | / M29W800B                                       | 1   |      |

|-------------------------------------|-------------------|-----------------------------------------|---------------------------------------------------------|------------|--------------------------------------------------|-----|------|

| Symbol                              | Alt               | Parameter                               | -90                                                     |            | -100                                             |     | Unit |

| Symbol                              |                   | i arameter                              | V <sub>CC</sub> = 3.0V to 3.6V<br>C <sub>L</sub> = 30pF |            | $V_{CC} = 2.7V \text{ to } 3.6V$<br>$C_L = 30pF$ |     |      |

|                                     |                   |                                         | Min                                                     | Max        | Min                                              | Мах | 1    |

| t <sub>AVAV</sub>                   | t <sub>WC</sub>   | Address Valid to Next Address Valid     | 90                                                      |            | 100                                              |     | ns   |

| telwl                               | tcs               | Chip Enable Low to Write Enable Low     | 0                                                       |            | 0                                                |     | ns   |

| t <sub>WLWH</sub>                   | t <sub>WP</sub>   | Write Enable Low to Write Enable High   | 45                                                      |            | 50                                               |     | ns   |

| t <sub>DVWH</sub>                   | t <sub>DS</sub>   | Input Valid to Write Enable High        | 45                                                      |            | 50                                               |     | ns   |

| t <sub>WHDX</sub>                   | t <sub>DH</sub>   | Write Enable High to Input Transition   | 0                                                       |            | 0                                                |     | ns   |

| t <sub>WHEH</sub>                   | t <sub>CH</sub>   | Write Enable High to Chip Enable High   | 0                                                       |            | 0                                                |     | ns   |

| t <sub>WHWL</sub>                   | t <sub>WPH</sub>  | Write Enable High to Write Enable Low   | 30                                                      |            | 30                                               |     | ns   |

| t <sub>AVWL</sub>                   | t <sub>AS</sub>   | Address Valid to Write Enable Low       | 0                                                       |            | 0                                                |     | ns   |

| t <sub>WLAX</sub>                   | t <sub>AH</sub>   | Write Enable Low to Address Transition  | 45                                                      |            | 50                                               |     | ns   |

| t <sub>GHWL</sub>                   |                   | Output Enable High to Write Enable Low  | 0                                                       |            | 0                                                |     | ns   |

| tvchel                              | tvcs              | V <sub>CC</sub> High to Chip Enable Low | 50                                                      |            | 50                                               |     | μs   |

| t <sub>WHGL</sub>                   | t <sub>OEH</sub>  | Write Enable High to Output Enable Low  | 0                                                       |            | 0                                                |     | ns   |

| t <sub>PHPHH</sub> <sup>(1,2)</sup> | t <sub>VIDR</sub> | RP Rise Time to VID                     | 500                                                     |            | 500                                              |     | ns   |

| t <sub>PLPX</sub>                   | t <sub>RP</sub>   | RP Pulse Width                          | 500                                                     |            | 500                                              |     | ns   |

| t <sub>WHRL</sub> <sup>(1)</sup>    | t <sub>BUSY</sub> | Program Erase Valid to RB Delay         |                                                         | 90         |                                                  | 90  | ns   |

| t <sub>PHWL</sub> <sup>(1)</sup>    | t <sub>RSP</sub>  | RP High to Write Enable Low             | 4                                                       |            | 4                                                |     | μs   |

Notes: 1. Sample only, not 100% tested. 2. This timing is for Temporary Block Unprotection operation.

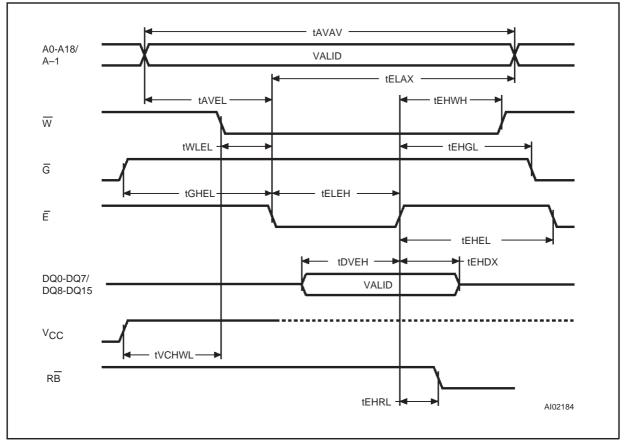

#### Table 15B. Write AC Characteristics, Write Enable Controlled

$(T_A = 0 \text{ to } 70^{\circ}C, -20 \text{ to } 85^{\circ}C \text{ or } -40 \text{ to } 85^{\circ}C)$

|                                     |                   |                                         | M29W800T / M29W800B |                     |     |                     |      |

|-------------------------------------|-------------------|-----------------------------------------|---------------------|---------------------|-----|---------------------|------|

| Symbol                              | Alt               | Parameter                               | -120                |                     | -1  | 50                  | Unit |

| Gymbol                              |                   | i arameter                              |                     | 7V to 3.6V<br>100pF |     | 'V to 3.6V<br>100pF |      |