# PROGRAMMABLE CODEC/FILTER COMBO 2ND GENERATION

- COMPLETE CODEC AND FILTER SYSTEM INCLUDING:

- TRANSMIT AND RECEIVE PCM CHANNEL FILTERS

- μ-LAW OR A-LAW COMPANDING CODER AND DECODER

- RECEIVE POWER AMPLIFIER DRIVES  $300\,\Omega$

- 4.096 MHz SERIAL PCM DATA (max)

- PROGRAMMABLE FUNCTIONS :

- TRANSMIT GAIN: 25.4 dB RANGE, 0.1 dB STEPS

- RECEIVE GAIN: 25.4 dB RANGE, 0.1 dB STEPS

- HYBRID BALANCE CANCELLATION FILTER

- TIME-SLOT ASSIGNMENT: UP TO 64 SLOTS/FRAME

- 2 PORT ASSIGNMENT (TS5070)

- 6 INTERFACE LATCHES (TS5070)

- A OR μ-LAW

- ANALÖG LOOPBACK

- DIGITAL LOOPBACK

- DIRECT INTERFACE TO SOLID-STATE SLICs

- SIMPLIFIES TRANSFORMER SLIC, SINGLE WINDING SECONDARY

- STANDARD SERIAL CONTROL INTERFACE

- 80 mW OPERATING POWER (typ)

- 1.5mW STANDBY POWER (typ)

- MEETS OR EXCEEDS ALL CCITT AND LSSGR SPECIFICATIONS

- TTL AND CMOS COMPATIBLE DIGITAL IN-TERFACES

## **DESCRIPTION**

The TS5070 series are the second generation combined PCM CODEC and Filter devices optimized for digital switching applications on subscriber and trunk line cards.

Using advanced switched capacitor techniques the TS5070 and TS5071 combine transmit bandpass and receive lowpass channel filters with a companding PCM encoder and decoder. The devices are A-law and  $\mu$ -law selectable and employ a conventional serial PCM interface capable of being clocked up to 4.096 MHz. A number of programmable functions may be controlled via a serial control port.

Channel gains are programmable over a 25.4 dB range in each direction, and a programmable filter is included to enable Hybrid Balancing to be adjusted to suit a wide range of loop impedance conditions.

Both transformer and active SLIC interface circuits with real or complex termination impedances can be balanced by this filter, with cancellation in excess of 30 dB being readily achievable when measured across the passbandagainst standardtest termination networks.

To enable COMBO IIG to interface to the SLIC control leads, a number of programmable latches are included; each may be configured as either an input or an output. The TS5070 provides 6 latches and the TS5071 5 latches.

December 1997 1/32

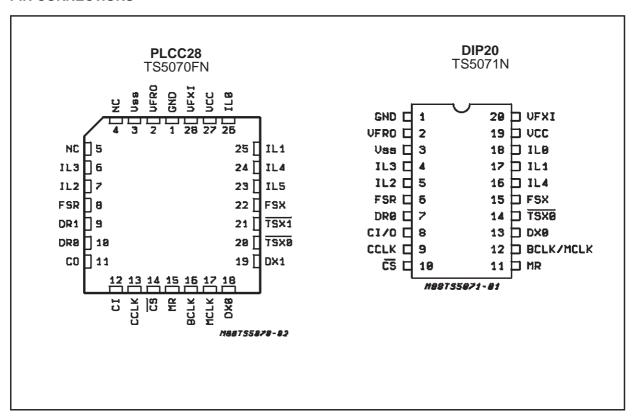

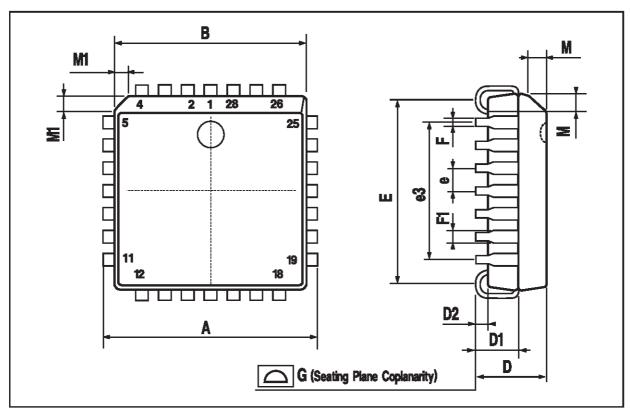

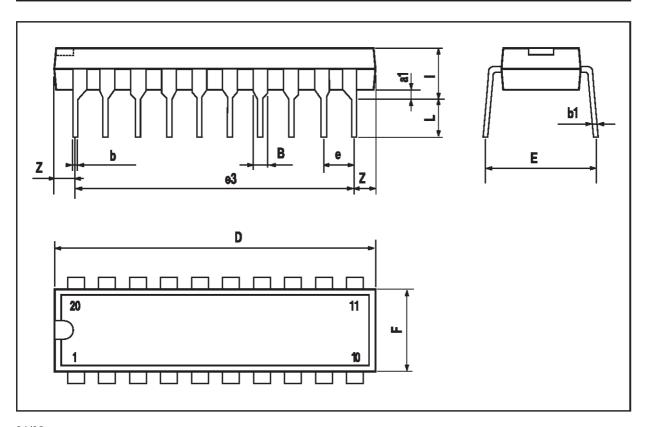

# **TS5070 PIN FUNCTIONALITY (PLCC28)**

| No. | Name                                        | Function                                                |

|-----|---------------------------------------------|---------------------------------------------------------|

| 1   | GND                                         | Ground Input (+0V)                                      |

| 2   | VF <sub>R</sub> 0                           | Analog Output                                           |

| 3   | $V_{SS}$                                    | Supply Input (-5V)                                      |

| 4   | NC                                          | Not Connected                                           |

| 5   | NC                                          | Not Connected                                           |

| 6   | IL3                                         | Digital Input or Output defined by LDR register content |

| 7   | IL2                                         | Digital Input or Output defined by LDR register content |

| 8   | $FS_R$                                      | Digital input                                           |

| 9   | D <sub>R</sub> 1                            | Digital input sampled by BCLK falling edge              |

| 10  | $D_R0$                                      | Digital input sampled by BCLK falling edge              |

| 11  | CO                                          | Digital output (shifted out on CCLK rising edge)        |

| 12  | CI                                          | Digital input (sampled on CCLK falling edge)            |

| 13  | C <u>CL</u> K                               | Digital input (clock)                                   |

| 14  | CS                                          | Digital input (chip select for CI/CO)                   |

| 15  | MR                                          | Digital Input                                           |

| 16  | BCLK                                        | Digital input (clock)                                   |

| 17  | MCLK                                        | Digital input                                           |

| 18  | D <sub>X</sub> 0                            | Digital output clocked by BCLK rising edge              |

| 19  | <u>D<sub>X</sub>1</u>                       | Digital output clocked by BCLK rising edge              |

| 20  | <u>TS<sub>X</sub>0</u><br>TS <sub>X</sub> 1 | Open drain output (pulled low by active DX0 time slot)  |

| 21  | TS <sub>X</sub> 1                           | Open drain output (pulled low by active DX1 time slot)  |

| 22  | FS <sub>X</sub>                             | Digital input                                           |

| 23  | IL5                                         | Digital input or output defined by LDR register content |

| 24  | IL4                                         | Digital input or output defined by LDR register content |

| 25  | IL1                                         | Digital input or output defined by LDR register content |

| 26  | IL0                                         | Digital input or output defined by LDR register content |

| 27  | V <sub>CC</sub>                             | Supply input (+5V)                                      |

| 28  | VF <sub>X</sub> I                           | Analog input                                            |

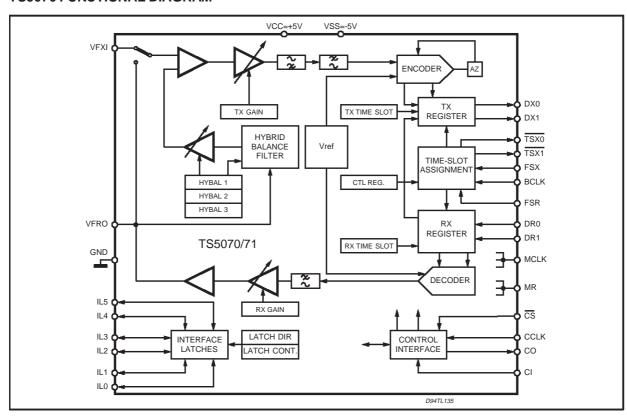

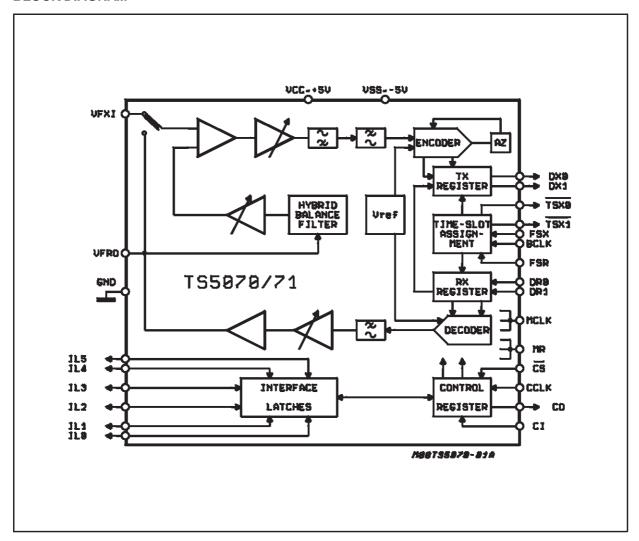

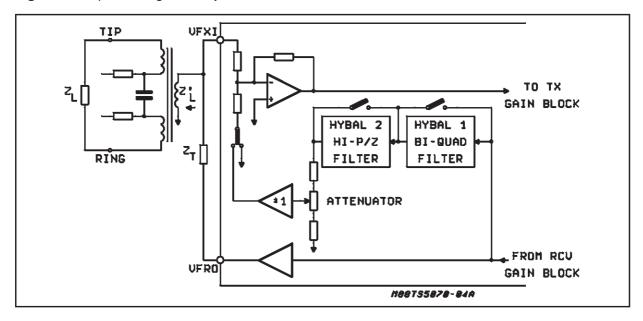

# **TS5070 FUNCTIONAL DIAGRAM**

# **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                                      | Value                              | Unit |

|-------------------|------------------------------------------------|------------------------------------|------|

| V <sub>CC</sub>   | V <sub>CC</sub> to GND                         | 7                                  | V    |

| V <sub>SS</sub>   | V <sub>SS</sub> to GND                         | <b>-</b> 7                         | V    |

|                   | Voltage at VFXI                                | $V_{CC}$ + 0.5 to $V_{SS}$ – 0.5   | V    |

| V <sub>IN</sub>   | Voltage at Any Digital Input                   | V <sub>CC</sub> + 0.5 to GND – 0.5 | V    |

|                   | Current at VFRO                                | ± 100                              | mA   |

| Io                | Current at Any Digital Output                  | ± 50                               | mA   |

| T <sub>stg</sub>  | Storage Temperature Range                      | −65, <b>+</b> 150                  | °C   |

| T <sub>lead</sub> | Lead Temperature Range (soldering, 10 seconds) | 300                                | °C   |

# **PIN CONNECTIONS**

# POWER SUPPLY, CLOCK

| Name            | Pin<br>Type | TS5070<br>FN | TS5071<br>N | Function               | Description                                                                                                                                                                                                                                 |

|-----------------|-------------|--------------|-------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc             | S           | 27           | 19          | Positive Power         | + 5 V ± 5 %                                                                                                                                                                                                                                 |

| V <sub>SS</sub> | S           | 3            | 3           | Supply<br>Negative     | -5 V ± 5 %                                                                                                                                                                                                                                  |

| GND             | S           | 1            | 1           | Power Supply<br>Ground | All analog and digital signals are referenced to this pin.                                                                                                                                                                                  |

| BCLK            | I           | 16           | 12          | Bit Clock              | Bit clock input used to shift PCM data into and out of the $D_R$ and $D_X$ pins. BCLK may vary from 64 kHz to 4.096 MHz in 8 kHz increments, and must be synchronous with MCLK (TS5071 only).                                               |

| MCLK            | I           | 17           | 12          | Master Clock           | Master clock input used by the switched capacitor filters and the encoder and decoder sequencing logic. Must be 512 kHz, 1.536/1.544 MHz, 2.048 MHz or 4.096 MHz and synchronous with BCLK. BCLK and MCLK are wired together in the TS5071. |

# TRANSMIT SECTION

| Name                                   | Pin<br>Type | TS5070<br>FN | TS5071<br>N | Function                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------|-------------|--------------|-------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FS <sub>X</sub>                        | _           | 22           | 15          | Transmit<br>Frame Sync. | Normally a pulse or squarewave waveform with an 8 kHz repetition rate is applied to this input to define the start of the transmit time-slot assigned to this device (non-delayed data mode) or the start of the transmit frame (delayed data mode using the internal time-slot assignment counter).                                                                                                                                                                                                                                                        |

| VF <sub>X</sub> I                      | -           | 28           | 20          | Transmit<br>Analog      | This is a high–impedance input. Voice frequency signals present on this input are encoded as an A–law or $\mu$ –law PCM bit stream and shifted out on the selected D <sub>X</sub> pin.                                                                                                                                                                                                                                                                                                                                                                      |

| D <sub>X</sub> 0<br>D <sub>X</sub> 1   | 0 0         | 18<br>19     | 13<br>-     | Transmit Data           | $D_X1$ is available on the TS5070 only, $D_X0$ is available on all devices. These transmit data TRI–STATE® outputs remain in the high impedance state except during the assigned transmit time—slot on the assigned port, during which the transmit PCM data byte is shifted out on the rising edges of BCLK.                                                                                                                                                                                                                                               |

| TS <sub>X</sub> 0<br>TS <sub>X</sub> 1 | 0           | 20<br>21     | 14<br>-     | Transmit<br>Time-slot   | $\overline{\frac{TS_{\chi}1}{TS_{\chi}0}} \ is \ available \ on \ the \ TS5070 \ only.$ $\overline{TS_{\chi}0} \ is \ available \ on \ all \ devices. \ Normally \ these \ opendrain \ outputs \ are \ floating \ in \ a high impedance \ state \ except \ when \ a time-slot \ \underline{is} \ \underline{active} \ on \ one \ of \ the \ D_{\chi} \ outputs, \ when \ the \ apppropriate \ \overline{TS_{\chi}} \ output \ pulls \ low \ to \ enable \ a \ backplane \ line-driver. \ Should \ be \ strapped \ to \ ground \ (GND) \ when \ not \ used.$ |

# RECEIVE SECTION

| Name                                 | Pin<br>Type | TS5070<br>FN | TS5071<br>N | Function               | Description                                                                                                                                                                                                                                                                                         |

|--------------------------------------|-------------|--------------|-------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FS <sub>R</sub>                      | _           | 8            | 6           | Receive Frame<br>Sync. | Normally a pulse or squarewave waveform with an 8 kHz repetition rate is applied to this input to define the start of the receive time—slot assigned to this device (non-delayed frame mode) or the start of the receive frame (delayed frame mode using the internal time-slot assignment counter. |

| VF <sub>R</sub> 0                    | 0           | 2            | 2           | Receive Analog         | The receive analog power amplifier output, capable of driving load impedances as low as $300\Omega$ (depending on the peak overload level required). PCM data received on the assigned D <sub>R</sub> pin is decoded and appears at this output as voice frequency signals.                         |

| D <sub>R</sub> 0<br>D <sub>R</sub> 1 |             | 10<br>9      | 7 –         | Receive Data           | $D_R1$ is available on the TS5070 only, $D_R0$ is available on all devices. These receive data input(s) are inactive except during the assigned receive time—slot of the assigned port when the receive PCM data is shifted in on the falling edges of BCLK.                                        |

#### INTERFACE, CONTROL, RESET

| Name                                   | Pin<br>Type                            | TS5070<br>FN                   | TS5071<br>N                   | Function                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|----------------------------------------|----------------------------------------|--------------------------------|-------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| IL5<br>IL4<br>IL3<br>IL2<br>IL1<br>IL0 | 1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0 | 23<br>24<br>6<br>7<br>25<br>26 | -<br>16<br>4<br>5<br>17<br>18 | Interface<br>Latches         | IL5 through IL0 are available on the TS5070, IL4 through IL0 are available on the TS5071. Each interface Latch I/O pin may be individually programmed as an input or an output determined by the state of the corresponding bit in the Latch Direction Register (LDR) . For pins configured as inputs, the logic state sensed on each input is latched into the interface Latch Register (ILR) whenever control data is written to COMBO IIG, while CS is low, and the information is shifted out on the CO (or CI/O) pin. When configured as outputs, control data written into the ILR appears at the corresponding IL pins. |  |  |  |  |

| CCLK                                   | -                                      | 13                             | 9                             | Control Clock                | This clock shifts serial control information into or out of CI or CO (or CI/O) when the CS input is low depending on the current instruction. CCLK may be asynchronous with the other system clocks.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| CI/O                                   | I/O                                    | -                              | 8                             | Control Data<br>Input/output | This is Control Data I/O pin wich is provided on the TS5071. Serial control information is shifted into or out of COMBO IIG on this pin when CS is low. The direction of the data is determined by the current instruction as defined in Table 1.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| CI                                     | 1                                      | 12                             | _                             | Control Data                 | These are separate controls, availables only on the TS5070. They can be wired together if required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| СО                                     | 0                                      | 11                             | -                             | Control Data<br>Output       | 133070. They cambe whed together in required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| CS                                     | 1                                      | 14                             | 10                            | Chip Select                  | When this pins is low, control information can be written to or read from the COMBO IIG via the CI and CO pins (or CI/O).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| MR                                     | I                                      | 15                             | 11                            | Master Reset                 | This logic input must be pulled low for normal operation of COMBO IIG. When pulled momentarily high, all programmable registers in the device are reset to the states specified under "Power–on Initialization".                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

## **FUNCTIONAL DESCRIPTION**

## POWER-ON INITIALIZATION

When power is first applied, power-on reset circuitry initializes COMBO IIG and puts it into the power-down state. The gain control registers for the transmit and receive gain sections are programmed for no output, the hybrid balance circuit is turned off, the power amp is disabled and the device is in the non-delayed timing mode. The Latch Direction Register (LDR) is pre-set with all IL pins programmed as inputs, placing the SLIC interface pins in a high impedance state. The

CI/O pin is set as an input ready for the first control byte of the initialization sequence. Other initial states in the Control Register are indicated in Table 2.

A reset to these same initial conditions may also be forced by driving the MR pin momentarily high. This may be done either when powered-up or down. For normal operation this pin must be pulled low. If not used, MR should be hard-wired to ground.

The desired modes for all programmable functions may be initialized via the control port prior to a Power-up command.

#### **POWER-DOWN STATE**

Following a period of activity in the powered-up state the power-down state may be re-entered by writing any of the control instructions into the serial control port with the "P" bit set to "1" It is recommended that the chip be powered down before writing any additional instructions. In the power-down state, all non-essential circuitry is de-activated and the  $D_{\rm X}0$  and  $D_{\rm X}1$  outputs are in the high impedance TRI-STATE condition.

The coefficients stored in the Hybrid Balance circuit and the Gain Control registers, the data in the LDR and ILR, and all control bits remain unchanged in the power-down state unless changed by writing new data via the serial control port, which remains operational. The outputs of the Interface Latches also remain active, maintaining the ability to monitor and control a SLIC.

## TRANSMIT FILTER AND ENCODER

The Transmit section input, VF<sub>X</sub>I, is a high impedance summing input which is used as the differencing point for the internal hybrid balance cancellation signal. No external components are needed to set the gain. Following this circuit is a programmable gain/attenuationamplifier which is controlled by the contents of the Transmit Gain Register (see Programmable Functions section). An active prefilter then precedes the 3rd order high-pass and 5th order low-pass switched capacitor filters. The A/D converter has a compressing characteristic according to the standard CCITT A or µ255 coding laws, which must be selected by a control instruction during initialization (see table 1 and 2). A precision onchip voltage reference ensures accurate and highly stable transmission levels. Any offset voltage arising in the gain-set amplifier, the filters or the comparator is cancelled by an internal auto-zero circuit. Each encode cycle begins immediately following the assigned Transmit time-slot. The total signal delay referenced to the start of the time-slot is approximately 165 µs (due to the Transmit Filter) plus 125 µs (due to encoding delay), which totals 290  $\mu$ s. Data is shifted out on D<sub>X</sub>0 or D<sub>X</sub>1 during the selected time slot on eight rising edges of

## DECODER AND RECEIVE FILTER

BCLK.

PCM data is shifted into the Decoder's Receive PCM Register via the  $D_R0$  or  $D_R1$  pin during the selected time-slot on the 8 falling edges of BCLK. The Decoder consists of an expanding DAC with either A or  $\mu255$  law decoding characteristic, which is selected by the same control instruction used to select the Encode law during initialization. Following the Decoder is a 5th order low-pass switched capacitor filter with integral Sin x/x correction for the 8 kHz sample and hold. A programmable gain amplifier, which must be set by writing to the Receive Gain

Register, is included, and finally a Post-Filter/Power Amplifier capable of driving a 300  $\Omega$  load to  $\pm$  3.5 V, a 600  $\Omega$  load to  $\pm$  3.8 V or 15 k $\Omega$  load to  $\pm$  4.0 V at peak overload.

A decode cycle begins immediately after each receive time-slot, and 10  $\mu$ s later the Decoder DAC output is updated. The total signal delay is 10  $\mu$ s plus 120  $\mu$ s (filter delay) plus 62.5  $\mu$ s (1/2 frame) which gives approximately 190  $\mu$ s.

#### **PCM INTERFACE**

The FSx and FSR frame sync inputs determine the beginning of the 8-bit transmit and receive time-slots respectively. They may have any duration from a single cycle of BCLK to one MCLK period LOW. Two different relationships may be established between the frame sync inputs and the actual time-slots on the PCM busses by setting bit 3 in the Control Register (see table 2). Non delayed data mode is similar to long-frame timing on the ETC5050/60 series of devices: time-slots being nominally coincident with the rising edge of the appropriate FS input. The alternative is to use Delayed Data mode which is similar to short-frame sync timing, in which each FS input must be high at least a half-cycle of BCLK earlier than the time-slot.

The Time-Slot Assignment circuit on the device can only be used with Delayed Data timing. When using Time-Slot Assignment, the beginning of the first time-slot in a frame is identified by the appropriate FS input. The actual transmit and receive time-slots are then determined by the internal Time-Slot Assignment counters. Transmit and Receive frames and time-slots may be skewed from each other by any number of BCLK cycles.

During each assigned transmit time-slot, the selected  $D_X0/1$  output shifts data out from the PCM register on the rising edges of BCLK.  $TS_X0$  (or  $TS_X1$  as appropriate) also pulls low for the first 7 1/2 bit times of the time-slot to control the TRI-STATE Enable of a backplane line driver. Serial PCM data is shifted into the selected  $D_R0/1$  input during each assigned Receive time slot on the falling edges of BCLK.  $D_X0$  or  $D_X1$  and  $D_R0$  or  $D_R1$  are selectable on the TS5070 only.

# SERIAL CONTROL PORT

Control information and data are written into or readback from COMBO IIG via the serial control port consisting of the control clock CCLK; the serial data input/output CI/O (or separate input CI, and output CO on the TS5070 only); and the Chip Select input CS. All control instructions require 2 bytes, as listed in table 1, with the exception of a single byte power-up/down command. The byte 1 bits are used as follows: bit 7 specifies power-up or power-down; bits 6, 5, 4 and 3 specify the register address; bit 2 specifies whether the instructions is read or write; bit 1 specifies a one or two byte in-

struction; and bit 0 is not used. To shift control data into COMBO IIG, CCLK must be pulsed high 8 times while  $\overline{CS}$  is low. Data on the CI or CI/O input is shifted into the serial input register on the falling edge of each CCLK pulse. After all data is shifted in, the contents of the input shift register are decoded, and may indicate that a 2nd byte of control data will follow. This second byte may either be defined by a second byte-wide  $\overline{CS}$  pulse or may follow the first continuously, i.e. it is not mandatory for  $\overline{CS}$  to return high in between the first and second control bytes. On the falling edge of the 8<sup>th</sup> CCLK clock pulse in the 2nd control byte the data is loaded into the appropriate programmable register.  $\overline{CS}$  may remain low continuously when programming succes-

sive registers, if desired. However  $\overline{CS}$  should be set high when no data transfers are in progress.

To readbackinterface Latch data or status information from COMBO IIG, the first byte of the appropriate instruction is strobed in during the first CS pulse, as defined in table 1. CS must then be taken low for a further 8 CCLK cycles, during which the data is shifted onto the CO or CI/O pin on the rising edges of CCLK. When CS is high the CO or CI/O pin is in the high-impedance TRI-STATE, enabling the CI/O pins of many devices to be multiplexed together. Thus, to summarize, 2-byte READ and WRITE instructions may use either two 8-bit wide CS pulses or a single 16-bit wide CS pulse.

Table 1: Programmable Register Instructions

|                                                                       |        |        |        | Byt    | e 1    |        |        |   | D. ( . 0                     |

|-----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|---|------------------------------|

| Function                                                              | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0 | Byte 2                       |

| Single Byte Power–up/down                                             | Р      | Х      | Х      | Х      | Х      | Х      | 0      | Χ | None                         |

| Write Control Register<br>Read-back Control Register                  | P<br>P | 0      | 0      | 0      | 0      | 0<br>1 | 1<br>1 | X | See Table 2<br>See Table 2   |

| Write Latch Direction Register (LDR)<br>Read Latch Direction Register | P<br>P | 0      | 0      | 1<br>1 | 0      | 0<br>1 | 1<br>1 | X | See Table 4<br>See Table 4   |

| Write Latch Content Register (ILR)<br>Read Latch Content Register     | P<br>P | 0      | 0      | 0      | 1<br>1 | 0<br>1 | 1<br>1 | X | See Table 5<br>See Table 5   |

| Write Transmit Time-slot/port<br>Read-back Transmit Time-slot/port    | P<br>P | 1<br>1 | 0      | 1      | 0      | 0<br>1 | 1      | X | See Table 6<br>See Table 6   |

| Write Receive Time-slot/port<br>Read-back Receive Time-slot/port      | P<br>P | 1<br>1 | 0      | 0      | 1<br>1 | 0<br>1 | 1      | X | See Table 6<br>See Table 6   |

| Write Transmit Gain Register<br>Read Transmit Gain Register           | P<br>P | 0      | 1<br>1 | 0      | 1<br>1 | 0<br>1 | 1      | X | See Table 7<br>See Table 7   |

| Write Receive Gain Register<br>Read Receive Gain Register             | P<br>P | 0      | 1      | 0      | 0      | 0<br>1 | 1      | X | See Table 8<br>See Table 8   |

| Write Hybrid Balance Register ≠ 1<br>Read Hybrid Balance Register ≠ 1 | P<br>P | 0      | 1<br>1 | 1<br>1 | 0      | 0<br>1 | 1<br>1 | X | See Table 9<br>See Table 9   |

| Write Hybrid Balance Register ≠ 2<br>Read Hybrid Balance Register ≠ 2 | P<br>P | 0<br>0 | 1<br>1 | 1<br>1 | 1<br>1 | 0<br>1 | 1<br>1 | X | See Table 10<br>See Table 10 |

| Write Hybrid Balance Register ≠ 3<br>Read Hybrid Balance Register ≠ 3 | P<br>P | 1<br>1 | 0      | 0      | 0      | 0<br>1 | 1<br>1 | X |                              |

Notes: 1. Bit 7 of bytes 1 and 2 is always the first bit clocked into or out of the CI, CO or CI/CO pin.

2. "P" is the power-up/down control bit, see "Power-up" section ("0" = Power Up "1" = Power Down).

## **PROGRAMMABLE FUNCTIONS**

# POWER-UP/DOWN CONTROL

Following power-on initialization, power-up and power-down control may be accomplished by writing any of the control instructions listed in table 1 into COMBO IIG with the "P" bit set to "0" for power-up or "1" for power-down. Normally it is recommended that all programmable functions be initially programmed while the device is powered down. Power state control can then be included with the last programming instruction or the sepa-

rate single-byte instruction. Any of the programmable registers may also be modified while the device is powered-up or down be setting the "P" bit as indicated. When the power up or down control is entered as a single byte instruction, bit one (1) must be set to a 0.

When a power-up command is given, all de-activated circuits are activated, but the TRI-STATE PCM output(s),  $D_XO$  (and  $D_X1$ ), will remain in the high impedance state until the second  $FS_X$  pulse after power-up.

#### CONTROL REGISTER INSTRUCTION

The first byte of a READ or WRITE instruction to the Control Register is as shown in table 1. The second byte functions are detailed in table 2.

## MASTER CLOCK FREQUENCY SELECTION

A Master clock must be provided to COMBO IIG for operation of the filter and coding/decoding functions. The MCLK frequency must be either 512 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz, or 4.096 MHz and must be synchronous with BCLK. Bits F1 and F0 (see table 2) must be set during initialization to select the correct internal divider.

# **CODING LAW SELECTION**

Bits "MA" and "IA" in table 2 permit the selection of  $\mu$ 255 coding or A-law coding with or without even-bit inversion.

Table 2: Control Register Byte 2 Functions

#### ANALOG LOOPBACK

Analog Loopback mode is entered by setting the "AL" and "DL" bits in the Control Register as shown in table 2. In the analog loopback mode, the Transmit input VF $_{\rm X}$ I is isolated from the input pin and internally connected to the VF $_{\rm R}$ O output, forming a loop from the Receive PCM Register back to the Transmit PCM Register. The VF $_{\rm R}$ O pin remains active, and the programmed settings of the Transmit and Receive gains remain unchanged, thus care must be taken to ensure that overload levels are not exceeded anywhere in the loop.

Hybrid balancing must be disabled for meaning ful analog loopback Function.

#### DIGITAL LOOPBACK

Digital Loopback mode is entered by setting the "DL" bit in the Control Register as shown in table 2.

|                  |                  |             | Bit Nu      | ımber  |             |             |        |                                                                                            |  |  |  |

|------------------|------------------|-------------|-------------|--------|-------------|-------------|--------|--------------------------------------------------------------------------------------------|--|--|--|

| 7                | 6                | 5           | 4           | 3      | 2           | 1           | 0      | Function                                                                                   |  |  |  |

| F1               | F0               | MA          | IA          | DN     | DL          | AL          | PP     |                                                                                            |  |  |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |             |             |        |             |             |        | MCLK = 512 kHz<br>MCLK = 1.536 or 1.544 MHz<br>MCLK = 2.048 MHz<br>MCLK = 4.096 MHz        |  |  |  |

|                  |                  | 0<br>1<br>1 | X<br>0<br>1 |        |             |             |        | Select μ. 255 Law *<br>A–law, Including Even Bit Inversion<br>A–Law, No Even Bit Inversion |  |  |  |

|                  |                  |             |             | 0<br>1 |             |             |        | Delayed Data Timing<br>Non-delayed Data Timing *                                           |  |  |  |

|                  |                  |             |             |        | 0<br>1<br>0 | 0<br>X<br>1 |        | Normal Operation * Digital Loopback Analog Loopback                                        |  |  |  |

|                  |                  |             |             |        |             |             | 0<br>1 | Power Amp Enabled in PDN<br>Power Amp Disabled in PDN *                                    |  |  |  |

<sup>(\*)</sup> State at power-on initialization (bit 4 = 0)

Table 3: Coding Law Conventions.

|                               |   | m255 Law<br>MSB LSB |        |        |        |        | True A-law with<br>even bit inversion<br>MSB LSB |        |        |        |   |        | A-law without<br>even bit inversion<br>MSB LSB |        |   |        |        |   |   |   |   |   |   |   |

|-------------------------------|---|---------------------|--------|--------|--------|--------|--------------------------------------------------|--------|--------|--------|---|--------|------------------------------------------------|--------|---|--------|--------|---|---|---|---|---|---|---|

| V <sub>IN</sub> = +Full Scale | 1 | 0                   | 0      | 0      | 0      | 0      | 0                                                | 0      | 1      | 0      | 1 | 0      | 1                                              | 0      | 1 | 0      | 1      | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| $V_{IN} = 0V$                 | 1 | 1<br>1              | 1<br>1 | 1<br>1 | 1<br>1 | 1<br>1 | 1<br>1                                           | 1<br>1 | 1<br>0 | 1<br>1 | 0 | 1<br>1 | 0                                              | 1<br>1 | 0 | 1<br>1 | 1<br>0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| V <sub>IN</sub> = -Full Scale | 0 | 0                   | 0      | 0      | 0      | 0      | 0                                                | 0      | 0      | 0      | 1 | 0      | 1                                              | 0      | 1 | 0      | 0      | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Note: The MSB is always the first PCM bit shifted in or out of COMBO IIG.

This mode provides another stage of path verification by enabling data written into the Receive PCM Register to be read back from that register in any Transmit time-slot at  $D_X0$  or  $D_X1$ .

For Analog Loopback as well as for Digital Loopback PCM decoding continues and analog output appears at VF<sub>R</sub>O. The output can be disabled by pro gramming "No Output" in the Receive Gain Register (see table 8).

## INTERFACE LATCH DIRECTIONS

Immediately following power-on, all Interface Latches assume they are inputs, and therefore all IL pins are in a high impedance state. Each IL pin may be individually programmed as a logic input or output by writing the appropriate instruction to the LDR, see table 1 and 4. Bits  $L_5$ - $L_0$  must be set by writing the specific instruction to the LDR with the L bits in the second byte set as specified in table 4. Unused interface latches should be programmed as outputs. For the TS5071, L5 should always be programmed as an output.

Table 4: Byte 2 Function of Latch Direction Register

|    | Bit Number |    |    |    |    |   |   |  |  |  |  |  |  |

|----|------------|----|----|----|----|---|---|--|--|--|--|--|--|

| 7  | 6          | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |  |  |  |

| L0 | L1         | L2 | L3 | L4 | L5 | Х | Х |  |  |  |  |  |  |

| L <sub>N</sub> Bit | IL Direction |

|--------------------|--------------|

| 0                  | Input *      |

| 1                  | Output       |

(\*) State at power-on initilization.

**Note:** L5 should be programmed as an output for the TS5071.

INTERFACE LATCH STATES

Interface Latches configured as outputs assume the state determined by the appropriate data bit in the 2-byte instruction written to the Latch Content Register (ILR) as shown in tables 1 and 5. Latches configured as inputs will sense the state applied by an external source, such as the Off-Hook detect output of a SLIC. All bits of the ILR, i.e. sensed inputs and the programmed state of outputs, can be read back in the 2nd byte of a READ from the ILR. It is recommended that, during initialization, the state of IL pins to be configured as outputs should first be programmed, followed immediately by the Latch Direction Register.

Table 5: Interface Latch Data Bit Order

|    | Bit Number      |    |    |    |    |   |   |  |  |  |  |  |  |  |

|----|-----------------|----|----|----|----|---|---|--|--|--|--|--|--|--|

| 7  | 7 6 5 4 3 2 1 0 |    |    |    |    |   |   |  |  |  |  |  |  |  |

| D0 | D1              | D2 | D3 | D4 | D5 | Х | Х |  |  |  |  |  |  |  |

#### TIME-SLOT ASSIGNMENT

COMBO IIG can operate in either fixed time-slot or time-slot assignment mode for selecting the Transmit and Receive PCM time-slots. Following poweron, the device is automatically in Non-Delayed Timing mode, in which the time-slot always begins with the leading (rising) edge of frame sync inputs FSx and FSR. Time-Slot Assignment may only be used with Delayed Data timing : see figure 6. FSx and FSR may have any phase relationship with each other in BCLK period increments.

Table 6: Byte 2 of Time-slot and Port Assignment Instructions

|         |                     |                     | Bit N   | umber   |                        |         |         | Function                                                                                                                                                                   |

|---------|---------------------|---------------------|---------|---------|------------------------|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>EN | 6<br>PS<br>(note 1) | 5<br>T5<br>(note 2) | 4<br>T4 | 3<br>T3 | 2<br>T2                | 1<br>T1 | 0<br>T0 |                                                                                                                                                                            |

| 0       | Х                   | Х                   | X       | Х       | Х                      | Х       | Х       | Disable D <sub>X</sub> Outputs (transmit instruction) * Disable D <sub>R</sub> Inputs (receive instruction) *                                                              |

| 1       | 0                   |                     |         | ,       | Time-slot<br>Time-slot |         |         | Enable $D_X0$ Output, Disable $D_X1$ Output (Transmit instruction) Enable $D_R0$ Input, Disable $D_R1$ Input (Receive Instruction)                                         |

| 1       | 1                   |                     |         | ,       | Time-slot              |         |         | Enable D <sub>X</sub> 1 Output, Disable D <sub>X</sub> 0 Output (Transmit instruction) Enable D <sub>R</sub> 1 Input, Disable D <sub>R</sub> 0 Input (Receive Instruction) |

#### Notes:

- 1. The "PS" bit MUST always be set to 0 for the TS5071.

- 2. T5 is the MSB of the time-slot assignment.

- (\*) State at power-on initialization

Alternatively, the internal time-slot assignment counters and comparators can be used to access any time-slot in a frame, using the frame sync inputs as marker pulses for the beginning of transmit and receive time-slot 0. In this mode, a frame may consist of up to 64 time-slots of 8 bits each. A time-slot is assigned by a 2-byte instruction as shown in table 1 and 6. The last 6 bits of the second byte indicate the selected time-slot from 0-63 using straight binary notation. A new assignment becomes active on the second frame following the end of the Chip Select for the second control byte. The "EN" bit allows the PCM inputs  $D_R0/1$  or outputs  $D_X0/1$  as appropriate, to be enabled or disabled.

Time-Slot Assignment mode requires that the FS<sub>X</sub> and FS<sub>R</sub> pulses must conform to the delayed timing format shown in figure 6.

## PORT SELECTION

On the TS5070 only, an additional capability is available: 2 Transmit serial PCM ports, Dx0 and Dx1, and 2 receive serial PCM ports, Dx0 and Dx1, are provided to enable two-way space switching to be implemented. Port selections for transmit and receive are made within the appropriate time-slot

assignmentinstruction using the "PS" bit in the second byte.

On the TS5071, only ports  $D_X0$  and  $D_R0$  are available, therefore the "PS" bit MUST always be set to 0 for these devices.

Table 6 shows the format for the second byte of both transmit and receive time-slot and port assignment instructions.

#### TRANSMIT GAIN INSTRUCTION BYTE 2

The transmit gain can be programmed in 0.1 dB steps by writing to the Transmit Gain Register as defined in tables 1 and 7. This corresponds to a range of 0 dBm0 levels at VF<sub>X</sub>I between 1.619 Vrms and 0.087 Vrms (equivalent to + 6.4 dBm to -19.0 dBm in  $600 \Omega$ ).

To calculate the binary code for byte 2 of this instruction for any desired input 0 dBm0 level in Vrms, take the nearest integer to the decimal number given by :

200 X

$$\log_{10} (V/\sqrt{6}) + 191$$

and convert to the binary equivalent. Some examples are given in table 7.

**Table 7:** Byte 2 of Transmit Gain Instructions.

| Bit Number |        |        |        |        |        |        |        | 0dBm0 Test Leve at VF <sub>X</sub> I |                   |  |

|------------|--------|--------|--------|--------|--------|--------|--------|--------------------------------------|-------------------|--|

| 7          | 6      | 5      | 4      | 3      | 2      | 1      | 0      | In dBm (Into 600 $\Omega$ )          | In Vrms (approx.) |  |

| 0          | 0      | 0      | 0      | 0      | 0      | 0      | 0      | No Output                            |                   |  |

| 0          | 0<br>0 | 0<br>0 | 0<br>0 | 0<br>0 | 0<br>0 | 0<br>1 | 1<br>0 | – 19<br>– 18.9                       | 0.087<br>0.088    |  |

| 1          | 0      | 1      | 1      | 1      | 1      | 1      | 1      | 0                                    | 0.775             |  |

| 1          | 1      | 1      | 1      | 1      | 1      | 1<br>1 | 0<br>1 | +6.3<br>+6.4                         | 1.60<br>1.62      |  |

<sup>(\*)</sup> State at power initialization

# **RECEIVE GAIN INSTRUCTION BYTE 2**

The receive gain can be programmed in 0.1 dB steps by writing to the Receive Gain Register as defined in table 1 and 8. Note the following restriction on output drive capability:

- a) 0 dBm0 levels  $\leq$  8.1dBm at VF<sub>R</sub>O may be driven into a load of  $\geq$  15 k $\Omega$  to GND,

- b) 0 dBm0 levels  $\leq$  7.6dBm at VF<sub>R</sub>O may be driven into a load of  $\geq$  600  $\Omega$  to GND,

- c) 0 dBm levels ≤ 6.9dBm at VF<sub>R</sub>O may be driven

into a load of  $\geq$  300  $\Omega$  to GND.

To calculate the binary code for byte 2 of this instruction for any desired output 0 dBm0 level in Vrms, take the nearest integer to the decimal number given by:

a 200 X

$$\log_{10} (V/\sqrt{6}) + 174$$

d convert to the binary equivalent. Some examples are given in table 8.

Table 8: Byte 2 of Receive Gain Instructions.

|   |   |   | Bit Nu | ımber  |   |        |        | 0dBm0 Test Leve at VF <sub>R</sub> 0 |                   |  |  |

|---|---|---|--------|--------|---|--------|--------|--------------------------------------|-------------------|--|--|

| 7 | 6 | 5 | 4      | 3      | 2 | 1      | 0      | In dBm (Into 600 $\Omega$ )          | In Vrms (approx.) |  |  |

| 0 | 0 | 0 | 0      | 0      | 0 | 0      | 0      | No Output                            |                   |  |  |

| 0 | 0 | 0 | 0      | 0<br>0 | 0 | 0<br>1 | 1<br>0 | – 17.3<br>– 17.2                     | 0.106<br>0.107    |  |  |

| 1 | 0 | 1 | 0      | 1      | 1 | 1      | 0      | 0                                    | 0.775             |  |  |

| 1 | 1 | 1 | 1      | 0      | 0 | 1      | 1      | + 6.9 (note 1)                       | 1.71              |  |  |

| 1 | 1 | 1 | 1      | 1      | 0 | 1      | 0      | + 7.6 (note 2)                       | 1.86              |  |  |

| 1 | 1 | 1 | 1      | 1      | 1 | 1      | 1      | + 8.1 (note 3)                       | 1.07              |  |  |

#### Notes:

Maximum level into 300Ω;

Maximum level into 600Ω;

R<sub>L</sub>≥15ΚΩ (\*) State at power on initialization

#### HYBRID BALANCE FILTER

The Hybrid Balance Filter on COMBO IIG is a programmable filter consisting of a second-order Bi-Quad section, Hybal1, followed by a first-order section, Hybal2, and a programmable attenuator. Either of the filter sections can be bypassed if only one is required to achieve good cancellation. A selectable 180 degree inverting stage is included to compensate for interface circuits which also invert the transmit input relative to the receive output signal. The Bi-Quad is intended mainly to balance low frequency signals across a transformer SLIC, and the first order section to balance midrange to higher audio frequency signals. The attenuator can be programmed to compensate for VF<sub>R</sub>O to VF<sub>X</sub>I echos in the range of -2.5 to -8.5 dB.

As a Bi-Quad, Hybal1 has a pair of low frequency zeroes and a pair of complex conjugate poles. When configuring the Bi-Quad, matching the phase of the hybrid at low to midband frequencies is most critical. Once the echo path is correctly balanced in phase, the magnitude of the cancellation signal can be corrected by the programmable

#### attenuator.

The Bi-Quad mode of Hybal1 is most suitable for balancing interfaces with transformers having high inductance of 1.5 Henries or more. An alternative configuration for smaller transformers is available by converting Hybal1 to a simple first-order section with a single real low frequency pole and 0 Hz zero. In this mode, the pole/zero frequency may be programmed.

Many line interfaces can be adequately balanced by use of the Hybal1 section only, in which case the Hybal2 filter should be de-selected to bypass it

Hybal2, the higher frequency first-order section, is provided for balancing an electronic SLIC, and is also helpful with a transformer SLIC in providing additional phase correction for mid and high-band frequencies, typically 1 kHz to 3.4 kHz. Such a correction is particularly useful if the test balance impedance includes a capacitor of 100 nF or less, such as the loaded and non-loaded loop test networks in the United States. Independent placement of the pole and zero location is provided.

Table 9: Hybrid Balance Register 1 Byte 2 Instruction.

| Bit   | State | Function                                                                                                                            |

|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 7     | 0     | Disable Hybrid Balance Circuit Completely. No internal cancellation is provided.                                                    |

|       | 1     | Enable Hybrid Balance Cancellation Path                                                                                             |

| 6     | 0     | Phase of the internal cancellation signal assumes inverted phase of the echo path from $VF_RO$ to $VF_XI$ .                         |

|       | 1     | Phase of the internal cancellation signal assumes no phase inversion in the line interface.                                         |

| 5     | 0     | Bypass Hybal 2 Filter Section                                                                                                       |

|       | 1     | Enable Hybal 2 Filter Section                                                                                                       |

| G4–G0 |       | Attenuation Adjustment for the Magnitude of the Cancellation Signal. Range is $-2.5~{\rm dB}~(00000)~{\rm to}-8.5~{\rm dB}~(11000)$ |

<sup>(\*)</sup> State at power on initialization Setting = Please refer to software TS5077 2

Figure 1 shows a simplified diagram of the local echo path for a typical application with a transformer interface. The magnitude and phase of the local echo signal, measured at  $VF_XI$ , are a function of the termination impedance  $Z_T$ , the line trans-

former and the impedance of the 2 W loop,  $Z_L$ . If the impedance reflected back into the transformer primary is expressed as  $Z_L$ ' then the echo path transfer function from  $VF_RO$  to  $VF_XI$  is :

$$H(W) = Z_L' / (Z_T + Z_L')$$

(1)

Figure 1: Simplified Diagram of Hybrid Balance Circuit

#### PROGRAMMING THE FILTER

On initial power-up the Hybrid Balance filter is disabled. Before the hybrid balance filter can be programmed it is necessary to design the transformer and termination impedance in order to meet system 2 W input return loss specifications, which are normally measured against a fixed test impedance  $(600 \text{ or } 900 \Omega \text{ in most countries})$ . Only then can the echo path be modeled and the hybrid balance filter programmed. Hybrid balancing is also measured against a fixed test impedance, specified by each national Telecom administration to provide adequate control of talker and listener echo over the majority of their network connections. This test impedance is Z<sub>L</sub> in figure 1. The echo signal and the degree of transhybrid loss obtained by the programmable filter must be measured from the PCM digital input  $D_R0$ , to the PCM digital output  $D_X0$ , either by digital test signal analysis or by conversion back to analog by a PCM CODEC/Filter.

Three registers must be programmed in COMBO IIG to fully configure the Hybrid Balance Filter as follows:

Register 1: select/de-select Hybrid Balance Filter; invert/non-invert cancellation signal; select/de-select Hybal2 filter section; attenuatorsetting.

Register 2: select/de-select Hybal1 filter; set Hybal1 to Bi-Quad or 1st order; program pole and zero frequency.

Table 10: Hybrid Balance Register 2 Byte 2 instructions

|   |   | В | it Nu | Function |   |   |   |                           |  |

|---|---|---|-------|----------|---|---|---|---------------------------|--|

| 7 | 6 | 5 | 4     | 3        | 2 | 1 | 0 | Function                  |  |

| 0 | 0 | 0 | 0     | 0        | 0 | 0 | 0 | By Pass Hybal 1<br>Filter |  |

| Х | Χ | Χ | Χ     | Χ        | Х | Χ | Χ | Pole/zero Setting         |  |

Register 3: program pole frequency in Hybal2 filter; program zero frequency in Hybal2 filter; settings = Please refer to software TS5077-2.

Standard filter design techniques may be used to model the echo path (see equation (1)) and design a matching hybrid balance filter configuration. Alternatively, the frequency response of the echo path can be measured and the hybrid balance filter programmed to replicate it.

An Hybrid Balance filter design guide and software optimization program are available under license from SGS-THOMSON Microelectronics (order TS5077-2).

# **APPLICATION INFORMATION**

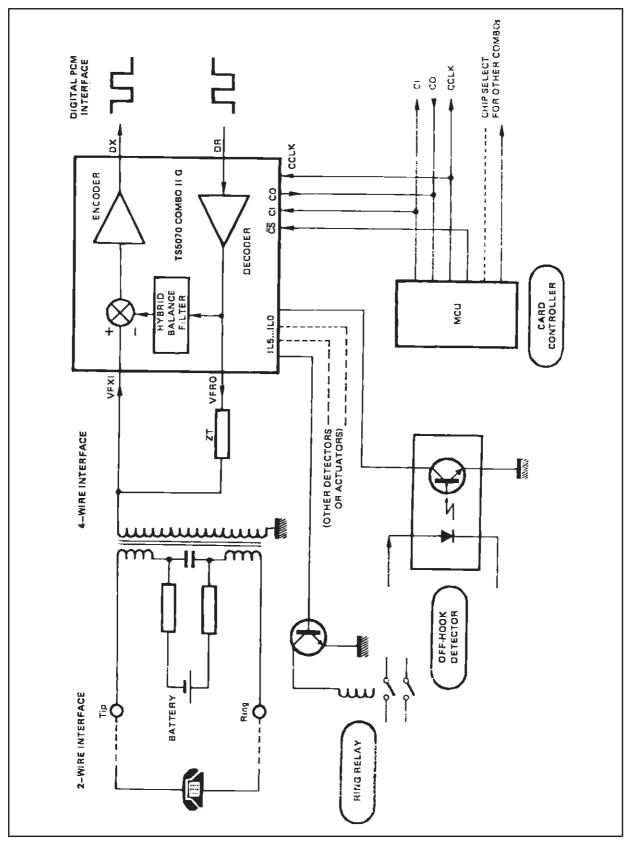

Figure 2 shows a typical application of the TS5070 together with a transformer SLIC.

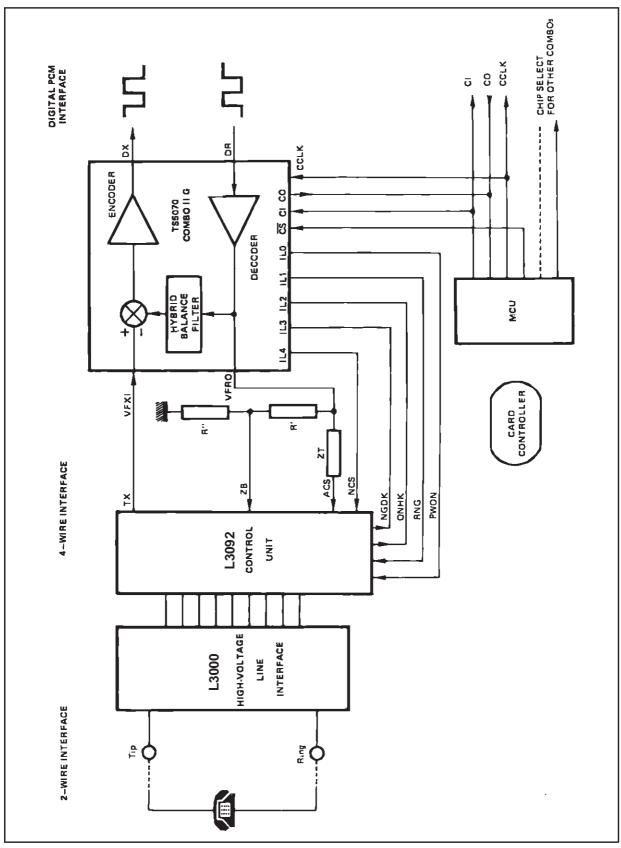

The design of the transformer is greatly simplified due to the on-chip hybrid balance cancellation filter. Only one single secondary winding is required (see application note AN.091 - Designing a subscriber line card module using the TS5070/COMBO IIG). Figures 3 and 4 show an arrangement with SGS-Thomson monolithic SLICS.

#### **POWER SUPPLIES**

While the pins of the TS5070 and TS5071/COMBO IIG devices are well protected against electrical misuse, it is recommended that the standard CMOS practice of applying GND to the device be-

fore any other connections are made should always be followed. In applications where the printed circuit card may be plugged into a hot socket with power and clocks already present, an extra long ground pin on the connector should be used and a Schottky diode connected between Vss and GND. To minimize noise sources all ground connections to each device should meet at a common point as close as possible to the GND pin in order to prevent the interaction of ground return currents flowing through a common bus impedance. Power supply decoupling capacitors of 0.1 µF should be connected from this common device ground point to V<sub>CC</sub> and V<sub>SS</sub> as close to the device pins as possible. Vcc and Vss should also be decoupled with low effective series resis-tance capacitors of at least 10 µF located near the card edge connector.

Figure 2: Transformer SLIC + COMBO IIG.

Figure 4: Interface with L3092 + L3000 Silicon SLIC.

# **ELECTRICAL OPERATING CHARACTERISTICS**

Unless otherwise noted, limits in **BOLD** characters are guaranteed for  $V_{CC}$  = + 5 V  $\pm$  5 %;  $V_{SS}$  = - 5 V  $\pm$  5 %.  $T_A$  = -40 °C to 85 °C by correlation with

100% electrical testing at  $T_A = 25\,^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterisation. All signals referenced to GND. Typicals specified at  $V_{CC} = +5\,V$ ,  $V_{SS} = -5\,V$ ,  $T_A = 25\,^{\circ}C$ .

# **DIGITAL INTERFACE**

| Symbol          | Parameter                                                                                                                                                                         | Min.                            | Тур. | Max. | Unit   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------|--------|

| $V_{IL}$        | Input Low Voltage All Digital Inputs (DC measurement)                                                                                                                             |                                 |      | 0.7  | V      |

| $V_{IH}$        | Input High Voltage All Digital Inputs (DC measurement)                                                                                                                            | 2.0                             |      |      | V      |

| V <sub>OL</sub> | Output Low Voltage<br>D <sub>X</sub> 0 and D <sub>X</sub> 1, TS <sub>X</sub> 0, TS <sub>X</sub> 1 and CO, $I_L = 3.2$ mA<br>All Other Digital Outputs, $I_L = 1$ mA               |                                 |      | 0.4  | V      |

| V <sub>OH</sub> | Output High Voltage DX0 and $\underline{DX}$ 1 and CO, $I_L$ = -3.2mA All other digital outputs except $\overline{TS}_X$ , $I_L$ = -1mA All Digital Outputs, $I_L$ = -100 $\mu$ A | <b>2.4</b> V <sub>CC</sub> -0.5 |      |      | V<br>V |

| I <sub>IL</sub> | Input Low Current all Digital Inputs (GND < V <sub>IN</sub> < V <sub>IL</sub> )                                                                                                   | -10                             |      | 10   | μΑ     |

| I <sub>IH</sub> | Input High Current all Digital Inputs Except MR (V <sub>IH</sub> < V <sub>IN</sub> < V <sub>CC</sub> )                                                                            | -10                             |      | 10   | μΑ     |

| I <sub>IH</sub> | Input High Current on MR                                                                                                                                                          | -10                             |      | 100  | μΑ     |

| l <sub>OZ</sub> | Output Current in High Impedance State (TRI-STATE) DX0 and DX1, CO and CI/O (as an input) IL5-IL0 as inputs (GND < $V_O$ < $V_{CC}$ )                                             | -10                             |      | 10   | μА     |

# **ANALOG INTERFACE**

| Symbol             | Parameter                                                                                                     | Min.             | Тур. | Max.      | Unit         |

|--------------------|---------------------------------------------------------------------------------------------------------------|------------------|------|-----------|--------------|

| I <sub>VFXI</sub>  | Input Current VF <sub>X</sub> I (-3.3V < VF <sub>X</sub> I < 3.3V)                                            | -10              |      | 10        | μΑ           |

| R <sub>VFXI</sub>  | Input Resistance VF <sub>X</sub> I (-3.3V < VF <sub>X</sub> I < 3.3V)                                         | 390              | 620  |           | kΩ           |

| VOS <sub>X</sub>   | Input offset voltage at VF <sub>X</sub> I<br>0dBm0 = -19dBm<br>0dBm0 = +6.4dBm                                |                  |      | 10<br>200 | mV<br>mV     |

| RL <sub>VFRO</sub> | Load Resistance at $VF_RO$<br>0dBm0 = 8.1dBm<br>0dBm0 = 7.6dBm<br>0dBm0 = 6.9dBm                              | 15<br>600<br>300 |      |           | kΩ<br>Ω<br>Ω |

| CL <sub>VFRO</sub> | Load Capacitance CLVFRO from VFRO to GND                                                                      |                  |      | 200       | pF           |

| RO <sub>VFRO</sub> | Output Resistance VFRO (steady zero PCM code applied to DR0 or $D_R1)$                                        |                  | 1    | 3         | Ω            |

| V <sub>OSR</sub>   | Output Offset Voltage at $VF_RO$ (alternating ±zero PCM code applied to $D_RO$ or $D_R1$ , $0dBm0 = 8.1dBm$ ) | -200             |      | 200       | mV           |

# **ELECTRICAL OPERATING CHARACTERISTICS (continued)**

## POWER DISSIPATION

| Symbol | Parameter                                                                                                                                                   | Min. | Тур. | Max. | Unit |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| ICC0   | Power Down Current (CCLK, CI/O, CI = 0.4V, $\overline{CS}$ = 2.4V) Interface Latches set as Outputs with no load All over Inputs active, Power Amp Disabled |      | 0.3  | 1.5  | mA   |

| -ISS0  | Power Down Current (as above)                                                                                                                               |      | 0.1  | 0.3  | mA   |

| ICC1   | Power Up Current (CCLK, CI/O, CI = 0.4V, $\overline{\text{CS}}$ = 2.4V)  No Load on Power Amp  Interface Latches set as Outputs with no Load                |      | 7    | 11   | mA   |

| -ISS1  | Power Up Current (as above)                                                                                                                                 |      | 7    | 11   | mA   |

| ICC2   | Power Down Current with Power Amp Enabled                                                                                                                   |      | 2    | 4    | mA   |

| -ISS2  | Power Down Current with Power Amp Enabled                                                                                                                   |      | 2    | 4    | mA   |

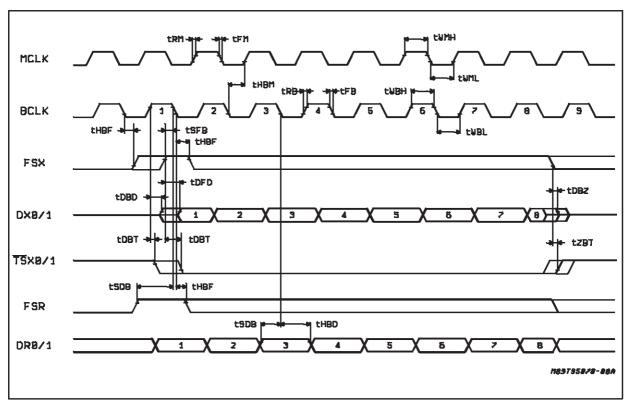

## TIMING SPECIFICATIONS

Unless otherwise noted, limits in BOLD characters are guaranteed for Vcc = + 5 V  $\pm$  5 %; Vss = -5V  $\pm$  5 %. T<sub>A</sub> = -40 °C to 85 °C by correlation with 100 % electrical testing at T<sub>A</sub> = 25 °C. All other limits are assured by correlation with other production tests

and/or product design and characterization. All signals referenced to GND. Typicals specified at V<sub>CC</sub> = +5 V, V<sub>SS</sub> = -5 V, T<sub>A</sub> = 25 °C. All timing parameters are measured at V<sub>OH</sub> = 2.0 V and V<sub>OL</sub> = 0.7 V.

See Definitions and Timing Conventions section for test methods information.

## MASTER CLOCK TIMING

| Symbol            | Parameter                                                                           | Min. | Тур.                                           | Max. | Unit                            |

|-------------------|-------------------------------------------------------------------------------------|------|------------------------------------------------|------|---------------------------------|

| f <sub>MCLK</sub> | Frequency of MCLK (selection of frequency is programmable, see table 2)             |      | 512<br>1.536<br>1.544<br>2.048<br><b>4.096</b> |      | kHz<br>MHz<br>MHz<br>MHz<br>MHz |

| t <sub>WMH</sub>  | Period of MCLK High (measured from V <sub>IH</sub> to V <sub>IH</sub> , see note 1) | 80   |                                                |      | ns                              |

| t <sub>WML</sub>  | Period of MCLK Low (measured from $V_{IL}$ to $V_{IL}$ , see note 1)                | 80   |                                                |      | ns                              |

| t <sub>RM</sub>   | Rise Time of MCLK (measured from $V_{IL}$ or $V_{IH}$ )                             |      |                                                | 30   | ns                              |

| t <sub>FM</sub>   | Fall Time of MCLK (measured from $V_{IH}$ to $V_{IL}$ )                             |      |                                                | 30   |                                 |

| t <sub>HBM</sub>  | Hold Time, BCLK Low to MCLK High (TS5070 only)                                      | 50   |                                                |      | ns                              |

| t <sub>WFL</sub>  | Period of $FS_X$ or $FS_R$ Low (Measured from $V_{IL}$ to $V_{IL}$ )                | 1    |                                                |      | (*)                             |

(\*) MCLK period

# **TIMING SPECIFICATIONS** (continued)

PCM INTERFACE TIMING

| Symbol            | Parameter                                                                                                                                                 | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| f <sub>BCLK</sub> | Frequency of BCLK (may vary from 64KHz to 4.096MHz in 8KHz increments, TS5070 only)                                                                       | 64   |      | 4096 | kHz  |

| t <sub>WBH</sub>  | Period of BCLK High (measured from V <sub>IH</sub> to V <sub>IH</sub> )                                                                                   | 80   |      |      | ns   |

| t <sub>WBL</sub>  | Period of BCLK Low (measured from V <sub>IL</sub> to V <sub>IL</sub> )                                                                                    | 80   |      |      | ns   |

| t <sub>RB</sub>   | Rise Time of BCLK (measured from V <sub>IL</sub> to V <sub>IH</sub> )                                                                                     |      |      | 30   | ns   |

| t <sub>FB</sub>   | Fall Time of BCLK (measured from V <sub>IH</sub> to V <sub>IL</sub> )                                                                                     |      |      | 30   | ns   |

| t <sub>HBF</sub>  | Hold Time, BCLK Low to FS <sub>X/R</sub> High or Low                                                                                                      | 30   |      |      | ns   |

| t <sub>SFB</sub>  | Setup Time FS <sub>X/R</sub> High to BCLK Low                                                                                                             | 30   |      |      | ns   |

| t <sub>DBD</sub>  | Delay Time, BCLK High to Data Valid (load = 100pF plus 2 LSTTL loads)                                                                                     |      |      | 80   | ns   |

| t <sub>DBZ</sub>  | Delay Time from BCLK8 Low to Dx Disabled (if FSx already low);<br>FSx Low to Dx Disabled (if BCLK8 low);<br>BCLK9 High to Dx Disabled (if FSx still high) | 15   |      | 80   | ns   |

| t <sub>DBT</sub>  | Delay Time from BCLK and FSx Both High to $\overline{\text{TSx}}$ Low (Load = 100pF plus 2 LSTTL loads)                                                   |      |      | 60   | ns   |

| t <sub>ZBT</sub>  | Delay Time from BCLK8 low to TSx Disabled (if FSx already low); FSx Low to TSx Disabled (if BCLK8 low); BCLK9 High to TSx Disabled (if FSx still high);   | 15   |      | 60   | ns   |

| t <sub>DFD</sub>  | Delay Time, FSx High to Data Valid (load = 100pF plus 2 LSTTL loads, applies if FSx rises later than BCLK rising edge in non-delayed data mode only)      |      |      | 80   | ns   |

| t <sub>SDB</sub>  | Setup Time, D <sub>R</sub> 0/1 Valid to BCLK Low                                                                                                          | 30   |      |      | ns   |

| t <sub>HBD</sub>  | Hold Time, BCLK Low to DR0/1 Invalid                                                                                                                      | 20   |      |      | ns   |

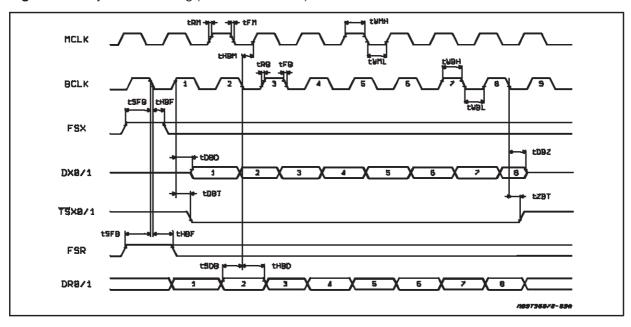

Figure 5: Non Delayed Data Timing (short frame mode)

Figure 6: Delayed Data Timing (short frame mode)

# SERIAL CONTROL PORT TIMING

| Symbol            | Parameter                                                                                                                                      | Min. | Тур. | Max.  | Unit |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|

| f <sub>CCLK</sub> | Frequency of CCLK                                                                                                                              |      |      | 2.048 | MHz  |

| t <sub>WCH</sub>  | Period of CCLK High (measured from V <sub>IH</sub> to V <sub>IH</sub> )                                                                        | 160  |      |       | ns   |

| t <sub>WCL</sub>  | Period of CCLK Low (measured from $V_{IL}$ to $V_{IL}$ )                                                                                       | 160  |      |       | ns   |

| t <sub>RC</sub>   | Rise Time of CCLK (measured from $V_{IL}$ to $V_{IH}$ )                                                                                        |      |      | 50    | ns   |

| t <sub>FC</sub>   | Fall Time of CCLK (measured from V <sub>IH</sub> to V <sub>IL</sub> )                                                                          |      |      | 50    | ns   |

| tHCS              | Hold Time, CCLK Low to CS Low (CCLK1)                                                                                                          | 10   |      |       | ns   |

| t <sub>HSC</sub>  | Hold Time, CCLK Low to CS High (CCLK8)                                                                                                         | 100  |      |       | ns   |

| t <sub>SSC</sub>  | Setup Time, CS Transition to CCLK Low                                                                                                          | 70   |      |       | ns   |

| tssco             | Setup Time, $\overline{\text{CS}}$ Transition to CCLK High (to insure CO is not enabled for single byte)                                       | 50   |      |       | ns   |

| t <sub>SDC</sub>  | Setup Time, CI (CI/O) Data in to CCLK low                                                                                                      | 50   |      |       | ns   |

| t <sub>HCD</sub>  | Hold Time, CCLK Low to CI (CI/O) Invalid                                                                                                       | 50   |      |       | ns   |

| t <sub>DCD</sub>  | Delay Time, CCLK High to CO (CI/O) Data Out Valid (load = 100 pF plus 2 LSTTL loads)                                                           |      |      | 80    | ns   |

| t <sub>DSD</sub>  | Delay Time, $\overline{CS}$ Low to $\underline{CO}$ (CI/O) Valid (applies only if separate $\overline{CS}$ used for byte 2)                    |      |      | 80    | ns   |

| t <sub>DDZ</sub>  | Delay Time, $\overline{CS}$ or $\underline{CCLK9}$ High to CO (CI/O) High Impedance (applies to earlier of $\overline{CS}$ high or CCLK9 high) | 15   |      | 80    | ns   |

# INTERFACE LATCH TIMING

| Symbol           | Parameter                                                                                             | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|

| tslc             | Setup Time, I <sub>L</sub> Valid to CCLK 8 of Byte 1 Low. I <sub>L</sub> as Input                     | 100  |      |      | ns   |

| tHCL             | Hold Time, I∟ Valid from CCLK 8 of Byte 1 Low. I∟ as Input                                            | 50   |      |      | ns   |

| t <sub>DCL</sub> | Delay Time, CCLK 8 of Byte 2 Low to I <sub>L</sub> . C <sub>L</sub> = 50 pF. I <sub>L</sub> as Output |      |      | 200  | ns   |

# MASTER RESET PIN

| Symbol           | Symbol Parameter              |   | Тур. | Max. | Unit |

|------------------|-------------------------------|---|------|------|------|

| t <sub>WMR</sub> | Duration of Master Reset High | 1 |      |      | μs   |

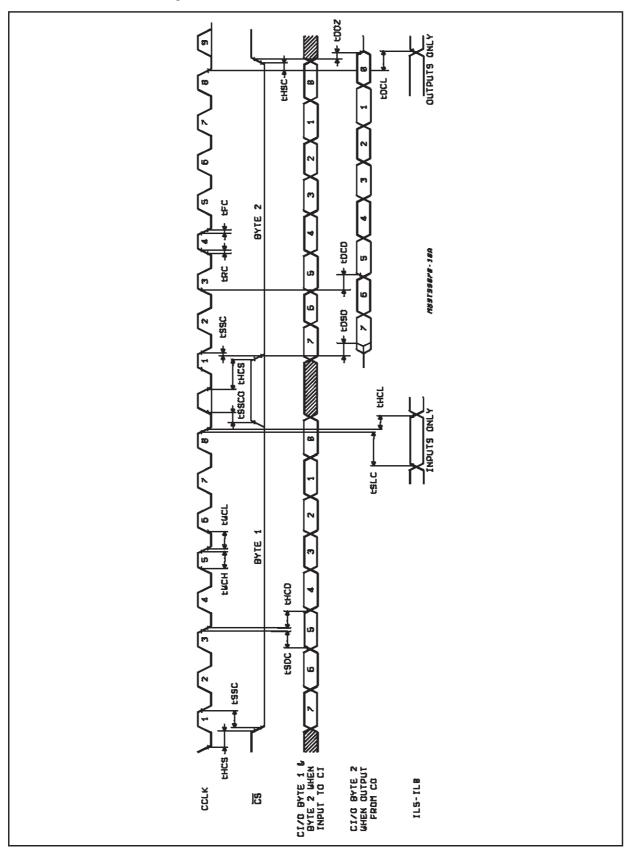

Figure 7: Control Port Timing

# TRANSMISSION CHARACTERISTICS

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC}$  = +5 V ± 5 %;  $V_{SS}$  = -5 V ± 5 %,  $T_A$  =-40 °C to 85 °C by correlation with 100 % electrical testing at  $T_A$  = 25 °C (-40 °C to 85 °C for TS5070-X and TS5071-X).

f=1031.25 Hz, VFxI = 0 dBm0, D<sub>R</sub>0 or D<sub>R</sub>1 = 0 dBm0 PCM code, Hybrid Balance filter disabled. All other limits are assured by correlation with other production tests and/or product design and characterization. All signals referenced to GND. dBm levels are into 600 ohms. Typicals specified at V<sub>CC</sub> = + 5 V, V<sub>SS</sub> = -5 V, T<sub>A</sub> = 25 °C.

## **AMPLITUDE RESPONSE**

| Symbol | Parameter                                                                                                                                                                                                                                                                                                                     | Min.   | Тур.                             | Max. | Unit                          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------|------|-------------------------------|

|        | Absolute levels                                                                                                                                                                                                                                                                                                               |        |                                  |      |                               |

|        | The nominal 0 dBm 0 levels are :<br>VF <sub>X</sub> I 0 dB Tx Gain<br>25.4 dB Tx Gain                                                                                                                                                                                                                                         |        | 1.618<br>86.9                    |      | Vrms<br>mVrms                 |

|        | $VF_RO$ 0 dB Rx Attenuation (RL $\geq$ 15 kΩ) 0.5 dB Rx Attenuation (RL $\geq$ 600 Ω) 1.2 dB Rx Attenuation (RL $\geq$ 300 Ω) 25.4 dB Rx Attenuation                                                                                                                                                                          |        | 1.968<br>1.858<br>1.714<br>105.7 |      | Vrms<br>Vrms<br>Vrms<br>mVrms |

|        | Maximum Overload                                                                                                                                                                                                                                                                                                              |        |                                  |      |                               |