# L6245

## **5V HARD DISK DRIVE POWER COMBO**

### PRODUCT PREVIEW

### General

- +5V OPERATION

- REGISTER BASED ARCHITECTURE

- MINIMUM EXTERNAL COMPONENTS

- SLEEP AND IDLE MODES FOR LOW POWER CONSUMPTION

- SELECTABLE GAINS FOR BOTH VCM AND SPINDLE Gm LOOP

- LINEAR CURRENT CONTROL LOOPS FOR BOTH VCM AND SPINDLE

- 8 BIT D/A FOR ACTUATOR DRIVER AND SPINDLE DRIVER

#### VCM Driver

- CURRENT SENSE CONTROL (VOLTAGE PROPORTIONAL TO CURRENT)

- VOLTAGE SENSE CONTROL (VOLTAGE PROPORTIONAL TO THE VOLTAGE ACROSS THE VCM)

- TWO CURRENT RANGES FOR SEEKING AND TRACKING

- INTERNAL REGISTER FOR POWER AMP CONTROL LINES

- SPEED OUTPUT (VOLTAGE PROPOR-TIONAL TO BEMF)

#### Spindle Driver

- BEMF PROCESSING FOR SENSORLESS MOTOR COMMUTATION

- PROGRAMMABLE COMMUTATION PHASE DELAY

- PROGRAMMABLE SLEW-RATE FOR RE-DUCED EMI

- 0.7Ω TYP. FOR ANY HALF BRIDGE

- CROSS CONDUCTION PROTECTION

- SYNTHESIZED HALL OUTPUT

#### **Other Functions**

- POWER UP SEQUENCING

- POWER DOWN SEQUENCING

- LOW VOLTAGE SENSE

- ACTUATOR RETRACTION

- DYNAMIC BRAKE

- THERMAL SHUTDOWN

MULTIPOWER BCD TECHNOLOGY

### DESCRIPTION

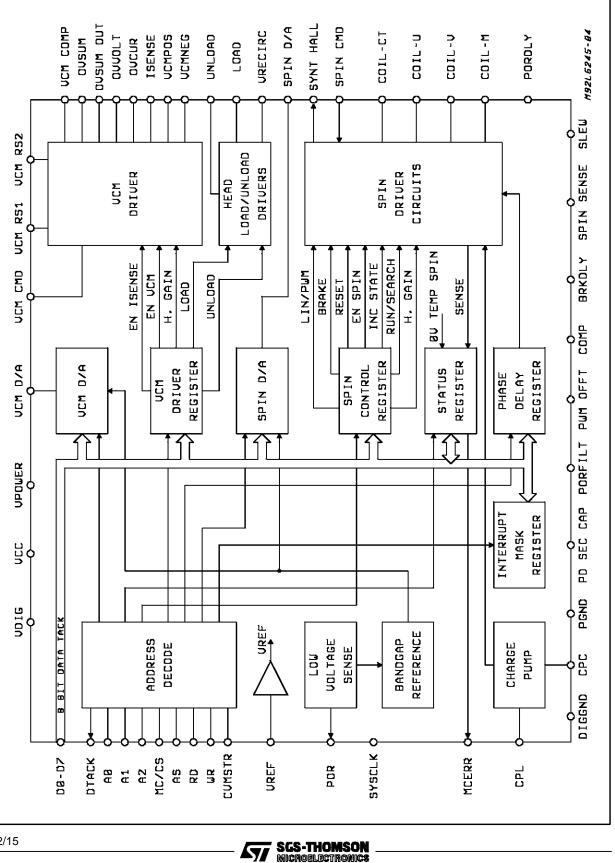

The L6245 contains in a single chip all the functions to operate a sensorless brushless (DC) motor and a voice coil motor, suitable for hard disk drive applications.

The device is configured to interface directly to an 8 bit parallel microprocessor bus, and has a register based architecture to reduce number of interconnection lines. All the positioning loop for sensorless spindle is integrated, including BEMF sensing, digital masking, digital delay and sequencing. All timing function are performed digitally, thus no external filtering components are required.

The VCM driver is a transconductance amplifier, able to provide 2 different current ranges, suitable for seeking or tracking of the head actuator. When a low voltage is detected, a monitor, in sequence, resets the internal registers, puts in tristate the spindle powers, retracts the actuator, and applies the dynamic brake of the spindle.

The L6245 is realized in Multipower-BCD 2 technology, which combine isolate DMOS power transistors with CMOS and Bipolar circuits in the same monolithic layer, and is assembled in a 64pin PQFP.

October 1992

#### **BLOCK DIAGRAM**

5/

#### L6245

2/15

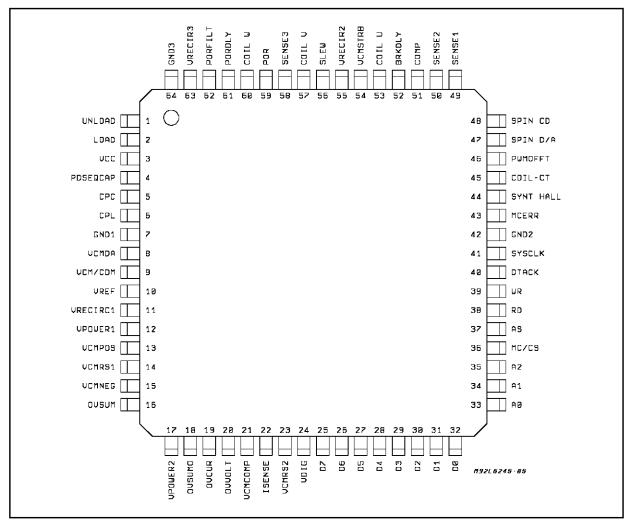

### **PIN CONNECTION** (Top view)

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                           | Parameter                                           |                                              | Value      | Unit |

|----------------------------------|-----------------------------------------------------|----------------------------------------------|------------|------|

| Vdssus                           | Peak Output Sustaining Voltage                      |                                              | 14         | V    |

| V <sub>P</sub> ; Vcc             |                                                     | er (V <sub>P</sub> )<br>c (V <sub>CC</sub> ) | 8<br>6     | > >  |

| Vi                               | Logic input Voltage                                 |                                              | 0 to 6     | V    |

| V <sub>cp</sub>                  | Charge Pump Input Voltage                           |                                              | 18         | V    |

| lp                               | Sink-Source Peak Output Current                     |                                              | 1.5        | А    |

| lo                               | Sink-Source DC Output Current                       |                                              | 1          | А    |

| Ptot                             | Total Power Dissipation ( $T_{amb} = 60^{\circ}C$ ) |                                              | 1          | W    |

| T <sub>stg,</sub> T <sub>j</sub> | Storage and Junction Temperature                    |                                              | -40 to 150 | °C   |

### THERMAL DATA

| Symbol               | Parameter                               |      | Value | Unit |

|----------------------|-----------------------------------------|------|-------|------|

| R <sub>thj-amb</sub> | Thermal Resistance Junction-ambient (*) | max. | 90    | °C/W |

(\*) Mounted on a typical PCB layout (see Fig. 7)

### **PIN DESCRIPTION** [Pin Types: I = Input, O = Output, P = Power, A = Analog (passive)] **Power**

| Pin Number         | Pin Name                          | Pin Type | Description                                                                                                                                                  |

|--------------------|-----------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12, 17<br>24,<br>3 | VPOWER<br>VDIG<br>V <sub>CC</sub> | Р        | Positive supply, nominally 5V.                                                                                                                               |

| 7, 42, 64          | GND                               | Р        | Ground.                                                                                                                                                      |

| 10                 | V <sub>REF</sub>                  | I        | All analog signals are referenced to this voltage, nominally 2V.                                                                                             |

| 59                 | POR                               | 0        | POWER ON RESET - Goes low when the supply voltage is below the VOLTAGE GOOD threshold. POR is an open collector output with an internal $20k\Omega$ pull-up. |

| 61                 | POR_DLY                           | А        | POR DELAY. An <u>external parallel RC network from this pin to ground</u> sets the time the POR signal stays active after voltage good.                      |

| 62                 | POR_FILT                          | А        | An external capacitor from this pin to ground provides filtering for the $V_{CC}$ sense input of the POR circuit.                                            |

| 5                  | CPC                               | А        | Charge pump capacitor                                                                                                                                        |

| 6                  | CPL                               | А        | Charge pump inductor                                                                                                                                         |

### Microprocessor Interface

| Pin Number                                   | Pin Name                                     | Pin Type                                      | Description                                                                                                                                                        |

|----------------------------------------------|----------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32 | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | An 8-bit bidirectional data bus which is connected to the internal registers.                                                                                      |

| 38                                           | RD                                           | I                                             | READ A low level on this pin allows the bus to be driven by the IC.                                                                                                |

| 39                                           | WR                                           | I                                             | A low level on $\overline{WRITE}$ allows the IC to read data from the system bus.                                                                                  |

| 35                                           | MC_CS                                        | I                                             | CHIP SELECT A low level on this pin selects the IC for bus transactions.                                                                                           |

| 41                                           | SYSCLK                                       | I                                             | Microprocessor clock used for internal timing.                                                                                                                     |

| 33<br>34<br>35                               | A0<br>A1<br>A2                               |                                               | The lowest three bits of the system address bus; used to address internal registers                                                                                |

| 37                                           | AS                                           | I                                             | ADDRESS STROBE The address appearing on A [0:2] is latched on the falling edge of the AS pulse.                                                                    |

| 43                                           | MC_ERR                                       | 0                                             | A maskable interrupt signal which is asserted low when an error flag in the Status Register is set. The output is open-drain with an internal $20K\Omega$ pull-up. |

| 40                                           | DTACK                                        | 0                                             | An open drain, active low signal used for asynchronous bus transactions.                                                                                           |

### Brushless, Sensorless Motor Driver and 8 bit D/A

| Pin Number     | Pin Name                   | Pin Type | Description                                                                         |

|----------------|----------------------------|----------|-------------------------------------------------------------------------------------|

| 47             | SPIN_DAC                   | 0        | The output of an 8 bit D/A used for the command to the spindle driver.              |

| 48             | SPIN_CMD                   | I        | The input to the spindle driver transconductance amplifier.                         |

| 45             | COIL_CT                    | I        | The center tap of the motor is connected to this pin.                               |

| 53<br>57<br>60 | COIL_U<br>COIL_V<br>COIL_W | 0        | The motor coils are driven by these outputs. Back EMF is also sensed at these pins. |

### PIN DESCRIPTION (continued)

| Pin Number    | Pin Name            | Pin Type | Description                                                                                                                             |

|---------------|---------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 44            | SYNTH_HALL          | 0        | A TTL compatible signal that emulates one of the Hall signals. SYNTH_HALL is an open drain output with an internal $20K\Omega$ pull-up. |

| 49, 50,<br>58 | SPIN SENSE<br>1,2,3 | А        | The current sensing resistors is connected from these pins to ground.                                                                   |

| 46            | PWM_OFFT            | А        | A parallel R-C from this pin to ground sets the PWM mode OFF time.                                                                      |

| 56            | SLEW                | А        | A resistor from this pin to ground sets the slew rate of the driver.                                                                    |

| 51            | S_COMP              | А        | An R-C network from this pin to GND sets the spin driver compensation.                                                                  |

### VCM Driver and 8 bit D/A

| Pin Number | Pin Name   | Pin Type | Description                                                                                                                                                               |

|------------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8          | VCM_DAC    | 0        | The output of an 8 bit D/A used to command the VCM driver.                                                                                                                |

| 9          | VCM_CMD    | I        | VCM driver input command which is relative to V <sub>REF</sub> .                                                                                                          |

| 21         | VCM_COMP   | А        | An R-C network from this pin to ground compensates the VCM driver.                                                                                                        |

| 14         | VCM_RS1    | А        | The high gain current sense resistor is attached from this pin to ground.                                                                                                 |

| 23         | VCM_RS2    | А        | The low gain current sense resistor is connected from this pin to VCM_RS1                                                                                                 |

| 13         | VCM+       | 0        | One end of the load is attached to this pin (Positive).                                                                                                                   |

| 15         | VCM-       | 0        | The other end of the load is attached to this pin (Negative).                                                                                                             |

| 20         | OV_VOLT    | 0        | A voltage which is proportional to the voltage across the load, referenced to $V_{\mbox{\scriptsize REF}}.$                                                               |

| 19         | OV_CUR     | 0        | A voltage which is proportional to the current through the load, referenced to $V_{\mbox{\scriptsize REF}}.$                                                              |

| 16         | OV_SUM-    | I        | Over-velocity summing op-amp inverting input.                                                                                                                             |

| 18         | OV_SUM_OUT | 0        | Over-velocity summing op-amp output.                                                                                                                                      |

| 22         | ISENSE     | 0        | A voltage which is proportional to the current through the VCM load as sensed by the sense resistor. This signal is enabled by setting bit 2 in the VCM Control Register. |

| 54         | VCM_STRB   | I        | The 8 bit input to the VCM D/A is updated on the rising edge of VCM_STRB.                                                                                                 |

### Solenoid Pre-drivers and Power Down Sequencing

| Pin Number   | Pin Name   | Pin Type | Description                                                                                                                                                                                                        |

|--------------|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11,55,<br>63 | V_RECIR    | Р        | Under normal conditions, power is supplied to various blocks via the V_RECIR pin. When external power is removed, energy stored in the rotating spindle is converted to a voltage which supplies the park circuit. |

| 2            | LOAD_SOL   | 0        | When a logic one is written to bit 3 of the VCM Control Register,<br>current is sourced from the LOAD_SOL pin. Otherwise, the pin is high<br>impedance.                                                            |

| 1            | UNLOAD_SOL | 0        | When a logic one is written to bit 4 of the VCM Control Register,<br>current is sourced from the UNLOAD_SOL pin. Otherwise, the pin is<br>high impedance.                                                          |

| 4            | PD_SEQ_CAP | A        | When power is removed, the charge stored on this capacitor keeps selected blocks alive long enough to effect an orderly power down.                                                                                |

| 52           | BRK_DLY    | A        | An external parallel RC network from this point to ground delays activation of the dynamic brake after power is removed.                                                                                           |

### **ELECTRICAL CHARACTERISTICS** ( $V_S = 5V$ , $T_j = 25^{\circ}C$ ; unless otherwise specified) **Power Supply Characteristics**

| Symbol   | Parameter                     | Test Condition                              | Min. | Тур. | Max. | Units |

|----------|-------------------------------|---------------------------------------------|------|------|------|-------|

| Vs       | Supply Voltage                | $V_{\rm S} = V_{\rm P} = V_{\rm CC}$        | 4.5  |      | 5.5  | V     |

| ID-READY | Quiescent Current Dissipation | No load attached VCM and Spin drivers enab. |      |      | 25   | mA    |

| ID_IDLE  |                               | VCM driver disabled Spin driver<br>enabled  |      |      | 20   | mA    |

| ID_SLEEP |                               | VCM and Spin drivers disabled               |      |      | 4    | mA    |

### VCM Driver (Notes 1, 2)

| los                 | Maximum Load Current<br>(Seeking)  | Output Devices A, B, E, F (Fig. 1)                         | 0.3 | A  |

|---------------------|------------------------------------|------------------------------------------------------------|-----|----|

| Іот                 | Maximum Load Current<br>(Traking)  | Output Devices C, D (Fig. 1)                               | 0.1 | A  |

| R <sub>DS(on)</sub> | Source & Sink Out ON<br>Resistance | Output Devices A, B, E, F<br>$T_j = 125^{\circ}C$ (Fig. 1) | 1   | Ω  |

| R <sub>DS(on)</sub> | Sink Out On Resistance             | Output Devices C, D<br>Tj = 125°C (Fig. 1)                 | 2.4 | Ω  |

| R <sub>DS(on)</sub> | Sink Out On Resistance             | Parking Device Tj = 125°C                                  | 12  | Ω  |

| VF                  | Body Diode Forward Drop            | I = 0.3A                                                   | 1.5 | V  |

| Vjump               | Jump Discontinuity (**)            | $R_{sense} = 2.01\Omega$                                   | 30  | mV |

| V <sub>DB</sub>     | Deadband Discontinuity (*)         | $R_{sense} = 2.01\Omega$                                   | 6   | mV |

| V <sub>CMOS</sub>   | Offset (***)                       | $R_{sense} = 2.01\Omega$                                   | 40  | mV |

(\*) The range of input voltages applied to the VCM\_CMD pin (with respect to VREF) for which only negligible current is present in the load. This deadband voltage (VDB) can be expressed either in mV or in LSBs, where one LSB is equal to 11.7mV.

(\*\*) A condition in which the transfer characteristic (i.e., load current vs. VCM\_CMD-VREF) exhibits a slope which is significantly grater than the desired value. The range of currents for which this condition exists is termed IJUMP. This current is referred o the VCM\_CMD input according to the following equation: VJUMP = IJUMP x 3 x RSENSE In this document, RSENSE is assumed to be 2.01 $\Omega$ . VJUMP can be expressed either in mV or in LSBs, where one LSB is equal to 11.7mV.

(\*\*\*) The value of VCM\_CMD (with respect to  $V_{REF}$ ) for which the load current is zero. In parts which exihibit a DEADBAND dicontinuity, the offset is defined to be at the midpoint of the deadband region. RSENSE is assumed to br 2.01 $\Omega$ .

### VCM Current sense amplifier (ISENSE)

| Voff            | Output Offset Voltage        | VCM_RS2 Shorted to GND O/S is<br>V <sub>(Isense)</sub> - V <sub>ref</sub> | -50  | 50   | mV  |

|-----------------|------------------------------|---------------------------------------------------------------------------|------|------|-----|

| G               | Closed Loop Voltage Gain     | 3V/V nominal                                                              | 2.85 | 3.15 | V/V |

| PSRR            | Power Supply Rejection Ratio | at DC                                                                     | 50   |      | dB  |

| BW              | Banwwidth                    |                                                                           | 200  |      | KHz |

| V <sub>OR</sub> | Output Range                 | $V_{CC} = 4.5V$ (note 4)                                                  | -0.2 | 3.5  | V   |

#### VCM Full wave rectifying amplifier

| I <sub>B</sub>   | Input Bias Current           | $VCM\_CMD = V_{ref}$                              |       | 2     | μA  |

|------------------|------------------------------|---------------------------------------------------|-------|-------|-----|

| l <sub>imp</sub> | Input Impedance              | Impedance seen at VCM_CMD<br>wrt V <sub>ref</sub> | 5     |       | KΩ  |

| G                | Closed Loop Gain             |                                                   | 0.320 | 0.347 | V/V |

| PSRR             | Power Supply Rejection Ratio | at DC                                             | 50    |       | dB  |

| GBW              | Unity Gain Bandwidth         |                                                   | 200   |       | KHz |

| CMR              | Input Common Mode Range      | VCM_CMD pin                                       | 0.3   | 3.7   | V   |

| V <sub>OR</sub>  | Output Range                 |                                                   | 0     | 1     | V   |

### ELECTRICAL CHARACTERISTICS (Continued) VCM DAC (Notes 5, 6)

| Symbol           | Parameter                 | Test Condition                                                  | Min.  | Тур. | Max.  | Units  |

|------------------|---------------------------|-----------------------------------------------------------------|-------|------|-------|--------|

| Res              | Resolution                |                                                                 | 8     |      |       | bit    |

| N.L.             | Differential Nonlinearity |                                                                 |       |      | ±0.5  | LSB    |

| I.N.L.           | Integral Nonlinearity     |                                                                 |       |      | ±0.5  | LSB    |

| СТ               | Conversion Time           | From 50% point of $\overline{\text{WR}}$ falling to 1% settling |       |      | 2     | μs     |

| Zo               | Output Z                  |                                                                 |       |      | 100   | Ω      |

| FSTC             | Full Scale Temp. Coeff.   |                                                                 |       |      | 200   | ppm/°C |

| V <sub>OH</sub>  | High Output Voltage       | Relative to $V_{ref}$ Input Code = 7Fh                          | 1.46  |      | 1.52  | V      |

| Vol              | Low Output Voltage        | Relative to Vref Input Code = 80h                               | -1.53 |      | -1.47 | V      |

| V <sub>ZSO</sub> | Zero Scale Offset         | Relative to $V_{ref}$ Input Code = 00                           |       |      | ±10   | mV     |

### Over velocity detector, coil voltage sense amplifier

| Symbol          | Parameter                    | <b>Test Condition</b>                                                                   | Min.  | Тур. | Max.               | Units |

|-----------------|------------------------------|-----------------------------------------------------------------------------------------|-------|------|--------------------|-------|

| Vo              | Output Offset Voltage        | VCM+ = VCM–, within input<br>common mode range.<br>Measure wrt to V <sub>ref</sub>      | -50   |      | +50                | mV    |

| I <sub>BC</sub> | Input Bias Current           | (Note 3)                                                                                |       |      | 10                 | μA    |

| G               | Closed Loop Voltage Gain     | Av = 0.25V/V nominal                                                                    | 0.242 |      | 0.258              | V/V   |

| PSRR            | Power Supply Rejection Ratio | at DC                                                                                   | 50    |      |                    | dB    |

| BW              | Bandwidth                    |                                                                                         | 200   |      |                    | KHz   |

| CMR             | Input Common Mode Range      | Above and below these values the op amp will be in saturation and will not invert sign. | 0     |      | VPOWER             | V     |

| V <sub>DR</sub> | Input Differential Range     |                                                                                         | 0     |      | V <sub>POWER</sub> | V     |

| V <sub>OR</sub> | Output Range                 |                                                                                         | 0.3   |      | 3.5                | V     |

| lo              | Output Current               |                                                                                         | æ400  |      |                    | μΑ    |

### Over velocity detector, coil current sense amplifier

| Symbol         | Parameter                    | Test Condition                                                                                                  | Min.         | Тур. | Max.  | Units |

|----------------|------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------|------|-------|-------|

| Vo             | Output Offset Voltage        | VCM_RS1 shorted to GND for:<br>(a) VCM_CMD < $V_{ref}$ and<br>b) VCM_CMD > $V_{ref}$ . Measure wrt<br>$V_{ref}$ | -50          |      | +50   | mV    |

| G              | Closed Loop Voltage Gain     | Av = 2.5V/V nominal                                                                                             | 2.425        |      | 2.575 | V/V   |

| PSRR           | Power Supply Rejection Ratio | at DC                                                                                                           | 50           |      |       | dB    |

| Bw             | Bandwidth                    |                                                                                                                 | 200          |      |       | KHz   |

| CMR            | Input Common Mode Range      |                                                                                                                 | -0.1         |      | 2     | V     |

| V <sub>R</sub> | Output Range                 |                                                                                                                 | 0.5          |      | 3.5   | V     |

| lo             | Output Current               |                                                                                                                 | <u>+</u> 400 |      |       | mA    |

### ELECTRICAL CHARACTERISTICS (Continued)

### Over velocity detector, summing amplifier

| Symbol          | Parameter                    | <b>Test Condition</b> | Min.         | Тур. | Max. | Units |

|-----------------|------------------------------|-----------------------|--------------|------|------|-------|

| Vo              | Input Offset Voltage         |                       |              |      | 10   | mV    |

| I <sub>BC</sub> | Input Bias Current           |                       |              |      | 1    | μA    |

| G               | Open Loop Gain               |                       | 60           |      |      | dB    |

| PSRR            | Power Supply Rejection Ratio | at DC                 | 50           |      |      | dB    |

| GBW             | Unity Gain Bandwidth         |                       | 200          |      |      | KHz   |

| V <sub>R</sub>  | Output Range                 |                       | 0.5          |      | 3.5  | V     |

| lo              | Output Current               |                       | <u>+</u> 400 |      |      | μA    |

### Over velocity detector, window comparator

| Symbol          | Parameter      | Test Condition               | Min.  | Тур. | Max.  | Units |

|-----------------|----------------|------------------------------|-------|------|-------|-------|

| ts              | Switching Time |                              |       |      | 50    | μs    |

| V <sub>TL</sub> | Low Threshold  | Relative to V <sub>ref</sub> | -1.32 |      | -1.18 | V     |

| VTH             | High Threshold | Relative to Vref             | 1.18  |      | 1.32  | V     |

Solenoid pre-driver (Note 7)

| Symbol          | Parameter      | Test Condition                 | Min. | Тур. | Max. | Units |

|-----------------|----------------|--------------------------------|------|------|------|-------|

| I <sub>OH</sub> | Output Current | $V_{OH} = 1.5V, V_{CC} = 4.4V$ | 10   |      |      | mA    |

### Three phase sensorless motor driver

| Symbol              | Parameter               | Test Condition         | Min. | Тур. | Max. | Units |

|---------------------|-------------------------|------------------------|------|------|------|-------|

| lo                  | Max. Load Current       |                        |      |      | 0.5  | А     |

| R <sub>DS(on)</sub> | Out On Resistance       | T <sub>j</sub> = 125°C |      |      | 0.75 | Ω     |

| dV/dt               | Slew Rate               |                        | 0.05 |      |      | V/µs  |

| VF                  | Body Diode Forward Drop | I = 0.5A               |      |      | 1.2  | V     |

### **Motor Current Sense Amplifier**

| Symbol          | Parameter                   | Test Condition                  | Min.         | Тур. | Max.         | Units      |

|-----------------|-----------------------------|---------------------------------|--------------|------|--------------|------------|

| I <sub>BC</sub> | Input Bias Current          |                                 |              |      | 1            | μA         |

| G               | Closed Loop Voltage Gain    | Low Gain mode<br>High Gain mode | 19.4<br>4.85 |      | 20.6<br>5.15 | V/V<br>V/V |

| PSRR            | Power Supply Rejection Rate | at DC                           | 50           |      |              | dB         |

| BW              | Bandwidth                   |                                 | 200          |      |              | KHz        |

| lo              | Output Range                |                                 | 0            |      | 3.2          | V          |

### Spin DAC (Notes 8, 9)

| Symbol          | Parameter                 | Test Condition                               | Min. | Тур. | Max. | Units  |

|-----------------|---------------------------|----------------------------------------------|------|------|------|--------|

| Res             | Resolution                |                                              | 8    |      |      | bit    |

| NL              | Differential Nonlinearity |                                              |      |      | ±0.5 | LSB    |

| INL             | Integral Nonlinearity     |                                              |      |      | ±0.5 | LSB    |

| СТ              | Conversion Time           | From 50% point of –WR falling to 1% settling |      |      | 5    | μs     |

| Zo              | Output Z                  |                                              |      |      | 14   | KΩ     |

| FSTC            | Full Scale Temp. Coeff.   |                                              |      |      | 200  | ppm/°C |

| V <sub>OH</sub> | High Output Voltage       |                                              | 2.85 |      | 3.15 | V      |

| VoL             | Low Output Voltage        | Unloaded                                     | 0    |      | 20   | mV     |

#### ELECTRICAL CHARACTERISTICS (Continued) Step-up converter

| Symbol          | Parameter       | Test Condition              | Min. | Тур. | Max. | Units |

|-----------------|-----------------|-----------------------------|------|------|------|-------|

| V <sub>SU</sub> | Step-up Voltage | Relative to V <sub>CC</sub> | 7    |      | 11   | V     |

#### Microprocessor interface (Note 10)

| Symbol           | Parameter                 | Test Condition                           | Min. | Тур. | Max. | Units |

|------------------|---------------------------|------------------------------------------|------|------|------|-------|

| Vih              | High Level Input Voltage  |                                          | 3    |      |      | V     |

| V <sub>IL</sub>  | Low Level Input Voltage   |                                          |      |      | 0.8  | V     |

| Vон              | High Level Output Voltage | $VCC = 5V, I_{OH} = 400 \mu A$           | 4.4  |      |      | V     |

| V <sub>OL1</sub> | Low Level Output Voltage  | –MCERR, –POR, –DTACK<br>IOL = 4mA        |      |      | 0.4  | V     |

| V <sub>OL2</sub> | Low Level Output Voltage  | SYNT_ALL<br>IOL = 0.5mA                  |      |      | 0.4  | V     |

| I <sub>IN1</sub> | Input Leakage Current     | –RD, –WR, AS, –MC_CS,<br>SYSCLK, A [0:2] |      |      | 1    | μA    |

| I <sub>IN2</sub> | Input Leakage Current     | D [0:7]                                  |      |      | 10   | μA    |

#### Microprocessor interface timing

| Trddh | Read Data Hold          | 5 | 40 | ns |

|-------|-------------------------|---|----|----|

| Trddt | -RD High to -DTACK high |   | 40 | ns |

| Twrdt | -WR High to -DTACK High |   | 40 | ns |

#### Power on reset

| V <sub>CCHL</sub> | V <sub>CC</sub> Good, HL | V <sub>CC</sub> falling   | 4.2  | 4.4 | V  |

|-------------------|--------------------------|---------------------------|------|-----|----|

| VCCHL             | V <sub>CC</sub> Good, LH | V <sub>CC</sub> rising    | 4.26 | 4.5 | V  |

| T <sub>PLH</sub>  | Rise Time                | C <sub>Load</sub> = 100pF |      | 200 | ns |

| RT                | Response Time            |                           |      | 50  | μs |

#### Notes:

1) The minimum voltage available from the brushless DC motor after power has been removed is 2.7V

2) The voltage available for actuator etraction shall be greater than 0.7V.

3) Sum of l<sub>bias+</sub>(V<sub>ref</sub>/internal resistor + power leakage).

4) Minimum output voltage is set to V<sub>ref</sub> by a resistor network.

5) The VCM DAC shall be monotonic over its full range.

6) The coding of the digital input shall be 2's complement.

7) The voltage available for solenoid operation shall be greater than 1.9V.

8) The Spin DAC shall be monotonic over its full range.

9) The coding of the digital input shall be uniplar (unsigned binary).

10) SYNTH\_HALL, MC\_ERR, DTACK and POR shall have open drain (collector) outputs and internal pull-up resistors. The minimum value of these pull-up resistors shall be  $20K\Omega$ .

#### FUNCTIONAL DESCRIPTION

Inside the system is the sensorless Spindle driver (Spin), the Voice Coil Motor driver (VCM), the Head load/unload predrivers, power sequencing, actuator over-velocity detection, actuator retraction and dynamic braking. The architecture of the system is configured to interface directly to an 8 bit, parallel, microprocessor bus.

During the application of power to the system (power-on), the output drivers are held in a disabled state until the applied voltage reaches the Voltage Good Threshold (VGT). During this period of time the output drivers are disabled, the internal register are set to predetermined states, and the Power On

Reset (POR) signal is held low. The POR signal is held low from the time the applied voltage reaches 0.7V and the VGT. The POR delay is programmable changing the value of a capacitor.

The VCM driver is driven via a D/A and it can be enabled through the VCM driver register. The VCM driver has a gain capability too. This function is to be accomplished by switching the sense resistor used such that the current sensing feedback in the VCM driver has more information and therefore results in lower deadband, offset current, and gain error. An actuator over velocity sensing circuit is incorporated in the system, which is accomplished by measuring BEMF voltage and comparing to a threshold.

The head load /unload mechanisms are just buffers for driving external power transistors. Controlled internally by Bit 3 and Bit 4 of the VCM Driver Register, each output has a current surcing capability of 10mA.

The Sensorless Spindle Driver function can be accessed from the microprocessor over the data bus to the Spin Register and Spin D/A. The Spin D/A is in Binary format. The operation of the Spindle system is controlled entirely by the microprocessor from start-up to speed regulaton. The spin system is accessible by selecting the Spin Control Register with the address 011 on the 3 bit address bus and has the following functions:

- 1)Enable (Bit 0): high to enable the spin system, while a low asserts braking of the spindle motor (if VCR enable is low.)

- 2)Sense amplifier gain (Bit 1): high implies high current mode which is equivalent to low sense amp gain, while a low selects low current mode or high sense amp gain.

- 3)Ŭnipolar/Bipolar (Bit 2): High selects the Unipolar driving mode.

- 4)Run/Search Mode (Bit 3): high selects the run mode whereby the Hall synthesizer output gives speed information while a low asserts the search mode whereby the sequencer is under  $\mu$ P control (stepper function).

- 5)Reset State (Bit 4): a low level resets the commutation state sequencer.

- 6)Incremental state (Bit 5): toggling of the bit increments the sequencer to drive the output stage when search mode is selected.

- 7)Linear/PWM (Bit 6): high selects linear mode of driving for current (speed) regulation while a low sets to PWM mode used during start-up.

Start-up current limiting is accomplished by the output of the microprocessor commanded D/A value. Jammed or stuck rotor detection is also done as part of the microprocessor algorithm. Integrated diode are present in the power bridge for BEMF rectification. This rectified voltage is used to retract the actuator and unload or latch the head assembly.

A conventional Bandgap is used to generate internal biasing for the device as well as the reference voltage for the D/A converters. A Step-up Converter is used to generate a 15V internal supply to drive the upper DMOSs and a regulated 11.6V internal supply to power internal circuits which have voltage head room problem, as well as to drive the lower DMOSs.

A Low Voltage Detector (LVD) is incorporated to sense a severely low value of applied voltage so as to shunt-down the VCM and Spindle drivers. The LVD is activated when the applied voltage drops below 4.3V (+/-0.1V). When a voltage drop is sensed, the LVD:

1. asserts POR, which resets the internal register;

2. retracts the actuator;

3. applies the dynamic brake.

When a severe low value of applied voltage is sensed, the motor control system goes into reset mode and also asserts the POR line to reset other circuits. The sub-circuit which get affected by the reset mode in the motor control system are the Spin Control Register, the VCM Driver Register, the Spindle D/A and the VCM D/A. This effectively disables the spin driver, VCM driver, head load/unload driver and initializes the D/A's at zero output command value.

An Over Velocity Detector circuit is integrated to sense when head arms are moving at a speed which could cause a damaging condition. When an over velocity condition is detected sensing the actuator BEMF, the actuator driver is shut off and held off until the microprocessor has detected this condition and then resets the error and retries the access.

The microprocessor has the possibility to put the device in sleep mode, which is asserted when both the VCM and Spindle drivers are disabled through the internal registers (Enable VCM and Enable Spindle). Under this condition, only the POR circuit is kept "alive", thus power consumption is kept at minimal. Before sleep mode is activated, the microprocessor must move the actuator to the unload zone, unload the recording heads, and apply dynamic braking.

All bits of all the registers are readable by the microprocessor interface. Also there are certain bits of the internal registers which are writable as defined in the Register Definition Tables (Tables 1 -7).

An internal register monitors the internal work of the system and latches certain error condition that are detected.

### REGISTER DEFINITION and 3bit Address Code

Table 1: Status Register (A.C. 001)

| Bit    | Name         | POR Initial<br>Value |

|--------|--------------|----------------------|

| 7      | NC           |                      |

| 6      | NC           |                      |

| 5      | NC           |                      |

| 4      | NC           |                      |

| 3<br>2 | REVERSE SPIN | 1                    |

| 2      | OVER TEMP.   | 1                    |

| 1      | SPIN SENSE   | 0                    |

| 0      | OVER VEL SET | 1                    |

### Table 2: VCM Driver Register (A.C. 010)

| Bit | Name          | POR Initial<br>Value |

|-----|---------------|----------------------|

| 7   | NC            |                      |

| 6   | NC            |                      |

| 5   | NC            |                      |

| 4   | UNLOAD HD     | 0                    |

| 3   | LOAD HD       | 0                    |

| 2   | ENABLE ISENSE | 0                    |

| 1   | HIGH GAIN VCM | 0                    |

| 0   | ENABLE VCM    | 0                    |

### Table 5: Spin D/A Register (A.C. 101)

| Bit    | Name                  | POR Initial<br>Value |

|--------|-----------------------|----------------------|

| 7      | Most Significant Bit  | 0                    |

| 6      | -                     | 0                    |

| 5      |                       | 0                    |

| 4      |                       | 0                    |

| 3<br>2 |                       | 0                    |

| 2      |                       | 0                    |

| 1      |                       | 0                    |

| 0      | Least Significant Bit | 0                    |

### Table 6: Interrupt Mask Register (A.C. 110)

| Bit | Name                 | POR Initial<br>Value |

|-----|----------------------|----------------------|

| 7   | NC                   |                      |

| 6   | NC                   |                      |

| 5   | NC                   |                      |

| 4   | NC                   |                      |

| 3   | NC                   |                      |

| 2   | MASK REV Spin        | 0                    |

| 1   | MASK OVER TEMP ERROR | 0                    |

| 0   | MASK OVER VEL ERROR  | 0                    |

Table 3: Spin Control Register (A.C. 011)

| Bit | Name            | POR Initial<br>Value |

|-----|-----------------|----------------------|

| 7   | NC              | 0                    |

| 6   | LINEAR/PWM      | 0                    |

| 5   | INCREMENT STATE | 0                    |

| 4   | RESET STATE     | 0                    |

| 3   | RUN/SEARCH      | 0                    |

| 2   | UNI/BI          | 0                    |

| 1   | HIGH GAIN SPIN  | 0                    |

| 0   | ENABLE Spin     | 0                    |

| Table 4: | VCM D/A | Register | (A.C. | 100) |

|----------|---------|----------|-------|------|

|----------|---------|----------|-------|------|

| Bit    | Name                  | POR Initial<br>Value |

|--------|-----------------------|----------------------|

| 7      | Most Significant Bit  | 0                    |

| 6      | -                     | 0                    |

| 6<br>5 |                       | 0                    |

| 4      |                       | 0                    |

| 3<br>2 |                       | 0                    |

| 2      |                       | 0                    |

| 1      |                       | 0                    |

| 0      | Least Significant Bit | 0                    |

Table 7: Phase Delay Register (A.C. 111)

| Bit    | Name                  | POR Initial<br>Value |

|--------|-----------------------|----------------------|

| 7      | NC                    |                      |

| 6      | NC                    |                      |

| 5      | NC                    |                      |

| 4      | NC                    |                      |

| 3<br>2 | Most Significant Bit  | 0                    |

| 2      | -                     | 0                    |

| 1      |                       | 0                    |

| 0      | Least Significant Bit | 0                    |

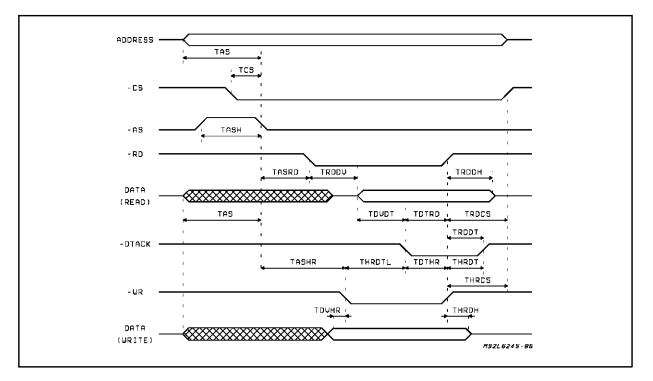

### SYSTEM BUS DESCRIPTION

The system bus is designed as a data acknowledge handshanking bus. At the beginning of the bus cycle the address and chip select are decoded transparently and qualified with read or write going low. On a read operation, data must not be driven for 5nsec after read goes low to allow the bus to clear. Once data is driven, data acknowledge is driven low to notify the processor that data is on the bus and ready to be read. The processor reads the data and responds by raising read. This is an indication that the processor has compleated the read and cycle is complete. Data acknowledge and data must go to high impedence within 20ns to clear the bus for the next

cycle. On a write operation, following write going low and whatever setup time required to latch data, data acknwledge is driven low. This notifies the processor that the cycle can end. This processor responds by raising write, indicating the end of the cycle. Data acknowledge must go to high impedance within 20nsec to clear the bus for the next cycle.

This handshaking design allows a peripheral to control the length of the bus cycle. The peripheral

Figure 1: System Bus Timing (see Table 8)

can take as much time as it needs to drive data onto the bus, then drive DTACK low. Likewise, the peripheral can wait as long as it needs to set up data and latch it (or set up data if WR is used to latch), then drive DTACK low. However, performance is an issue, so even though this control has been given to the peripheral, it must not be abused. All delays are minimized to assure optimum system speed, infact the bus can be driven synchronously (E.G. has regarding DTACK) when procesor clocks below 12MHz are used.

Table 8: System Bus Timing

| Symbol | Description                                |

|--------|--------------------------------------------|

| TAS    | Address Setup Time (non MUX bus; (MUX bus) |

| TCS    | System Select to Address Strobe            |

| TASW   | Address Strobe Width                       |

| TASRD  | Address Strobe to RD                       |

| TRDDV  | RD to Data Driven                          |

| TRDDH  | Read Data Hold                             |

| TRDCS  | RD High to CS High                         |

| TDVDT  | Data Valid to DTACK                        |

| TDTRD  | DTACK to RD High                           |

| TRDDT  | RD High to DTACH High                      |

| TASWR  | Address Strobe to WR                       |

| TDVWR  | Write Data Valid to WR                     |

| TWRDTL | WR to DTACK                                |

| TDTWR  | DTACK to WR High                           |

| TWRCS  | WR High to CS High                         |

| TWRDT  | WR High to DTACK High                      |

| TWRDH  | Write Data Hold                            |

#### THERMAL CHARACTERISTICS

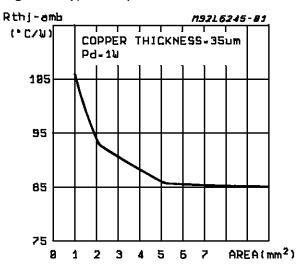

On the application, the L6245 must be soldered on a PCB system. The Traks Area, depending on the lenght and the width of each track, must be between 2 to 10 square mm. An area of 10 mm<sup>2</sup> can give a typ. Thermal Resistance Junction-to-Ambient value of  $85^{\circ}$ C/W (See Fig. 2): this value refer3 to a Total Power Dissipated Power of 1W.

Figure 2: Typical Rth j-amb vs. Tracks Area on PCB

Figure 4: Typical Transient Thermal Impedance vs. Time or Pulse Width. (L6245 mounted on a typical PCB)

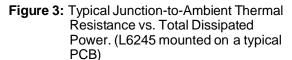

Fig. 9 shows the increase of the Rth j-amb when the Dissipated Power decreases.

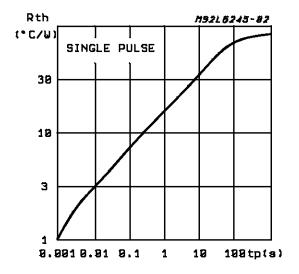

Practically, very useful information is the change of the thermal resistance (Thermal Impedance) versus a single pulse of power width or versus the time the dissipation begins.

Fig. 4 shows this Thermal Impedance trend.

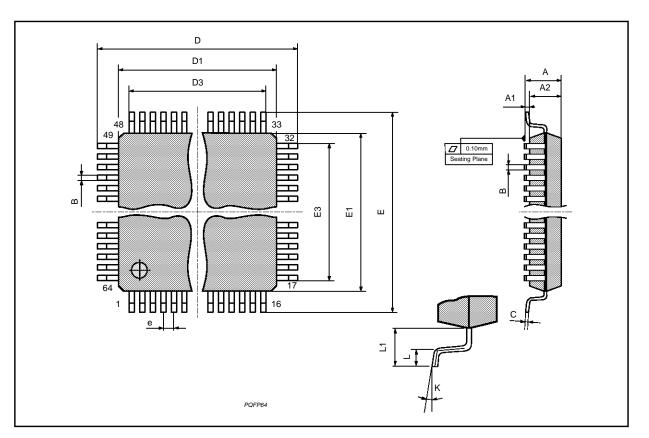

| DIM. | mm    |       |          | inch       |        |        |

|------|-------|-------|----------|------------|--------|--------|

| Diw. | MIN.  | TYP.  | MAX.     | MIN.       | TYP.   | MAX.   |

| А    |       |       | 3.40     |            |        | 0.134  |

| A1   | 0.25  |       |          | 0.010      |        |        |

| A2   | 2.55  | 2.80  | 3.05     | 0.100      | 0.110  | 0.120  |

| В    | 0.30  |       | 0.45     | 0.0118     |        | 0.0177 |

| С    | 0.13  |       | 0.23     | 0.005      |        | 0.009  |

| D    | 16.95 | 17.20 | 17.45    | 0.667      | 0.677  | 0.687  |

| D1   | 13.90 | 14.00 | 14.10    | 0.547      | 0.551  | 0.555  |

| D3   |       | 12.00 |          |            | 0.472  |        |

| е    |       | 0.80  |          |            | 0.0315 |        |

| Е    | 16.95 | 17.20 | 17.45    | 0.667      | 0.677  | 0.687  |

| E1   | 13.90 | 14.00 | 14.10    | 0.547      | 0.551  | 0.555  |

| E3   |       | 12.00 |          |            | 0.472  |        |

| К    |       |       | 0°(min.) | , 7°(max.) |        |        |

| L    | 0.65  | 0.80  | 0.95     | 0.026      | 0.0315 | 0.0374 |

| L1   |       | 1.60  |          |            | 0.063  |        |

### PQFP64 PACKAGE MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thaliand - United Kingdom - U.S.A.