# 256 x 256 DIGITAL SWITCHING MATRIX

PRELIMINARY DATA

■ 256 INPUT AND 256 OUTPUT CHANNEL CMOS DIGITAL SWITCHING MATRIX COM-PATIBLE WITH M088

SGS-THOMSON MICROELECTRONICS

- BUILDING BLOCK DESIGNED FOR LARGE CAPACITY ELECTRONIC EXCHANGES, SUB-SYSTEMS AND PABX

- NO EXTRA PIN NEEDED FOR NOT-BLOCK-ING SINGLE STAGE AND HIGHER CAPACITY SYNTHESIS BLOCKS (512 or 1024 channels)

- EUROPEAN TELEPHONE STANDARD COM-PATIBLE (32 serial channels per frame)

- PCM INPUTS AND OUTPUTS MUTUALLY COMPATIBLE

- ACTUAL INPUT-OUTPUT CHANNEL CON-NECTIONS STORED AND MODIFIED VIA AN ON CHIP 8-BIT PARALLEL MICROPROCES-SOR INTERFACE

- TYPICAL BIT RATE : 2Mbit/s

- TYPICAL SYNCHRONIZATION RATE : 8KHz (time frame is 125µs)

- 5V POWER SUPPLY

- CMOS & TTL INPUT/OUTPUT LEVELS COM-PATIBLE

- HIGH DENSITY ADVANCED 1.2µm HCMOS3 PROCESS

#### Main instructions controlled by the microprocessor interface

- CHANNEL CONNECTION/DISCONNECTION

- OUTPUT CHANNEL DISCONNECTION

- INSERTION OF A BYTE ON A PCM OUTPUT CHANNEL/DISCONNECTION

- TRANSFER TO THE MICROPROCESSOR OF A SINGLE PCM OUTPUT CHANNEL SAMPLE

- TRANSFER TO THE MICROPROCESSOR OF A SINGLE OUTPUT CHANNEL CONTROL WORD

- TRANSFER TO THE MICROPROCESSOR OF A SELECTED 0 CHANNEL PCM INPUT DATA

#### ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                       | Test Conditions              | Unit |

|------------------|---------------------------------|------------------------------|------|

| V <sub>CC</sub>  | Supply Voltage                  | -0.3 to 7                    | V    |

| VI               | Input Voltage                   | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Vo               | Off State Output Voltage        | -0.3 to V <sub>CC</sub> +0.3 | V    |

| lo               | Current at Digital Outputs      | 30                           | mA   |

| Ptot             | Total Package Power Dissipation | 1.5                          | W    |

| T <sub>stg</sub> | Storage Temperature Range       | -65 to 150                   | °C   |

| T <sub>op</sub>  | Operating Temperature Range     | 0 to 70                      | °C   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operating conditions of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

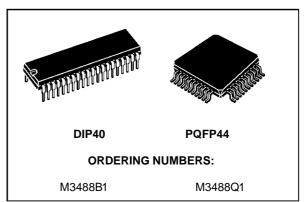

**PIN CONNECTIONS** (Top views)

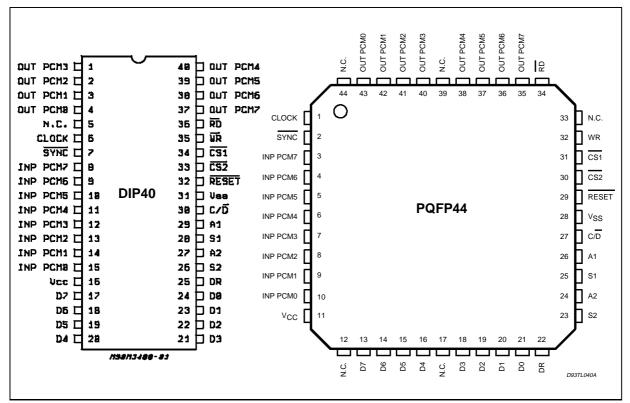

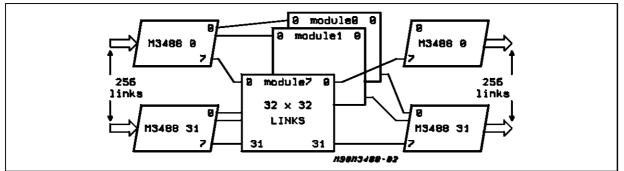

#### **EXCHANGE NETWORKS APPLICATIONS**

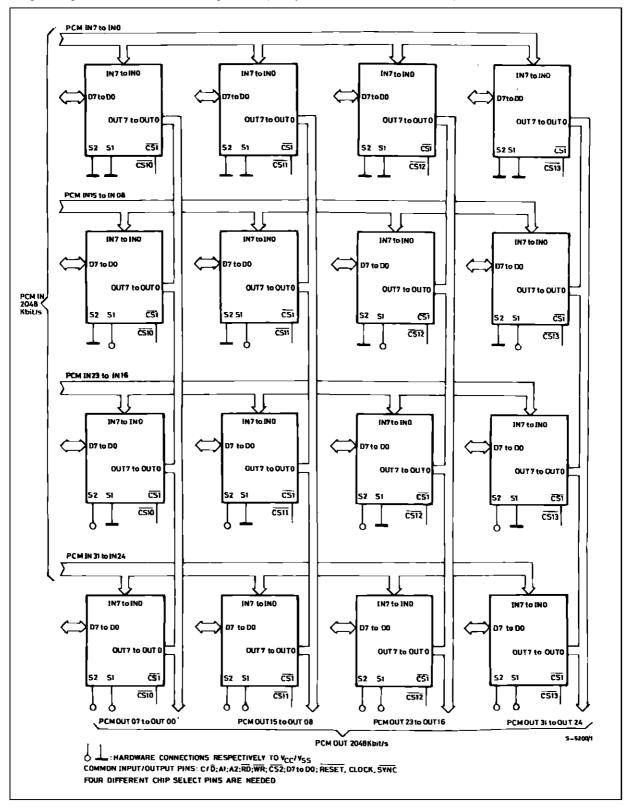

256 PCM links network (160 or 192 DSM) : the 32 x 32 link module shown on the next page.

2048 PCM links network (1792 or 2048 DSM) : the 256 x 256 link network is shown above.

# EXCHANGE NETWORKS APPLICATIONS (continued)

Single Stage/Sixteen Devices Configuration (32 by 32 links or 1024 channels).

SGS-THOMSON MICROELECTRONICS

<u>۲</u>۲

#### **BLOCK DIAGRAM**

# RECOMMENDED OPERATING CONDITIONS

| Symbol         | Parameter                       | Value        | Unit |

|----------------|---------------------------------|--------------|------|

| Vcc            | Supply Voltage                  | 4.75 to 5.25 | V    |

| Vi             | Input Voltage                   | 0 to 5.25    | V    |

| Vo             | Off State Input Voltage         | 0 to 5.25    | V    |

| CLOCK<br>Freq. | Input Clock Frequency           | 4.096        | MHz  |

| SYNC Freq.     | Input Synchronization Frequency | 8            | KHz  |

| Top            | Operating Temperature           | 0 to 70      | °C   |

CAPACITANCES (measurement freq. = 1MHz; T<sub>op</sub> = 0 to 70°C; unused pins tied to V<sub>SS</sub>)

| Symbol           | Parameter          | Pins (*)                       | Min. | Тур. | Max. | Unit |

|------------------|--------------------|--------------------------------|------|------|------|------|

| Cı               | Input Capacitance  | 6 to 15; 26 to 30; 32 to 36    |      |      | 5    | pF   |

| C <sub>I/O</sub> | I/O Capacitance    | 20 to 24                       |      |      | 15   | рF   |

| Co               | Output Capacitance | 1 to 4; 17 to 19; 25; 37 to 40 |      |      | 10   | pF   |

D.C. ELECTRICAL CHARACTERISTICS (T<sub>amb</sub> = 0 to 70°C, V<sub>CC</sub> = 5V ±5%) All D.C. characteristics are valid 250µs after V<sub>CC</sub> and clock have been applied.

| Symbol          | Parameter                   | Pins (*)                                    | Test Condition                                                                                                    | Min. | Тур. | Max.            | Unit |

|-----------------|-----------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|------|-----------------|------|

| VILC            | Clock Input Low Level       | 6                                           |                                                                                                                   | -0.3 |      | 0.8             | V    |

| VIHC            | Clock Input High Level      | 6                                           |                                                                                                                   | 2.4  |      | V <sub>CC</sub> | V    |

| VIL             | Input Low Level             | 7 to 15<br>20 to 24<br>26 to 30<br>32 to 36 |                                                                                                                   | -0.3 |      | 0.8             | V    |

| V <sub>IH</sub> | Input High Level            | 7 to 15<br>20 to 24<br>26 to 30<br>32 to 36 |                                                                                                                   | 2    |      | V <sub>CC</sub> | V    |

| Vон             | Output High Voltage (Level) | 17 to 25                                    | l <sub>OH</sub> = 5mA                                                                                             | 2.4  |      |                 | V    |

| lон             | Output High Current         |                                             | V <sub>OH</sub> = 2.4V                                                                                            | 5    |      |                 | mA   |

| V <sub>OL</sub> | Output Low Voltage (Level)  | 1 to 4                                      | l <sub>OL</sub> = 5mA                                                                                             |      |      | 0.4             | V    |

| I <sub>OL</sub> | Output Low Current          | 37 to 40<br>17 to 25                        | $V_{OL} = 0.4 V$                                                                                                  | 5    |      |                 | mA   |

| Ι <sub>Ι</sub>  | Input Leakage Current       | 6 to 15<br>26 to 30<br>32 to 36             | $V_{IN} = 0$ to $V_{CC}$                                                                                          |      |      | 5               | μΑ   |

| I <sub>DL</sub> | Data Bus Leakage Current    | 17 to 24                                    | $V_{IN} = 0$ to $V_{CC}$<br>$V_{CC}$ applied; Pins 35<br>and 36 tied to $V_{CC}$ ,<br>after Device Initialization |      |      | ±5              | μA   |

| Icc             | Supply Current              | 16                                          | Clock Freq. = 4.096MHz                                                                                            |      | 15   | 30              | mA   |

$(\ensuremath{^*})$  The pin number is referred to the DIP40 version.

| Signal        | Symbol              | Parameter                 | Test Condition                         | Min.            | Тур. | Max. | Unit |

|---------------|---------------------|---------------------------|----------------------------------------|-----------------|------|------|------|

| CK (clock)    | tск                 | Clock Period              |                                        | 230             | 244  |      | ns   |

|               | t <sub>WL</sub>     | Clock Low Level Width     |                                        | 100             |      |      | ns   |

|               | twн                 | Clock High Level Width    |                                        | 100             |      |      | ns   |

|               | t <sub>R</sub>      | Rise Time                 |                                        |                 |      | 25   | ns   |

|               | t <sub>F</sub>      | Fall Time                 |                                        |                 |      | 25   | ns   |

| SYNC          | t <sub>SL</sub>     | Low Level Setup Time      |                                        | 60              |      |      | ns   |

| (frame pulse) | t <sub>HL</sub>     | Low Level Hold Time       |                                        | 30              |      |      | ns   |

|               | t <sub>SH</sub>     | High Level Setup Time     |                                        | 80              |      |      | ns   |

|               | twн                 | High Level Width          |                                        | tск             |      |      | ns   |

| PCM Input     | ts                  | Setup Time                |                                        | 5               |      |      | ns   |

| Busses        | t <sub>H</sub>      | Hold Time                 |                                        | +40             |      |      | ns   |

| PCM Output    | t <sub>PD min</sub> | Propagation time          |                                        | 45              | 110  |      | ns   |

| Busses        |                     | referred to CK low level  | C <sub>L</sub> = 150pF                 |                 |      |      |      |

| Open Drain    | t <sub>PD max</sub> | Propagation time          | R∟ = 1K                                |                 | 110  | 140  | ns   |

|               |                     | referred to CK high level |                                        |                 |      |      |      |

| RESET         | t <sub>SL</sub>     | Low Level Setup Time      |                                        | 60              |      |      | ns   |

|               | t <sub>HL</sub>     | Low Level Hold Time       |                                        | 30              |      |      | ns   |

|               | tsH                 | High Level Setup Time     |                                        | 80              |      |      | ns   |

|               | t <sub>WH</sub>     | High level Width          |                                        | t <sub>CK</sub> |      |      | ns   |

| WR, RD        | t <sub>WL</sub>     | Low Lvel Width            |                                        | 100             |      |      | ns   |

|               | twн                 | High Level Width          |                                        | tск             |      |      | ns   |

|               | t <sub>REP</sub>    | Repetition Interval       |                                        | see             |      |      | ns   |

|               |                     | between Active Pulses     |                                        | formula         |      |      |      |

|               | tsH                 | High Level Setup Time     | $t_{REP} 40 + 2 t_{CK} + t_{WL(CK)} +$ | 0               |      |      | ns   |

|               |                     | to Active Read Strobe     | + t <sub>R(СК)</sub>                   |                 |      |      |      |

|               | tнн                 | High Level Hold Time      |                                        | 15              |      |      | ns   |

|               |                     | from Active Write Strobe  |                                        |                 |      |      |      |

|               | t <sub>R</sub>      | Rise Time                 |                                        |                 |      | 60   | ns   |

|               | t <sub>F</sub>      | Fall Time                 |                                        |                 |      | 60   | ns   |

A.C. ELECTRICAL CHARACTERISTICS (T<sub>amb</sub> = 0 to 70°C, V<sub>CC</sub> = 5V ±5%) All A.C. characteristics are valid 250µs after V<sub>CC</sub> and clock have been applied. C<sub>L</sub> is the max. capacitive load.

| Signal                 | Symbol                                | Parameter                                                                                  | Test Condition                | Min.              | Тур. | Max.              | Unit |

|------------------------|---------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------|-------------------|------|-------------------|------|

| CS1, <u>CS2</u>        | $t_{SL(\overline{CS}-\overline{WR})}$ | Low level setup time                                                                       | Active Case                   | 0                 |      |                   | ns   |

|                        | $t_{HL}(\overline{CS}-\overline{WR})$ | to WR falling edge<br>Low Level hold time                                                  | Active Case                   | 0                 |      |                   | ns   |

|                        | $t_{\overline{SH}}(\overline{CS}-WR)$ | from WR rising edge<br>Hig <u>h L</u> evel setup time<br>to WR falling edge                | Inactive Case                 | 0                 |      |                   | ns   |

|                        | tHH(CS-WR)                            | High level hold time<br>from WR rising edge                                                | Inactive Case                 | 0                 |      |                   | ns   |

|                        | $t_{\overline{SL}}(\overline{CS}-RD)$ | Low level setup time<br>to RD falling edge                                                 | Active Case                   | 0                 |      |                   | ns   |

|                        | $t_{\overline{HL}}(\overline{CS}-RD)$ | Low level hold time<br>from RD rising edge                                                 | Active Case                   | 0                 |      |                   | ns   |

|                        | tsH(CS-RD)                            | High level setup time<br>RD falling edge                                                   | Inactive Case                 | 0                 |      |                   | ns   |

|                        | tHH(CS-RD)                            | High level hold time from RD                                                               | Inactive Case                 | 0                 |      |                   | ns   |

| C/D                    | ts(C/D-WR)                            | Setup time to write strobe end                                                             |                               | 130               |      |                   | ns   |

|                        | tH(C/D-WR)                            | Hold time from<br>write strobe end                                                         |                               | 15                |      |                   | ns   |

|                        | $\overline{t_{S}(C/D)}$ -RD)          | Setup time to read strobe start                                                            |                               | 20                |      |                   | ns   |

|                        | t <sub>H</sub> (C/D-RD)               | Hold time from read strobe end                                                             |                               | 20                |      |                   | ns   |

| A1, S1,<br>A2, S2      | $t_{S(match-WR)}$                     | Setup time to write strobe end                                                             |                               | 130               |      |                   | ns   |

| (match<br>inputs)      | t <sub>H(match-WR)</sub>              | Hold time from<br>strobe end                                                               |                               | 15                |      |                   | ns   |

|                        | $t_{S(match-\overline{RD})}$          | Setup time to read strobe start                                                            |                               | 20                |      |                   | ns   |

|                        | t <sub>H(match-RD)</sub>              | Hold time from read<br>strobe end                                                          |                               | 20                |      |                   | ns   |

| DR<br>(data            | t <sub>W</sub><br>t <sub>PD</sub>     | Low state width<br>DR output delay                                                         | Instructions 5 and 6          |                   |      | 2.t <sub>CK</sub> | ns   |

| ready)                 |                                       | from write strobe end (active command)                                                     | Instruction 5, $C_L = 150 pF$ | 4.t <sub>CK</sub> |      | 7.t <sub>CK</sub> | ns   |

| D0 to D7<br>(interface | t <sub>S(BUS-WR)</sub>                | Input setup time to<br>write strobe end                                                    |                               | 130               |      |                   | ns   |

| bus)                   | t <sub>H(BUS</sub> -WR)               | Input hold time<br>from write strobe end                                                   |                               | 15                |      |                   | ns   |

|                        | tpd(bus)                              | Propagation time<br>from (active) falling<br>Edge of read strobe                           | C <sub>L</sub> = 200pF        |                   |      | 120               | ns   |

|                        | t <sub>HZ(BUS)</sub>                  | Propagation time<br>from (active) rising<br>Edge of read strobe<br>to high impedance state | C <sub>L</sub> = 200pF        |                   |      | 80                | ns   |

## A.C. ELECTRICAL CHARACTERISTICS (continued)

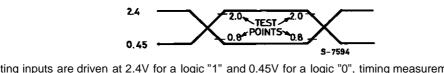

## A.C. TESTING, OUTPUT WAVEFORM

A.C. testing inputs are driven at 2.4V for a logic "1" and 0.45V for a logic "0", timing measurement are made at 2.0V for a logic "1" and 0.8V for a logic "0".

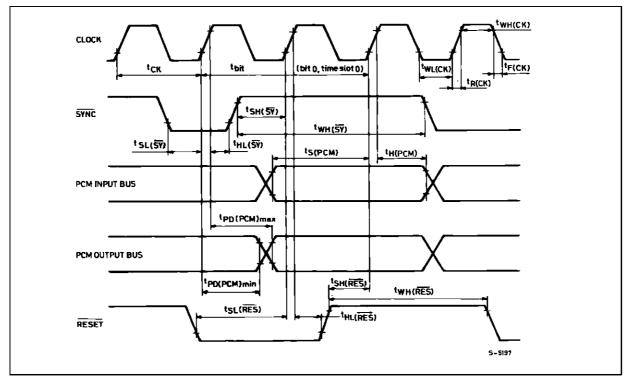

#### PCM TIMING, RESET, SYNC

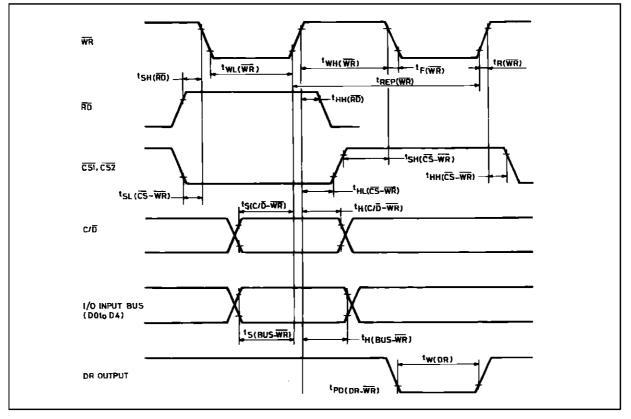

# WRITE OPERATION TIMING

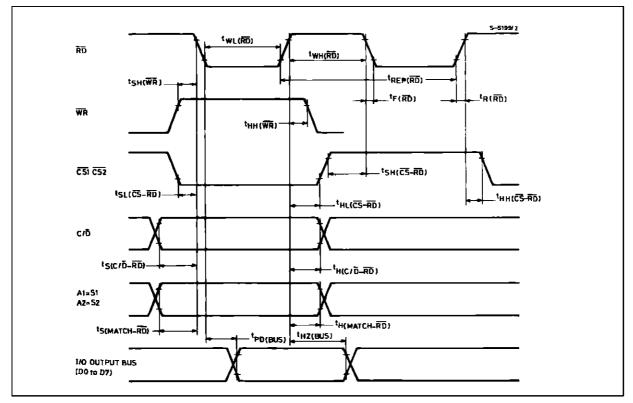

#### **READ OPERATION TIMING**

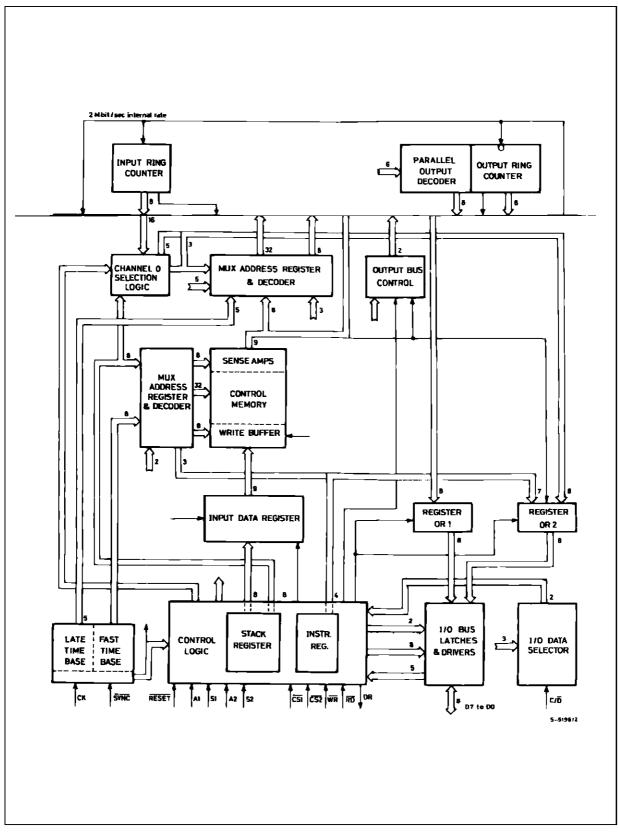

#### **GENERAL DESCRIPTION**

The M3488 is intended for large telephone switching systems, mainly central exchanges, digital line concentrators and private branch exchanges where a distributed microcomputer control approach is extensively used. It consists of a speech memory (SM), a control memory (CM), a serial/parallel and a parallel/serial converter, an internal parallel bus, an interface (8 data lines, 11 control signals) and dedicated control logic.

By means of repeated clock division two timebases are generated. These are preset from an external synchronization signal to two specific count numbers so that sequential scanning of the bases give synchronous addresses to the memories and I/O channel controls. Different preset count numbers are needed because of processing delays and data path direction. The timebase for the input channels is delayed and the timebase for output channels is advanced with respect to the actual time.

Each serial PCM input channel is converted to parallel data and stored in the speech memory at the beginning of any new time slot (according to first timebase) in the location determined by input pin number and time slot number. The control memory CM maintains the correspondences between input and output channels. More exactly, for any output pin/output channel combination the control memory gives either the full address of the speech memory location involved in the PCM transfer or an 8-bit word to be supplied to the parallel/serial output converter. A 9<sup>th</sup> bit at each CM location defines the data source for output links, low for SM, high for CM.

The late timebase is used to scan the output channels and to determine the pins to be serviced within each channel; enough idle cycles are left to the microprocessor for asynchronous instruction processing.

Two 8-bit registers OR1 and OR2 supply feedback data for control or diagnostic purposes; OR1 comes from internal bus i.e. from memories, OR2 gives an opcode copy and additional data to the microcomputer. A four byte-five bit stack register and an instruction register, under microcomputer control, store input data available at the interface.

Dedicated logic, under control of the microprocessor interface, extracts the 0 channel content of any selected PCM input bus, using spare cycles of SM.

# **PINS FUNCTION**

| Symbol            | Name                    | Pin Assi               | gnement                  |

|-------------------|-------------------------|------------------------|--------------------------|

|                   |                         | DIP40                  | PQFP44                   |

| D7 to D0          | Data bus                | 17 to 24               | 13 to 21                 |

| C/D               | Input control           | 30                     | 27                       |

| A1, S1, A2, S2    | Address select or match | 26 to 29               | 23 to 26                 |

| CS1, CS2          | Chip select             | 33, 34                 | 30, 31                   |

| WR                | Data transfer enable    | 35                     | 32                       |

| RD                | Read enable             | 36                     | 34                       |

| DR                | Data ready              | 25                     | 22                       |

| RESET             | RESET control           | 32                     | 29                       |

| CLOCK             | Input master clock      | 6                      | 1                        |

| SYNC              | Input synchronization   | 7                      | 2                        |

| IN PCM 7 to 0     | PCM input bus           | 8 to 15                | 3 to 10                  |

| OUT PCM 7<br>to 0 | PCM output bus          | 37 to 40 and<br>1 to 4 | 35 to 38 and<br>40 to 43 |

#### **PIN DESCRIPTION**

#### D7 to D0

Data bus pins. The bidirectional bus is used to transfer data and instructions to/from the microprocessor. D0 is the least significant digit. The output bus is 8 bits wide ; input is only 5 bits wide. (D4 to D0)

The bus is tristate and cannot be used while RESET is held low.

The meaning of input data, such as bus or channel numbers, and of expected output data is specified in detail by the instruction description. (Pagg. 12-14)

## C/D (pin 30)

Input control pin, select pin. In a write operation C/D = 0 qualifies any bus content as data, while C/D = 1 qualifies it as <u>an</u> opcode. In a read operation OR1 is selected by C/D = 0, OR2 by C/D = 1.

## A1, S1, A2, S2

Address select or match pins. In a multi-chip configuration (e.g. <u>a</u> single stage matrix expansion), using the same CS pins, the match condition (A1 = S1 and A2 = S2) leaves the command instruction as defined; on the contrary the mismatch condition modifies the execution as follows : instructions 1 and 3 are reversed to channel disconnection, instruction 5 is unaffected, instructions 2-4-6 are cancelled (not executed).

Bus reading takes place only on match condition, instruction flow is in any case affected.

Each pins couple is commutative : in a multichip configuration pins S1 and S2 give a hard-wired address selection for individual matrixes, while in single configuration S1 and A1 or S2 and A2 are normally tied together.

#### CS1, CS2

Commutative chip select pins. They enable the device to perform valid read/write operations (active low). Two pins allow row/column selection with different types of microprocessors ; normally one is tied to ground.

# WR

Pin WR, when CS1 and CS2 are low, enables data transfer from microprocessor to the device. Data or opcode and controls are latched on WR rising edge. Because of internal clock resynchronization one single additional requirement is recommended in order to produce a simultaneous instruction execution in a multichip configuration: WR rising edge has to be 20 to  $20 + t_{WL(CK)}$  nsec late relative to clock falling edge.

# RD

When CS1 and CS2 <u>are</u> low and match condition exists, a low level on RD enables a register OR1 or OR2 read operation, through the bidirectional bus.

In addition, the rising edge of  $\overline{RD}$  latches C/ $\overline{D}$  and the match condition pins in order to direct the internal flow of operations. Because of internal clock resynchronization, one single additional requirement is recommended in order to produce a simultan<u>eous</u> instruction flow in a multichip configuration: the RD rising edge has to be 20 to 20 + twL(CK) nsec late relative to clock falling edge.

## DR

Data ready. Normally high, DR output pin goes low to tell the microprocessor that :

a) the instruction code was found to be invalid;

b) executing instruction 5 an active output channel was found in the whole matrix array, that is a CM word not all "ones" was found in a configuration of devices sharing the same CS pins;

c) executing instruction 6 "0 channel extraction" took place and OR2 was loaded with total number of messages inserted on 0 time slot.

DR is active low about two clock cycles in case  $\bf{b}$  and  $\bf{c}$ ; in case a it is left low until a valid instruction code is supplied.

# RESET

RESET control pin is normally used at the very beginning to initialize the device or the network. Any <u>logical status</u> is reset and CM is set to all "ones" after RESET going low.

The internal initialization routine takes one time frame whatever the RESET width on low level (minimum one cycle roughly), but it is repeated an integer number of time frames as long as RESET is found low during 0 time slot.

Initialization pulls the interface bus immediately to a high impedance state. After the CM has been set to all "ones" the PCM output channels are also set to high impedance state.

#### CLOCK

Input master clock. Typical frequency is 4.096MHz. First division gives an internal clock controlling the input and output channels bit rate.

# SYNC

Input synchronization signal is active low. Typical frequency is 8kHz.

Internal time bases are forced by synchronism to an assigned count number in order to restore channels and bit sequential addressing to a known state. Count difference between the bases is 32, corresponding to two time slots, that is the minimum PCM propagation time, or latency time.

#### INP PCM 7 to INP PCM 0

PCM input busses or pins ; they accept a standard 2Mbit/s rate. Bit 1 (sign bit) is the first of the serial sequence; in a parallel conversion it is left adjusted as the most significant digit.

## OUT PCM 7 to OUT PCM 0

PCM output busses or pins ; bit rate and organization are the same as input pins.

Output buffers are open drain CMOS .

The device drives the output channels theoretically one bit time before they can be exploited as logical input channels (bit and slot compatibility is preserved): this feature allows inputs and outputs to be tied together cancelling any analog delay of digital outputs up to

$t_{DEL max} = t_{bit} - t_{PD(PCM)max} + t_{PD(PCM)min}$

# MIXED RD and WR OPERATIONS

In principle  $\overline{RD}$  and  $\overline{WR}$  operations are allowed in any order within specification constraints.

In practive, <u>only</u> one <u>control</u> pin is low at any given time when CS1 and CS2 are enabled.

If by mistake or hardware failure both  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  pins are low, the interface bus is internally pushed to tristate condition as long as  $\overline{\text{WR}}$  is held low and input registers are protected.

Registers OR<u>1 and OR2 can be read in any order</u> with a single RD strobe using C/D as multiplexing control; never the less this procedure is not recommended because the device is directed for instruction flow only according to data latched by RD rising edge.

Multiple RD operations of the same kind are allowed without affecting the instruction flow : only "new" OR1 or OR2 read operations step the flow.

Input and output registers are held for sure in the previous state for the first 3 cycles following an opcode or an OR2 read.

# FUNCTIONAL DESCRIPTION OF SPECIFIC MICROPROCESSOR OPERATIONS

The device, under microprocessor control, performs the following instructions :

- **1 CHANNEL CONNECTION**

- **2 CHANNEL DISCONNECTION**

- 3 LOADING OF A BYTE ON A PCM OUTPUT CHANNEL

- 4 TRANSFER OF A SINGLE PCM OUTPUT CHANNEL SAMPLE

- 5 TRANSFER OF A SINGLE OUTPUT CHANNEL CONTROL WORD

- 6 TRANSFER OF A SELECTED 0 CHANNEL PCM INPUT DATA ACCORDING TO AN 8-BIT MASK PREVIOUSLY STORED IN THE "EXPECTED MESSAGES" REGISTER

The instruction flow is as follows.

Any input protocol is started by the microprocessor interface loading the internal stack register with 2 bytes (4 bytes for instructions 1 and 3) qualified as data bytes  $\underline{by} C/D = 0$  and a specific opcode qualified by C/D = 1 (match condition is normally needed).

After the code is loaded in the instruction register it is immediately checked to see whether it is acceptable and if not it is rejected. If accepted the instruction is also processed as regards match condition and is appended for execution during the memories' spare cycles.

Four cases are possible :

a) the code is not valid; execution cannot take place, the DR output pin is reset to indicate the error; all registers are saved;

b) the code is valid for types 2, 4 and 6 but it is unmatched; execution cannot take place, DR is not affected.

c) the code is valid for types 1 and 3 and it is unmatched; the instruction is interpreted as a channel disconnection.

d) the code is valid and is either matched or of type 5; the instruction is processed as received.

Validation control takes only two cycles out of a total execution time of 4 to 7 cycles; the last operation is updating of the content of registers OR1 and OR2, according to the following instruction tables.

During a very long internal operation (device initialization after RESET going high or execution of instruction 6) a new set of data bytes with a valid opcode is accepted while a wrong code is rejected. At the end of the current routine execution takes place in the same way as described before.

At the end of an instruction it is normally recommended to read one or both registers. To exploit instruction 6, however, it is mandatory to read register OR2. This is because instruction 6, used between other short instructions of type 1 to 5, must have priority and can be enabled only after the short instructions have been completed. Instruction 6 normally has a long process and a special flow which is described below.

First a not-all-zero mask is stored in the "expected messages" register and in another "background" register. This operation starts the second phase of instruction 6 which is called "channel 0 extraction" and is repeated at the beginning of any new time frame. At the beginning of the time frame a new copy of activated channels to be extracted is made from the "background register" and put in the "expected messages" register. In addition the latter register is modified to indicate the exact number of messages that have arrived. The term messages covers any input 0 channel data with starting sequence different from the label 01. So using this label the number of expected messages can be reduced to correspond to the number of effective messages. If and only if the residual number is different from zero will the device start the extraction protocol at the end of the current routine.

The procedure is as follows: the DR output is pulsed low as a two cycle interrupt request and OR2 is loaded with the total number of active channels to be extracted.

The transfer of OR2 content to the microprocessor continues the extraction which consists of repeated steps of OR1 and OR2 loading, indicating respectively the message and the incoming bus number. Reading the registers in the order OR1, OR2 must be continued until completion or until the time frame runs out.

With a new time frame a new extraction process begins, resuming the copy operation from the background register.

During extraction the active channels are scanned from the highest to the lowest number (from 7 to 0). While extraction is being carried out the time interval requirements between active rising edges of RD are minimum 4 to 7 t<sub>CK</sub> for sequence OR2 - OR1 and minimum 2 times t<sub>CK</sub> for sequence OR1 - OR2. More details are given in the following tables.

## INSTRUCTION TABLES

The most significant digits of OR2 A7, A6, A5 are a copy of the PCM selected output bus; the least significant digits of OR2 are the opcode, C8 is the control bit. In any case parentheses () define actual register content.

| <b>(</b> | Contro | ol Sig | nals |    |                    |                  |                  | Data           | Bus            |                |                |                  | Notes                                                                            |

|----------|--------|--------|------|----|--------------------|------------------|------------------|----------------|----------------|----------------|----------------|------------------|----------------------------------------------------------------------------------|

| Match    | C/D    | CS     | WR   | RD | D7                 | D6               | D5               | D4             | D3             | D2             | D1             | D0               | NOLES                                                                            |

| Х        | 0      | 0      | 0    | 1  | Х                  | Х                | Х                | Х              | Х              | Bi2            | Bi1            | Bi0              | 1 <sup>st</sup> Data Byte: selected input bus.                                   |

| Х        | 0      | 0      | 0    | 1  | Х                  | Х                | Х                | Ci4            | Ci3            | Ci2            | Ci1            | Ci0              | 2 <sup>nd</sup> Data Byte: selected input channel.                               |

| х        | 0      | 0      | 0    | 1  | Х                  | Х                | Х                | Х              | Х              | Bo2            | Bo1            | Bo0              | 3 <sup>rd</sup> Data Byte: selected output bus.                                  |

| Х        | 0      | 0      | 0    | 1  | Х                  | Х                | Х                | Co4            | Co3            | Co2            | Co1            | Co0              | 4th Data Byte: selected output channel.                                          |

| yes/no   | 1      | 0      | 0    | 1  | Х                  | Х                | Х                | Х              | 0              | 0              | 0              | 1                | Instruction Opcode                                                               |

| yes      | 0      | 0      | 1    | 0  | C7<br>(1<br>(Bi2   | C6<br>1<br>Bi1   | C5<br>1<br>Bi0   | C4<br>1<br>Ci4 | C3<br>1<br>Ci3 | C2<br>1<br>Ci2 | C1<br>1<br>Ci1 | C0<br>1)<br>Ci0) | OR1: CM content copy, that is,<br>for mismatch condition,<br>for match condition |

| yes      | 1      | 0      | 1    | 0  | A7<br>(Bo2<br>(Bo2 | A6<br>Bo1<br>Bo1 | A5<br>Bo0<br>Bo0 | C8<br>1<br>0   | 0<br>0<br>0    | 0<br>0<br>0    | 0<br>0<br>0    | 1<br>1)<br>1)    | OR2: that is,<br>for mismatch condition<br>for match condition                   |

#### INSTRUCTION 1: CHANNEL CONNECTION

| C     | Contro | ol Sig | nals |    |            |    |           | Data   | Bus    |        |        |         | Notes                                                |

|-------|--------|--------|------|----|------------|----|-----------|--------|--------|--------|--------|---------|------------------------------------------------------|

| Match | C/D    | CS     | WR   | RD | D7         | D6 | D5        | D4     | D3     | D2     | D1     | D0      | Notes                                                |

| Х     | 0      | 0      | 0    | 1  | Х          | Х  | Х         | Х      | Х      | Bo2    | Bo1    | Bo0     | 1 <sup>st</sup> Data Byte: selected output bus.      |

| Х     | 0      | 0      | 0    | 1  | Х          | Х  | Х         | Co4    | Co3    | Co2    | Co1    | Co0     | 2 <sup>nd</sup> Data Byte: selected output channel.  |

| Yes   | 1      | 0      | 0    | 1  | Х          | Х  | Х         | Х      | 0      | 0      | 1      | 0       | Instruction Opcode                                   |

| Yes   | 0      | 0      | 1    | 0  | 1          | 1  | 1         | 1      | 1      | 1      | 1      | 1       | OR1: CM Content Copy (output<br>channel is inactive) |

| Yes   | 1      | 0      | 1    | 0  | A7<br>(Bo2 | -  | A5<br>Bo0 | 1<br>1 | 0<br>0 | 1<br>1 | 1<br>1 | 1<br>1) | OR2: that is.                                        |

#### INSTRUCTION2: OUTPUT CHANNEL DISCONNECTION

#### INSTRUCTION3: LOADING ON A PCM OUTPUT CHANNEL FROM A MICROPROCESSOR BYTE

| C      | Contro | ol Sig | nals |    |                  |                |                | Data           | Bus            |                |                |                  | Notes                                                                            |

|--------|--------|--------|------|----|------------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------|----------------------------------------------------------------------------------|

| Match  | C/D    | CS     | WR   | RD | D7               | D6             | D5             | D4             | D3             | D2             | D1             | D0               | Notes                                                                            |

| х      | 0      | 0      | 0    | 1  | х                | Х              | Х              | Х              | Х              | Ci7            | Ci6            | Ci5              | 1 <sup>st</sup> Data Byte: most significant digits to be inserted.               |

| х      | 0      | 0      | 0    | 1  | х                | х              | Х              | Ci4            | Ci3            | Ci2            | Ci1            | Ci0              | 2 <sup>nd</sup> Data Byte: least significant digits to be inserted.              |

| Х      | 0      | 0      | 0    | 1  | Х                | Х              | Х              | Х              | Х              | Bo2            | Bo1            | Bo0              | 3 <sup>rd</sup> Data Byte: selected output bus.                                  |

| Х      | 0      | 0      | 0    | 1  | Х                | Х              | Х              | Co4            | Co3            | Co2            | Co1            | Co0              | 4th Data Byte: selected output channel                                           |

| Yes/no | 1      | 0      | 0    | 1  | Х                | Х              | Х              | Х              | 0              | 1              | 0              | 0                | Instruction Opcode                                                               |

| Yes    | 0      | 0      | 1    | 0  | C7<br>(1<br>(Ci7 | C6<br>1<br>Ci6 | C5<br>1<br>Ci5 | C4<br>1<br>Ci4 | C3<br>1<br>Ci3 | C2<br>1<br>Ci2 | C1<br>1<br>Ci1 | C0<br>1)<br>Ci0) | OR1: CM content copy, that is,<br>for mismatch condition,<br>for match condition |

| Yes    | 1      | 0      | 1    | 0  | A7<br>(Bo2       | A6<br>Bo1      | A5<br>Bo0      | 1<br>1         | 0<br>0         | 1<br>1         | 1<br>1         | 1<br>1)          | OR2: that is.                                                                    |

#### INSTRUCTION4: TRANSFER OF A SINGLE PCM SAMPLE

| 0     | Contro | ol Sig | nals |    |            |           |           | Data     | Bus      |          |          |          | Notes                                                             |

|-------|--------|--------|------|----|------------|-----------|-----------|----------|----------|----------|----------|----------|-------------------------------------------------------------------|

| Match | C/D    | CS     | WR   | RD | D7         | D6        | D5        | D4       | D3       | D2       | D1       | D0       | Notes                                                             |

| Х     | 0      | 0      | 0    | 1  | Х          | Х         | Х         | Х        | Х        | Bo2      | Bo1      | Bo0      | 1 <sup>st</sup> Data Byte: selected output bus.                   |

| Х     | 0      | 0      | 0    | 1  | Х          | Х         | Х         | Co4      | Co3      | Co2      | Co1      | Co0      | 2 <sup>nd</sup> Data Byte: selected output channel.               |

| Yes   | 1      | 0      | 0    | 1  | Х          | Х         | Х         | Х        | 1        | 0        | 1        | 1        | Instruction Opcode                                                |

| Yes   | 0      | 0      | 1    | 0  | C7<br>S7   | C6<br>S6  | C5<br>S5  | C4<br>S4 | C3<br>S3 | C2<br>S2 | C1<br>S1 | C0<br>S0 | OR1: CM Content Copy if C8 = 1; or<br>SM Content Sample if C8 = 0 |

| Yes   | 1      | 0      | 1    | 0  | A7<br>(Bo2 | A6<br>Bo1 | A5<br>Bo0 | 1<br>1   | 0<br>0   | 1<br>1   | 1<br>1   | 1<br>1)  | OR2: that is.                                                     |

Notes: S7...S0 is a parallel copy of a PCM data, S7 is the most significant digit and the first of the sequence.

## INSTRUCTION5: TRANSFER OF AN OUTPUT CHANNEL CONTROL WORD

| 0     | Contro | l Sig | nals |    |      |     |     | Data | Bus |     | Notes |     |                                                 |

|-------|--------|-------|------|----|------|-----|-----|------|-----|-----|-------|-----|-------------------------------------------------|

| Match | C/D    | CS    | WR   | RD | D7   | D6  | D5  | D4   | D3  | D2  | D1    | D0  | Notes                                           |

| Х     | 0      | 0     | 0    | 1  | Х    | Х   | Х   | Х    | Х   | Bo2 | Bo1   | Bo0 | 1 <sup>st</sup> Data Byte: selected output bus. |

| Х     | 0      | 0     | 0    | 1  | Х    | Х   | Х   | Co4  | Co3 | Co2 | Co1   | Co0 |                                                 |

| Yes   | 1      | 0     | 0    | 1  | Х    | Х   | Х   | Х    | 1   | 0   | 0     | 0   | Instruction Opcode                              |

| Yes   | 0      | 0     | 1    | 0  | C7   | C6  | C5  | C4   | C3  | C2  | C1    | C0  | OR1: CM selected CM word copy.                  |

| Yes   | 1      | 0     | 1    | 0  | A7   | A6  | A5  | C8   | 1   | 0   | 0     | 0   | OR2: that is.                                   |

| res   | 1      | 0     | 1    | 0  | (Bo2 | Bo1 | Bo0 | C8   | 1   | 0   | 0     | 0)  |                                                 |

#### INSTRUCTION6: CHANNEL 0 SELECTION MASK STORE/DATA TRANSFER

| Control Signals                                   |     |    |    |    | Data Bus           |    |    |     |      |                                |                                | Notes |                                                                  |  |

|---------------------------------------------------|-----|----|----|----|--------------------|----|----|-----|------|--------------------------------|--------------------------------|-------|------------------------------------------------------------------|--|

| Match                                             | C/D | CS | WR | RD | D7                 | D6 | D5 | D4  | D3   | D2                             | D1                             | D0    | Notes                                                            |  |

| х                                                 | 0   | 0  | 0  | 1  | х                  | Х  | Х  | Х   | Х    | Mi7                            | Mi6                            | Mi5   | 1 <sup>st</sup> Data Byte: most sign. digits of selection mask.  |  |

| х                                                 | 0   | 0  | 0  | 1  | х                  | Х  | Х  | Mi4 | Mi3  | Mi2                            | Mi1                            | Mi0   | 2 <sup>nd</sup> Data Byte: least sign. digits of selection mask. |  |

| Yes                                               | 1   | 0  | 0  | 1  | Х                  | Х  | Х  | Х   | 1    | 1                              | 1                              | 0     | Instruction Opcode                                               |  |

| Mask store control                                |     |    |    |    |                    |    |    |     |      |                                |                                |       |                                                                  |  |

| Yes                                               | 0   | 0  | 1  | 0  | (previous content) |    |    |     |      | ent)                           | OR1: register is not affected. |       |                                                                  |  |

| Yes                                               | 1   | 0  | 1  | 0  | N2                 | N1 | N0 | Tn  | 1    | 1                              | 1                              | 0     | OR2: see below.                                                  |  |

| First Data Transfer (after DR going low)          |     |    |    |    |                    |    |    |     |      |                                |                                |       |                                                                  |  |

| Yes                                               | 0   | 0  | 1  | 0  | (previous content) |    |    |     | ent) | OR1: register is not affected. |                                |       |                                                                  |  |

| Yes                                               | 1   | 0  | 1  | 0  | N2                 | N1 | N0 | Tn  | 1    | 1                              | 1                              | 0     | OR2: see below.                                                  |  |

| Repeated Data Transfer (after first OR2 transfer) |     |    |    |    |                    |    |    |     |      |                                |                                |       |                                                                  |  |

| Yes                                               | 0   | 0  | 1  | 0  | S7                 | S6 | S5 | S4  | S3   | S2                             | S1                             | S0    | OR1: expected message stored in SM.                              |  |

| Yes                                               | 1   | 0  | 1  | 0  | P2                 | P1 | P0 | Fn  | 1    | 1                              | 1                              | 0     | OR2: see below.                                                  |  |

Notes: 1. About mask bits Mi0 to Mi7 a logic "0" level means disabling condition, a logic "1" level means enabling condition.

2. A null mask or a RESET pulse clear the mask and the deep background mask registers and disable channel 0 extraction function. 3. Reading of OR2 is optional after mask store or redefinition, because function is activated only by not-null mask writing.

4. After mask store (N2 N1 N0) is the sum of activated channels, after DR is the sum of active channels; Tn = 1/0 means activation/suppression of the function after store while after DR only Tn = 1 can appear to tell a not-null configuration to be extracted.

5. Reading of OR2 is imperative after DR in order to step the data transfer ; reading of OR1 is also needed to scan in descending order the priority register. Relevant messages only are considered, that means only messages with a MSD label different from 01.

6. (P2 P1 P0) is the PCM bus on which the message copied in OR1 was found; Fn is a continuation bit telling respectively on level 1/0 for any more/no more extraction step to be performed.

#### M3488 WITH LESS PCM LINKS THAN 32 **CHANNELS**

It is also possible to use M3488 when the PCM frames are made up of a number of channels other than 32.

Suppose that the PCM frames are made up of N-Channels, which will be numbered from 0 to (N-1).

Each PCM frame will thus be made up of a number of bits multiplied by 8; this exactly equal to (N 8).

Also, in this case, it is necessary to respect the timing relationship between the different signals shown on the data sheet; in particular, a relation-ship is always carefully made between the rising edge of SYNC and the first clock (CK) bit contained in the slot time for bit 0 of channel 0.

In order to use M3488 with these frames, it is sufficient, using the data bytes sent by the microprocessor, to modify the numbering of a few channels.

In particular :

- a) in all instructions in which reference is made to the input channel (N-1), the number 31 should be substituted for the number (N-1);

- b) in all instructions in which reference is made to the output channel 0, the number N should be substituted for the number 0.

| DIM.  |                    | mm    |       | inch  |       |       |  |  |  |

|-------|--------------------|-------|-------|-------|-------|-------|--|--|--|

| Diwi. | MIN.               | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |  |  |  |

| А     |                    |       | 2.45  |       |       | 0.096 |  |  |  |

| A1    | 0.25               |       |       | 0.010 |       |       |  |  |  |

| A2    | 1.95               | 2.00  | 2.10  | 0.077 | 0.079 | 0.083 |  |  |  |

| В     | 0.30               |       | 0.45  | 0.012 |       | 0.018 |  |  |  |

| с     | 0.13               |       | 0.23  | 0.005 |       | 0.009 |  |  |  |

| D     | 12.95              | 13.20 | 13.45 | 0.51  | 0.52  | 0.53  |  |  |  |

| D1    | 9.90               | 10.00 | 10.10 | 0.390 | 0.394 | 0.398 |  |  |  |

| D3    |                    | 8.00  |       |       | 0.315 |       |  |  |  |

| е     |                    | 0.80  |       |       | 0.031 |       |  |  |  |

| E     | 12.95              | 13.20 | 13.45 | 0.510 | 0.520 | 0.530 |  |  |  |

| E1    | 9.90               | 10.00 | 10.10 | 0.390 | 0.394 | 0.398 |  |  |  |

| E3    |                    | 8.00  |       |       | 0.315 |       |  |  |  |

| L     | 0.65               | 0.80  | 0.95  | 0.026 | 0.031 | 0.037 |  |  |  |

| L1    |                    | 1.60  |       |       | 0.063 |       |  |  |  |

| К     | 0°(min.), 7°(max.) |       |       |       |       |       |  |  |  |

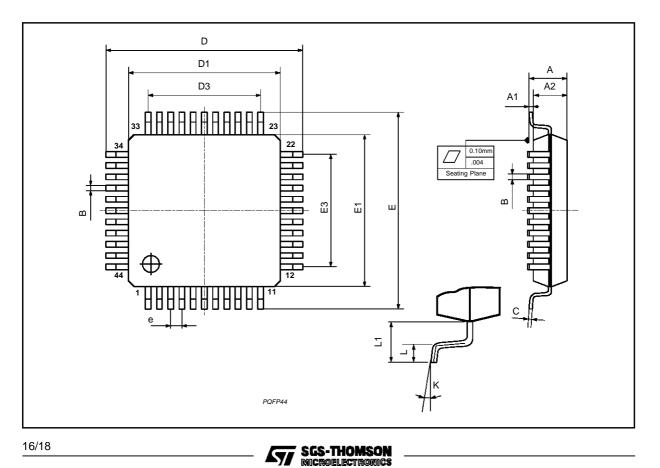

# PQFP44 (10 x 10) PACKAGE MECHANICAL DATA

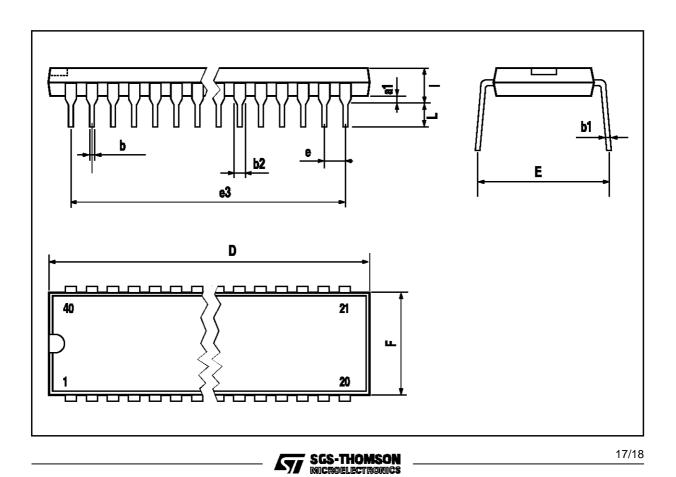

## **DIP40 PACKAGE MECHANICAL DATA**

| DIM. |      | mm    |       | inch  |       |       |  |

|------|------|-------|-------|-------|-------|-------|--|

|      | MIN  | ТҮР   | МАХ   | MIN   | ТҮР   | МАХ   |  |

| a1   |      | 0.63  |       |       | 0.025 |       |  |

| b    |      | 0.45  |       |       | 0.018 |       |  |

| b1   | 0.23 |       | 0.31  | 0.009 |       | 0.012 |  |

| b2   |      | 1.27  |       |       | 0.050 |       |  |

| D    |      |       | 52.58 |       |       | 2.070 |  |

| E    | 15.2 |       | 16.68 | 0.598 |       | 0.657 |  |

| е    |      | 2.54  |       |       | 0.100 |       |  |

| e3   |      | 48.26 |       |       | 1.900 |       |  |

| F    |      |       | 14.1  |       |       | 0.555 |  |

| I    |      | 4.445 |       |       | 0.175 |       |  |

| L    |      | 3.3   |       |       | 0.130 |       |  |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1996 SGS-THOMSON Microelectronics - Printed in Italy - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco -The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.