# DUAL HIGH SIDE SWITCH WITH DUAL POWER MOS GATE DRIVER (BRIDGE CONFIGURATION)

| TYPE     | R <sub>DS(on)</sub> | I <sub>OUT</sub> | V <sub>DSS</sub> |

|----------|---------------------|------------------|------------------|

| VND670SP | 30 mΩ               | 15 A             | 40 V             |

- OUTPUT CURRENT:15A PER CHANNEL

- 5V LOGIC LEVEL COMPATIBLE INPUTS

- GATE DRIVE FOR TWO EXTERNAL POWER MOS

- UNDERVOLTAGE AND OVERVOLTAGE SHUT-DOWN

- OVERVOLTAGE CLAMP

- THERMAL SHUT DOWN

- CROSS-CONDUCTION PROTECTION

- **CURRENT LIMITATION**

- VERY LOW STAND-BY POWER CONSUMPTION

- PWM OPERATION UP TO 10 KHz

- PROTECTION AGAINST: LOSS OF GROUND AND LOSS OF V<sub>CC</sub>

- REVERSE BATTERY PROTECTION (\*)

#### DESCRIPTION

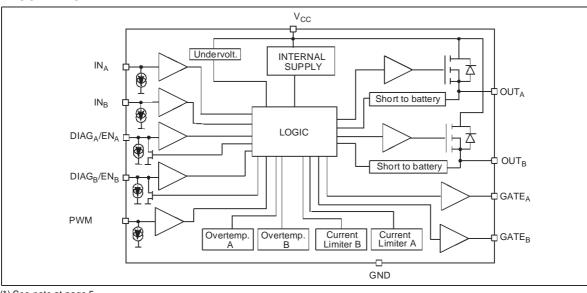

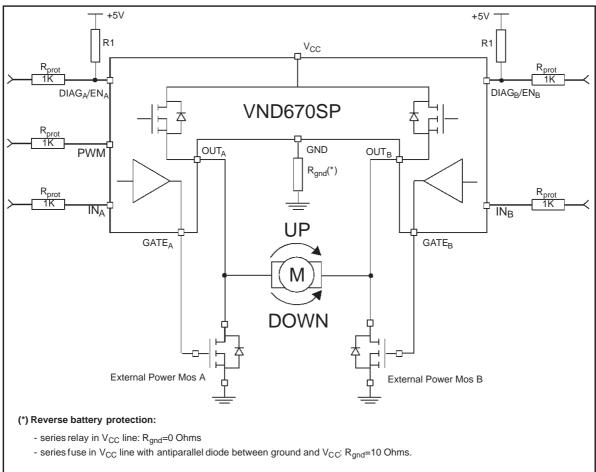

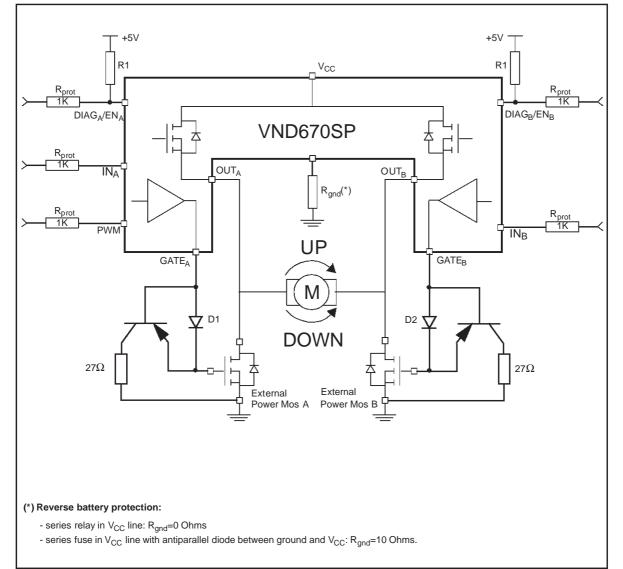

The VND670SP is a monolithic device made using STMicroelectronics VIPower technology, intended for driving motors in full bridge

#### **BLOCK DIAGRAM**

configuration. The device integrates two 30 m $\Omega$  Power MOSFET in high side configuration, and provides gate drive for two external Power MOSFET used as low side switches. IN<sub>A</sub> and IN<sub>B</sub> allow to select clockwise or counter clockwise drive or brake; DIAG<sub>A</sub>/EN<sub>A</sub>, DIAG<sub>B</sub>/EN<sub>B</sub> allow to disable one half bridge and feedback diagnostic. Built-in thermal shut-down, combined with a current limiter, protects the chip in overtemperature and short circuit conditions. Short to battery protects the external connected low-side Power MOSFET.

(\*) See note at page 5

June 2000

# ABSOLUTE MAXIMUM RATING

| Symbol            | Parameter                                      | Value      | Unit |

|-------------------|------------------------------------------------|------------|------|

| V <sub>CC</sub>   | Supply voltage                                 | -0.3 40    | V    |

| I <sub>max1</sub> | Maximum output current (continuous)            | 15         | A    |

| I <sub>max2</sub> | Maximum output current (250 ms pulse duration) | 20         | A    |

| I <sub>R</sub>    | Reverse output current (continuous)            | -15        | A    |

| I <sub>IN</sub>   | Input current                                  | +/- 10     | mA   |

| I <sub>EN</sub>   | Enable pin current                             | +/- 10     | mA   |

| I <sub>pw</sub>   | PWM pin current                                | +/- 10     | mA   |

| l <sub>gs</sub>   | Output gate current                            | +/- 20     | mA   |

| V <sub>ESD</sub>  | Electrostatic discharge (R=1.5kΩ, C=100pF)     | 2000       | V    |

| Тj                | Junction operating temperature                 | -40 to 150 | °C   |

| T <sub>STG</sub>  | Storage temperature                            | -55 to 150 | °C   |

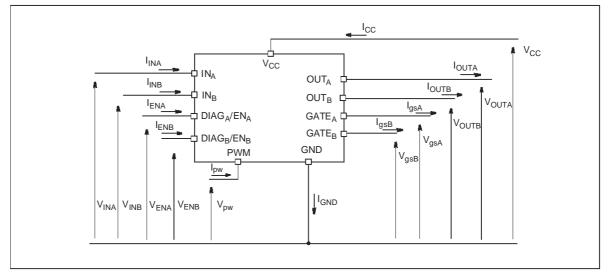

#### CURRENT AND VOLTAGE CONVENTIONS

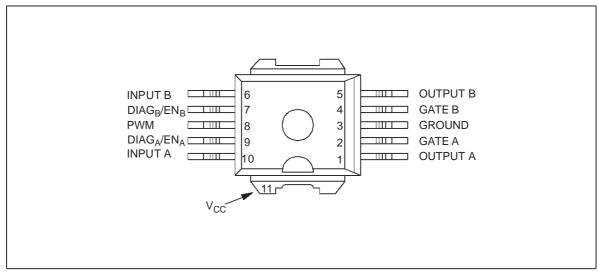

### **CONNECTION DIAGRAM (TOP VIEW)**

# THERMAL DATA

| Symbol                   | Parameter                                      | Value | Unit |      |

|--------------------------|------------------------------------------------|-------|------|------|

| R <sub>thj-case</sub>    | Thermal resistance junction-case (per channel) | (MAX) | 1.4  | °C/W |

| R <sub>thj-amb</sub> (*) | Thermal resistance junction-ambient            | (MAX) | 50   | °C/W |

(\*) When mounted using the recommended pad size on FR-4 board (See AN515 Application Note).

# **ELECTRICAL CHARACTERISTICS** (V<sub>CC</sub>=9V up to 18V; -40°C<T<sub>j</sub><150°C; unless otherwise specified)

# POWER

| Symbol             | Parameter                 | Test Conditions                                           | Min | Тур | Max | Unit |

|--------------------|---------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>    | Operating supply voltage  |                                                           | 5.5 |     | 26  | V    |

| R <sub>ON</sub>    | On state resistance       | I <sub>LOAD</sub> =12A                                    |     |     | 50  | mΩ   |

| NON                | On state resistance       | I <sub>LOAD</sub> =12A<br>I <sub>LOAD</sub> =12A; Tj=25°C |     | 26  | 30  | mΩ   |

| 1                  | Supply surrent            | ON state                                                  |     |     | 15  | mA   |

| I <sub>S</sub>     | Supply current            | OFF state                                                 |     |     | 40  | μΑ   |

| Vgate              | Gate output voltage       |                                                           | 5.0 |     | 8.5 | V    |

| V <sub>gs,cl</sub> | Gate output clamp voltage | I <sub>gs</sub> =-1 mA                                    | 6.8 | 7.4 | 8.5 | V    |

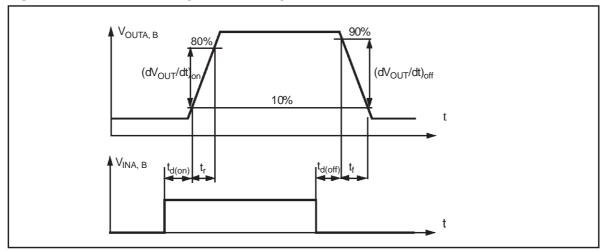

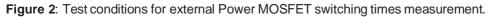

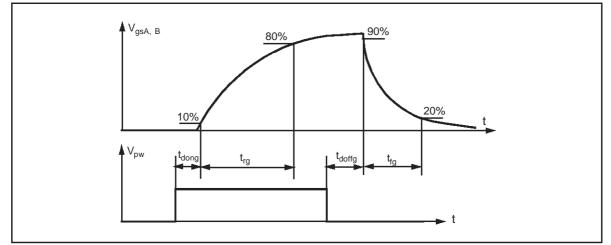

# SWITCHING (V<sub>CC</sub>=13V, $R_{LOAD}$ =1.1 $\Omega$ )

| Symbol                                 | Parameter                           | Test Conditions                          | Min | Тур | Max  | Unit |

|----------------------------------------|-------------------------------------|------------------------------------------|-----|-----|------|------|

| t <sub>D(on)</sub>                     | Turn-on delay time                  |                                          |     | 50  | 150  | μs   |

| t <sub>D(off)</sub>                    | Turn-on delay time                  |                                          |     | 45  | 135  | μs   |

| t <sub>r</sub>                         | Output voltage rise time            | Input rise time < 1µs (see fig. 1)       |     | 50  | 150  | μs   |

| t <sub>f</sub>                         | Output voltage fall time            | $111put lise time < 1\mu s (see lig. 1)$ |     | 40  | 120  | μs   |

| (dV <sub>OUT</sub> /dt) <sub>on</sub>  | Turn-on voltage slope               |                                          |     | 160 | 500  | V/ms |

| (dV <sub>OUT</sub> /dt) <sub>off</sub> | Turn-off voltage slope              |                                          |     | 230 | 1200 | V/ms |

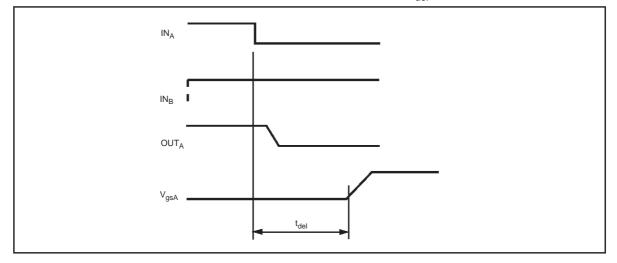

| t <sub>dong</sub>                      | V <sub>gs</sub> Turn-on delay time  | C1=4.7nF                                 |     | 0.5 | 2    | μs   |

| t <sub>rg</sub>                        | V <sub>gs</sub> rise time           | Break to ground configuration            |     | 2.6 | 10   | μs   |

| t <sub>doffg</sub>                     | V <sub>gs</sub> Turn-off delay time | 5 5                                      |     | 1.0 | 5.0  | μs   |

| t <sub>fg</sub>                        | V <sub>gs</sub> fall time           | (see fig. 2)                             |     | 2.2 | 10   | μs   |

| t <sub>del</sub>                       | External MOSFET turn-on dead time   | (see fig. 3)                             | 150 | 600 | 1800 | μs   |

#### PROTECTION AND DIAGNOSTIC

| Symbol           | Parameter                                              | Test Conditions               | Min                 | Тур | Max                 | Unit |

|------------------|--------------------------------------------------------|-------------------------------|---------------------|-----|---------------------|------|

| V <sub>USD</sub> | Undervoltage shut-down                                 |                               |                     |     | 5.5                 | V    |

| V <sub>OV</sub>  | Overvoltage shut-down                                  |                               | 36                  | 43  |                     | V    |

| I <sub>LIM</sub> | Current limitation                                     |                               | 30                  | 45  |                     | А    |

| T <sub>TSD</sub> | Thermal shut-down temperature                          | V <sub>IN</sub> = 3.25 V      | 150                 | 170 | 200                 | °C   |

| V <sub>ocl</sub> | Output turn-off clamp voltage                          | I <sub>LOAD</sub> =12A, L=6mH | V <sub>CC</sub> -55 |     | V <sub>CC</sub> -41 | V    |

| V <sub>sat</sub> | External MOSFET saturation voltage detection threshold |                               | 2.5                 | 4.2 | 5.5                 | V    |

# ELECTRICAL CHARACTERISTICS (continued) PWM

| Symbol              | Parameter                 | Test Conditions              | Min                  | Тур                  | Max                  | Unit |

|---------------------|---------------------------|------------------------------|----------------------|----------------------|----------------------|------|

| V                   | PWM low level             |                              |                      |                      | 1.5                  | V    |

| V <sub>pwl</sub>    | voltage                   |                              |                      |                      | 1.5                  | v    |

| Ipwl                | PWM pin current           | V <sub>pw</sub> =1.5V        | 1                    |                      |                      | μΑ   |

| V                   | PWM high level            |                              | 3.25                 |                      |                      | V    |

| V <sub>pwh</sub>    | voltage                   |                              | 5.25                 |                      |                      | v    |

| I <sub>pwh</sub>    | PWM pin current           | V <sub>pw</sub> =3.25V       |                      |                      | 10                   | μΑ   |

| Vpwhhyst            | PWM hysteresis voltage    |                              | 0.5                  |                      |                      | V    |

| V                   | PWM clamp voltage         | I <sub>pw</sub> = 1 mA       | V <sub>CC</sub> +0.3 | V <sub>CC</sub> +0.7 | V <sub>CC</sub> +1.0 | V    |

| V <sub>pwcl</sub>   | F WW clamp voltage        | $I_{pw} = -1 \text{ mA}$     | -5.0                 | -3.5                 | -2.0                 | V    |

| V <sub>pwtest</sub> | Test mode PWM pin voltage |                              | -3.5                 | -2.0                 | -0.5                 | V    |

| Ipwtest             | Test mode PWM pin current | V <sub>pwtest</sub> = -2.0 V | -2000                | -500                 |                      | μΑ   |

# LOGIC INPUT (IN<sub>A</sub>/IN<sub>B</sub>)

| Symbol             | Parameter                | Test Conditions                               | Min  | Тур  | Max  | Unit |

|--------------------|--------------------------|-----------------------------------------------|------|------|------|------|

| V <sub>IL</sub>    | Input low level voltage  |                                               |      |      | 1.5  | V    |

| I <sub>INL</sub>   | Input current            | V <sub>IN</sub> =1.5 V                        | 1    |      |      | μA   |

| V <sub>IH</sub>    | Input high level voltage |                                               | 3.25 |      |      | V    |

| I <sub>INH</sub>   | Input current            | V <sub>IN</sub> =3.25 V                       |      |      | 10   | μA   |

| V <sub>IHYST</sub> | Input hysteresis voltage |                                               | 0.5  |      |      | V    |

| V                  | Input clamp voltage      | I <sub>IN</sub> =1mA                          | 6.8  | 7.4  | 8.5  | V    |

| V <sub>ICL</sub>   | Input clamp voltage      | I <sub>IN</sub> =1mA<br>I <sub>IN</sub> =-1mA | -1.0 | -0.7 | -0.3 | V    |

# ENABLE (LOGIC I/O PIN)

| Symbol             | Parameter                       | Test Conditions                                               | Min  | Тур  | Max  | Unit |

|--------------------|---------------------------------|---------------------------------------------------------------|------|------|------|------|

|                    |                                 | Normal operation                                              |      |      |      |      |

| V <sub>ENL</sub>   | Enable low level voltage        | (DIAG <sub>X</sub> /EN <sub>X</sub> pin acts as an input pin) |      |      | 1.5  | V    |

| I <sub>ENL</sub>   | Enable pin current              | V <sub>EN</sub> = 1.5 V                                       | 1    |      |      | μΑ   |

|                    |                                 | Normal operation                                              |      |      |      |      |

| V <sub>ENH</sub>   | Enable high level voltage       | (DIAG <sub>X</sub> /EN <sub>X</sub> pin acts as an input pin) | 3.25 |      |      | V    |

| I <sub>ENH</sub>   | Enable pin current              | V <sub>EN</sub> = 3.25 V                                      |      |      | 10   | μΑ   |

|                    |                                 | Normal operation                                              |      |      |      |      |

| V <sub>EHYST</sub> | Enable hysteresis voltage       | (DIAG <sub>X</sub> /EN <sub>X</sub> pin acts as an input pin) | 0.5  |      |      | V    |

| V                  | Enable clamp voltage            | I <sub>EN</sub> =1mA                                          | 6.8  | 7.4  | 8.5  | V    |

| V <sub>ENCL</sub>  | Enable clamp voltage            | I <sub>EN</sub> =-1mA                                         | -1.0 | -0.7 | -0.3 | V    |

|                    |                                 | Fault operation                                               |      |      |      |      |

| V <sub>DIAG</sub>  | Enable output low level voltage | $(DIAG_X/EN_X pin acts as an input pin)$                      |      |      | 0.4  | V    |

|                    |                                 | I <sub>EN</sub> =1.6 mA                                       |      |      |      |      |

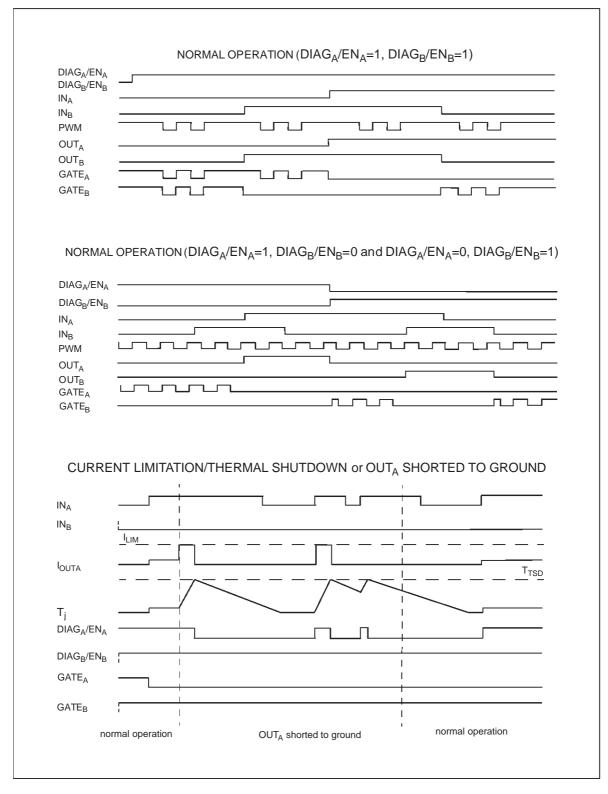

# WAVEFORMS AND TRUTH TABLE

# TRUTH TABLE IN NORMAL OPERATING CONDITIONS

In normal operating conditions the DIAG<sub>X</sub>/EN<sub>X</sub> pin is considered as an input pin by the device. This pin must be externally pulled high.

| INA | INB | DIAG <sub>A</sub> /EN <sub>A</sub> | DIAG <sub>B</sub> /EN <sub>B</sub> | OUT <sub>A</sub> | OUT <sub>B</sub> | GATE <sub>A</sub> | GATE <sub>B</sub> | Comment                  |

|-----|-----|------------------------------------|------------------------------------|------------------|------------------|-------------------|-------------------|--------------------------|

| 1   | 1   | 1                                  | 1                                  | Н                | Н                | L                 | L                 | Brake to V <sub>CC</sub> |

| 1   | 0   | 1                                  | 1                                  | Н                | OPEN             | L                 | Н                 | Clockwise                |

| 0   | 1   | 1                                  | 1                                  | OPEN             | Н                | Н                 | L                 | Counter cw               |

| 0   | 0   | 1                                  | 1                                  | OPEN             | OPEN             | Н                 | Н                 | Brake to GND             |

| Х   | Х   | 0                                  | 0                                  | OPEN             | OPEN             | L                 | L                 | Stand by                 |

| 1   | Х   | 1                                  | 0                                  | Н                | OPEN             | L                 | L                 | HS <sub>A</sub> only     |

| 0   | Х   | 1                                  | 0                                  | OPEN             | OPEN             | Н                 | L                 | MOS <sub>A</sub> only    |

| Х   | 1   | 0                                  | 1                                  | OPEN             | Н                | L                 | L                 | HS <sub>B</sub> only     |

| Х   | 0   | 0                                  | 1                                  | OPEN             | OPEN             | L                 | Н                 | MOS <sub>B</sub> only    |

PWM pin usage: In all cases, a "0" on the PWM pin will turn-off both  $GATE_A$  and  $GATE_B$  outputs. When PWM rises back to "1",  $GATE_A$  or  $GATE_B$  turn on again depending on the input pin state.

#### **TYPICAL APPLICATION CIRCUIT FOR DC TO 10KHz PWM OPERATION**

#### TYPICAL APPLICATION CIRCUIT FOR A 20KHZ PWM OPERATION

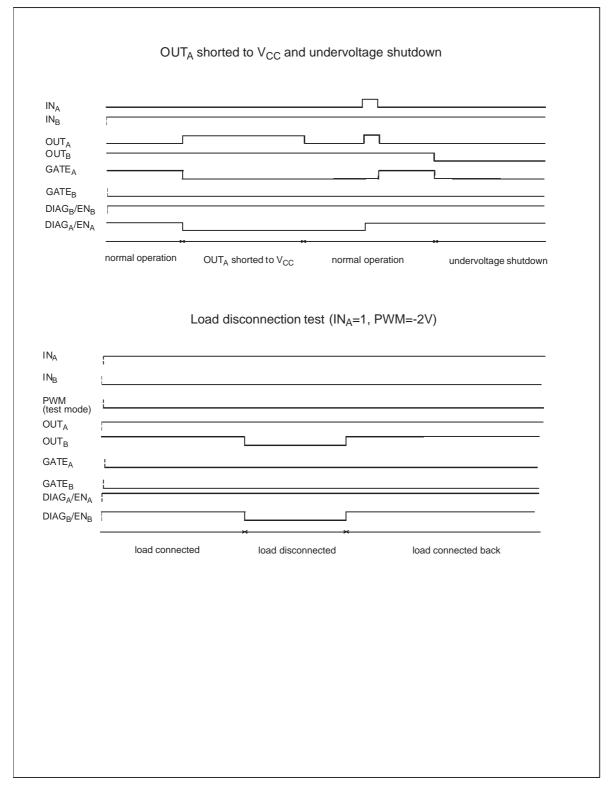

#### WAVEFORMS AND TRUTH TABLE (CONTINUED)

In case of a fault condition the  $DIAG_X/EN_X$  pin is considered as an output pin by the device. The fault conditions are:

- overtemperature on one or both high sides;

- short to battery condition on the output (saturation detection on the external connected Power MOSFET).

Possible origins of fault conditions may be:

OUT<sub>A</sub> is shorted to ground ---> overtemperature detection on high side A.

$OUT_A$  is shorted to  $V_{CC}$  ---> external Power MOSFET saturation detection (driven by GATE<sub>A</sub>).

When a fault condition is detected, the user can know which power element is in fault by monitoring the  $IN_A$ ,  $IN_B$ ,  $DIAG_A / EN_A$  and  $DIAG_B / EN_B$  pins.

In any case, when a fault is detected, the faulty half bridge is latched off. To turn-on the respective output ( $GATE_X$  or  $OUT_X$ ) again, the input signal must rise from low to high level.

| INA | IN <sub>B</sub> | DIAG <sub>A</sub> /EN <sub>A</sub> | DIAG <sub>B</sub> /EN <sub>B</sub> | OUTA | OUT <sub>B</sub> | GATE <sub>A</sub> | GATEB |

|-----|-----------------|------------------------------------|------------------------------------|------|------------------|-------------------|-------|

| 1   | 1               | 0                                  | 1                                  | OPEN | Н                | L                 | L     |

| 1   | 0               | 0                                  | 1                                  | OPEN | OPEN             | L                 | н     |

| 0   | 1               | 0                                  | 1                                  | OPEN | Н                | L                 | L     |

| 0   | 0               | 0                                  | 1                                  | OPEN | OPEN             | L                 | н     |

| Х   | Х               | 0                                  | 0                                  | OPEN | OPEN             | L                 | L     |

| 1   | Х               | 0                                  | 0                                  | OPEN | OPEN             | L                 | L     |

| 0   | Х               | 0                                  | 0                                  | OPEN | OPEN             | L                 | L     |

| Х   | 1               | 0                                  | 1                                  | OPEN | н                | L                 | L     |

| Х   | 0               | 0                                  | 1                                  | OPEN | OPEN             | L                 | Н     |

#### TRUTH TABLE IN FAULT CONDITIONS (detected on OUT<sub>A</sub>)

Fault Information

#### **TEST MODE**

The PWM pin allows to test the load connection between two half-bridges. In the test mode ( $V_{pwm}$ =-2V) the external Power Mos gate drivers are disabled. The IN<sub>A</sub> or IN<sub>B</sub> inputs allow to turn-on the High Side A or B, respectively, in order to connect one side of the load at  $V_{CC}$  voltage. The check of the voltage on the other side of the load allow to verify the continuity of the load connection. In case of load disconnection the DIAD<sub>X</sub>/EN<sub>X</sub> pin corresponding to the faulty output is pulled down.

# VND670SP

| ISO T/R<br>7637/1<br>Test Pulse | Test Level<br>I | Test Level<br>II | Test Level<br>III | Test Level<br>IV | Test Levels<br>Delays and Impedance |

|---------------------------------|-----------------|------------------|-------------------|------------------|-------------------------------------|

| 1                               | -25V            | -50V             | -75V              | -100V            | 2ms, 10Ω                            |

| 2                               | +25V            | +50V             | +75V              | +100V            | 0.2ms, 10Ω                          |

| 3a                              | -25V            | -50V             | -100V             | -150V            | 0.1μs, 50Ω                          |

| 3b                              | +25V            | +50V             | +75V              | +100V            | 0.1μs, 50Ω                          |

| 4                               | -4V             | -5V              | -6V               | -7V              | 100ms, 0.01Ω                        |

| 5                               | +26.5V          | +46.5V           | +66.5V            | +86.5V           | 400ms, 2Ω                           |

#### **ELECTRICAL TRANSIENT REQUIREMENTS**

| ISO T/R<br>7637/1<br>Test Pulse | Test Levels Result<br>I | Test Levels Result<br>II | Test Levels Result<br>III | Test Levels Result<br>IV |

|---------------------------------|-------------------------|--------------------------|---------------------------|--------------------------|

| 1                               | С                       | С                        | С                         | С                        |

| 2                               | С                       | С                        | С                         | С                        |

| 3a                              | С                       | С                        | С                         | С                        |

| 3b                              | С                       | С                        | С                         | С                        |

| 4                               | С                       | С                        | С                         | С                        |

| 5                               | С                       | E                        | E                         | E                        |

| Class                           |                         | Con                      | tents                     |                          |

| Class | Contents                                                                                                                                                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C     | All functions of the device are performed as designed after exposure to disturbance.                                                                                     |

| E     | One or more functions of the device are not performed as designed after exposure to disturbance and cannot be returned to proper operation without replacing the device. |

57

8/13

Figure 1: Test conditions for High Side switching times measurement.

### VND670SP

#### Waveforms

# Waveforms (Continued)

# VND670SP

Γ

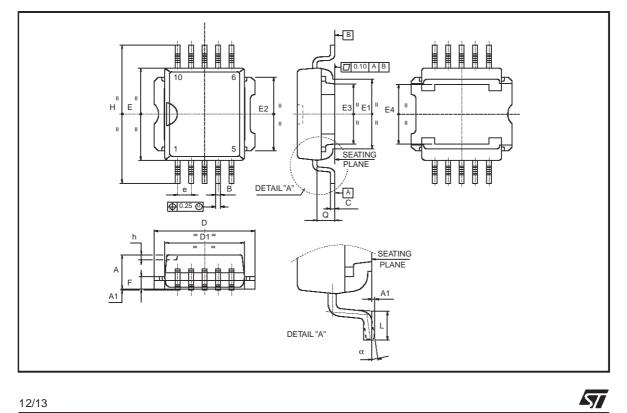

| DIM. | mm.   |      |       | inch  |       |       |

|------|-------|------|-------|-------|-------|-------|

|      | MIN.  | ТҮР  | MAX.  | MIN.  | TYP.  | MAX   |

| А    | 3.35  |      | 3.65  | 0.132 |       | 0.144 |

| A1   | 0.00  |      | 0.10  | 0.000 |       | 0.004 |

| В    | 0.40  |      | 0.60  | 0.016 |       | 0.024 |

| С    | 0.35  |      | 0.55  | 0.013 |       | 0.022 |

| D    | 9.40  |      | 9.60  | 0.370 |       | 0.378 |

| D1   | 7.40  |      | 7.60  | 0.291 |       | 0.300 |

| E    | 9.30  |      | 9.50  | 0.366 |       | 0.374 |

| E1   | 7.20  |      | 7.40  | 0.283 |       | 0.291 |

| E2   | 7.20  |      | 7.60  | 0.283 |       | 300   |

| E3   | 6.10  |      | 6.35  | 0.240 |       | 0.250 |

| E4   | 5.90  |      | 6.10  | 0.232 |       | 0.240 |

| е    |       | 1.27 |       |       | 0.050 |       |

| F    | 1.25  |      | 1.35  | 0.049 |       | 0.053 |

| Н    | 13.80 |      | 14.40 | 0.543 |       | 0.567 |

| h    |       | 0.50 |       |       | 0.002 |       |

| L    | 1.20  |      | 1.80  | 0.047 |       | 0.070 |

| Q    |       | 1.70 |       |       | 0.067 |       |

12/13

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. The ST logo is a registered trademark of STMicroelectronics

© 2000 STMicroelectronics - Printed in ITALY- All Rights Reserved.

STMicroelectronics GROUP OF COMPANIES Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta -Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com