# **ST9040**

# 16K ROM HCMOS MCU WITH EEPROM, RAM AND A/D CONVERTER

- Register oriented 8/16 bit CORE with RUN, WFI and HALT modes

- Minimum instruction cycle time: 500ns (12MHz internal)

- Internal Memory :

ROM 16K bytes RAM 256 bytes EEPROM 512 bytes

224 general purpose registers available as RAM, accumulators or index registers (register file)

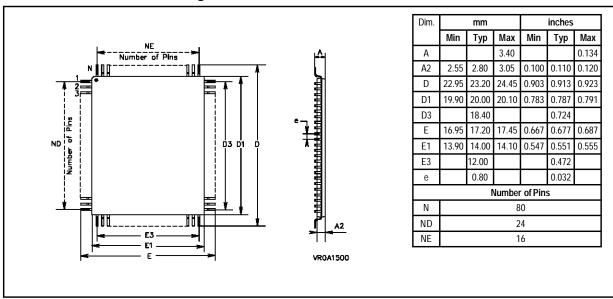

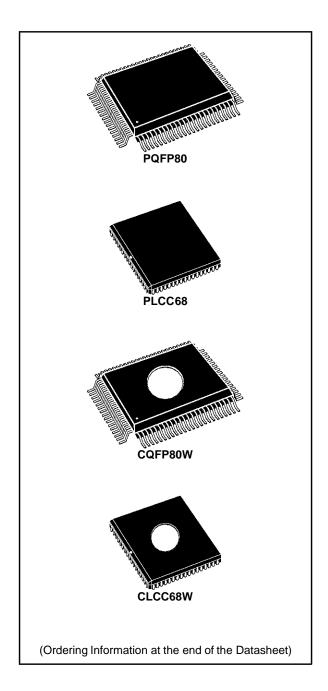

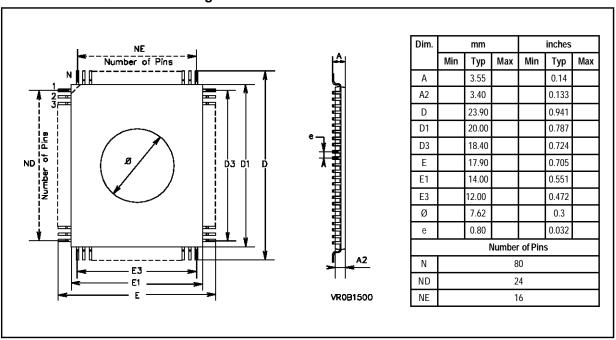

- 80-pin PQFP package for ST9040Q

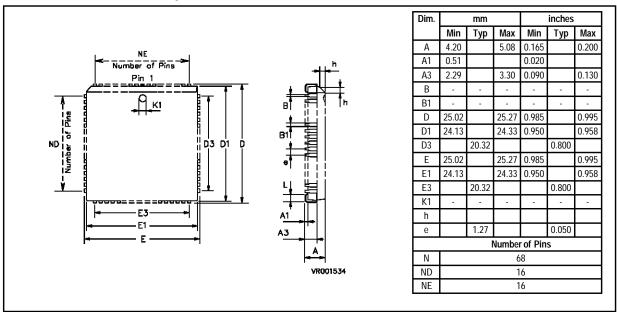

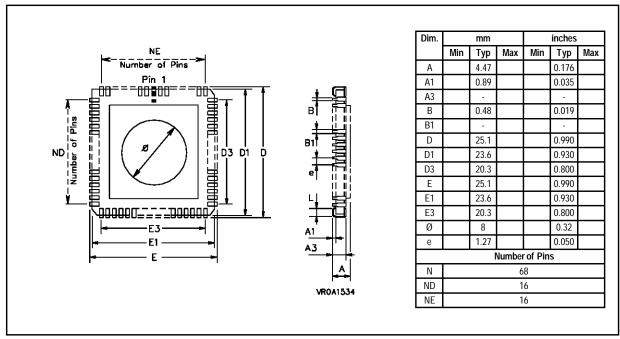

- 68-lead PLCC package for ST9040C

- DMA controller, Interrupt handler and Serial Peripheral Interface as standard features

- Up to 56 fully programmable I/O pins

- Up to 8 external plus 1 non-maskable interrupts

- 16 bit Timer with 8 bit Prescaler, able to be used as a Watchdog Timer

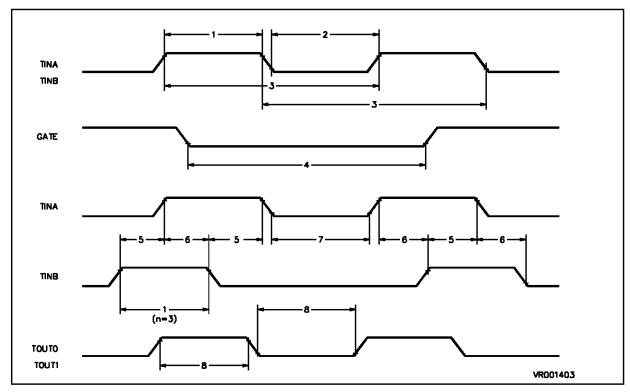

- Two 16 bit Multifunction Timers, each with an 8 bit prescaler and 13 operating modes

- 8 channel 8 bit Analog to Digital Converter, with Analog Watchdogs and external references

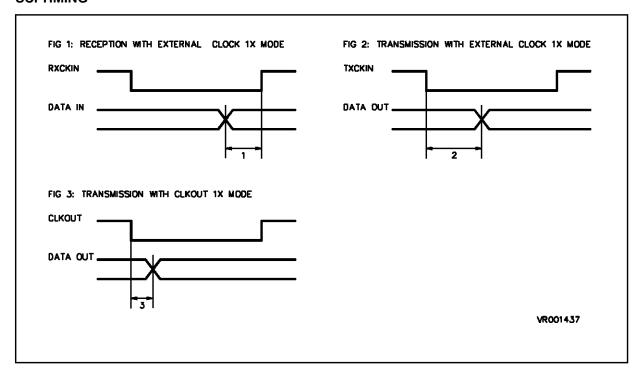

- Serial Communications Interface with asynchronous and synchronous capability

- Rich Instruction Set and 14 Addressing modes

- Division-by-Zero trap generation

- Versatile development tools, including assembler, linker, C-compiler, archiver, graphic oriented debuggerand hardware emulators

- Real Time Operating System

- Windowed and One Time Programmable EPROM parts available for prototyping and pre-production development phases

- Pin to pin compatible with ST9036

February 1997 1/56

## **TABLE OF CONTENTS**

| ST9  | 040   |                                        |

|------|-------|----------------------------------------|

|      | 1.1 ( | GENERAL DESCRIPTION                    |

|      | 1.2   | PIN DESCRIPTION                        |

|      |       | 1.2.1 I/O Port Alternate Functions     |

|      | 1.3   | MEMORY                                 |

|      |       | 1.3.1 INTRODUCTION                     |

|      |       | 1.3.2 EEPROM                           |

|      |       | 1.3.2.1 Introduction                   |

|      |       | 1.3.2.2 EEPROM Programming Procedure   |

|      |       | 1.3.2.3 Parallel Programming Procedure |

|      |       | 1.3.2.4 EEPROM Programming Voltage     |

|      |       | 1.3.2.5 EEPROM Programming Time        |

|      |       | 1.3.2.6 EEPROM Interrupt Management    |

|      |       | 1.3.2.7 EEPROM Control Register        |

|      |       | 1.3.3 REGISTER MAP                     |

| 2 EL | ECTRI | CAL CHARACTERISTICS                    |

| ST9  | 0E40  | / ST90T40 35                           |

|      | 1.1   | GENERAL DESCRIPTION                    |

|      | 1.2   | PIN DESCRIPTION                        |

|      |       | 1.2.1 I/O PORT ALTERNATE FUNCTIONS     |

|      | 1.1   | MEMORY                                 |

|      | 1.2   | EPROM PROGRAMMING                      |

|      |       | 1.2.1 Eprom Erasing                    |

| ST9  | 0R40  | 49                                     |

|      | 1.1   | GENERAL DESCRIPTION                    |

|      | 1.2   | PIN DESCRIPTION                        |

|      |       | 1.2.1 I/O PORT ALTERNATE FUNCTIONS     |

|      | 13    | MEMORY 55                              |

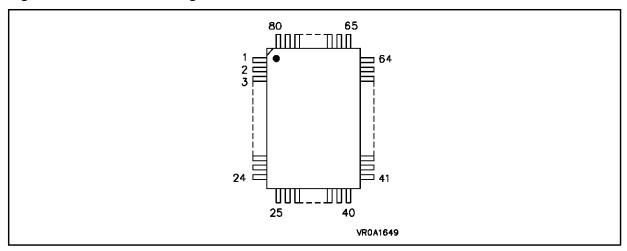

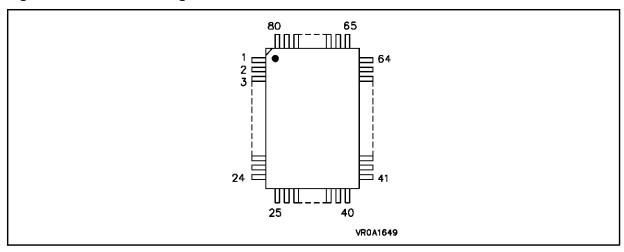

Figure 1. 80 Pin PQFP Package

Table 1. ST9040Q Pin Description

| Pin | Name             |  |

|-----|------------------|--|

| 1   | AV <sub>SS</sub> |  |

| 2   | NC               |  |

| 3   | NC               |  |

| 4   | P44/AIN4         |  |

| 5   | P57              |  |

| 6   | P56              |  |

| 7   | P55              |  |

| 8   | P54              |  |

| 9   | INT7             |  |

| 10  | INT0             |  |

| 11  | P53              |  |

| 12  | NC               |  |

| 13  | P52              |  |

| 14  | P51              |  |

| 15  | P50              |  |

| 16  | OSCOUT           |  |

| 17  | $V_{SS}$         |  |

| 18  | V <sub>SS</sub>  |  |

| 19  | NC               |  |

| 20  | OSCIN            |  |

| 21  | RESET            |  |

| 22  | P37/T1OUTB       |  |

| 23  | P36/T1INB        |  |

| 24  | P35/T1OUTA       |  |

| Pin | Name          |

|-----|---------------|

| 25  | P34/T1INA     |

| 26  | P33/T0OUTB    |

| 27  | P32/T0INB     |

| 28  | P31/T0OUTA    |

| 29  | P30/P/D/T0INA |

| 30  | A15           |

| 31  | A14           |

| 32  | NC            |

| 33  | A13           |

| 34  | A12           |

| 35  | A11           |

| 36  | A10           |

| 37  | A9            |

| 38  | A8            |

| 39  | P00/A0/D0     |

| 40  | P01/A1/D1     |

| Pin | Name                      |

|-----|---------------------------|

| 64  | P20/NMI                   |

| 63  | NC                        |

| 62  | V <sub>SS</sub>           |

| 61  | P70/SIN                   |

| 60  | P71/SOUT                  |

| 59  | P72/INT4/TXCLK<br>/CLKOUT |

| 58  | P73/INT5<br>/RXCLK/ADTRG  |

| 57  | P74/P/D/INT6              |

| 56  | P75/WAIT                  |

| 55  | P76/WDOUT<br>/BUSREQ      |

| 54  | P77/WDIN<br>/BUSACK       |

| 53  | R/W                       |

| 52  | NC                        |

| 51  | DS                        |

| 50  | ĀS                        |

| 49  | NC                        |

| 48  | $V_{DD}$                  |

| 47  | $V_{DD}$                  |

| 46  | P07/A7/D7                 |

| 45  | P06/A6/D6                 |

| 44  | P05/A5/D5                 |

| 43  | P04/A4/D4                 |

| 42  | P03/A3/D3                 |

| 41  | P02/A2/D2                 |

| Pin | Name                    |

|-----|-------------------------|

| 80  | AV <sub>DD</sub>        |

| 79  | NC                      |

| 78  | P47/AIN7                |

| 77  | P46/AIN6                |

| 76  | P45/AIN5                |

| 75  | P43/AIN3                |

| 74  | P42/AIN2                |

| 73  | P41/AIN1                |

| 72  | P40/AIN0                |

| 71  | P27/RRDY5               |

| 70  | P26/INT3<br>/RDSTB5/P/D |

| 69  | P25/WRRDY5              |

| 68  | P24/INT1<br>/WRSTB5     |

| 67  | P23/SDO                 |

| 66  | P22/INT2/SCK            |

| 65  | P21/SDI/P/D             |

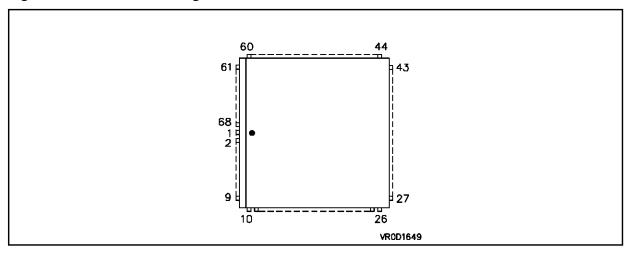

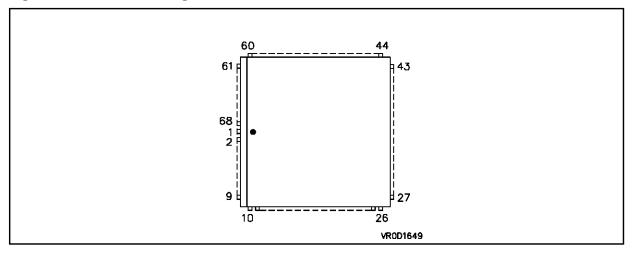

Figure 2. 68 Pin PLCC Package

Table 2. ST9040C Pin Description

| Pin | Name            | Pin | Name          |

|-----|-----------------|-----|---------------|

| 61  | P44/AIN4        | 10  | P35/T1OUTA    |

| 62  | P57             | 11  | P34/T1INA     |

| 63  | P56             | 12  | P33/T0OUTB    |

| 64  | P55             | 13  | P32/T0INB     |

| 65  | P54             | 14  | P31/T0OUTA    |

| 66  | INT7            | 15  | P30/P/D/T0INA |

| 67  | INT0            | 16  | P17/A15       |

| 68  | P53             | 17  | P16/A14       |

| • 1 | P52             | 18  | P15/A13       |

| 2   | P51             | 19  | P14/A12       |

| 3   | P50             | 20  | P13/A11       |

| 4   | OSCOUT          | 21  | P12/A10       |

| 5   | V <sub>SS</sub> | 22  | P11/A9        |

| 6   | OSCIN           | 23  | P10/A8        |

| 7   | RESET           | 24  | P00/A0/D0     |

| 8   | P37/T1OUTB      | 25  | P01/A1/D1     |

| 9   | P36/T1INB       | 26  | P02/A2/D2     |

| Pin | Name                      |

|-----|---------------------------|

| 43  | P70/SIN                   |

| 42  | P71/SOUT                  |

| 41  | P72/CLKOUT<br>/TXCLK/INT4 |

| 40  | P73/ADTRG<br>/RXCLK/INT5  |

| 39  | P74/P/D/INT6              |

| 38  | P75/WAIT                  |

| 37  | P76/WDOUT<br>/BUSREQ      |

| 36  | P77/WDIN<br>/BUSACK       |

| 35  | R/W                       |

| 34  | DS                        |

| 33  | ĀS                        |

| 32  | $V_{DD}$                  |

| 31  | P07/A7/D7                 |

| 30  | P06/A6/D6                 |

| 29  | P05/A5/D5                 |

| 28  | P04/A4/D4                 |

| 27  | P03/A3/D3                 |

| Pin | Name                    |

|-----|-------------------------|

| 60  | AV <sub>SS</sub>        |

| 59  | $AV_{DD}$               |

| 58  | P47/AIN7                |

| 57  | P46/AIN6                |

| 56  | P45/AIN5                |

| 55  | P43/AIN3                |

| 54  | P42/AIN2                |

| 53  | P41/AIN1                |

| 52  | P40/AIN0                |

| 51  | P27/RRDY5               |

| 50  | P26/INT3<br>/RDSTB5/P/D |

| 49  | P25/WRRDY5              |

| 48  | P24/INT1<br>/WRSTB5     |

| 47  | P23/SDO                 |

| 46  | P22/INT2/SCK            |

| 45  | P21/SDI/P/D             |

| 44  | P20/NMI                 |

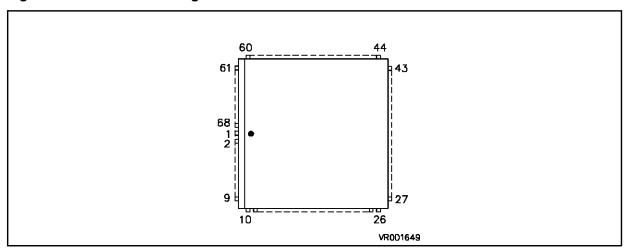

#### 1.1GENERAL DESCRIPTION

The ST9040 is a ROM member of the ST9 family of microcontrollers, completely developed and produced by SGS-THOMSON Microelectronics using a proprietary n-well HCMOS process.

The ST9040 peripheral and functional actions are fully compatible throughout the ST903x/4x family. This datasheet will thus provide only information specific to this ROM device.

## THE READER IS ASKED TO REFER TO THE DATASHEET OF THE ST9036 ROM-BASED DE-VICE FOR FURTHER DETAILS.

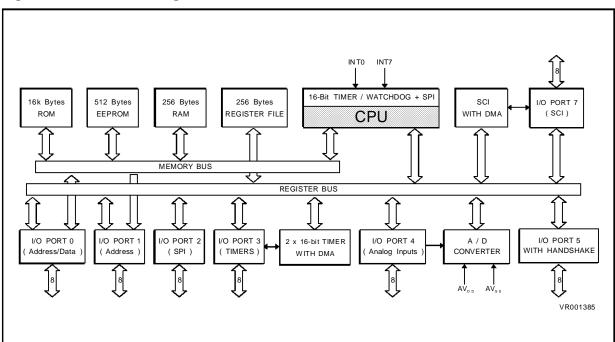

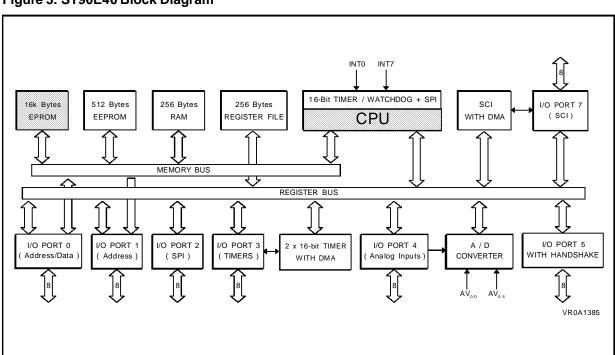

The nucleus of the ST9040 is the advanced Core which includes the Central Processing Unit (CPU), the Register File, a 16 bit Timer/Watchdog with 8 bit Prescaler, a Serial Peripheral Interface supporting S-bus, I<sup>2</sup>C-bus and IM-bus Interface, plus two 8 bit I/O ports. The Core has independent memory and register buses allowing a high degree of pipelining to add to the efficiency of the code execution speed of the extensive instruction set. The powerful I/O capabilities demanded by microcontroller applications are fulfilled by the ST9040 with up to 56 I/O lines dedicated to digital Input/Output. These lines are grouped into up to seven 8 bit I/O Ports and can be configured on a bit basis under

software control to provide timing, status signals, an address/data bus for interfacing external memory, timer inputs and outputs, analog inputs, external interrupts and serial or parallel I/O with or without handshake.

Three basic memory spaces are available to support this wide range of configurations: Program Memory (internal and external), Data Memory (internal and external) and the Register File, which includes the control and status registers of the on-chip peripherals.

Two 16 bit MultiFunction Timers, each with an 8 bit Prescaler and 13 operating modes allow simple use for complex waveform generation and measurement, PWM functions and many other system timing functions by the usage of the two associated DMA channels for each timer. In addition there is an 8 channel Analog to Digital Converter with integral sample and hold, fast 11µs conversion time and 8 bit resolution. An Analog Watchdog feature is included for two input channels.

Completing the device is a full duplex Serial Communications Interface with an integral 110 to 375,000 baud rate generator, asynchronous and 1.5Mbyte/s synchronous capability (fully programmable format) and associated address/wake-up option, plus two DMA channels.

#### 1.2 PIN DESCRIPTION

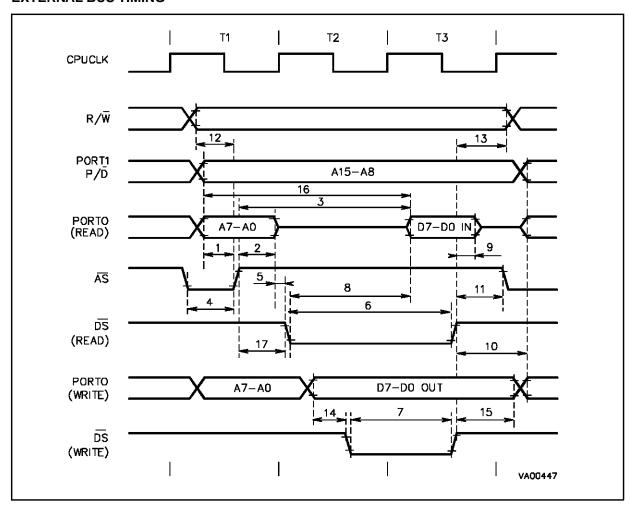

AS. Address Strobe (output, active low, 3-state). Address Strobe is pulsed low once at the beginning of each memory cycle. The rising edge of AS indicates that address, Read/Write (R/W), and Data Memory signals are valid for program or data memory transfers. Under program control, AS can be placed in a high-impedance state along with Port 0 and Port 1, Data Strobe (DS) and R/W

DS. Data Strobe (output, active low, 3-state). Data Strobe provides the timing for data movement to or from Port 0 for each memory transfer. During a write cycle, data out is valid at the leading edge of **DS**. During a read cycle, Data In must be valid prior to the trailing edge of DS. When the ST9040 accesses on-chip memory, DS is held high during the whole memory cycle. It can be placed in a high impedancestate along with Port 0, Port 1,  $\overline{AS}$  and  $R/\overline{W}$ .

**R/W.** Read/Write (output, 3-state). Read/Write determines the direction of data transfer for external memory transactions. RW is low when writing to external program or data memory, and high for all other transactions. It can be placed in a high impedance state along with Port 0, Port 1,  $\overline{AS}$  and  $\overline{DS}$ .

RESET. Reset (input, active low). The ST9 is initialised by the Reset signal. With the deactivation of RE-SET, program execution begins from the Program memory location pointed to by the vector contained in program memory locations 00h and 01h.

INTO, INT7. External interrupts (input, active on rising or falling edge). External interrupt inputs 0 and 7 respectively. INTO channel may also be used for the timer watchdog interrupt.

OSCIN, OSCOUT. Oscillator (input and output). These pins connect a parallel-resonant crystal (24MHz maximum), or an external source to the on-chip clock oscillator and buffer. OSCIN is the input of the oscillator inverter and internal clock generator; OSCOUT is the output of the oscillator inverter.

$AV_{DD}$ . Analog  $V_{DD}$  of the Analog to Digital Converter.

AVss. Analog Vss of the Analog to Digital Converter. Must be tied to Vss.

**V**<sub>DD</sub>. Main Power Supply Voltage (5V ± 10%)

Vss. Digital Circuit Ground.

P0.0-P0.7, P1.0-P1.7, P2.0-P2.7 P3.0-P3.7, P4.0-P4.7, P5.0-P5.7, P7.0-P7.7 I/O Port Lines (Input/Output, TTL or CMOS compatible). 56 lines grouped into I/O ports of 8 bits, bit programmable under program control as general purpose I/O or as alternate functions.

### 1.2.1 I/O Port Alternate Functions

Each pin of the I/O ports of the ST9040 may assume software programmable Alternative Functions as shown in the Pin Configuration Drawings. Table 1-3 shows the Functions allocated to each I/O Port pins and a summary of packages for which they are available.

Figure 3. ST9040 Block Diagram

### PIN DESCRIPTION (Continued)

Table 3. ST9040 I/O Port Alternate Function Summary

| I/O PORT  | Name Function Alternate Function Pin |     | Pin Ass                      | Assignment |      |  |

|-----------|--------------------------------------|-----|------------------------------|------------|------|--|

| Port. bit |                                      |     |                              | PLCC       | PQFP |  |

| P0.0      | A0/D0                                | I/O | Address/Data bit 0 mux       | 24         | 39   |  |

| P0.1      | A1/D1                                | I/O | Address/Data bit 1 mux       | 25         | 40   |  |

| P0.2      | A2/D2                                | I/O | Address/Data bit 2 mux       | 26         | 41   |  |

| P0.3      | A3/D3                                | I/O | Address/Data bit 3 mux       | 27         | 42   |  |

| P0.4      | A4/D4                                | I/O | Address/Data bit 4 mux       | 28         | 43   |  |

| P0.5      | A5/D5                                | I/O | Address/Data bit 5 mux       | 29         | 44   |  |

| P0.6      | A6/D6                                | I/O | Address/Data bit 6 mux       | 30         | 45   |  |

| P0.7      | A7/D7                                | I/O | Address/Data bit 7 mux       | 31         | 46   |  |

| P1.0      | A8                                   | 0   | Address bit 8                | 23         | 38   |  |

| P1.1      | A9                                   | 0   | Address bit 9                | 22         | 37   |  |

| P1.2      | A10                                  | 0   | Address bit 10               | 21         | 36   |  |

| P1.3      | A11                                  | 0   | Address bit 11               | 20         | 35   |  |

| P1.4      | A12                                  | 0   | Address bit 12               | 19         | 34   |  |

| P1.5      | A13                                  | 0   | Address bit 13               | 18         | 33   |  |

| P1.6      | A14                                  | 0   | Address bit 14               | 17         | 31   |  |

| P1.7      | A15                                  | 0   | Address bit 15               | 16         | 30   |  |

| P2.0      | NMI                                  | ı   | Non-Maskable Interrupt       | 44         | 64   |  |

| P2.0      | ROMless                              | ı   | ROMless Select (Mask option) | 44         | 64   |  |

| P2.1      | P/D                                  | 0   | Program/Data Space Select    | 45         | 65   |  |

| P2.1      | SDI                                  | I   | SPI Serial Data Out          | 45         | 65   |  |

| P2.2      | INT2                                 | ı   | External Interrupt 2         | 46         | 66   |  |

| P2.2      | SCK                                  | 0   | SPI Serial Clock             | 46         | 66   |  |

| P2.3      | SDO                                  | 0   | SPI Serial Data In           | 47         | 67   |  |

| P2.4      | INT1                                 | 1   | External Interrupt 1         | 48         | 68   |  |

| P2.4      | WRSTB5                               | 1   | Handshake Write Strobe P5    | 48         | 68   |  |

| P2.5      | WRRDY5                               | 0   | Handshake Write Ready P5     | 49         | 69   |  |

| P2.6      | INT3                                 | 1   | External Interrupt 3         | 50         | 70   |  |

| P2.6      | RDSTB5                               | I   | Handshake Read Strobe P5     | 50         | 70   |  |

| P2.6      | P/D                                  | 0   | Program/Data Space Select    | 50         | 70   |  |

| P2.7      | RDRDY5                               | 0   | Handshake Read Ready P5 51   |            | 71   |  |

| P3.0      | TOINA                                | I   | MF Timer 0 Input A           | 15         | 29   |  |

| P3.0      | P/D                                  | 0   | Program/Data Space Select 15 |            | 29   |  |

| P3.1      | T0OUTA                               | 0   | MF Timer 0 Output A 14       |            | 28   |  |

| P3.2      | T0INB                                | I   | MF Timer 0 Input B           | 13         | 27   |  |

| P3.3      | T0OUTB                               | 0   | MF Timer 0 Output B          | 12         | 26   |  |

| P3.4      | T1INA                                | ı   | MF Timer 1 Input A           | 11         | 25   |  |

### PIN DESCRIPTION (Continued)

Table 4. ST9040 I/O Port Alternate Function Summary(Continued)

| I/O PORT  | Name    | Function | Inction Alternate Function   | Pin Ass | Pin Assignment |  |  |

|-----------|---------|----------|------------------------------|---------|----------------|--|--|

| Port. bit |         |          |                              | PLCC    | PQFP           |  |  |

| P3.5      | T1OUTA  | 0        | MF Timer 1 Output A          | 10      | 24             |  |  |

| P3.6      | T1INB   | I        | MF Timer 1 Input B           | 9       | 23             |  |  |

| P3.7      | T1OUTB  | 0        | MF Timer 1 Output B          | 8       | 22             |  |  |

| P4.0      | AIN0    | 1        | A/D Analog Input 0           | 52      | 72             |  |  |

| P4.1      | AIN1    | I        | A/D Analog Input 1           | 53      | 73             |  |  |

| P4.2      | AIN2    | I        | A/D Analog Input 2           | 54      | 74             |  |  |

| P4.3      | AIN3    | 1        | A/D Analog Input 3           | 55      | 75             |  |  |

| P4.4      | AIN4    | 1        | A/D Analog Input 4           | 61      | 4              |  |  |

| P4.5      | AIN5    | I        | A/D Analog Input 5           | 56      | 76             |  |  |

| P4.6      | AIN6    | I        | A/D Analog Input 6           | 57      | 77             |  |  |

| P4.7      | AIN7    | I        | A/D Analog Input 7           | 58      | 78             |  |  |

| P5.0      |         | I/O      | I/O Handshake Port 5         | 3       | 15             |  |  |

| P5.1      |         | I/O      | I/O Handshake Port 5         | 2       | 14             |  |  |

| P5.2      |         | I/O      | I/O Handshake Port 5         | 1       | 13             |  |  |

| P5.3      |         | I/O      | I/O Handshake Port 5         | 68      | 11             |  |  |

| P5.4      |         | I/O      | I/O Handshake Port 5         | 65      | 8              |  |  |

| P5.5      |         | I/O      | I/O Handshake Port 5         | 64      | 7              |  |  |

| P5.6      |         | I/O      | I/O Handshake Port 5         | 63      | 6              |  |  |

| P5.7      |         | I/O      | I/O Handshake Port 5         | 62      | 5              |  |  |

| P7.0      | SIN     | I        | SCI Serial Input             | 43      | 61             |  |  |

| P7.1      | SOUT    | 0        | SCI Serial Output            | 42      | 60             |  |  |

| P7.1      | ROMIess | I        | ROMless Select (Mask option) | 42      | 60             |  |  |

| P7.2      | INT4    | I        | External Interrupt 4         | 41      | 59             |  |  |

| P7.2      | TXCLK   | I        | SCI Transmit Clock Input     | 41      | 59             |  |  |

| P7.2      | CLKOUT  | 0        | SCI Byte Sync Clock Output   | 41      | 59             |  |  |

| P7.3      | INT5    | ı        | External Interrupt 5         | 40      | 58             |  |  |

| P7.3      | RXCLK   | I        | SCI Receive Clock Input      | 40      | 58             |  |  |

| P7.3      | ADTRG   | I        | A/D Conversion Trigger       | 40      | 58             |  |  |

| P7.4      | INT6    | I        | External Interrupt 6         | 39      | 57             |  |  |

| P7.4      | P/D     | 0        | Program/Data Space Select    | 39      | 57             |  |  |

| P7.5      | WAIT    | 1        | External Wait Input          | 38      | 56             |  |  |

| P7.6      | WDOUT   | 0        | T/WD Output 37               |         | 55             |  |  |

| P7.6      | BUSREQ  | 1        | External Bus Request         | 37      | 55             |  |  |

| P7.7      | WDIN    | 1        | T/WD Input                   | 36      | 54             |  |  |

| P7.7      | BUSACK  | 0        | External Bus Acknowledge     | 36      | 54             |  |  |

### **ADDRESS SPACES**

Table 1-4. Group F Peripheral Organization

| Applica | able for   | ST9040   |          |          |          |          |          |          |          |     |

|---------|------------|----------|----------|----------|----------|----------|----------|----------|----------|-----|

| DEC     | DEC<br>HEX | 00<br>00 | 02<br>02 | 03<br>03 | 08<br>08 | 09<br>09 | 10<br>0A | 24<br>18 | 63<br>3F |     |

| R255    | RFF        | RESERVED | RESERVED |          |          |          |          | RESERVED |          | RFF |

| R254    | RFE        | MSPI     |          | PORT 7   |          |          |          |          |          | RFE |

| R253    | RFD        | Wierr    | PORT 3   |          |          | RESERVED |          |          |          | RFD |

| R252    | RFC        | WCR      |          |          |          |          |          |          |          | RFC |

| R251    | RFB        |          | RESERVED |          |          |          |          |          |          | RFB |

| R250    | RFA        | T/WD     |          | RESERVED |          |          |          |          |          | RFA |

| R249    | RF9        |          | PORT 2   |          | MFT 1    |          | MFT 0    |          | A/D      | RF9 |

| R248    | RF8        |          |          |          |          | MFT      |          |          |          | RF8 |

| R247    | RF7        |          | RESERVED |          |          |          |          | SCI      |          | RF7 |

| R246    | RF6        |          |          | PORT 5   |          | MFT 1    |          |          |          | RF6 |

| R245    | RF5        | EXT INT  | PORT1    |          |          |          |          |          |          | RF5 |

| R244    | RF4        |          |          |          |          |          |          |          |          | RF4 |

| R243    | RF3        |          | RESERVED | RESERVED |          |          |          |          |          | RF3 |

| R242    | RF2        |          |          |          |          | MFT0     |          |          |          | RF2 |

| R241    | RF1        | EEPROMCR | PORT 0   | PORT 4   |          |          |          |          |          | RF1 |

| R240    | RF0        | RESERVED |          |          |          |          |          |          |          | RF0 |

|         |            |          |          |          |          |          |          |          |          |     |

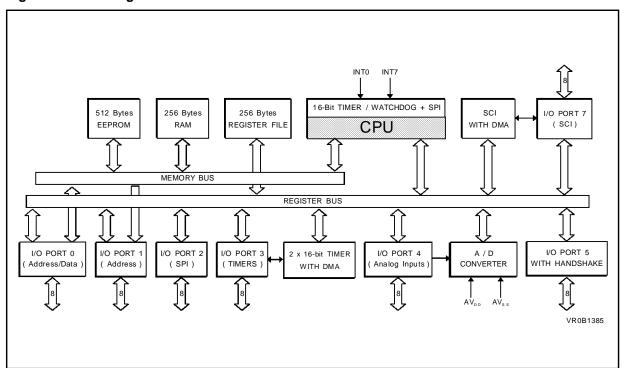

#### 1.3 MEMORY

#### 1.3.1 INTRODUCTION

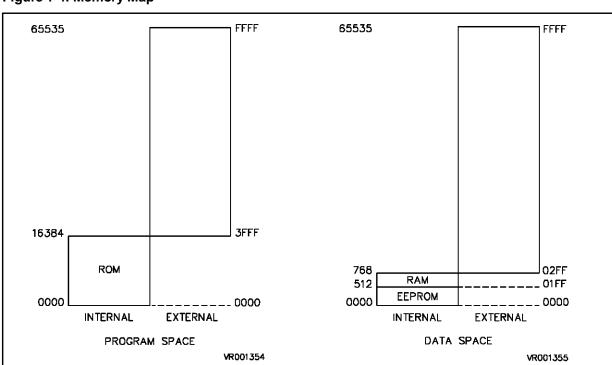

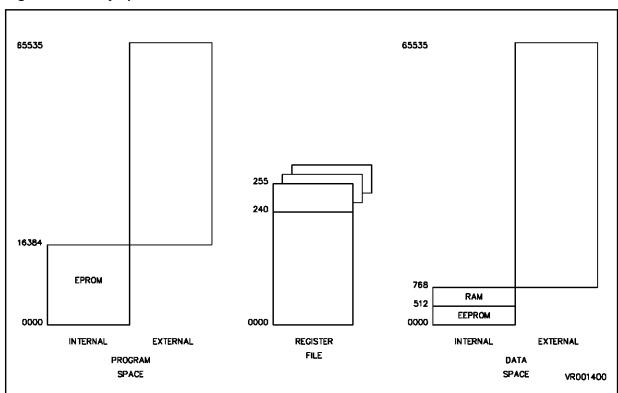

The memory of the ST9 is divided into two spaces:

- Data memory with up to 64K (65536) bytes

- Program memory with up to 64K (65536) bytes

Thus, there is a total of 128K bytes of addressable memory space.

The 16K bytes of on-chip ROM memory of the ST9040 are selected at memory addresses 0 through 3FFFh (hexadecimal) in the PROGRAM space.

The DATA space includes the 512 bytes of on-chip EEPROM at addresses 0 through 1FFh and the 256 bytes of on-chip RAM memory at addresses 200h through 2FFh.

#### **1.3.2 EEPROM**

#### 1.3.2.1 Introduction

The EEPROMmemory provides user-programmable non-volatile memory on-chip, allowing fast and reliable storage of user data. As there is also no off-chip access required, as for an external serial EEPROM, high security levels can be achieved.

The EEPROM memory is read as normal RAM memory at Data Space addresses 0 to 1FFh, however one WAIT cycle is automatically added for a Read cycle, while a byte write cycle to the

EEPROM will cause the start of an ERASE/WRITE cycle at the addressed location. Word (16 bit) writes are not allowed.

The programming cycle is self-timed, with a typical programming time of 6ms. The voltage necessary for programming the EEPROM is internally generated with a +18V charge pump circuit.

Up to 16 bytes of data may be programmed into the EEPROM during the same write cycle by using the PARALLEL WRITE function.

A standby mode is also available which disables all power consumption sources within the EEPROM for low power requirements. When STBY is high, any attempt to access the EEPROM memory will produce unpredictable results. After the re-enabling of the EEPROM, a delay of 6 INTCLK cycles must be allowed before the selection of the EEPROM.

The EEPROM of the ST9040 has been implemented in a high reliability technology developed by SGS-THOMSON, this, together with the double bit structure, allow 300k Erase/Write cycles and 10 year data retention to be achieved on a microcontroller.

Control of the EEPROM is performed through one register mapped at register address R241 in Page 0.

Figure 1-4. Memory Map

### **EEPROM** (Continued)

### 1.3.2.2 EEPROM Programming Procedure

The programming of a byte of EEPROMmemory is equivalent to writing a byte into a RAM location after verifying that EEBUSY bit is low. Instructions operating on word data (16 bits) will not access the EEPROM.

The EEPROM ENABLE bit EEWEN must first be set before writing to the EEPROM. When this bit is low, attempts to write data to the EEPROM have no affect, this prevents any spurious memory accesses from affecting the data in the EEPROM.

Termination of the write operation can be detected by polling on the EEBUSY status bit, or by interrupt, taking the interrupt vector from the External Interrupt4 channel. The selection of the interrupt is made by EEPROM Interrupt enable bit EEIEN. It should be noted that the Mask bit of External Interrupt 4 should be set, and the Interrupt Pending bit reset, before the setting of EEIEN to prevent unwanted interrupts. A delay (eg a nop instruction) should also be included between the operations on the mask and pending bits of External Interrupt 4.

If polling on EEBUSY is used, a delay of 6 INTCLK clock cycles is necessary after the end of programming, this can be a nop instruction or, normally, therequired time to test the EEBUSY bit and to branch to the next instruction will be sufficient. While EEBUSY is active, any attempt to access the EEPROM matrix will be aborted and the data read will be invalid. EEBUSY is a read only bit and cannot be reset by the user if active.

An erased bit of the EEPROM memory will read as a logic "0", while a programmed cell will be read as a logic "1". For applications requiring the highest level of reliability, the Verify Mode, set by EEPROM control register bit VRFY, allows the reading of the EEPROM memory cells with a reduced gate voltage (typically 20%). If the EEPROM memory cell has been correctly programmed, a logic "1" will be read with the reduced voltage, otherwise a logic "0" will be read.

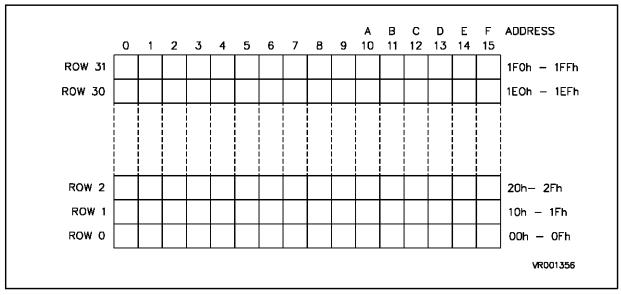

### 1.3.2.3 Parallel Programming Procedure

Parallel programming is a feature of the EEPROM macrocell. One up to sixteen bytes of a same row can be programmed at once.

The constraint is that each of the bytes occur in the same ROW of the EEPROM memory (A4 constant, A3-A0 variable). To operate this mode, the Parallel Mode enable bit, PLLEN, must be set. The data written is then latched into buffers (at the addresses specified, which may be non-sequential) and then transferred to the EEPROM memory by the setting of the PLLST bit of the control register. Both PLLST and PLLEN are internally reset at the end of the programming cycle. Any attempt to read the EEPROM memory when PLLEN is set will give invalid data. In the event that the data in the buffer latches is not required to be written into the memory by the setting of PLLST, the correct way to terminate the operation is to reset PLLEN and to perform a dummy read of the EEPROMmemory. This termination will clear all data present in the latches.

### 1.3.2.4 EEPROM Programming Voltage

No external Vpp voltage is required, an internal 18Volt charge-pump gives the required energy by a dedicated oscillator pumping at a typical frequency of 5MHz, regardless of the external clock.

### 1.3.2.5 EEPROM Programming Time

No timing routine is required to control the programming time as dedicated circuitry takes care of the EEPROM programming time (The typical programming time is 6ms).

#### 1.3.2.6 EEPROM Interrupt Management

At the end of each write procedure the EEPROM sends an interrupt request (if EEIEN bit is set). The EEPROM shares its interrupt channel with the external interrupt source INT4, from which the priority level is derived.

Care must be taken when EEIEN is reset. The associated external interrupt channel must be disabled (by reseting bit 4 of EIMR, R244) along with reseting the interrupt pending bit (bit 4 of EIPR, R243) to prevent unwanted interrupts. A delay instruction (at least 1 nop instruction) must be inserted between these two operations

**WARNING.** The content of the EEPROM of the ST9040 family after the out-going test at SGS-THOMSON's manufacturing location is not guarenteed.

#### **EEPROM** (Continued)

# **1.3.2.7 EEPROM Control Register EECR R241** (F1h) Page 0 Read/Write

(except EEBUSY: read only) EEPROM Control Register Reset value: 0000 0000b (00h)

7 0

O VERIFY EESTBY EEIEN PLLST PLLEN EEBUSYEEWEN

bit 7 = **B7**: This bit is forced to "0" after reset and **MUST** not be modified by the user.

bit 6 = **VERIFY**: *Set Verify mode*. Verify (active high) is used to activate the verify mode.

The verify mode provides a guarentee of good retention of the programmed bit. When active, the reading voltage on the cell gate is decreased from 1.2V to 0.0V, decreasing the current from the programmed cell by 20%. If the cell is well programmed (to "1"), a "1" will still be read, otherwise a "0" will be read.

**Note.** The verify mode must not be used during an erasing or a programming cycle).

bit 5 = **EESTBY**: *EEPROM Stand-By*. EESTBY = "1" switches off all power consumption sources inside the EEPROM. Any attempt to access the EEPROM when EESTBY = "1" will produce unpredictable results.

**Note.** After EESTBY is reset, the user must wait 6 CPUCLK cycles (e.g. 1 nop instruction) before selecting the EEPROM.

bit 4 = **EEIEN:** EEPROM Interrupt Enable. INTEN = "1" disables the external interrupt source INT4, and enables the EEPROM to send its interrupt request to the central interrupt unit at the end of each write procedure.

bit 3 = **PLLST**: Parallel Write Start. Setting PLLST to "1" starts the parallel writing procedure. It can be set only if PLLEN is already set. PLLST is internally reset at the end of the programming sequence.

bit 2 = **PLLEN:** Parallel write Enable. Setting PLLEN to "1" enables the parallel writing mode which allows the user to write up to 16 bytes at the same time. PLLEN is internally reset at the end of the programming sequence.

bit 1 = **EEBUSY**: *BUSY*. When this read only bit is high, an EEPROM write operation is in progress and any attempt to access the EEPROM is aborted.

bit 0 = **EEWEN**: *EEPROM Write Enable*. Setting this bit allows programming of the EEPROM, when low a writing attempt has no effect.

#### 1.3.3 REGISTER MAP

Please refer to the Register Map of the ST9036 for all general registers with the exception of the register shown in the following table.

Table 1-5. Register Map Addendum

EECR R241 (F1h) Page 0 Read/Write Control Registers

Figure 1-5. EEPROM Parallel Programming Rows

### **2 ELECTRICAL CHARACTERISTICS**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                              | Parameter                                               | Value                                   | Unit |

|-------------------------------------|---------------------------------------------------------|-----------------------------------------|------|

| V <sub>DD</sub>                     | Supply Voltage                                          | - 0.3 to 7.0                            | V    |

| AV <sub>DD</sub> , AV <sub>SS</sub> | Analog Supply Voltage                                   | $V_{SS} = AV_{SS} < AV_{DD} \le V_{DD}$ | V    |

| VI                                  | Input Voltage                                           | - 0.3 to V <sub>DD</sub> +0.3           | V    |

| Vo                                  | Output Voltage                                          | - 0.3 to V <sub>DD</sub> +0.3           | V    |

| T <sub>STG</sub>                    | Storage Temperature                                     | - 55 to + 150                           | °C   |

| I <sub>INJ</sub>                    | Pin Injection Current Digital Input                     | -5 to +5                                | mA   |

| I <sub>INJ</sub>                    | Pin Injection Current Analog Input                      | -5 to +5                                | mA   |

|                                     | Maximum Accumulated Pin injection Current in the device | -50 to +50                              | mA   |

Note: Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. All voltages are referenced to VSS

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol            | Parameter                         | Va          | Unit |     |  |

|-------------------|-----------------------------------|-------------|------|-----|--|

| Syllibol          | r di diffetet                     | Min.        | Max. |     |  |

| T <sub>A</sub>    | Operating Temperature             | <b>- 40</b> | 85   | °C  |  |

| $V_{DD}$          | Operating Supply Voltage          | 4.5         | 5.5  | V   |  |

| f <sub>OSCE</sub> | External Oscillator Frequency     |             | 24   | MHz |  |

| f <sub>OSCI</sub> | Internal Clock Frequency (INTCLK) |             | 12   | MHz |  |

### DC ELECTRICAL CHARACTERISTICS

$V_{DD} = 5V \pm 10\%$  T<sub>A</sub> = -40 °C to +85°C, unless otherwise specified)

| Comple al         | Danamatan.                                     | Took Complisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       | Value |                       | 11   |

|-------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----------------------|------|

| Symbol            | Parameter                                      | l est Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min.                  | Тур.  | Max.                  | Unit |

| V <sub>IHCK</sub> | Clock Input High Level                         | External Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.7 V <sub>DD</sub>   |       | V <sub>DD</sub> + 0.3 | V    |

| V <sub>ILCK</sub> | Clock Input Low Level                          | External Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 0.3                 |       | 0.3 V <sub>DD</sub>   | V    |

| M                 | Input High Lovel                               | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.0                   |       | V <sub>DD</sub> + 0.3 | V    |

| $V_{IH}$          | Input High Level                               | Test Conditions         Min.         Typ.         Max.           External Clock         0.7 V <sub>DD</sub> V <sub>DD</sub> + 0.3         V           External Clock         -0.3         0.3 V <sub>DD</sub> V           TTL         2.0         V <sub>DD</sub> + 0.3         V           CMOS         0.7 V <sub>DD</sub> V <sub>DD</sub> + 0.3         V           CMOS         -0.3         0.3 V <sub>DD</sub> V           Push Pull, lload = -0.8mA         V <sub>DD</sub> -0.8         V         V           Push Pull or Open Drain, lload = 1.6mA         0.4         V         V           Bidirectional Weak Pull-up, V <sub>OL</sub> = 0V         -50         -200         -420         µ           V <sub>IN</sub> < 0.8V, under Reset         -80         -200         -420         µ           Input/Tri-State, 0V < V <sub>IN</sub> < V <sub>DD</sub> -30 | CMOS                  |       | V                     |      |

| M                 | Innut I avel avel                              | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 0.3                 |       | 0.8                   | V    |

| $V_{IL}$          | Input Low Level                                | Test Conditions           Min.         Typ.         Max.           External Clock         0.7 V <sub>DD</sub> V <sub>DD</sub> + 0           External Clock         −0.3         0.3 V <sub>DD</sub> + 0           TTL         2.0         V <sub>DD</sub> + 0           CMOS         0.7 V <sub>DD</sub> V <sub>DD</sub> + 0           TTL         −0.3         0.8           CMOS         −0.3         0.3 V <sub>DI</sub> CMOS         −0.3         0.3 V <sub>DI</sub> 0.7 V <sub>DD</sub> V <sub>DD</sub> + 0           0.7 V <sub>DD</sub> V <sub>DD</sub> + 0           0.3 V <sub>DI</sub> 0.4 V <sub>DD</sub> 0.4           Dush Pull, Iload = −0.8mA         V <sub>DD</sub> −0.8           Push Pull or Open Drain, Iload = 1.6mA         0.4           Bidirectional Weak Pull-up, V <sub>OL</sub> = 0V         −50         −200         −420           V <sub>IN</sub> < 0.8V, under Reset                                                                                                                                              | 0.3 V <sub>DD</sub>   | V     |                       |      |

| V <sub>IHRS</sub> | RESET Input High Level                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.7 V <sub>DD</sub>   |       | V <sub>DD</sub> + 0.3 | V    |

| V <sub>ILRS</sub> | RESET Input Low Level                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -0.3                  |       | 0.3 V <sub>DD</sub>   | V    |

| V <sub>HYRS</sub> | RESET Input Hysteresis                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.3                   |       | 1.5                   | V    |

| V <sub>OH</sub>   | Output High Level                              | Push Pull, Iload = - 0.8mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DD</sub> – 0.8 |       |                       | V    |

| V <sub>OL</sub>   | Output Low Level                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |       | 0.4                   | V    |

| I <sub>WPU</sub>  | Weak Pull-up Current                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 50                  | - 200 | - 420                 | μА   |

| I <sub>APU</sub>  | Active Pull-up Current, for INT0 and INT7 only | V <sub>IN</sub> < 0.8V, under Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 80                  | - 200 | - 420                 | μА   |

| I <sub>LKIO</sub> | I/O Pin Input Leakage                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 10                  |       | + 10                  | μА   |

| ILKRS             | Reset Pin Input Leakage                        | OV < VIN < VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 30                  |       | + 30                  | μΑ   |

| I <sub>LKAD</sub> | A/D Pin Input Leakage                          | Open Drain,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -3                    |       | + 3                   | μΑ   |

| I <sub>LKAP</sub> | Active Pull-up Input<br>Leakage                | 0V < V <sub>IN</sub> < 0.8V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - 10                  |       | + 10                  | μА   |

| I <sub>LKOS</sub> | OSCIN Pin Input Leakage                        | $0V < V_{IN} < V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 10                  |       | + 10                  | μА   |

Note: All I/O Ports are configured in Bidirectional Weak Pull-up Mode with no DC load, External Clock pin (OSCIN) is driven by square wave external clock. No peripheral working.

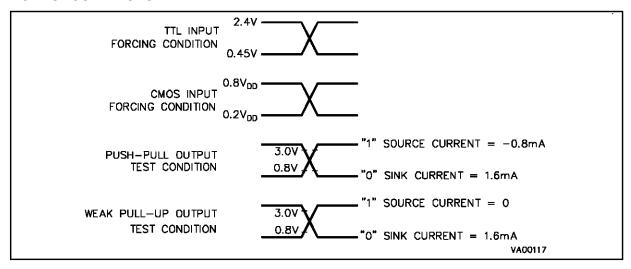

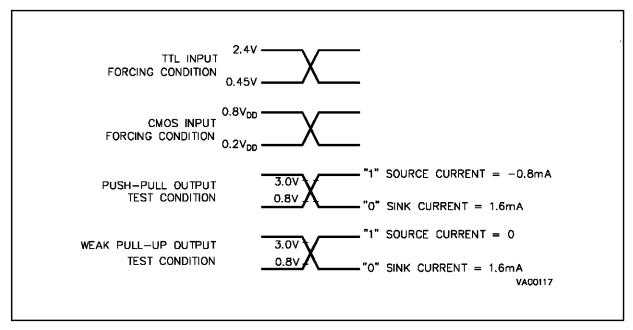

### **DC TEST CONDITIONS**

AC ELECTRICAL CHARACTERISTICS (VDD =  $5V \pm 10\%$  TA = -40 °C to + 85°C, unless otherwise specified)

| Symbol            | Parameter                                                    | Test Conditions |      | Value |      | Unit |

|-------------------|--------------------------------------------------------------|-----------------|------|-------|------|------|

| Cymbol            | T drameter                                                   | rest conditions | Min. | Тур.  | Max. |      |

| I <sub>DD</sub>   | Run Mode Current<br>no CPUCLK prescale,<br>Clock divide by 2 | 24MHz, Note 1   |      |       | 40   | mA   |

| I <sub>DP2</sub>  | Run Mode Current<br>Prescale by 2<br>Clock divide by 2       | 24MHz, Note 1   |      |       | 30   | mA   |

| lwFi              | WFI Mode Current<br>no CPUCLK prescale,<br>Clock divide by 2 | 24MHz, Note 1   |      |       | 20   | mA   |

| I <sub>HALT</sub> | HALT Mode Current                                            | 24MHz, Note 1   |      |       | 100  | μΑ   |

Note 1: All I/O Ports are configured in Bidirectional Weak Pull-up Mode with no DC load, External Clock pin (OSCIN) is driven by square wave external clock. No peripheral working.

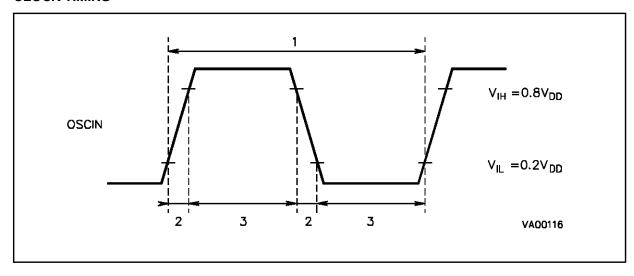

CLOCK TIMING TABLE ( $V_{DD} = 5V \pm 10\%$ ,  $T_A = -40^{\circ}C$  to + 85°C, INTCLK = 12MHz, unless otherwise specified)

| N°   | Symbol     | Parameter                | Va   | lue  | - Unit | Note |

|------|------------|--------------------------|------|------|--------|------|

| IN . | Зушьог     | raiametei                | Min. | Max. | Offic  | Note |

| 1    | ТрС        | OSCIN Clock Period       | 41.5 |      | ns     | 1    |

|      |            |                          | 83   |      | ns     | 2    |

| 2    | TrC, TfC   | OSCIN Rise and Fall Time |      | 12   | ns     |      |

| 3    | TwCL, TwCH | OSCIN Low and High Width | 17   | 25   | ns     | 1    |

|      |            |                          | 38   |      | ns     | 2    |

#### Notes:

- Clock divided by 2 internally (MODER.DIV2=1)

- Clock not divided by 2 internally (MODER.DIV2=0)

### **CLOCK TIMING**

### **EXTERNAL BUS TIMING TABLE**

( $V_{DD} = 5V \pm 10\%$ ,  $T_A = -40$  °C to +85 °C, Cload = 50pF, CPUCLK = 12MHz, unless otherwise specified)

|    |             |                                            | \                     | /alue (Note)              |                |      |      |

|----|-------------|--------------------------------------------|-----------------------|---------------------------|----------------|------|------|

| N° | Symbol      | Parameter                                  | OSCIN Divided<br>By 2 | OSCIN Not Divided<br>By 2 | Min.           | Мах. | Unit |

| 1  | TsA (AS)    | Address Set-up Time before AS ↑            | TpC (2P+1)-22         | TWCH+PTpC -18             | 20             |      | ns   |

| 2  | ThAS (A)    | Address Hold Time after AS ↑               | TpC -17               | TwCL -13                  | 25             |      | ns   |

| 3  | TdAS (DR)   | AS ↑ to Data Available (read)              | TpC (4P+2W+4) -52     | TpC (2P+W+2) -51          |                | 115  | ns   |

| 4  | TwAS        | AS Low Pulse Width                         | TpC (2P+1)-7          | TwCH+PTpC -3              | 35             |      | ns   |

| 5  | TdAz (DS)   | Address Float to DS ↓ t                    | 12                    | 12                        | 12             |      | ns   |

| 6  | TwDSR       | DS Low Pulse Width (read)                  | TpC (4P+2W+3) -20     | TwCH+TpC<br>(2P+W+1) -16  | 105            |      | ns   |

| 7  | TwDSW       | DS Low Pulse Width (write)                 | TpC (2P+2W+2)-13      | TpC (P+W+1) -13           | 70             |      | ns   |

| 8  | TdDSR (DR)  | DS ↓ to Data Valid Delay (read)            | TpC (4P+2W-3) -50     | TwCH+TpC(2P+W+1)<br>-46   |                | 75   | ns   |

| 9  | ThDR (DS)   | Data to DS ↑ Hold Time (read)              | 0                     | 0                         | 0              |      | ns   |

| 10 | TdDS (A)    | DS ↑ to Address Active Delay               | TpC -7                | TwCL -3                   | 35             |      | ns   |

| 11 | TdDS (AS)   | DS ↑ to AS ↓ Delay                         | TpC -18               | TwCL -14                  | 24             |      | ns   |

| 12 | TsR/W (AS)  | R/W Set-up Time before AS↑                 | TpC (2P+1)-22         | TwCH+PTpC -18             | 20             |      | ns   |

| 13 | TdDSR (R/W) | DS ↑ to R/W and Address Not<br>Valid Delay | TpC -9                | TwCL –5                   | 33             |      | ns   |

| 14 | TdDW (DSW)  | Write Data Valid to DS ↓ Delay (write)     | TpC (2P+1)-32         | TwCH+PTpC –28             | CH+PTpC -28 10 |      | ns   |

| 15 | ThDS (DW)   | Data Hold Time after DS↑ (write)           | TpC -9                | TwCL –5                   | 33             |      | ns   |

| 16 | TdA (DR)    | Address Valid to Data Valid Delay (read)   | TpC (6P+2W+5) -68     | TwCH+TpC<br>(3P+W+2) -64  |                | 140  | ns   |

| 17 | TdAs (DS)   | AS ↑ to DS ↓ Delay                         | TpC -18               | TwCL -14                  | 24             |      | ns   |

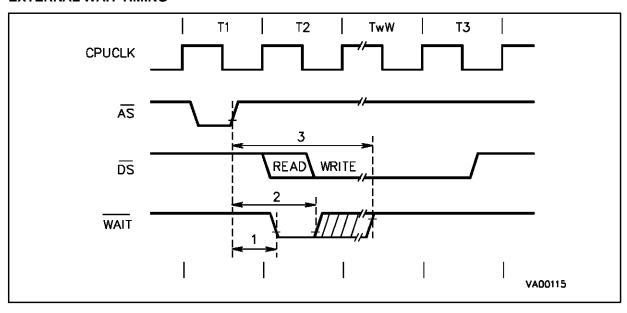

### **EXTERNAL WAIT TIMING TABLE**

$(V_{DD} = 5V \pm 10\%, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, Cload = 50pF,$

INTCLK = 12MHz, Push-pull output configuration, unless otherwise specified)

|    |             |                           | Value (Note)          |                           |      |            |      |

|----|-------------|---------------------------|-----------------------|---------------------------|------|------------|------|

| N° | Symbol      | Parameter                 | OSCIN Divided<br>By 2 | OSCIN Not Divided<br>By 2 | Min. | Мах.       | Unit |

| 1  | TdAs (WAIT) | AS ↑ to WAIT ↓ Delay      | 2(P+1)TpC -29         | 2(P+1)TpC -29             |      | 40         | ns   |

| 2  | TdAs (WAIT) | AS ↑ to WAIT ↓ Min. Delay | 2(P+W+1)TpC -4        | 2(P+W+1)TpC -4            | 80   |            | ns   |

| 3  | TdAs (WAIT) | AS ↑ to WAIT ↓ Max. Delay | 2(P+W+1)TpC -29       | 2(P+W+1)TpC -29           |      | 83W+<br>40 | ns   |

Note: (for both tables) The value in the left hand two columns show the formula used to calculate the timing minimum or maximum from the oscillator clock period, prescale value and number of wait cycles inserted.

The value in the right hand two columns show the timing minimum and maximum for an external clock at 24 MHz divided by 2, prescaler value

of zero and zero wait status.

Legend:

P = Clock Prescaling Value

W = Wait Cycles

TpC =OSCIN Period TwCH = High Level OSCIN half period TwCL =Low Level OSCIN half period

### **EXTERNAL BUS TIMING**

### **EXTERNAL WAIT TIMING**

SGS-THOMSON MICROELECTRONICS

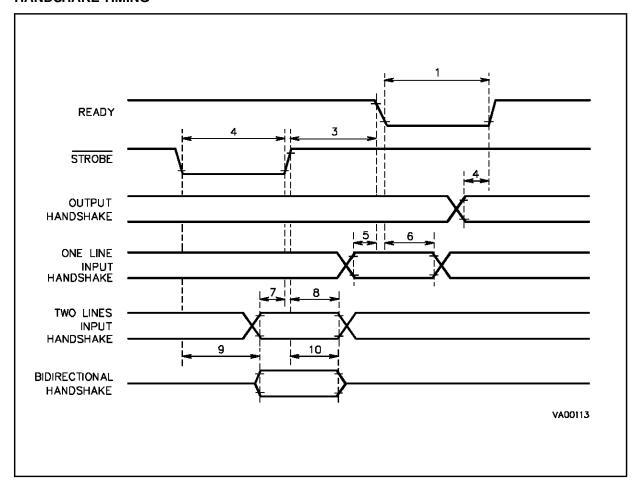

**HANDSHAKE TIMING TABLE** ( $V_{DD} = 5V \pm 10\%$ ,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, Cload = 50pF, INTCLK = 12MHz, Push-pull output configuration, unless otherwise specified)

|    |                |                                                                    |                      | Value               | (Note)                    |                   |      |      |      |

|----|----------------|--------------------------------------------------------------------|----------------------|---------------------|---------------------------|-------------------|------|------|------|

| N° | Symbol         | Parameter                                                          | OSCIN I              |                     | OSCIN No                  | ot Divided<br>/ 2 | Min. | Max. | Unit |

|    |                |                                                                    | Min.                 | Max.                | Min.                      | Max.              |      |      |      |

| 1  | TwRDY          | RDRDY, WRRDY Pulse<br>Width in One Line<br>Handshake               | 2TpC<br>(P+W+1) –18  |                     | TpC<br>(P+W+1) –<br>18    |                   | 65   |      | ns   |

| 2  | TwSTB          | RDSTB, WRSTB Pulse<br>Width                                        | 2TpC+12              |                     | TpC+12                    |                   | 95   |      | ns   |

| 3  | TdST<br>(RDY)  | RDSTB, or WRSTB↑ to RDRDY or WRRDY↓                                |                      | TpC+45 (TpC-TwC +45 |                           | (TpC-TwCL)<br>+45 |      | 87   | ns   |

| 4  | TsPD<br>(RDY)  | Port Data to RDRDY ↑<br>Set-up Time                                | (2P+2W+1)<br>TpC -25 |                     | TwCH+<br>(W+P)<br>TpC –25 |                   | 16   |      | ns   |

| 5  | TsPD<br>(RDY)  | Port Data to WRRDY ↓<br>Set-up Time in One Line<br>Handshake       | 43                   | 43                  |                           |                   | 43   |      | ns   |

| 6  | ThPD<br>(RDY)  | Port Data to WRRDY ↓ Hold Time in One Line Handshake               | 0                    |                     | 0                         |                   | 0    |      | ns   |

| 7  | TsPD<br>(STB)  | Port Data to WRSTB ↑<br>Set-up Time                                | 10                   |                     | 10                        |                   | 10   |      | ns   |

| 8  | ThPD<br>(STB)  | Port Data to WRSTB ↑ Hold Time                                     | 25                   |                     | 25                        |                   | 25   |      | ns   |

| 9  | TdSTB<br>(PD)  | RDSTBD ↑ to Port Data<br>Delay Time in<br>Bidirectional Handshake  |                      | 35                  |                           | 35                |      | 35   | ns   |

| 10 | TdSTB<br>(PHZ) | RDSTB ↑ to Port High-Z<br>Delay Time in<br>Bidirectional Handshake |                      | 25                  |                           | 25                |      | 25   | ns   |

Note: The value in the left hand two columns show the formula used to calculate the timing minimum or maximum from the oscillator clock period, prescale value and number of wait cycles inserted.

The value in the right hand two columns show the timing minimum and maximum for an external clock at 24 MHz divided by 2, prescaler value

of zero and zero wait status.

#### Legend:

= Clock Prescaling Value (R235.4,3,2)

= Programmable Wait Cycles (R252.2.1.0/5,4,3) + External Wait Cycles

### HANDSHAKE TIMING

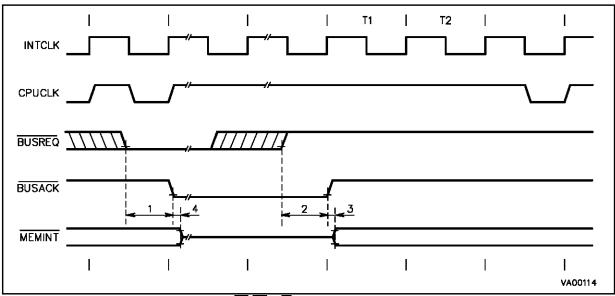

**BUS REQUEST/ACKNOWLEDGE TIMING TABLE** ( $V_{DD} = 5V \pm 10\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , Cload = 50pF, INTCLK = 12MHz, Push-pull output configuration, unless otherwise specified)

|             |                |                            |                       | Value (Note)              |      |     | Unit |

|-------------|----------------|----------------------------|-----------------------|---------------------------|------|-----|------|

| N°          | Symbol         | Parameter                  | OSCIN Divided<br>By 2 | OSCIN Not Divided<br>By 2 | Min. | 1 1 |      |

| 1           | TdBR (BACK)    | BREQ ↓ to BUSACK ↓         | TpC+8                 | TwCL+12                   | 50   |     | ns   |

| Tubk (BACK) | rabit (b/tott) | Bried & to Book or \$      | TpC(6P+2W+7)+65       | TpC(3P+W+3)+TwCL+65       |      | 360 | ns   |

| 2           | TdBR (BACK)    | BREQ ↑ to BUSACK ↑         | 3TpC+60               | TpC+TwCL+60               |      | 185 | ns   |

| 3           | TdBACK (BREL)  | BUSACK ↓ to Bus<br>Release | 20                    | 20                        |      | 20  | ns   |

| 4           | TdBACK (BACT)  | BUSACK ↑ to Bus<br>Active  | 20                    | 20                        |      | 20  | ns   |

Note: The value left hand two columns show the formula used to calculate the timing minimum or maximum from the oscillator clock period,

prescale value and number of wait cycles inserted.

The value right hand two columns show the timing minimum and maximum for an external clock at 24MHz divided by 2, prescale value of zero and zero wait status.

### **BUS REQUEST/ACKNOWLEDGE TIMING**

Note: MEMINT = Group of memory interface signals: AS, DS, R/W, P00-P07, P10-P17

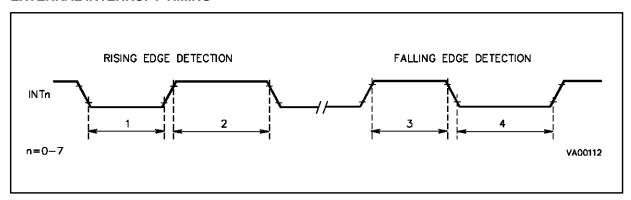

**EXTERNAL INTERRUPT TIMING TABLE** ( $V_{DD} = 5V \pm 10\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , Cload = 50pF, INTCLK = 12MHz, Push-pull output configuration, unless otherwise specified)

|            |        |                                                     | Value (Note)                  |                                   |      |      |      |

|------------|--------|-----------------------------------------------------|-------------------------------|-----------------------------------|------|------|------|

| <b>N</b> ° | Symbol | Parameter                                           | OSCIN<br>Divided By<br>2 Min. | OSCIN Not<br>Divided By<br>2 Min. | Min. | Max. | Unit |

| 1          | TwLR   | Low Level Minimum Pulse Width in Rising Edge Mode   | 2TpC+12                       | TpC+12                            | 95   |      | ns   |

| 2          | TwHR   | High Level Minimum Pulse Width in Rising Edge Mode  | 2TpC+12                       | TpC+12                            | 95   |      | ns   |

| 3          | TwHF   | High Level Minimum Pulse Width in Falling Edge Mode | 2TpC+12                       | TpC+12                            | 95   |      | ns   |

| 4          | TwLF   | Low Level Minimum Pulse Width in Falling Edge Mode  | 2TpC+12                       | TpC+12                            | 95   |      | ns   |

Note: The value left hand two columns show the formula used to calculate the timing minimum or maximum from the oscillator clock period, prescale value and number of wait cycles inserted.

The value right hand two columns show the timing minimum and maximum for an external clock at 24 MHz divided by 2, prescale value of zero

and zero wait status.