## N-CHANNEL 24V - 0.0052 Ω - 60A D²PAK STripFET™ III POWER MOSFET

| TYPE        | V <sub>DSS</sub> | R <sub>DS(on)</sub> | ID       |

|-------------|------------------|---------------------|----------|

| STB100NH02L | 24 V             | < 0.006 Ω           | 60 A (2) |

- TYPICAL R<sub>DS</sub>(on) = 0.0052 Ω @ 10 V

- TYPICAL  $R_{DS}(on) = 0.007 \ \Omega @ 5 V$

- R<sub>DS(ON)</sub> \* Qg INDUSTRY's BENCHMARK

- CONDUCTION LOSSES REDUCED

- SWITCHING LOSSES REDUCED

- LOW THRESHOLD DEVICE

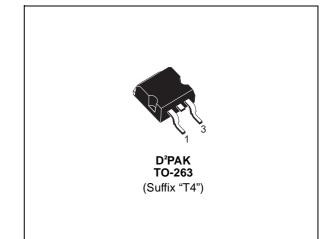

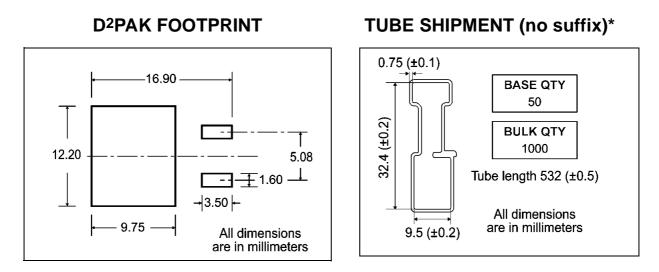

- SURFACE-MOUNTING D<sup>2</sup>PAK (TO-263)

POWER PACKAGE IN TUBE (NO SUFFIX) OR

IN TAPE & REEL (SUFFIX "T4")

#### DESCRIPTION

The STB100NH02L utilizes the latest advanced design rules of ST's proprietary STripFET<sup>™</sup> technology. This is suitable fot the most demanding DC-DC converter applications where high efficiency is to be achieved.

#### APPLICATIONS

SPECIFICALLY DESIGNED AND OPTIMISED FOR HIGH EFFICIENCY DC/DC CONVERTERS

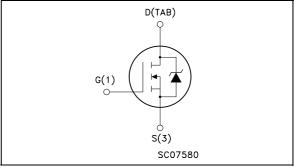

#### INTERNAL SCHEMATIC DIAGRAM

## ABSOLUTE MAXIMUM RATINGS

| Symbol Parameter                                   |                                                      | Value      | Unit |

|----------------------------------------------------|------------------------------------------------------|------------|------|

| V <sub>spike(1)</sub>                              | Drain-source Voltage Rating                          | 30         | V    |

| V <sub>DS</sub>                                    | Drain-source Voltage (V <sub>GS</sub> = 0)           | 24         | V    |

| Vdgr                                               | Drain-gate Voltage ( $R_{GS}$ = 20 k $\Omega$ )      | 24         | V    |

| $V_{GS}$                                           | Gate- source Voltage                                 | ± 20       | V    |

| I <sub>D</sub> (2)                                 | Drain Current (continuous) at T <sub>C</sub> = 25°C  | 60         | A    |

| I <sub>D</sub> (2)                                 | Drain Current (continuous) at T <sub>C</sub> = 100°C | 60         | A    |

| I <sub>DM</sub> (3)                                | Drain Current (pulsed)                               | 240        | A    |

| P <sub>tot</sub>                                   | Total Dissipation at $T_C = 25^{\circ}C$             | 100        | W    |

|                                                    | Derating Factor                                      | 0.67       | W/°C |

| E <sub>AS</sub> (4)                                | Single Pulse Avalanche Energy                        | 600        | mJ   |

| T <sub>stg</sub> Storage Temperature               |                                                      | 55 to 175  | °C   |

| T <sub>i</sub> Max. Operating Junction Temperature |                                                      | -55 to 175 |      |

September 2003

#### THERMAL DATA

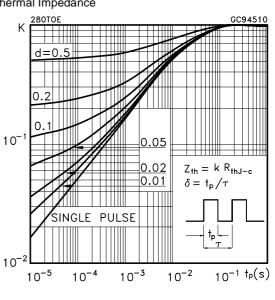

| Rthj-case<br>Rthj-amb | Thermal Resistance Junction-case<br>Thermal Resistance Junction-ambient<br>Maximum Lead Temperature For Soldering Purpose | Max<br>Max | 1.5<br>62.5<br>300 | °C/W<br>°C/W |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------|------------|--------------------|--------------|

| 11                    | Maximum Leau Temperature For Soldening Purpose                                                                            |            | 300                | C            |

# **ELECTRICAL CHARACTERISTICS** (T<sub>CASE</sub> = 25 °C UNLESS OTHERWISE SPECIFIED) OFF

| Symbol               | Parameter                                                | Test Conditions                                           | Min. | Тур. | Max.    | Unit     |

|----------------------|----------------------------------------------------------|-----------------------------------------------------------|------|------|---------|----------|

| V <sub>(BR)DSS</sub> | Drain-source<br>Breakdown Voltage                        | I <sub>D</sub> = 25 mA, V <sub>GS</sub> = 0               | 24   |      |         | V        |

| I <sub>DSS</sub>     | Zero Gate Voltage<br>Drain Current (V <sub>GS</sub> = 0) | $V_{DS} = 20 V$<br>$V_{DS} = 20 V$ $T_{C} = 125^{\circ}C$ |      |      | 1<br>10 | μΑ<br>μΑ |

| I <sub>GSS</sub>     | Gate-body Leakage<br>Current (V <sub>DS</sub> = 0)       | $V_{GS} = \pm 20 V$                                       |      |      | ±100    | nA       |

#### ON (5)

| Symbol              | Parameter                            | Test Conditions   |                         | Min. | Тур.            | Max.           | Unit   |

|---------------------|--------------------------------------|-------------------|-------------------------|------|-----------------|----------------|--------|

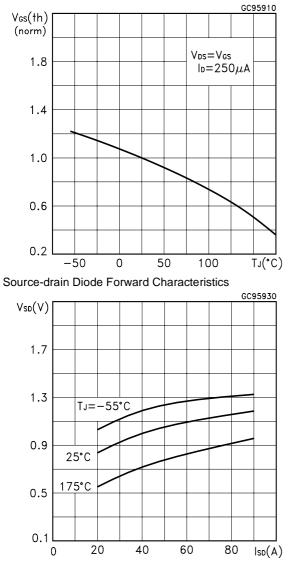

| V <sub>GS(th)</sub> | Gate Threshold Voltage               | $V_{DS} = V_{GS}$ | I <sub>D</sub> = 250 μA | 1    | 1.8             |                | V      |

| R <sub>DS(on)</sub> | Static Drain-source On<br>Resistance |                   |                         |      | 0.0052<br>0.007 | 0.006<br>0.011 | Ω<br>Ω |

#### DYNAMIC

| Symbol                                                   | Parameter                                                                  | Test Conditions                                                  | Min. | Тур.               | Max. | Unit           |

|----------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------|------|--------------------|------|----------------|

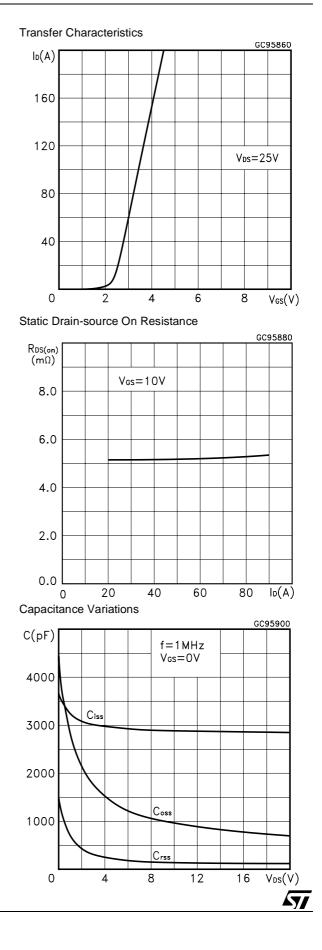

| g <sub>fs</sub> <sup>(5)</sup>                           | Forward Transconductance                                                   | V <sub>DS</sub> = 10 V I <sub>D</sub> = 30 A                     |      | 40                 |      | S              |

| C <sub>iss</sub><br>C <sub>oss</sub><br>C <sub>rss</sub> | Input Capacitance<br>Output Capacitance<br>Reverse Transfer<br>Capacitance | $V_{DS}$ = 15V f = 1 MHz $V_{GS}$ = 0                            |      | 2850<br>800<br>120 |      | pF<br>pF<br>pF |

| R <sub>G</sub>                                           | Gate Input Resistance                                                      | f=1 MHz Gate DC Bias=0<br>Test Signal Level =20 mV<br>Open Drain |      | 1                  |      | Ω              |

#### ELECTRICAL CHARACTERISTICS (continued)

#### SWITCHING ON

| Symbol                                               | Parameter                                                    | Test Conditions                                                  | Min. | Тур.            | Max. | Unit           |

|------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------|------|-----------------|------|----------------|

| t <sub>d(on)</sub><br>t <sub>r</sub>                 | Turn-on Delay Time<br>Rise Time                              |                                                                  |      | 13<br>75        |      | ns<br>ns       |

| Q <sub>g</sub><br>Q <sub>gs</sub><br>Q <sub>gd</sub> | Total Gate Charge<br>Gate-Source Charge<br>Gate-Drain Charge | V <sub>DD</sub> =10 V I <sub>D</sub> =60 A V <sub>GS</sub> =10 V |      | 47.5<br>10<br>7 | 64   | nC<br>nC<br>nC |

#### SWITCHING OFF

| Symbol                                | Parameter                        | Test Conditions                                                                                                                              | Min. | Тур.     | Max. | Unit     |

|---------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|----------|

| t <sub>d(off)</sub><br>t <sub>f</sub> | Turn-off Delay Time<br>Fall Time | $ \begin{array}{ll} V_{DD} = 10 \ V & I_D = 30 \ A \\ R_G = 4.7 \Omega, & V_{GS} = 10 \ V \\ (\text{Resistive Load, Figure 3}) \end{array} $ |      | 50<br>18 | 24.3 | ns<br>ns |

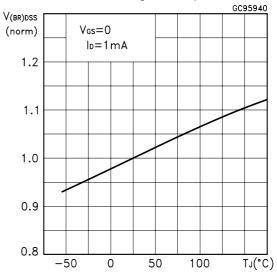

#### SOURCE DRAIN DIODE

| Symbol                                                 | Parameter                                                                    | Test Conditions                                                                                                                                                                          | Min. | Тур.          | Max.      | Unit          |

|--------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-----------|---------------|

| I <sub>SD</sub><br>I <sub>SDM</sub>                    | Source-drain Current<br>Source-drain Current (pulsed)                        |                                                                                                                                                                                          |      |               | 60<br>240 | A<br>A        |

| V <sub>SD</sub> <sup>(5)</sup>                         | Forward On Voltage                                                           | $I_{SD} = 30 \text{ A}$ $V_{GS} = 0$                                                                                                                                                     |      |               | 1.3       | V             |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>RRM</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $      I_{SD} = 60 \mbox{ A} \qquad \mbox{di/dt} = 100 \mbox{A/} \mu \mbox{s} \\ V_{DD} = 16 \mbox{ V} \qquad \mbox{T}_j = 150^{\circ} \mbox{C} \\ (\mbox{see test circuit, Figure 5}) $ |      | 35<br>35<br>2 |           | ns<br>nC<br>A |

$^{(5)}$  Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %.  $^{(6)}$  Q<sub>oss</sub> = C<sub>oss</sub>\* $\Delta$  V<sub>in</sub> , C<sub>oss</sub> = C<sub>gd</sub> + C<sub>ds</sub> . See Appendix A  $^{(7)}$  Gate charge for synchronous operation

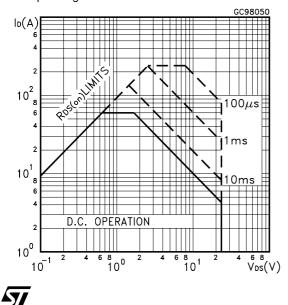

#### Safe Operating Area

Thermal Impedance

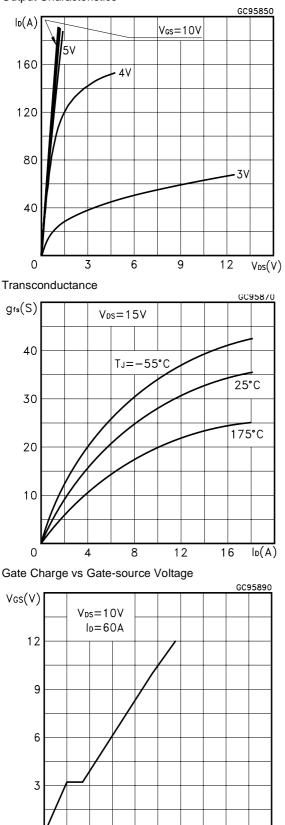

#### **Output Characteristics**

0

20

40

60

80

Q₀(nC)

Normalized Gate Threshold Voltage vs Temperature

Ros(on) (norm) 1.6 1.4 1.2 1.0 0.8 -50 0 50 100 TJ(°C)

Normalized Breakdown Voltage vs Temperature.

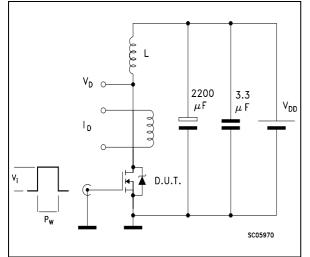

#### Fig. 1: Unclamped Inductive Load Test Circuit

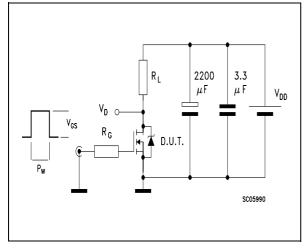

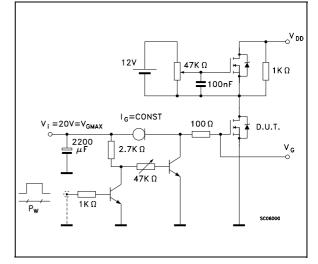

**Fig. 3:** Switching Times Test Circuits For Resistive Load

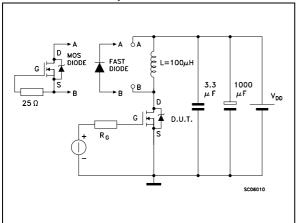

**Fig. 5:** Test Circuit For Inductive Load Switching And Diode Recovery Times

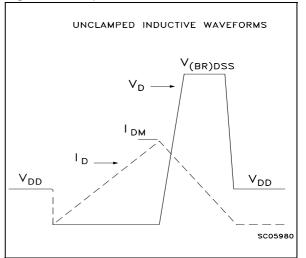

#### Fig. 2: Unclamped Inductive Waveform

Fig. 4: Gate Charge test Circuit

Γ

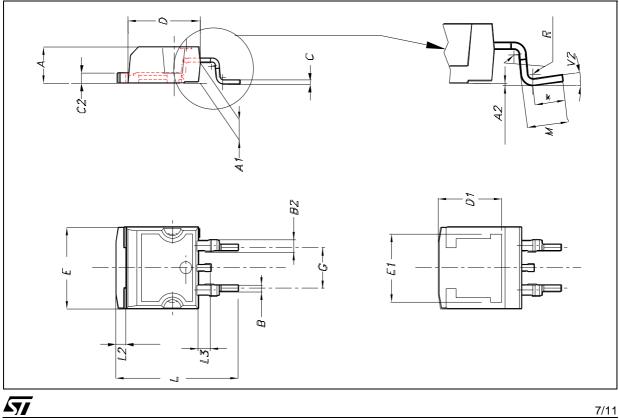

|      |      | D <sup>2</sup> PA | K MECHANIC | AL DATA |       |       |

|------|------|-------------------|------------|---------|-------|-------|

| DIM. |      | mm.               |            |         | inch. |       |

|      | MIN. | TYP.              | MAX.       | MIN.    | TYP.  | TYP.  |

| Α    | 4.4  |                   | 4.6        | 0.173   |       | 0.181 |

| A1   | 2.49 |                   | 2.69       | 0.098   |       | 0.106 |

| A2   | 0.03 |                   | 0.23       | 0.001   |       | 0.009 |

| В    | 0.7  |                   | 0.93       | 0.028   |       | 0.037 |

| B2   | 1.14 |                   | 1.7        | 0.045   |       | 0.067 |

| С    | 0.45 |                   | 0.6        | 0.018   |       | 0.024 |

| C2   | 1.21 |                   | 1.36       | 0.048   |       | 0.054 |

| D    | 8.95 |                   | 9.35       | 0.352   |       | 0.368 |

| D1   |      | 8                 |            |         | 0.315 |       |

| E    | 10   |                   | 10.4       | 0.394   |       | 0.409 |

| E1   |      | 8.5               |            |         | 0.334 |       |

| G    | 4.88 |                   | 5.28       | 0.192   |       | 0.208 |

| L    | 15   |                   | 15.85      | 0.591   |       | 0.624 |

| L2   | 1.27 |                   | 1.4        | 0.050   |       | 0.055 |

| L3   | 1.4  |                   | 1.75       | 0.055   |       | 0.069 |

| М    | 2.4  |                   | 3.2        | 0.094   |       | 0.126 |

| R    |      | 0.4               |            | 1       | 0.015 |       |

| V2   | 0°   |                   | 4°         | 0°      |       | 4°    |

7/11

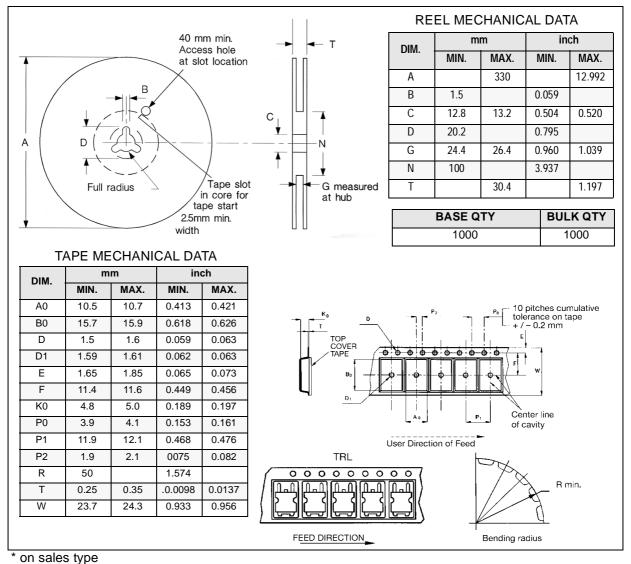

## TAPE AND REEL SHIPMENT (suffix "T4")\*

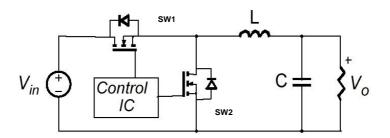

### APPENDIX A Buck Converter: Power Losses Estimation

The power losses associated with the FETs in a Synchronous Buck converter can be estimated using the equations shown in the table below. The formulas give a good approximation, for the sake of performance comparison, of how different pairs of devices affect the converter efficiency. However a very important parameter, the working temperature, is not considered. The real device behavior is really dependent on how the heat generated inside the devices is **e**moved to allow for a safer working junction temperature.

The low side (SW2) device requires:

- Very low R<sub>DS(on)</sub> to reduce conduction losses

- Small Q<sub>gls</sub> to reduce the gate charge losses

- Small C<sub>oss</sub> to reduce losses due to output capacitance

- Small Q<sub>rr</sub> to reduce losses on SW<sub>1</sub> during its turn-on

- The  $C_{gd}/C_{gs}$  ratio lower than  $V_{th}/V_{gg}$  ratio especially with low drain to source voltage to avoid the cross conduction phenomenon;

The high side (SW1) device requires:

- Small  $R_g$  and  $L_s$  to allow higher gate current peak and to limit the voltage feedback on the gate

- Small Qg to have a faster commutation and to reduce gate charge losses

- Low R<sub>DS(on)</sub> to reduce the conduction losses.

**A**7/

|                      |            | High Side Switch (SW1)                                         | Low Side Switch (SW2)                                                             |

|----------------------|------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Pconduct             | ion        | $R_{\rm DS(on)SW1}*I_L^2*d$                                    | $R_{DS(on)SW2} * I_L^2 * (1-d)$                                                   |

| Pswitching           |            | $V_{in} * (Q_{gsth(SW1)} + Q_{gd(SW1)}) * f * \frac{I_L}{I_g}$ | Zero Voltage Switching                                                            |

| P <sub>diode</sub>   | Recovery   | Not Applicable                                                 | $^{1}V_{in} * Q_{rr(SW2)} * f$                                                    |

|                      | Conduction | Not Applicable                                                 | $V_{\rm f(SW2)} * I_{\rm L} * t_{\rm deadtime} * f$                               |

| Pgate(Q <sub>G</sub> | )          | $Q_{g(SW1)} * V_{gg} * f$                                      | $\mathbf{Q}_{\mathbf{gls}(\mathrm{SW2})} * \mathbf{V}_{\mathbf{gg}} * \mathbf{f}$ |

| P <sub>Qoss</sub>    |            | $\frac{V_{in} * Q_{oss(SW1)} * f}{2}$                          | $\frac{V_{in} * Q_{oss(SW2)} * f}{2}$                                             |

| Parameter        | Meaning                                      |

|------------------|----------------------------------------------|

| d                | Duty-cycle                                   |

| Qgsth            | Post threshold gate charge                   |

| Q <sub>gls</sub> | Third quadrant gate charge                   |

| Pconduction      | On state losses                              |

| Pswitching       | On-off transition losses                     |

| Pdiode           | Conduction and reverse recovery diode losses |

| Pgate            | Gate drive losses                            |

| PQoss            | Output capacitance losses                    |

<sup>&</sup>lt;sup>1</sup> Dissipated by SW1 during turn-on

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

All other names are the property of their respective owners.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com