# Nonvolatile DACPOT™ Electronic Potentiometer With Up/Down Counter Interface

#### **FEATURES**

- Digitally Controlled Electronic Potentiometer

- 7-Bit Digital-to-Analog Converter (DAC)

- Independent Reference Inputs

- Differential Non-Linearity ±0.5LSB

- Integral Non-Linearity ±1LSB

- V<sub>OUT</sub> Value in EEPROM for Power-On Recall

- Equivalent to 128-Step Potentiometer

- Unity Gain Op Amp Drives ±100μA

- Simple Trimming Adjustment

- Up/Down Counter Style Operation

- Low Noise Operation

- "Clickless" Transitions between DAC Steps

- No Mechanical Wearout Problem

- 1,000,000 Stores (typical)

- 100 Year Data Retention

- Operation from +2.7V to +5.5V Supply

- Ultra-Low Power, 0.5mW max at +5V

#### **OVERVIEW**

The SMP9317 DACPOT<sup>TM</sup> trimmer is a 7-bit nonvolatile DAC designed to replace mechanical potentiometers. The SMP9317 includes a unity-gain amplifier to buffer the DAC output and enables  $V_{OUT}$  to swing from rail to rail. The DACPOT trimmer operates over a supply voltage range of 2.7V to 5.5V.

The SMP9317's simple up/down counter input provides an ideal interface for automatic test equipment to dither and monitor the V<sub>OUT</sub> voltage. This interface allows for quick and consistent calibration of even the most sophisticated systems.

The SMP9317 is a pin-compatible performance upgrade for other industry nonvolatile potentiometers. The SMP9317 offers higher resolution than these devices and provides 'clickless' transitions of V<sub>OUT</sub>.

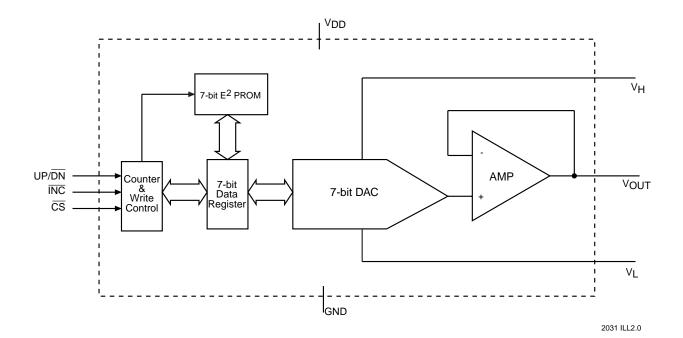

#### **FUNCTIONAL BLOCK DIAGRAM**

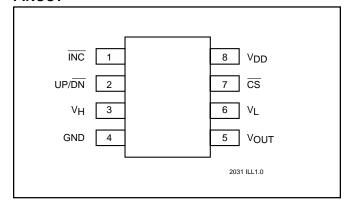

#### **PIN NAMES**

| Symbol          | Description                                      |  |  |

|-----------------|--------------------------------------------------|--|--|

| ĪNC             | Increment Input, High to Low<br>Edge Trigger     |  |  |

| UP/DN           | Up/Down Input controlling relative Vout movement |  |  |

| V <sub>H</sub>  | V+ reference input                               |  |  |

| GND             | Analog and Digital Ground                        |  |  |

| Vout            | Trimmed Voltage Output                           |  |  |

| VL              | V- reference input                               |  |  |

| CS              | Active low chip select input                     |  |  |

| V <sub>DD</sub> | Supply Voltage (2.7V to 5.5V)                    |  |  |

## **Analog Section**

The SMP9317 is a 7-bit, voltage output digital-to-analog converter (DAC). The DAC consists of a resistor network that converts a 7-bit value into equivalent analog output voltages in proportion to the applied reference voltage.

## Reference Inputs

The voltage differential between the  $V_L$  and  $V_H$  inputs sets the full-scale output voltage range.  $V_L$  must be equal to or greater than ground (i.e. a positive voltage).  $V_H$  must be greater than  $V_L$  and less than or equal to  $V_{DD}$ . See table on page 3 for guaranteed operating limits.

#### **Output Buffer Amplifier**

The voltage output is from a precision unity-gain follower that can slew up to  $1V/\mu s$ .

#### **Digital Interface**

The interface is designed to emulate a simple up/down counter, but instead of a parallel count output, a ratiometric voltage output is provided.

Chip Select ( $\overline{\text{CS}}$ ) is an active low input. Whenever  $\overline{\text{CS}}$  is high the SMP9317 is in standby mode and consumes the least power. This mode is equivalent to a potentiometer that is adjusted to the required setting. When  $\overline{\text{CS}}$  is low the SMP9317 will recognize transitions on the  $\overline{\text{INC}}$  input and will move the  $V_{\text{OUT}}$  either toward the  $V_{\text{H}}$  reference or toward the  $V_{\text{L}}$  reference depending upon the state of the UP/ $\overline{\text{DN}}$  input.

The host may exit an adjustment routine in two ways: deselecting the SMP9317 while  $\overline{\text{INC}}$  is low will not perform a store operation (a subsequent power cycle will recall the original data); deselecting the SMP9317 while  $\overline{\text{INC}}$  is high will store the current  $V_{\text{OUT}}$  setting into nonvolatile memory.

#### **PINOUT**

Increment ( $\overline{INC}$ ) is an edge triggered input. Whenever  $\overline{CS}$  is low and a high to low transition occurs on the  $\overline{INC}$  input, the  $V_{OUT}$  voltage will either move toward  $V_H$  or  $V_L$  depending upon the state of the  $UP/\overline{DN}$  input.

**UP/Down (UP/DN)** is an input that will determine the V<sub>OUT</sub> movement relative to V<sub>H</sub> and V<sub>L</sub>. When  $\overline{\text{CS}}$  is low, UP/ $\overline{\text{DN}}$  is high and there is a high to low transition on  $\overline{\text{INC}}$ , the V<sub>OUT</sub> voltage will move (1/128<sup>th</sup> x V<sub>H</sub>-V<sub>L</sub>) toward V<sub>H</sub>. When  $\overline{\text{CS}}$  and UP/ $\overline{\text{DN}}$  are low, and there is a high to low transition on  $\overline{\text{INC}}$ , the V<sub>OUT</sub> will move (1/128<sup>th</sup> x V<sub>H</sub>-V<sub>L</sub>) toward V<sub>L</sub>.

## Power-Up/Power-Down Conditions

On power–up the SMP9317 loads the value of EEPROM memory into the wiper position register. The value in the register is changed using the  $\overline{CS}$ ,  $\overline{INC}$ , and UP/DN pins. The new data in the register will be lost at power-down unless  $\overline{CS}$  was brought high, with  $\overline{INC}$  high, to initiate a store operation after the last increment or decrement. On the next device power–up, the value of EEPROM memory will be loaded into the wiper position register. During power-up the SMP9317 is write-protected in two ways:

- 1) A power-on reset, that trips at approximately 2.5V, holds  $\overline{\text{CS}}$  and  $\overline{\text{INC}}$  high internally.

- 2) Resistor pull-ups on all logic inputs prevent data change if the inputs are floating.

#### **Data Retention**

The SMP9317 is guaranteed to perform at least 1,000,000 writes to EEPROM before a wear—out condition can occur. After EEPROM wearout, the SMP9317 continues to function as a volatile digital-potentiometer. The wiper position can be changed during powered conditions using the digital interface. However, on power—up the wiper—position will be indeterminate.

On shipment from the factory, Summit Microelectronics does not specify any EEPROM memory value. The value must be set by the customer as needed.

2031 PGM T1.0

## **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias         |                 | -55°C to +125°C               |

|--------------------------------|-----------------|-------------------------------|

| Storage Temperature            |                 | -65°C to +150°C               |

| Voltage on pins with reference | to GND:         |                               |

|                                | Analog Inputs   | -0.5V to V <sub>DD</sub> +.5V |

|                                | Digital Inputs  | -0.5V to V <sub>DD</sub> +.5V |

| A                              | nalog Outputs   | -0.5V to V <sub>DD</sub> +.5V |

| ]                              | Digital Outputs | -0.5V to V <sub>DD</sub> +.5V |

| Lead Solder Temperature (10    | secs)           | 300°C                         |

|                                |                 |                               |

#### \*COMMENT

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside those listed in the operation sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

## **RECOMMENDED OPERATING CONDITIONS**

| Condition       | Min   | Max   |

|-----------------|-------|-------|

| Temperature     | -40°C | +85°C |

| V <sub>DD</sub> | +2.7V | +5.5V |

## DAC DC ELECTRICAL CHARACTERISTICS

$V_{DD}$  = +2.7V to +5.5V,  $V_{refH}$  =  $V_{DD}$ ,  $V_{refL}$  = 0V,  $T_A$  = -40°C to +85°C, unless specified otherwise

|            | Symbol             | Parameter                                           | Conditions                                                                                  |                                         | Min.   | Тур.         | Max.                 | Units      |

|------------|--------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------|--------|--------------|----------------------|------------|

| Accuracy   | INL                | Integral Non-Linearity                              | $I_{LOAD} = 50\mu A$ ,                                                                      | $T_R = C$<br>$T_R = I$                  | -<br>- | 0.6<br>0.6   | ±1<br>±1             | LSB<br>LSB |

|            |                    |                                                     | $I_{LOAD} = 100 \mu A$ ,                                                                    | T <sub>R</sub> =C<br>T <sub>R</sub> = I | -      | 1.2<br>1.2   | -                    | LSB<br>LSB |

|            | DNL                | Differential Non-Linearity                          | $I_{LOAD} = 50\mu A$ ,                                                                      | $T_R = C$<br>$T_R = I$                  | -      | 0.25<br>0.25 | ±0.5<br>±0.5         | LSB<br>LSB |

|            |                    |                                                     | $I_{LOAD} = 100 \mu A$ ,                                                                    | $T_R = C$<br>$T_R = I$                  | -      | 0.5<br>0.5   | -                    | LSB<br>LSB |

| References | VH                 | V <sub>refH</sub> Input Voltage                     |                                                                                             |                                         | 2.5    | -            | V <sub>DD</sub>      | V          |

|            | VL                 | V <sub>refL</sub> Input Voltage                     | $V_H \ge V_L$                                                                               |                                         | Gnd    | -            | V <sub>DD</sub> -2.5 | V          |

|            | R <sub>IN</sub>    | V <sub>refH</sub> to V <sub>refL</sub> Resistance   |                                                                                             |                                         | -      | 38K          | -                    | Ω          |

|            | TCRIN              | Temperature Coefficient of R <sub>IN</sub>          | V <sub>refH</sub> to V <sub>refL</sub>                                                      |                                         | -      | 700          | -                    | ppm/°C     |

| Analog     | G <sub>EFS</sub>   | Full-Scale Gain Error                               | DATA = 7F                                                                                   |                                         | -      | -            | ±1                   | LSB        |

| Output     | VoutZS             | Zero-Scale Output Voltage                           | DATA = 00                                                                                   |                                         | 0      |              | 20                   | mV         |

|            | TCV <sub>OUT</sub> | V <sub>OUT</sub> Temperature<br>Coefficient, note 3 | V <sub>DD</sub> = +5, I <sub>LOAD</sub> = 5<br>V <sub>refH</sub> = +5V, V <sub>refL</sub> = |                                         | -      | -            | 200                  | μV/°C      |

|            | IL                 | Amplifier Output Load Current                       |                                                                                             |                                         |        |              | 100                  | μΑ         |

|            | R <sub>OUT</sub>   | Amplifier Output Resistance                         | I <sub>L</sub> = 100μA                                                                      | +5V<br>+3V                              | -      | 10<br>20     |                      | Ω          |

|            | PSRR               | Power Supply Rejection                              | $I_{LOAD} = 10\mu A$                                                                        |                                         | -      | -            | 1                    | LSB/V      |

|            | e <sub>N</sub>     | Amplifier Output Noise                              | f = 1KHz, V <sub>DD</sub> = +5                                                              | V                                       | -      | 90           | -                    | nV/ √Hz    |

|            | THD                | Total Harmonic Distortion                           | V <sub>IN</sub> = 1V rms, f = 1                                                             | KHz                                     | -      | 0.08         | -                    | %          |

|            | BW                 | Bandwidth - 3dB                                     | V <sub>IN</sub> = 100mV rms                                                                 |                                         | -      | 1,000        | -                    | kHz        |

## RELIABILITY CHARACTERISTICS (over recommended operating conditions unless otherwise specified)

| Symbol           | Parameter          | Min       | Max | Unit   | Test Method       |

|------------------|--------------------|-----------|-----|--------|-------------------|

| VZAP             | ESD Susceptibility | 2000      |     | V      | MS-883, TM 3015   |

| <sup>I</sup> LTH | Latch-Up           | 100       |     | mA     | JEDEC Standard 17 |

| T <sub>DR</sub>  | Data Retention     | 100       |     | Years  | MS-883, TM 1008   |

| N <sub>END</sub> | Endurance          | 1,000,000 |     | Stores | MS-883, TM 1033   |

2031 PGM T2.0

## DC ELECTRICAL CHARACTERISTICS

V<sub>DD</sub> = +2.7V to +5.5V, V<sub>H</sub> = V<sub>DD</sub>, V<sub>L</sub> = 0V, T<sub>A</sub> = -40°C to +85°C, Unless otherwise specified

| Symbol          | Parameter                           | Conditions                                          | Min | Тур | Max             | Units |

|-----------------|-------------------------------------|-----------------------------------------------------|-----|-----|-----------------|-------|

| I <sub>DD</sub> | Supply Current during store, note 1 | CS = V <sub>IL</sub> to V <sub>IH</sub><br>W/INC HI |     | 1.0 |                 | mA    |

| I <sub>SB</sub> | Supply Standby Current              | CS = V <sub>IH</sub>                                |     |     | 100             | μΑ    |

| lін             | Input Leakage Current               | $V_{IN} = V_{DD}$                                   |     |     | 10              | μΑ    |

| I <sub>IL</sub> | Input Leakage Current, note 2       | V <sub>IN</sub> = 0V                                |     |     | -25             | μΑ    |

| ViH             | High Level Input Voltage            |                                                     | 2   |     | V <sub>DD</sub> | V     |

| V <sub>IL</sub> | Low Level Input Voltage             | V <sub>DD</sub> ≥ 4.5V                              | 0   |     | 0.8             | V     |

2031 PGM T4.1

#### Notes:

- 1. I<sub>DD</sub> is the supply current drawn while the EEPROM is being updated. I<sub>DD</sub> does not include the current that flows through the Reference resistor chain.

- 2.  $\overline{\text{CS}}$ , UP/ $\overline{\text{DN}}$  and  $\overline{\text{INC}}$  have internal pull-up resistors of approximately 200k $\Omega$ . When the input is pulled to ground the resulting output current will be  $V_{DD}/200k\Omega$ .

- 3. TCV<sub>OUT</sub> is guaranteed but not tested.

## **OPERATIONAL TRUTH TABLE**

| INC                 | <del>CS</del>       | UP/DN | Operation                              |  |

|---------------------|---------------------|-------|----------------------------------------|--|

| HI <sub>TO</sub> LO | L                   | Н     | V <sub>OUT</sub> toward V <sub>H</sub> |  |

| HI <sub>TO</sub> LO | L                   | L     | V <sub>OUT</sub> toward V <sub>L</sub> |  |

| Н                   | LO <sub>TO</sub> HI | X     | Store Setting                          |  |

| L                   | LO <sub>TO</sub> HI | Х     | Maintain Setting, NO Store             |  |

| Х                   | Н                   | Х     | Standby, note 1                        |  |

Notes: 1. The Standby or operating current will be lowest with INC and UP/DN pins at H as there are weak internal pull-ups that draw current when connected LO.

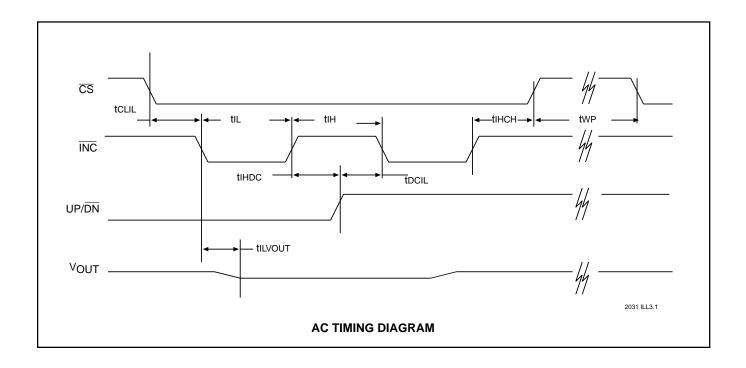

# **AC TIMING CHARACTERISTICS**

| Symbol              | Parameter                     | Min | Max | Units |

|---------------------|-------------------------------|-----|-----|-------|

| tcliL               | CS to INC Setup               | 100 |     | ns    |

| t <sub>IHDC</sub>   | INC High to UP/DN Change      | 100 |     | ns    |

| t <sub>DCIL</sub>   | UP/DN to INC Setup            | 100 |     | ns    |

| tıL                 | INC Low Period                | 200 |     | ns    |

| t <sub>IH</sub>     | INC High Period               | 200 |     | ns    |

| tihch               | INC Inactive to CS Inactive   | 100 |     | ns    |

| twp                 | Write Cycle Time              |     | 5   | ms    |

| t <sub>ILVOUT</sub> | INC to V <sub>OUT</sub> Delay |     | 5   | μs    |

2031 PGM T6.0

#### **NOTICE**

SUMMIT Microelectronics, Inc. reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. SUMMIT Microelectronics, Inc. assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained herein reflect representative operating parameters, and may vary depending upon a user's specific application. While the information in this publication has been carefully checked, SUMMIT Microelectronics, Inc. shall not be liable for any damages arising as a result of any error or omission.

SUMMIT Microelectronics, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless SUMMIT Microelectronics, Inc. receives written assurances, to its satisfaction, that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; and (c) potential liability of SUMMIT Microelectronics, Inc. is adequately protected under the circumstances.

© Copyright 1998 SUMMIT Microelectronics, Inc.