#### **FEATURES**

- Low Cost

- Latch-Up Protected: Will Withstand 500 mA Reverse Output Current

- ESD Protected .....±2 kV

- High Peak Output Current......1.2A Peak

- High Capacitive Load Drive

- Capability ...... 1000pF in 38nsec

- Wide Operating Range ...... 4.5V to 16V

- Low Delay Time......75nsec Max

- Logic Input Threshold Independent of Supply Voltage

- Output Voltage Swing to Within 25mV of Ground or V<sub>DD</sub>

- Low Output Impedance ...... 8 $\Omega$

#### **APPLICATIONS**

- Power MOSFET Drivers

- Switched Mode Power Supplies

- Pulse Transformer Drive

- **■** Small Motor Controls

- Print Head Drive

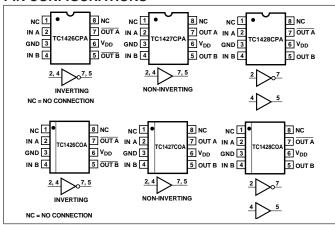

#### **PIN CONFIGURATIONS**

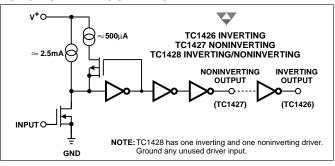

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **GENERAL DESCRIPTION**

The TC1426/27/28 are a family of 1.2A dual high-speed drivers. CMOS fabrication is used for low power consumption and high efficiency.

These devices are fabricated using an epitaxial layer to effectively short out the intrinsic parasitic transistor responsible for CMOS latch-up. They incorporate a number of other design and process refinements to increase their long-term reliability.

The TC1426 is compatible with the bipolar DS0026, but only draws 1/5 of the quiescent current. The TC1426/27/28 are also compatible with the TC426/27/28, but with 1.2A peak output current rather than the 1.5A of the TC426/27/28 devices.

Other compatible drivers are the TC4426/27/28 and the TC4426A/27A/28A. The TC4426/27/28 have the added feature that the inputs can withstand negative voltage up to 5V with diode protection circuits. The TC4426A/27A/28A have matched input to output leading edge and falling edge delays, tD1 and tD2, for processing short duration pulses in the 25 nanoseconds range. All of the above drivers are pin compatible.

The high-input impedance TC1426/27/28 drivers are CMOS/TTL input-compatible, do not require the speed-up needed by the bipolar devices, and can be directly driven by most PWM ICs.

This family of devices is available in inverting and non-inverting versions. Specifications have been optimized to achieve low-cost and high-performance devices, well-suited for the high-volume manufacturer.

#### **ORDERING INFORMATION**

| Part No.  | Package           | Temp. Range  |

|-----------|-------------------|--------------|

| TC1426COA | 8-Pin SOIC        | 0°C to +70°C |

| TC1426CPA | 8-Pin Plastic DIP | 0°C to +70°C |

| TC1427COA | 8-Pin SOIC        | 0°C to +70°C |

| TC1427CPA | 8-Pin Plastic DIP | 0°C to +70°C |

| TC1428COA | 8-Pin SOIC        | 0°C to +70°C |

| TC1428CPA | 8-Pin Plastic DIP | 0°C to +70°C |

|           |                   |              |

TC1426 TC1427 TC1428

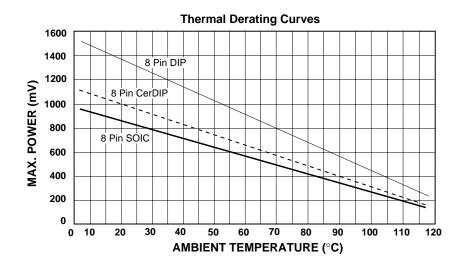

#### **ABSOLUTE MAXIMUM RATINGS\***

| Power Dissipation (T <sub>A</sub> ≤ 70°C)    |                            |

|----------------------------------------------|----------------------------|

| Plastic DIP                                  | 730W                       |

| SOIC                                         | 470 mW                     |

| Derating Factor                              |                            |

| Plastic DIP                                  | 8 mW/°C                    |

| SOIC                                         | 4 mW/°C                    |

| Supply Voltage                               | 18V                        |

| Input Voltage, Any Terminal (V <sub>DF</sub> | + 0.3V) to (GND $- 0.3V$ ) |

| Operating Temperature: C Versio              | n0°C to +70°C              |

| E Versio                                     | n – 40°C to +85°C          |

| Maximum Chip Temperature             | +150°C |

|--------------------------------------|--------|

| Storage Temperature                  |        |

| Lead Temperature (Soldering ,10 sec) |        |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS:** $T_A = 25^{\circ}C$ with $4.5V \le V_{DD}^+ \le 16V$ unless otherwise specified.

| Symbol           | Parameter            | Test Conditions                                                                                      | Min                     | Тур | Max      | Unit |

|------------------|----------------------|------------------------------------------------------------------------------------------------------|-------------------------|-----|----------|------|

| Input            |                      |                                                                                                      |                         |     | 1        |      |

| V <sub>IH</sub>  |                      | Logic 1, Input Voltage                                                                               | 3                       | _   | _        | V    |

| $V_{IL}$         |                      | Logic 0, Input Voltage                                                                               | _                       |     | 0.8      | V    |

| I <sub>IN</sub>  | Input Current        | $0V \le V_{IN} \le V_{DD}$                                                                           | -1                      | _   | 1        | μΑ   |

| Output           |                      |                                                                                                      |                         |     |          |      |

| $V_{OH}$         | High Output Voltage  | Test Figures 1 and 2                                                                                 | V <sub>DD</sub> – 0.025 |     | _        | V    |

| $V_{OL}$         | Low Output Voltage   | Test Figures 1 and 2                                                                                 | _                       | _   | 0.025    | V    |

| R <sub>O</sub>   | Output Resistance    | $V_{IN} = 0.8V$ ,                                                                                    | _                       | 12  | 18       | Ω    |

|                  |                      | $I_{OUT} = 10 \text{ mA}, V_{DD} = 16V$<br>$V_{IN} = 3V,$<br>$I_{OUT} = 10 \text{ mA}, V_{DD} = 16V$ | _                       | 8   | 12       |      |

| I <sub>PK</sub>  | Peak Output Current  |                                                                                                      | _                       | 1.2 | _        | А    |

| I                | Latch-Up Current     | Withstand Reverse Current                                                                            | > 500                   | _   | _        | mA   |

| Switching        | Time (Note 1)        |                                                                                                      |                         |     |          |      |

| $\overline{t_R}$ | Rise Time            | Test Figures 1 and 2                                                                                 | _                       | _   | 35       | nsec |

| t <sub>F</sub>   | Fall Time            | Test Figures 1 and 2                                                                                 | _                       | _   | 25       | nsec |

| t <sub>D1</sub>  | Delay Time           | Test Figures 1 and 2                                                                                 | _                       | _   | 75       | nsec |

| $t_{D2}$         | Delay Time           | Test Figures 1 and 2                                                                                 | _                       | _   | 75       | nsec |

| Power Sup        | oply                 |                                                                                                      |                         |     |          |      |

| Is               | Power Supply Current | $V_{IN} = 3V$ (Both Inputs)<br>$V_{IN} = 0V$ (Both Inputs)                                           | _                       | _   | 9<br>0.5 | mA   |

Note: 1. Switching times guaranteed by design.

TC1426 TC1427 TC1428

# **ELECTRICAL CHARACTERISTICS:** Over operating temperature range with $4.5V \le V_{DD} + \le 16V$ unless otherwise specified.

|                 |                        | outerwise operation.                                                      |                         |     |       |      |

|-----------------|------------------------|---------------------------------------------------------------------------|-------------------------|-----|-------|------|

| Symbol          | Parameter              | Test Conditions                                                           | Min                     | Тур | Max   | Unit |

| Input           |                        |                                                                           |                         |     |       |      |

| V <sub>IH</sub> | Logic 1, Input Voltage |                                                                           | 3                       |     | _     | V    |

| V <sub>IL</sub> | Logic 0, Input Voltage |                                                                           | _                       | _   | 0.8   | V    |

| I <sub>IN</sub> | Input Current          | $0V \le V_{IN} \le V_{DD}$                                                | - 10                    | _   | 10    | μΑ   |

| Output          |                        |                                                                           | •                       |     |       |      |

| V <sub>OH</sub> | High Output Voltage    | Test Figures 1 and 2                                                      | V <sub>DD</sub> – 0.025 | _   | _     | V    |

| V <sub>OL</sub> | Low Output Voltage     | Test Figures 1 and 2                                                      | _                       | _   | 0.025 | V    |

| R <sub>O</sub>  | Output Resistance      | V <sub>IN</sub> = 0.8V,<br>I <sub>OUT</sub> = 10mA, V <sub>DD</sub> = 16V | _                       | 15  | 23    | Ω    |

|                 |                        | $V_{IN} = 3V$ ,<br>$I_{OUT} = 10$ mA, $V_{DD} = 16V$                      | _                       | 10  | 18    |      |

| I               | Latch-Up Current       | Withstand Reverse Current                                                 | > 500                   | _   | _     | mA   |

| Switching       | Time (Note 1)          |                                                                           |                         |     |       |      |

| t <sub>R</sub>  | Rise Time              | Test Figures 1 and 2                                                      | _                       | _   | 60    | nsec |

| t <sub>F</sub>  | Fall Time              | Test Figures 1 and 2                                                      | _                       | _   | 40    | nsec |

| t <sub>D1</sub> | Delay Time             | Test Figures 1 and 2                                                      | _                       | _   | 125   | nsec |

| $t_{D2}$        | Delay Time             | Test Figures 1 and 2                                                      | _                       | _   | 125   | nsec |

| Power Sup       | pply                   |                                                                           | -                       |     | 1     |      |

| Is              | Power Supply Current   | V <sub>IN</sub> = 3V (Both Inputs)                                        | _                       | _   | 13    | mA   |

|                 |                        | V <sub>IN</sub> = 0V (Both Inputs)                                        | _                       | _   | 0.7   |      |

Note: 1. Switching times guaranteed by design.

#### SUPPLY BYPASSING

Large currents are required to charge and discharge capacitive loads quickly. For example, charging a 1000-pF load to 16V in 25nsec requires an 0.8A current from the device power supply.

To guarantee low supply impedance over a wide frequency range, a parallel capacitor combination is recommended for supply bypassing. Low-inductance ceramic MLC capacitors with short lead lengths (< 0.5-in.) should be used. A 1.0- $\mu F$  film capacitor in parallel with one or two 0.1- $\mu F$  ceramic MLC capacitors normally provides adequate bypassing.

#### **GROUNDING**

The TC1426 and TC1428 contain inverting drivers. Individual ground returns for the input and output circuits or a ground plane should be used. This will reduce negative feedback that causes degradation in switching speed characteristics.

### **INPUT STAGE**

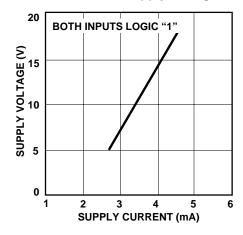

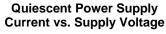

The input voltage level changes the no-load or quiescent supply current. The N-channel MOSFET input stage transistor drives a 2.5 mA current source load. With a logic "1" input, the maximum quiescent supply current is 9mA. Logic "0" input level signals reduce quiescent current to 500  $\mu$ A maximum. **Unused driver inputs must be connected to V**DD **or GND**. Minimum power dissipation occurs for logic "0" inputs for the TC1426/27/28.

The drivers are designed with 100 mV of hysteresis. This provides clean transitions and minimizes output stage current spiking when changing states. Input voltage thresholds are approximately 1.5V, making logic "1" input any voltage greater than 1.5V up to  $V_{DD}$ . Input current is less than  $1\mu A$  over this range.

The TC1426/27/28 may be directly driven by the TL494, SG1526/27, TC38C42, TC170 and similar switch-mode power supply integrated circuits.

TC1426 TC1427 TC1428

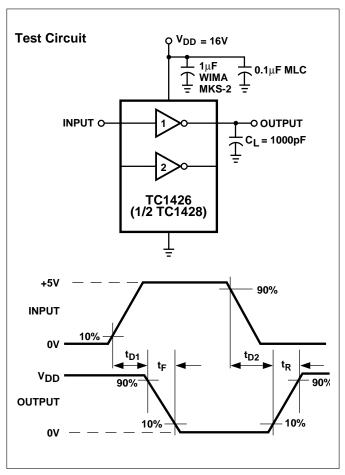

Figure 1. Inverting Driver Switching Time

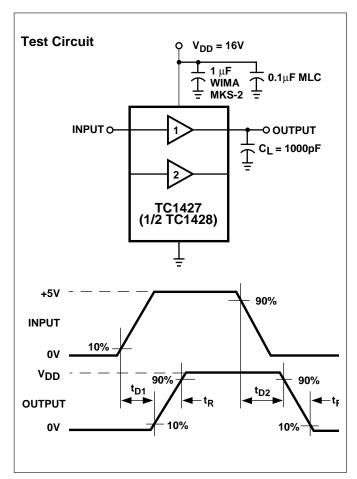

Figure 2. Non-Inverting Driver Switching Time

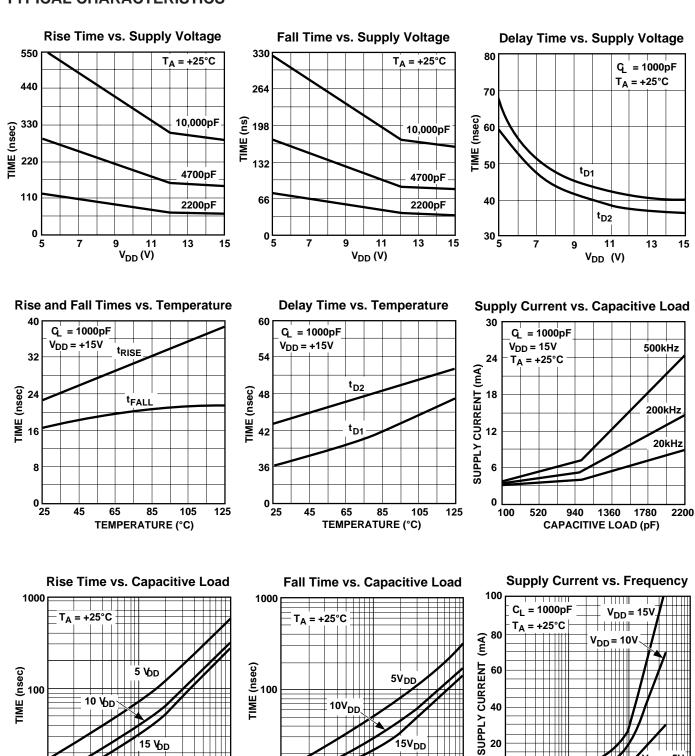

#### TYPICAL CHARACTERISTICS

15V<sub>DD</sub>

**CAPACITIVE LOAD (pF)**

10,000

10

1000

**CAPACITIVE LOAD (pF)**

15 V<sub>D</sub>

10

100

10,000

++++++

FREQUENCY (kHz)

10,000

TC1426 TC1427 TC1428

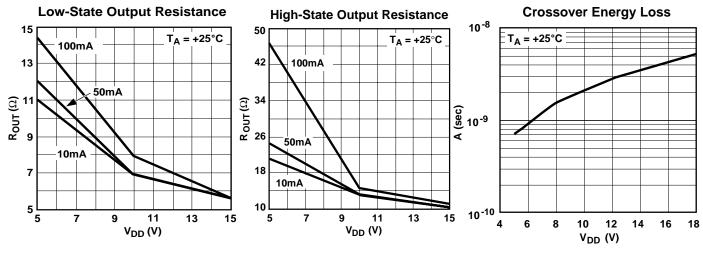

## TYPICAL CHARACTERISTIC (Cont.)

# **Quiescent Power Supply Current vs. Supply Voltage**