## AVPro<sup>®</sup> 5001 Quad A/V Drivers

# **Advanced Information**

September 1999

### **DESCRIPTION**

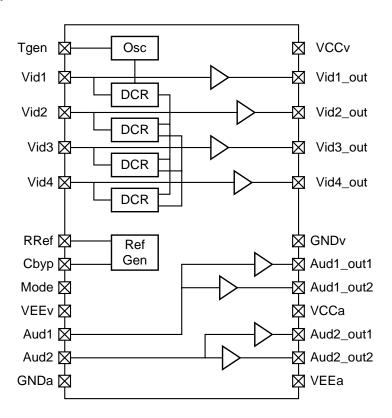

The AVPro 5001 device is an audio/video driver IC that supports four video inputs and two audio inputs. Each video paths has a gain of 2 with output buffers designed to drive a 137 ohm load. Each audio path has two output drivers that are buffered to provide 2 Vrms output (3.2 Vrms maximum). In addition, the audio drivers use +/- 5 volt power supplies so that the output is centered around ground. This allows direct coupling of the 5001 audio outputs to the associated load. Typical applications for the 5001 include DVD players, VCRs, and digital receivers for satellite, cable, and terrestrial television.

#### **FEATURES**

- · Video section

- Internal DC restore circuits

- 150 ohm drivers

- · Audio section

- better than 90 dB SNR+distortion

- direct coupled outputs

- +5V and -5V power supplies

- 24-lead small outline (SO) package

#### **BLOCK DIAGRAM**

### AVPro<sup>®</sup> 5001 Quad A/V Drivers

#### **VIDEO DESCRIPTION**

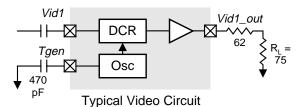

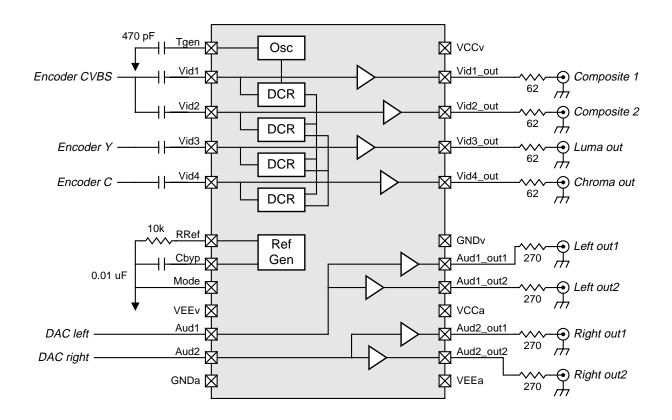

The 5001 video section provides inputs for four video signals which are typically AC coupled into the device. The pin labeled MODE is used to select the type of video inputs that are supported. When the MODE pin is connected to ground, the device is configured to support luma (Y), chroma (C), and two composite signals. In this mode, the Vid1, Vid2, and Vid3 paths each have an active DC restore circuit. The DC restore circuit triggers on the falling edge of the incoming video sync pulse and then tries to force the blank level to a fixed DC value. The trigger from the Vid1 path is also passed along to the Vid2 and Vid3 paths to insure that the DC restore circuits are triggered. The Vid4 path is used for a chroma signal. This path is set to a fixed DC level of 0.89V.

When the MODE pin is left open, the device is configured to support RGB signals and a composite signal. In this mode, all video paths have active DC restore circuits. The Vid1 path provides a master trigger to the other three DC restore circuits. This accommodates an application where the video sync for the RGB signals is provided by the composite signal. The Vid2 path also provides a trigger for the Vid3 and Vid4 pins. This supports applications where the sync signal is embedded in one of the RGB signals (sync on green). For this application, the video source that contains the sync pulse must be applied to Vid2. An internal timing circuit is used to allow the DC restore circuit to initially acquire the correct DC level. The timing circuit requires that a 470 pF capacitor be connected between the Tgen pin and around.

The output amplifiers are designed to provide a gain of approximately two (2) so that a 137 ohm load can be driven. The output impedance of each video driver is nominally 12 ohm. An external 62 ohm resistor is placed in series with the output to provide a nominal 75 ohm output impedance to the system.

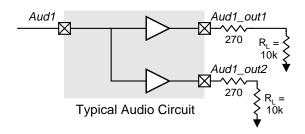

#### **AUDIO DESCRIPTION**

The 5001 audio section provides inputs for two audio signals, typically left and right channels of a stereo audio source. In many applications, the audio inputs are generated by an external DAC.

The impedance of the 5001 audio input is approximately 40k ohms. Each input has two independently buffered outputs. Each buffer can output a signal of 2 Vpp. The audio buffers use +5V and -5V power supplies which allow the DC level of the output to be 0 Vdc. For most applications, this allows the inputs and outputs of the 5001 to be direct coupled to the source and load. A resistor in series with the load is suggested to provide over-current protection.

#### **Reference Generator**

The 5001 generates internal reference currents based on an external 10.0k ohm, 1% resistor connected between the *RRef* pin and analog ground. The reference generator also uses a 0.01 uF capacitor connected between the Cbyp pin and analog ground for filtering purposes.

### PIN DESCRIPTIONS (Pins marked N/C should be left unconnected during normal use)

| NAME       | TYPE     | DESCRIPTION                                                                                                                                                                             |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O Pins:  | J        | ,                                                                                                                                                                                       |

| Aud_1      | I        | Audio input 1: This pin accepts an audio signal that can be either direct coupled or AC-coupled. This pin is typically connected to one channel of a stereo audio source.               |

| Aud_2      | I        | Audio input 2: This pin accepts an audio signal that can be either direct coupled or AC-coupled. This pin is typically connected to the other channel of a stereo audio source.         |

| Vid_1      | I        | Video input 1: This pin accepts an AC-coupled video signal. In a typical system, this pin will be connected to a composite (CVBS) signal source.                                        |

| Vid_2      | I        | Video input 2: This pin accepts an AC-coupled video signal. In a typical system, this pin will be connected to a composite (CVBS) source or a green signal source (RGB).                |

| Vid_3      | I        | Video input 3: This pin accepts an AC-coupled video signal. In a typical system, this pin will be connected to a luma signal source or a blue signal source (RGB).                      |

| Vid_4      | I        | Video input 4: This pin accepts an AC-coupled video signal. In a typical system, this pin will be connected to a chroma signal source or a red signal source (RGB).                     |

| Aud1_out1  | 0        | Audio 1 output 1: This pin is the primary output for the Aud_1 input channel.                                                                                                           |

| Aud1_out2  | 0        | Audio 1 output 2: This pin is the secondary output for the <i>Aud_1</i> input channel.                                                                                                  |

| Aud2_out1  | 0        | Audio 2 output 1: This pin is the primary output for the Aud_2 input channel.                                                                                                           |

| Aud2_out2  | 0        | Audio 2 output 2: This pin is the secondary output for the Aud_2 input channel.                                                                                                         |

| Mode       | I        | Mode select: This pin selects the video mode. When left open, the device is in the RGB mode. When connected to ground, the device is in the CVBS/S-video mode.                          |

| Vid1_out   | 0        | Video 1 output: This pin is the buffered output of the <i>Vid_1</i> input pin with a gain of 2. For a typical 75 ohm load, an external 62 ohms should be added in series with the load. |

| Vid2_out   | 0        | Video 2 output: This pin is the buffered output of the <i>Vid_2</i> input pin with a gain of 2. For a typical 75 ohm load, an external 62 ohms should be added in series with the load. |

| Vid3_out   | 0        | Video 3 output: This pin is the buffered output of the <i>Vid_3</i> input pin with a gain of 2. For a typical 75 ohm load, an external 62 ohms should be added in series with the load. |

| Vid4_out   | 0        | Video 4 output: This pin is the buffered output of the <i>Vid_4</i> input pin with a gain of 2. For a typical 75 ohm load, an external 62 ohms should be added in series with the load. |

| Power/Grou | nd Pins: |                                                                                                                                                                                         |

| VCCa,v     | -        | +5 VDC power inputs. VCCa is the audio supply, VCCv is the video supply.                                                                                                                |

| VEEa,v     | -        | -5 VDC power inputs. VEEa is the audio supply, VEEv is the video supply.                                                                                                                |

| Cbyp       | -        | Internal current reference bypass pin. Add capacitor 0.01 uF to ground.                                                                                                                 |

| GNDa,v     | -        | Ground for all blocks. GNDa is the audio supply, GNDv is the video supply.                                                                                                              |

| RRef       | -        | Bias point of internal current generator. Add resistor 10.0k to ground.                                                                                                                 |

| Tgen       | -        | Reference point for internal timing circuit. Add capacitor 470 pF to ground.                                                                                                            |

#### **ABSOLUTE MAXIMUM RATINGS**

Operation beyond the maximum ratings may damage the device

| PARAMETER                         | RATING               | UNIT |

|-----------------------------------|----------------------|------|

| Storage temperature               | -55 to 150           | °C   |

| Junction operating temperature    | +150                 | °C   |

| Positive supply voltages          | Gnd > 0.3; VCC < 6V  | V    |

| Negative supply voltages          | -6 < VEE < -0.3      | V    |

| Voltage applied to Digital Inputs | Gnd -0.3V to VCC+0.3 | V    |

| audio/video input pins            | VEE -0.3V to VCC+0.3 | V    |

**TARGET SPECIFICATIONS**: Unless otherwise specified:  $0^{\circ}$  < Ta < 70  $^{\circ}$ C; power supplies VCC = +5.0 V ±5%, VEE = -5.0 V ±5%.

### **Operating Characteristics**

| PARAMETER         | CONDITION                                     | MIN | NOM | MAX | UNIT |

|-------------------|-----------------------------------------------|-----|-----|-----|------|

| Power dissipation | All outputs loaded                            |     | 350 |     | mW   |

| PSRR              | f <sub>in</sub> = 100 Hz, 0.3 Vpp on VCC/ VEE | 40  |     |     | dB   |

**Video Characteristics -** Unless otherwise noted, typical output loading on all video outputs is  $137\Omega$ . All video outputs are capable of withstanding a sustained 75 ohm load to ground without damage.

| Input impedance                     | All video inputs                         | 100  |      |      | kΩ   |

|-------------------------------------|------------------------------------------|------|------|------|------|

| Input dynamic range                 | f <sub>in</sub> = 100 kHz, THD < 1.0%    |      | 1.5  |      | Vpp  |

| Gain                                | 1.0 Vpp input, f <sub>in</sub> = 100 kHz | 1.85 | 1.95 | 2.05 | V/V  |

| Output gain inequality              | channel to channel                       | -2.0 |      | 2.0  | %    |

| Output DC level                     |                                          |      | 1.0  |      | V    |

| Blank level clamp voltage           | RGB, CVBS or luma input                  |      | 0.55 |      | V    |

| DC level                            | chroma input                             |      | 0.89 |      | V    |

| Signal to noise ratio               | 1 Vpp input                              | 58   | 65   |      | dB   |

| Cross talk                          | f <sub>in</sub> = 4.43 MHz, 1 Vpp        |      | -55  |      | dB   |

| Output to output differential delay | f <sub>in</sub> = 100 kHz                | -20  |      | 20   | nsec |

| Differential phase                  | CVBS input                               |      |      | 2.0  | Deg. |

| Differential gain                   | CVBS input                               |      |      | 2.5  | %    |

**Audio Characteristics -** Unless otherwise noted, all audio outputs shall drive a load of 10 k $\Omega$ . All audio outputs will withstand a sustained short to ground without damage.

| PARAMETER             | CONDITION                            | MIN  | NOM | MAX  | UNIT |

|-----------------------|--------------------------------------|------|-----|------|------|

| Input impedance       |                                      |      | 40  |      | kΩ   |

| Gain                  | f <sub>in</sub> = 1.0 kHz, 0.5 Vrms  | 0.95 | 1.0 | 1.05 | V/V  |

| Frequency response    | 0.5 Vrms input, Flat within ± 0.3 dB | 20   |     |      | kHz  |

|                       | Measured -3 dB point                 | 100  |     |      | kHz  |

| Dynamic range         | f <sub>in</sub> = 1.0 kHz            | 90   | 100 |      | dB   |

| Signal to Noise ratio | f <sub>in</sub> = 1.0 kHz, 0.5 Vrms  | 90   | 100 |      | dB   |

| Distortion (THD)      | f <sub>in</sub> = 1.0 kHz, 0.5 Vrms  |      |     | 0.01 | %    |

|                       | f <sub>in</sub> = 1.0 kHz, 2 Vrms    |      |     | TBD  | %    |

| Output impedance      |                                      |      | TBD |      | Ω    |

| Output DC Offset      | Input to Output                      |      |     | 30   | mV   |

| Output phase matching | f <sub>in</sub> = 1.0 kHz, 0.5 Vrms  |      | 0.5 |      | Deg. |

| Channel separation    | f <sub>in</sub> = 1.0 kHz, 0.5 Vrms  | 90   |     |      | dB   |

**AVPro 5001: Typical Application Diagram**

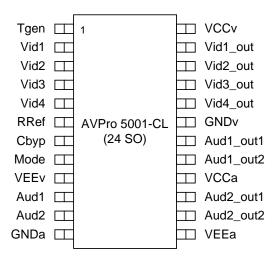

#### **PACKAGE PIN DESIGNATION**

(Top View)

AVPRO® 5001 (SOL)

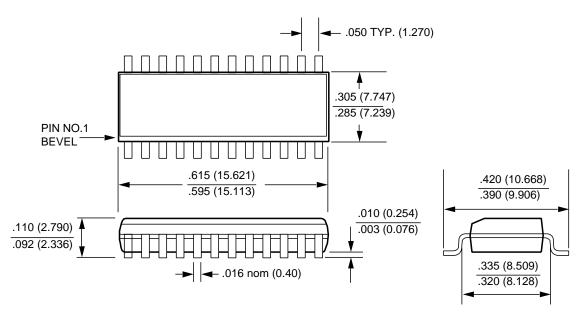

#### **MECHANICAL DRAWING**

### 24-Lead Small Outline (SOL)

Note: Controlling dimensions are in mm.

## AVPro<sup>®</sup> 5001 Quad A/V Drivers

### **ORDERING INFORMATION**

| PART DESCRIPTION                         | ORDER NO.       | PACKAGE MARK   |  |  |

|------------------------------------------|-----------------|----------------|--|--|

| AVPro <sup>®</sup> 5001 Quad A/V Drivers | Consult factory | AVPro® 5001-CL |  |  |

**Advanced Information:** The Advanced Information data sheet is to be approved for Beta Site and advanced customer information purposes only. It is not intended to replace the electrical specification for the specific device it represents. This document will be updated and converted into a Final (Preliminary Data Sheet) upon completion of Design Engineering Validation. Design Engineering should review this documentation for its accuracy to the definition and the design goals for the product it represents.

No responsibility is assumed by TDK Semiconductor Corporation for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of TDK Semiconductor Corporation and the company reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that you are referencing the most current data sheet before placing orders. To do so, see our web site at http://www.tsc.tdk.com or contact your local TDK Semiconductor representative.

TDK Semiconductor Corp., 2642 Michelle Dr., Tustin, CA 92780, (714) 508-8800, FAX (714) 508-8877, http://www.tsc.tdk.com