**DGG PACKAGE**

(TOP VIEW)

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

- 9 Channels for the Data and Control Paths of the Small Computer Systems Interface (SCSI)

- Supports Single-Ended and Low-Voltage Differential (LVD) SCSI

- CMOS Input Levels ('LVDM976) or TTL Input Levels ('LVDM977) Available

- Includes DIFFSENS Comparators on CDE0

- Single-Ended Receivers Include Noise Pulse Rejection Circuitry

- Packaged in Thin Shrink Small-Outline Package With 20-Mil Terminal Pitch

- Low Disabled Supply Current 7 mA Maximum

- Power-Up/Down Glitch Protection

- Bus is High-Impedance With V<sub>CC</sub> = 1.5 V

- Pin-Compatible With the SN75976ADGG High-Voltage Differential Transceiver

### description

The SN75LVDM976 and SN75LVDM977 have nine transceivers for transmitting or receiving the signals to or from a SCSI data bus. They offer electrical compatibility to both the single-ended signaling of X3.277:1996–SCSI–3 Parallel Interface (Fast–20) and the new low-voltage differential signaling method of proposed standard 1142–D SCSI Parallel Interface – 2 (SPI–2).

The differential drivers are nonsymmetrical. The SCSI bus uses a dc bias on the line to allow

INV/NON 56 CDE2 55 CDE1 GND [ 2 GND ¶ 54 CDE0 3 53 1 9B+ 1A 1DE/RE **1** 5 52 1 9B-51 8B+ 2А П 2DE/RE 50 ¶ 8B-7 ЗА ∏ 7B+ 8 49 3DE/RE 9 48**∏** 7B− 47**∏** 6B+ 4A 10 4DE/RE □ 46 **1** 6B− 11 V<sub>CC</sub> [] 12 45 VCC GND **1** 13 44 GND GND [ 43 GND 14 GND [ 15 42 | GND GND [ 16 41 | GND 40 ] GND GND [ 17 18 39 **∏** V<sub>CC</sub> Vcc [ 19 38 1 5B+ 5A 37 1 5B-6A 21 36**∏** 4B+ 6DE/RE 22 35 **1** 4B-23 34 1 3B+ 7A 24 33 3B-7DE/RE 8A 25 32 1 2B+ 8DE/RE 26 31 1 2B-27 30**∏** 1B+ 9A 29**∏** 1B− 28 9DE/RE

terminated fail safe and wired-OR signaling. This bias can be as high as 125 mV and induces a difference in the high-to-low and low-to-high transition times of a symmetrical driver. In order to reduce pulse skew, an LVD SCSI driver's output characteristics become nonsymmetrical. In other words, there is more assertion current than negation current to or from the driver. This allows the actual differential signal voltage on the bus to be symmetrical about 0 V. Even though the driver output characteristics are nonsymmetrical, the design of the 'LVDM976 drivers maintains balanced signaling. Balanced means that the current that flows in each signal line is nearly equal but opposite in direction and is one of the keys to the low-noise performance of a differential bus.

#### **AVAILABLE OPTIONS**

|             | PACKAGE                                        |                                                |  |  |

|-------------|------------------------------------------------|------------------------------------------------|--|--|

| TA          | TSSOP<br>(DGG)<br>CMOS INPUT LEVELS            | TSSOP<br>(DGG)<br>TTL INPUTS LEVELS            |  |  |

| 0°C to 70°C | SN75LVDM976DGG<br>SN75LVDM976DGGR <sup>†</sup> | SN75LVDM977DGG<br>SN75LVDM977DGGR <sup>†</sup> |  |  |

<sup>†</sup>The R suffix designates a taped and reeled package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

### description (continued)

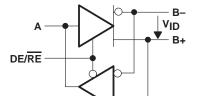

The signal symmetry requirements of the LVD-SCSI bus mean you can no longer obtain logical inversion of a signal by simply reversing the differential signal connections. This requires the ability to invert the logic convention through the INV/NON terminal. This input would be a low for SCSI controllers with active-high data and high for active-low data. In either case, the B+ signals of the transceiver must be connected to the SIGNAL+ line of the SCSI bus and the B- of the transceiver to the SIGNAL- line.

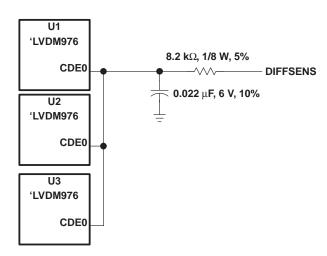

The CDE0 input incorporates a window comparator to detect the status of the DIFFSENS line of a SCSI bus. This line is below 0.5 V, if using single-ended signals, between 1.7 V and 1.9 V if low-voltage differential, and between 2.4 V and 5.5 V if high-voltage differential. The outputs assume the characteristics of single-ended or LVD accordingly or place the outputs into high-impedance, when HVD is detected. This, and the INV/NON input, are the only differences to the trade-standard function of the SN75976A HVD transceiver.

Two options are offered to minimize the signal noise margins on the interface between the communications controller and the transceiver. The SN75LVDM976 has logic input voltage thresholds of about 0.5  $V_{CC}$ . The SN75LVDM977 has a fixed logic input voltage threshold of about 1.5 V. The input voltage threshold should be selected to be near the middle of the output voltage swing of the corresponding driver circuit.

The SN75LVDM976 and SN75LVDM977 are characterized for operation over an free-air temperature range of  $T_A = 0$ °C to 70°C.

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

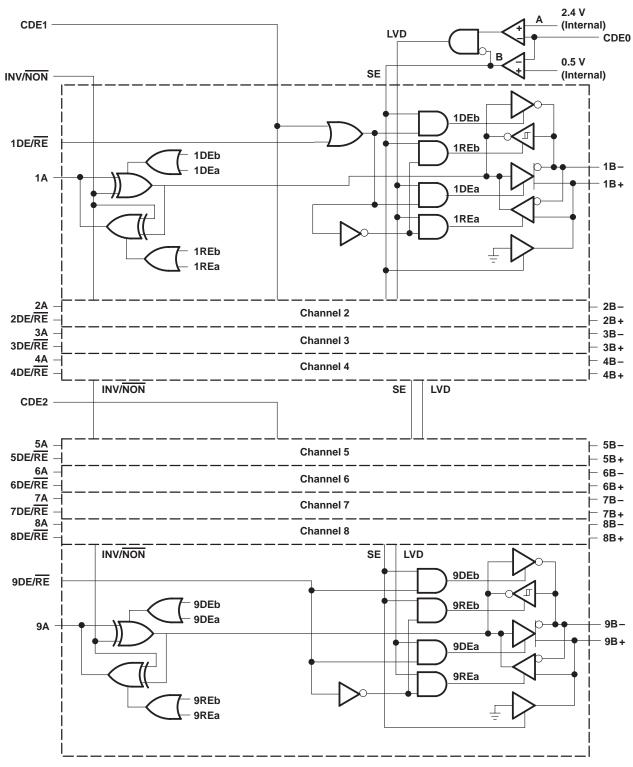

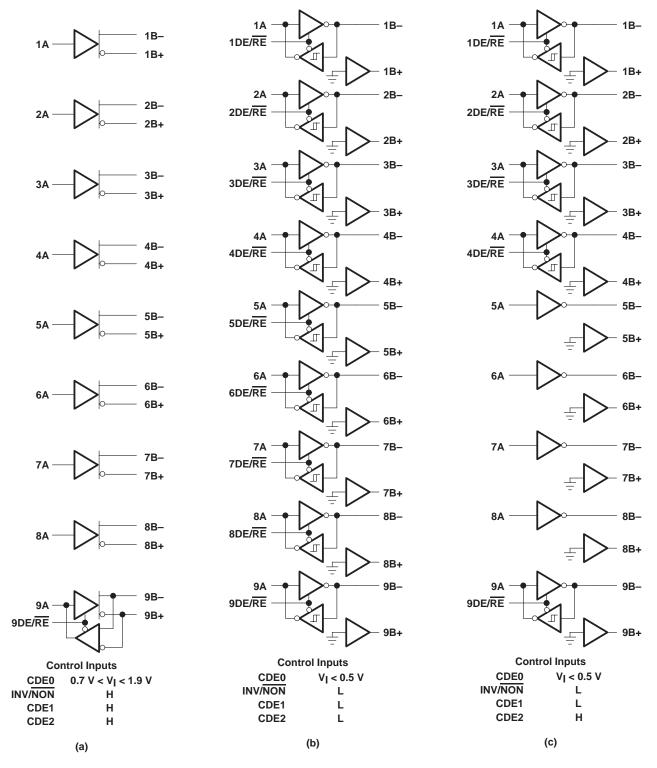

# logic diagram (positive logic)

## logic diagrams and function tables

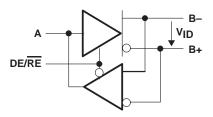

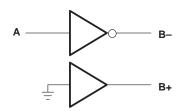

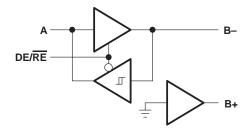

Figure 1. Inverting LVD Transceiver

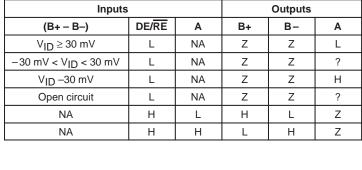

**FUNCTION TABLE**

Figure 2. Inverting Single-Ended Transceiver

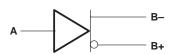

Figure 3. Inverting Single-Ended Driver

Figure 4. Inverting LVD Driver

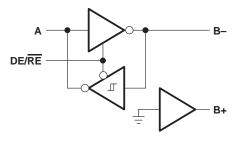

#### **FUNCTION TABLE**

| Inputs       |       |    |    | Outputs |   |

|--------------|-------|----|----|---------|---|

| B-           | DE/RE | Α  | B+ | B-      | Α |

| Н            | L     | NA | L  | Z       | L |

| L            | L     | NA | L  | Z       | Н |

| Open circuit | L     | NA | L  | Z       | ? |

| NA           | Н     | L  | L  | Н       | Z |

| NA           | Н     | Н  | L  | L       | Z |

### **FUNCTION TABLE**

| Input | Outputs |   |  |  |  |

|-------|---------|---|--|--|--|

| Α     | B+ B-   |   |  |  |  |

| L     | L       | Н |  |  |  |

| Н     | L       | L |  |  |  |

### **FUNCTION TABLE**

| Input | Outputs |   |  |  |

|-------|---------|---|--|--|

| Α     | B+ B-   |   |  |  |

| L     | Н       | L |  |  |

| Н     | L       | Н |  |  |

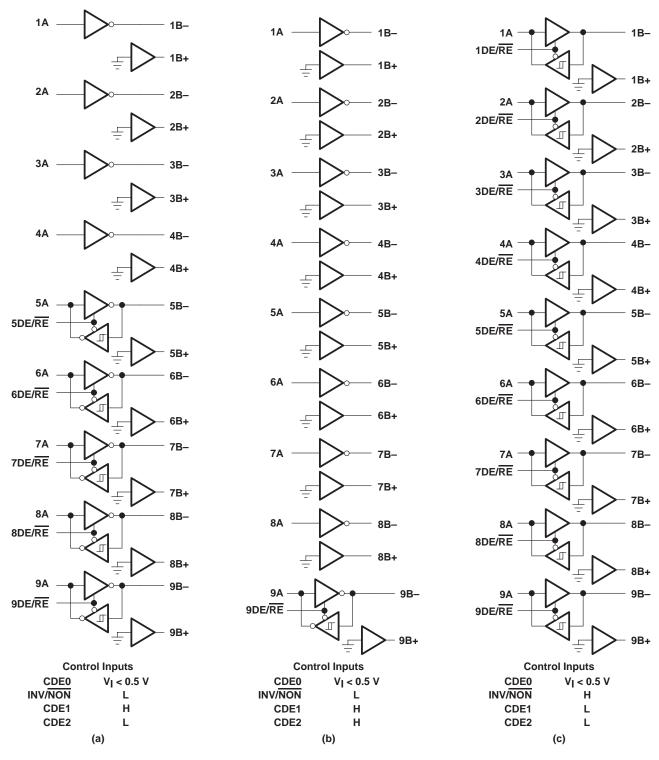

# logic diagrams and function tables (continued)

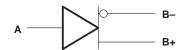

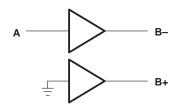

Figure 5. Noninverting LVD Driver

### **FUNCTION TABLE**

| Input | Outputs |   |  |  |

|-------|---------|---|--|--|

| Α     | B+ B-   |   |  |  |

| L     | L       | Н |  |  |

| Н     | Н       | L |  |  |

Figure 6. Noninverting LVD Transceiver

### **FUNCTION TABLE**

| Inputs                                                  |       |    |    | Outputs |   |

|---------------------------------------------------------|-------|----|----|---------|---|

| (B+ - B-)                                               | DE/RE | Α  | B+ | B-      | Α |

| $V_{ID} \ge 30 \text{ mV}$                              | L     | NA | Z  | Z       | Н |

| $-30 \text{ mV} < \text{V}_{\text{ID}} < 30 \text{ mV}$ | L     | NA | Z  | Z       | ? |

| V <sub>ID</sub> ≤ -30 mV                                | L     | NA | Z  | Z       | L |

| Open circuit                                            | L     | NA | Z  | Z       | ? |

| NA                                                      | Н     | L  | L  | Н       | Z |

| NA                                                      | Н     | Н  | Н  | Ĺ       | Z |

Figure 7. Noninverting Single-Ended Transceiver

# FUNCTION TABLE Inputs

| Inputs       |   |    | (  | Outputs | ; |

|--------------|---|----|----|---------|---|

| B-           | Α | B+ | B- | Α       |   |

| Н            | L | NA | L  | Z       | Н |

| L            | L | NA | L  | Z       | L |

| Open Circuit | L | NA | L  | Z       | ? |

| NA           | Н | L  | L  | L       | Z |

| NA           | Н | Н  | L  | Н       | Z |

Figure 8. Noninverting Single-Ended Driver

### **FUNCTION TABLE**

| Input | Outputs |   |  |  |

|-------|---------|---|--|--|

| Α     | B+ B-   |   |  |  |

| L     | L       | L |  |  |

| Н     | L       | Н |  |  |

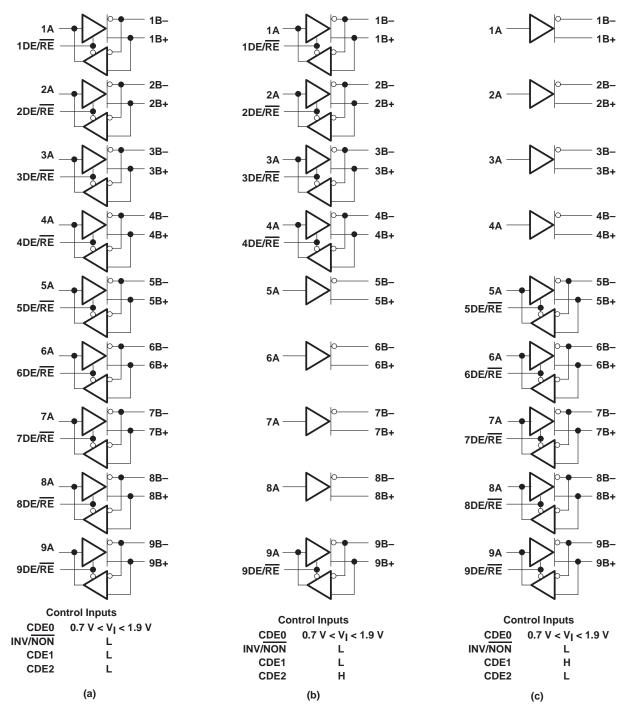

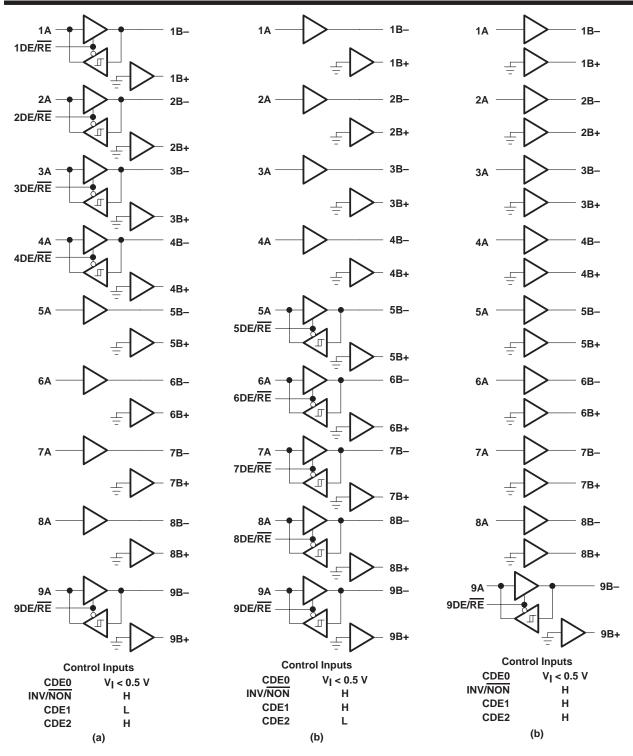

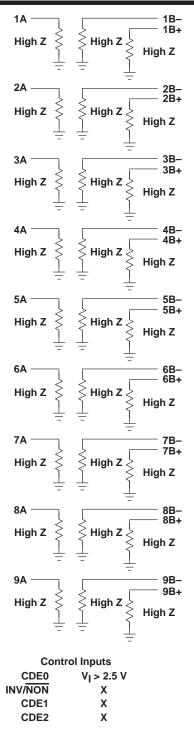

Figure 9. Logic Diagrams

Figure 10. Logic Diagrams

Figure 11. Logic Diagrams

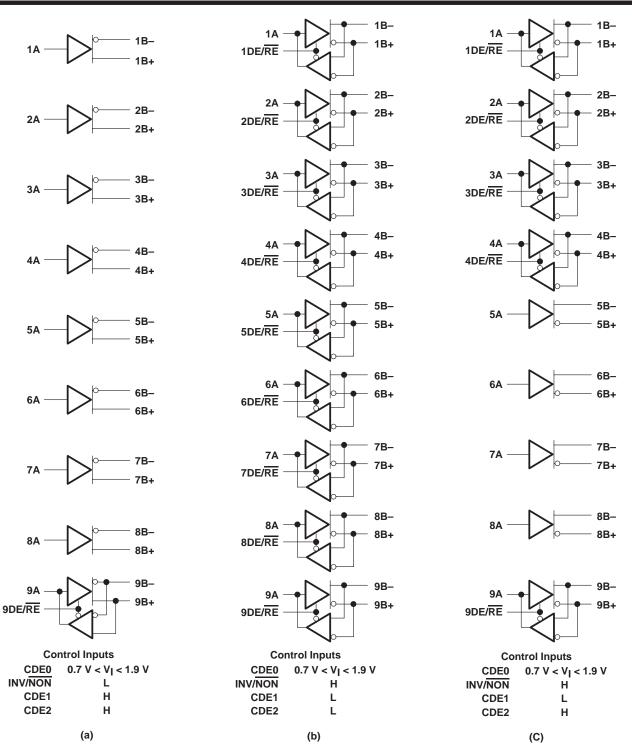

Figure 12. Logic Diagrams

Figure 13. Logic Diagrams

Figure 14. Logic Diagrams

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

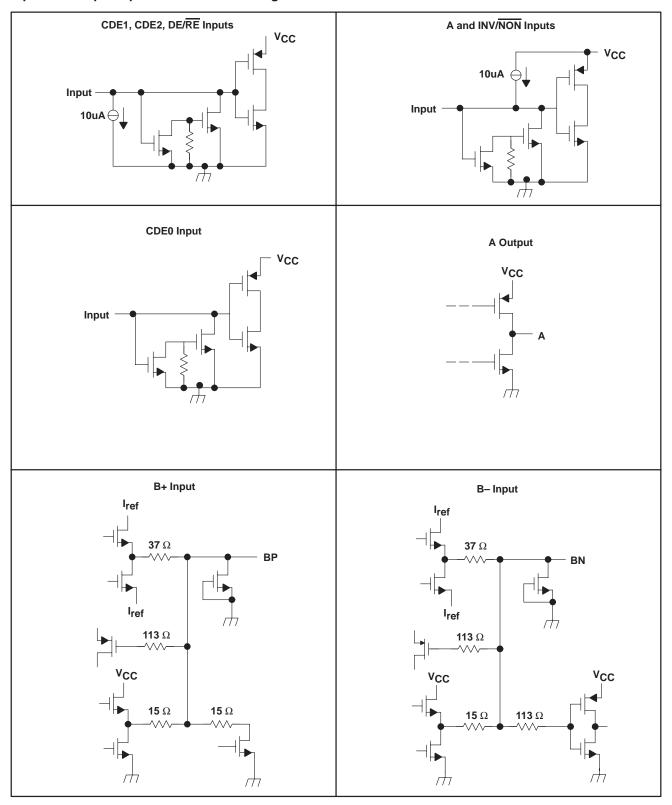

# input and output equivalent schematic diagrams

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

## **Terminal Functions**

| TERM                             | IINAL                                         | LVDM976        | LVDM977        |       |             |                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------|-----------------------------------------------|----------------|----------------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                             | NO.                                           | Logic<br>Level | Logic<br>Level | I/O   | Termination | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                   |

| 1A – 9A                          | 4,6,8,10,<br>19,21,23,<br>25,27               | CMOS           | TTL            | I/O   | Pullup      | 1A – 9A carry data to and from the communication controller.                                                                                                                                                                                                                                                                                                                                  |

| 1B <sup>-</sup> -9B <sup>-</sup> | 29,31,33,<br>35,37,46,<br>48,50,52            | LVD or<br>TTL  | LVD or<br>TTL  | I/O   | None        | 1B – to 9B – are the signals to and from the data bus. When $INV/\overline{NON}$ is low, the logic <u>sense</u> is the opposite that of the A input (inverted). When $INV/\overline{NON}$ is high, the logic sense is the same as the A input (noninverted).                                                                                                                                  |

| 1B+ - 9B+                        | 30,32,34,<br>36,38,47,<br>49,51,53            | LVD or<br>GND  | LVD or<br>GND  | I/O   | None        | When in the LVD mode, $1B+-9B+$ are signals to or from the data bus and follow the same logic sense as the A input when INV/ $\overline{\text{NON}}$ is low (noninverted). The logic sense is opposite that of the A input (inverted) when $\overline{\text{INV/NON}}$ is high. When in single-ended mode, these terminals become a ground connection through a transistor and do not switch. |

| CDE0                             | 54                                            | Trinary        | Trinary        | Input | None        | CDE0 is the common driver enable 0. With the driver enabled and the CDE0 input less than 0.5 V, the driver output is single-ended mode. With the driver enabled and the CDE0 input between 0.7 V and 1.9 V the driver output is LVD mode. All drivers are disabled when the input is greater than 2.4 V.                                                                                      |

| CDE1                             | 55                                            | CMOS           | TTL            | Input | Pulldown    | CDE1 is the common driver enable 1. When CDE1 is high, drivers 1 – 4 are enabled                                                                                                                                                                                                                                                                                                              |

| CDE2                             | 56                                            | CMOS           | TTL            | Input | Pulldown    | CDE2 is the common driver enable 2. When CDE2 is high, drivers 5 to 8 are enabled.                                                                                                                                                                                                                                                                                                            |

| 1DE/RE –<br>9DE/RE               | 5,7,9,11,<br>20,22,24,<br>26,28               | CMOS           | TTL            | Input | Pulldown    | 1DE/RE – 9DE/RE are direction controls that transmit data to the bus when it is high and CDE0 is below 2.2 V. Data is received from the bus when 1DE/RE – 9DE/RE, CDE1, and CDE2 are low.                                                                                                                                                                                                     |

| GND                              | 2,3,13,14,<br>15,16,17,<br>40,41,42,<br>43,44 | NA             | NA             | Power | NA          | GND is the circuit ground.                                                                                                                                                                                                                                                                                                                                                                    |

| INV/NON                          | 1                                             | CMOS           | CMOS           | Input | Pullup      | A high-level input to INV/NON inverts the logic to and from the A terminals. (i.e., the voltage at A terminal and the corresponding B – terminal are in phase.)                                                                                                                                                                                                                               |

| VCC                              | 12,18,39,<br>45                               | NA             | NA             | Power | NA          | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                |

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)           | 0.5 V to 7 \                               |

|--------------------------------------------------------------|--------------------------------------------|

| Input voltage range, V <sub>I</sub> (A, INV/NON)             | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| (DE/RE, B+, B-, CDE0, CDE1, CDE2)                            | 0.5 V to 5.25 \                            |

| Continuous total power dissipation                           | See Dissipation Rating Table               |

| Storage temperature range, T <sub>stq</sub>                  | 65°C to 150°C                              |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds | 260°C                                      |

NOTE 1: All voltage values are with respect to GND unless otherwise noted.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|

| DGG     | 978 mW                                                                     | 10.8 mW/°C                                     | 492 mW                                |

## recommended operating conditions (see Figure 15)

|                                                                                                                                                                           |                       | MIN                                                                                            | NOM                                                                              | MAX                 | UNIT |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------|------|

| Supply voltage, V <sub>CC</sub>                                                                                                                                           |                       | 4.75                                                                                           | 5                                                                                | 5.25                | V    |

| High level input voltage V                                                                                                                                                | SN75LVDM976           | 0.7 V <sub>CC</sub>                                                                            |                                                                                  |                     | V    |

| High-level input voltage, VIH                                                                                                                                             | SN75LVDM977           | 4.75 5 5.29  0.7 V <sub>CC</sub> 2  0.3 V <sub>CC</sub> 0.4  0.7 1.4  -100 -129  -2  44  40 68 |                                                                                  | V                   |      |

| Low level input voltage V.                                                                                                                                                | SN75LVDM976           |                                                                                                |                                                                                  | 0.3 V <sub>CC</sub> | V    |

| igh-level input voltage, V <sub>IH</sub> ow-level input voltage, V <sub>IL</sub> ifferential input voltage,  V <sub>ID</sub>    ommon-mode input voltage, V <sub>IC</sub> | SN75LVDM977           |                                                                                                | 0.8                                                                              |                     | 1 '  |

| Differential input voltage,  V <sub>ID</sub>                                                                                                                              | Differential receiver | 0.03                                                                                           |                                                                                  | 3.6                 | V    |

| Common-mode input voltage, V <sub>IC</sub>                                                                                                                                |                       | 0.7                                                                                            |                                                                                  | 1.8                 | V    |

| Differential output voltage bias, V <sub>OD(bias)</sub>                                                                                                                   | Differential          | -100                                                                                           |                                                                                  | -125                | mV   |

| High level entert engage                                                                                                                                                  | Single-ended driver   |                                                                                                |                                                                                  |                     |      |

| High-level output current, IOH                                                                                                                                            | Receiver              |                                                                                                | 4.75 5 5.2  0.7 V <sub>CC</sub> 2  0.3 V <sub>C</sub> 0  0.03 3  0.7 1  -100 -12 | -2                  | mA   |

| Level and autorit anyment Leve                                                                                                                                            | Single-ended driver   |                                                                                                |                                                                                  |                     | A    |

| mmon-mode input voltage, V <sub>IC</sub> ferential output voltage bias, V <sub>OD</sub> (bias) gh-level output current, I <sub>OH</sub>                                   | Receiver              |                                                                                                |                                                                                  | 2                   | mA   |

| Differential load impedance, Z <sub>L</sub>                                                                                                                               | -                     | 40                                                                                             |                                                                                  | 65                  | Ω    |

| Operating free-air temperature, TA                                                                                                                                        |                       | 0                                                                                              |                                                                                  | 70                  | °C   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER |                                   | TEST CONDITIONS   |                                               | MIN     | TYP† | MAX | UNIT |    |

|-----------|-----------------------------------|-------------------|-----------------------------------------------|---------|------|-----|------|----|

| Ī         | High-level input current          | CDE1 and CDE2     |                                               |         |      |     | 50   |    |

| l'IH      | nigri-level input current         | INV/NON           |                                               |         |      |     | -50  | μΑ |

| l         | Low-level input current           | CDE1 and CDE2     |                                               |         |      |     | 50   | μΑ |

| ¹IL       | Low-level input current           | INV/NON           |                                               |         |      |     | -50  | μΑ |

|           |                                   |                   | Disabled                                      |         |      |     | 7    |    |

|           |                                   |                   | LVD drivers enabled,                          | No load |      |     | 26   |    |

| ICC       | Supply current                    |                   | Single-ended drivers enabled,                 | No load |      |     | 10   | mA |

|           |                                   |                   | LVD receivers enabled,                        | No load |      |     | 26   |    |

|           |                                   |                   | Singled-ended receivers enabled,              | No load |      |     | 7    |    |

| CI        | Input capacitance                 | Bus terminal      | $V_I = 0.2 \sin (2 \pi (1E06)t) + 0.5 \pm 0.$ | 01 V    |      | 9.5 |      | pF |

| ΔCI       | Difference in input capacitance I | oetween B+ and B- |                                               |         |      |     | 0.2  | ы  |

$<sup>\</sup>dagger$  All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

# DIFFSENS (CDE0) receiver electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER               | TEST CONDITIONS                                         | MIN | TYP | MAX | UNIT |

|----------------------|-------------------------|---------------------------------------------------------|-----|-----|-----|------|

| VIT1                 | Input threshold voltage |                                                         | 0.5 | 0.6 | 0.7 | V    |

| V <sub>IT2</sub>     | Input threshold voltage |                                                         | 1.9 | 2.1 | 2.4 | V    |

| II                   | Input current           | 0 V ≤ V <sub>I</sub> ≤ 2.7 V                            |     |     | ±1  | μΑ   |

| I <sub>I</sub> (OFF) | Power-off input current | $V_{CC} = 0,$ $0 \text{ V} \le V_{I} \le 2.7 \text{ V}$ |     |     | ±1  | μΑ   |

$<sup>\</sup>dagger$  All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

## LVD driver electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                                     |          | TEST CONDITIONS                                                            | MIN                           | TYP <sup>†</sup>                                                           | MAX                           | UNIT |      |

|-----------------------|-------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------|-------------------------------|------|------|

|                       |                                                                               |          | $V_{I(1)} = 0.96 \text{ V}, \ V_{I(2)} = 0.53 \text{ V},$                  | 270                           | 460                                                                        | 780                           |      |      |

| \/op#\                | Driver differential high-lev                                                  | el out-  | See Figure 16                                                              | 0.69 V <sub>OD(L)</sub>  + 50 | 0(L)  + 50 1.45 V <sub>OD(L)</sub>  - 6                                    |                               | mV   |      |

| VOD(H)                | ) put voltage $V_{I(1)}$                                                      |          | put voltage $V_{I(1)} = 1.96 \text{ V}, V_{I(2)} = 1.53 \text{ V},$        |                               | 270                                                                        | 500                           | 780  | IIIV |

|                       |                                                                               |          | See Figure 16                                                              | 0.69 V <sub>OD(L)</sub>  + 50 |                                                                            | 1.45 V <sub>OD(L)</sub>  - 65 |      |      |

| V =                   | Driver differential low-level output voltage                                  |          | $V_{I(1)} = 0.96 \text{ V}, \ V_{I(2)} = 0.53 \text{ V},$<br>See Figure 16 | -260                          | -400                                                                       | -640                          | mV   |      |

| VOD(L)                |                                                                               |          | voltage $ V_{I(1)} = 1.96 \text{ V}, \ V_{I(2)} = 1.53 $ See Figure 16     |                               | $V_{I(1)} = 1.96 \text{ V}, \ V_{I(2)} = 1.53 \text{ V},$<br>See Figure 16 | -260                          | -400 | -640 |

| V <sub>OC</sub> (SS)  | Steady-state common-mo                                                        | ode out- |                                                                            | 1.1                           | 1.2                                                                        | 1.5                           | V    |      |

| ΔV <sub>OC</sub> (SS) | Change in steady-state common-<br>mode output voltage between<br>logic states |          | $V_{I(1)} = 1.41 \text{ V}, \ V_{I(2)} = 0.99 \text{ V},$<br>See Figure 17 |                               | ±50                                                                        | ±120                          | mV   |      |

| V <sub>OC(PP)</sub>   | Peak-to-peak common-moutput voltage                                           | ode      |                                                                            |                               | 80                                                                         | 150                           | mV   |      |

| l                     | High lovel input ourrent                                                      | Α        | V <sub>IH</sub> = 3.3 V ('976)                                             | -7                            |                                                                            |                               |      |      |

| I'IH                  | High-level input current                                                      | DE/RE    | V <sub>IH</sub> = 2 V ('977)                                               |                               |                                                                            | 50                            | μΑ   |      |

| 1                     | Low-level input current                                                       | Α        | V <sub>IL</sub> = 1.6 V ('976)                                             |                               |                                                                            | -30                           | μА   |      |

| 'IL                   | Low-lever input current                                                       | DE/RE    | V <sub>IL</sub> = 0.8 V ('977)                                             | 8                             |                                                                            |                               | μΑ   |      |

| lo(OFF)               | Power-off output current                                                      |          | $V_{CC} = 0$ , $0 \text{ V} \le V_{O} \le 2.5 \text{ V}$                   |                               |                                                                            | ±1                            | μΑ   |      |

| los                   | Short-circuit output currer                                                   | nt       | $0 \text{ V} \leq \text{V}_{\text{O}} \leq 2.5 \text{ V}$                  |                               |                                                                            | ±24                           | mA   |      |

| loz                   | High-impedance output c                                                       | urrent   | $V_0 = 0 \text{ or } 2.5 \text{ V}$                                        |                               |                                                                            | ±1                            | μΑ   |      |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

# LVD driver switching characteristics over recommended operating conditions (unless otherwise noted) (See Figure 16)

|                  | PARAMETER                                                   | TEST COI                                           | NDITIONS               | MIN                                                     | TYP | MAX | UNIT |     |    |

|------------------|-------------------------------------------------------------|----------------------------------------------------|------------------------|---------------------------------------------------------|-----|-----|------|-----|----|

| tPLH             | Propagation delay time, low-to-high level output            |                                                    |                        | 2.9                                                     |     | 8.8 | ns   |     |    |

| <sup>t</sup> PHL | Propagation delay time, high-to-low level output            | $V_{CC} = 5 \text{ V},$ $V_{12} = 0.99 \text{ V},$ | V <sub>CC</sub> = 5 V, |                                                         |     | 2.9 |      | 8.8 | ns |

| t <sub>r</sub>   | Differential output signal rise time                        |                                                    |                        | $V_{ 1} = 1.41 \text{ V},$ $T_{A} = 25^{\circ}\text{C}$ | 1   | 3   | 6    | ns  |    |

| tf               | Differential output signal fall time                        |                                                    | 1A - 20 0              | 1                                                       | 3   | 6   | ns   |     |    |

| tsk(p)           | Pulse skew ( tpHL - tpLH )                                  |                                                    |                        |                                                         |     | 3.7 | ns   |     |    |

| tsk(lim)         | Skew limit <sup>‡</sup>                                     |                                                    |                        |                                                         |     | 5.9 | ns   |     |    |

| tPHZ             | Propagation delay time, high-level to high-impedance output | V <sub>I1</sub> = 1.41 V,                          | $V_{12} = 0.99 V$ ,    |                                                         |     | 50  | ns   |     |    |

| t <sub>en</sub>  | Enable time, receiver to driver                             | See Figure 18                                      |                        |                                                         |     | 33  | ns   |     |    |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. † t<sub>Sk(lim)</sub> is the maximum delay time difference between any two drivers on any two devices operating at the same supply voltage and the same ambient temperature.

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

### single-ended driver electrical characteristics over recommended operating conditions (unless otherwise noted)

| PARAMETER            |                               | TEST CO   | NDITIONS                        | MIN                                             | TYP | MAX | UNIT |    |

|----------------------|-------------------------------|-----------|---------------------------------|-------------------------------------------------|-----|-----|------|----|

| Vari                 | High lovel output voltage     | P output  | $I_{OH} = -7 \text{ mA},$       | See Figure 19                                   | 2   |     | 3.24 | V  |

| VOH                  | High-level output voltage     | B– output | I <sub>OH</sub> = 0 mA          |                                                 |     |     | 3.7  | V  |

|                      |                               | B- output | V <sub>CC</sub> = 5 V,          | $I_{OL} = 48 \text{ mA}$                        |     |     | 0.5  | V  |

| VOL                  | Low-level output voltage      | B+        | I <sub>OL</sub> = -25 mA        |                                                 |     |     | -0.5 | ٧  |

|                      |                               | D†        | I <sub>OL</sub> = 25 mA         |                                                 |     |     | 0.5  | V  |

| l                    | High-level input current      | А         | V <sub>IH</sub> = 3.3 V ('976), |                                                 | -7  |     |      |    |

| lιΗ                  | riigii-ievei iiiput curient   | DE/RE     | V <sub>IH</sub> = 2 V ('977)    |                                                 |     |     | 50   | μΑ |

| 1                    | Low-level input current       | А         | V <sub>IL</sub> = 1.6 V ('976), |                                                 |     |     | -30  |    |

| IIL.                 | Low-level input current       | DE/RE     | V <sub>IL</sub> = 0.8 V ('977)  |                                                 | 8   |     |      | μΑ |

| I <sub>O</sub> (OFF) | Power-off output current      | B-        | $V_{CC} = 0$ ,                  | $0~V \leq V_{\mbox{\scriptsize O}} \leq 5.25~V$ |     |     | ±1   | μΑ |

| loz                  | High-impedance output current |           | $V_O = 0$ or $V_{CC}$           |                                                 |     |     | ±1   | μΑ |

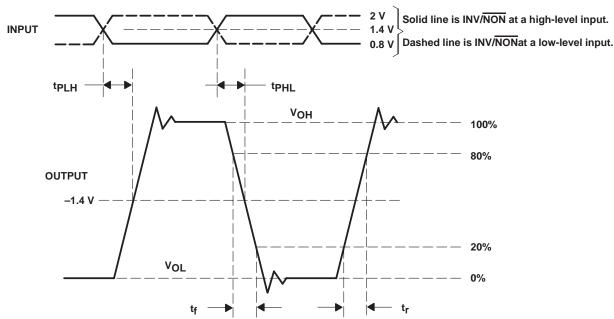

## single-ended driver switching characteristics over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                                  | TEST CONDITIONS        | MIN | TYP <sup>†</sup> | MAX | UNIT |

|--------------------|------------------------------------------------------------|------------------------|-----|------------------|-----|------|

| tPLH               | Propagation delay time, low-to-high level output           |                        | 2.7 |                  | 8.2 | ns   |

| tPHL               | Propagation delay time, high-to-low level output           | V <sub>CC</sub> = 5 V, | 2.7 |                  | 8.2 | ns   |

| t <sub>r</sub>     | Differential output signal rise time                       | $T_A = 25^{\circ}C$ ,  | 0.5 |                  | 4   | ns   |

| t <sub>f</sub>     | Differential output signal fall time                       | See Figure 19          | 0.5 |                  | 4   | ns   |

| t <sub>sk(p)</sub> | Pulse skew ( tpHL - tpLH )                                 |                        |     |                  | 3.4 | ns   |

| tsk(lim)           | Skew limit <sup>‡</sup>                                    |                        |     |                  | 5.5 | ns   |

| ten                | Enable time, receiver to driver                            | Soo Figure 20          |     |                  | 50  | ns   |

| tPLZ               | Propagation delay time, low-level to high-impedance output | See Figure 20          |     |                  | 30  | ns   |

### LVD receiver electrical characteristics over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                           | TEST CONDITIONS                                                   | MIN | TYP | MAX | UNIT |

|----------------------|-----------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>IT+</sub>     | Positive-going differential input voltage threshold | See Figure 24                                                     |     |     | 30  | mV   |

| VIT-                 | Negative-going differential input voltage threshold | See Figure 21                                                     |     |     | -30 | mV   |

| Vон                  | High-level output voltage                           | $I_{OH} = -2 \text{ mA}$                                          | 3.7 |     |     | V    |

| VOL                  | Low-level output voltage                            | I <sub>OL</sub> = 2 mA                                            |     |     | 0.5 | V    |

| Ц                    | Input current, B+ or B-                             | V <sub>I</sub> = 0 V to 2.5 V                                     |     |     | ±1  | μΑ   |

| I <sub>I</sub> (OFF) | Power-off Input current, B+ or B-                   | $V_{CC} = 0$ , $V_{I} = 0 V \text{ to } 2.5 V$                    |     |     | ±1  | μΑ   |

| lіН                  | High-level input current, DE/RE                     | V <sub>IH</sub> = 3.3 V ('976),<br>V <sub>IH</sub> = 2 V ('977)   |     |     | 50  | μΑ   |

| Ι <sub>ΙL</sub>      | Low-level input current, DE/RE                      | V <sub>IL</sub> = 1.6 V ('976),<br>V <sub>IL</sub> = 0.8 V ('977) | 8   |     |     | μΑ   |

| loz                  | High-impedance output current                       | VO = 0 or $VCC$                                                   |     |     | ±30 | μΑ   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. ‡ t<sub>Sk(lim)</sub> is the maximum delay time difference between any two drivers on any two devices operating at the same supply voltage and the same ambient temperature.

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

## LVD receiver switching characteristics over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                                                   | TEST CONDITIONS        | MIN | TYP <sup>†</sup> | MAX | UNIT |

|------------------|-------------------------------------------------------------|------------------------|-----|------------------|-----|------|

| tPLH             | Propagation delay time, low-to-high level output            |                        | 4.5 |                  | 10  | ns   |

| tPHL             | Propagation delay time, high-to-low level output            | V <sub>CC</sub> = 5 V, | 4.5 |                  | 10  | ns   |

| tsk(p)           | Pulse skew ( tpHL - tpLH )                                  | $T_A = 25^{\circ}C$ ,  |     |                  | 3   | ns   |

| t <sub>r</sub>   | Output signal rise time                                     | See Figure 21          |     |                  | 8   | ns   |

| t <sub>f</sub>   | Output signal fall time                                     |                        |     |                  | 8   | ns   |

| tsk(lim)         | Skew limit <sup>‡</sup>                                     |                        |     |                  | 5.5 | ns   |

| tPHZ             | Propagation delay time, high-level to high-impedance output |                        |     |                  | 42  | ns   |

| t <sub>PLZ</sub> | Propagation delay time, low-level to high-impedance output  | See Figure 18          | ·   |                  | 20  | ns   |

| t <sub>en</sub>  | Enable time, driver to receiver                             |                        | ·   |                  | 26  | ns   |

### single-ended receiver electrical characteristics over recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                              |       | TEST CONDITIONS                                                   | MIN | TYP | MAX | UNIT |

|-------------------|----------------------------------------|-------|-------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>IT+</sub>  | Positive-going input voltage threshold | B-    |                                                                   |     | 1.6 | 1.9 | V    |

| V <sub>IT</sub> - | Negative-going input voltage threshold | B-    |                                                                   | 1   | 1.1 |     | V    |

| Vон               | High-level output voltage              |       | I <sub>OH</sub> = -2 mA                                           | 3.7 | 4.6 |     | V    |

| VOL               | Low-level output voltage               |       | I <sub>OL</sub> = 2 mA                                            |     | 0.3 | 0.5 | V    |

| II                | Input current                          | B-    | V <sub>I</sub> = 0 to V <sub>CC</sub>                             |     |     | ±1  | μΑ   |

| I(OFF)            | Power-off Input current                | B-    | V <sub>CC</sub> = 0 V,<br>V <sub>I</sub> = 0 to 5.25 V            |     |     | ±1  | μΑ   |

| ΊΗ                | High-level input current               | DE/RE | V <sub>IH</sub> = 3.3 V ('976),<br>V <sub>IH</sub> = 2 V ('977)   |     |     | 50  | μΑ   |

| IIL               | Low-level input current                | DE/RE | V <sub>IL</sub> = 1.6 V ('976),<br>V <sub>IL</sub> = 0.8 V ('977) | 8   |     |     | μΑ   |

| loz               | High-impedance output current          |       | VO = 0 or VCC                                                     |     |     | -30 | μΑ   |

### single-ended receiver switching characteristics over recommended operating conditions (unless otherwise noted)

|                 | PARAMETER                                                   | TEST CONDITIONS        | MIN | TYP | MAX  | UNIT |

|-----------------|-------------------------------------------------------------|------------------------|-----|-----|------|------|

| tPLH            | Propagation delay time, low-to-high level output            |                        | 7   |     | 12.5 | ns   |

| tPHL            | Propagation delay time, high-to-low level output            | V <sub>CC</sub> = 5 V, | 7   |     | 12.5 | ns   |

| tsk(p)          | Pulse skew ( tpHL - tpLH )                                  | $T_A = 25^{\circ}C$ ,  |     |     | 3.5  | ns   |

| t <sub>r</sub>  | Output signal rise time                                     | See Figure 22          |     |     | 8    | ns   |

| tf              | Output signal fall time                                     |                        |     |     | 8    | ns   |

| tsk(lim)        | Skew limit <sup>†</sup>                                     |                        |     |     | 5.5  | ns   |

| tPHZ            | Propagation delay time, high-level to high-impedance output |                        |     |     | 20   | ns   |

| tPLZ            | Propagation delay time, low-level to high-impedance output  | See Figure 20          |     |     | 30   | ns   |

| t <sub>en</sub> | Enable time, driver to receiver                             |                        |     |     | 48   | ns   |

<sup>†</sup> t<sub>Sk(lim)</sub> is the maximum delay time difference between any two drivers on any two devices operating at the same supply voltage and the same ambient temperature.

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. ‡ t<sub>sk(lim)</sub> is the maximum delay time difference between any two drivers on any two devices operating at the same supply voltage and the same ambient temperature.

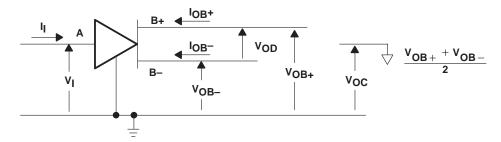

Figure 15. Voltage and Current Definitions

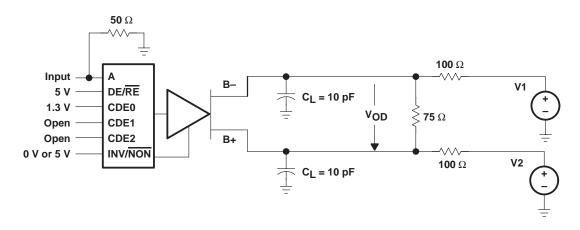

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_{\Gamma}$  or  $t_{\tilde{f}} \le 1$  ns, pulse repetition rate (PRR) = 10 Mpps, pulsewidth = 50 ns  $\pm 5$  ns,  $Z_0 = 50 \Omega$ .

- B. C<sub>I</sub> includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

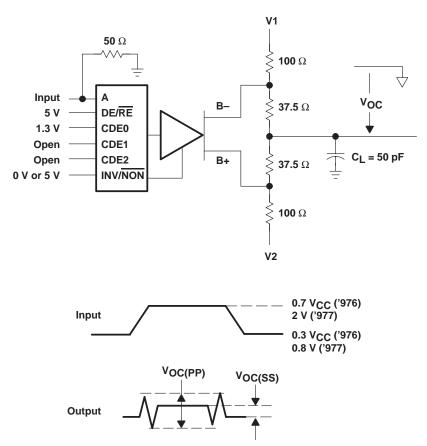

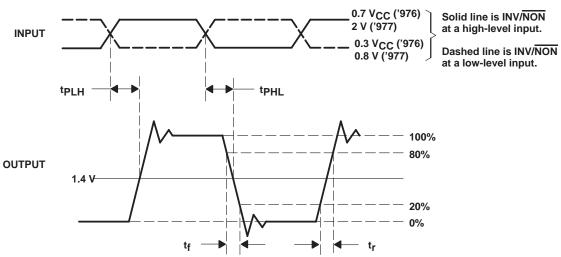

Figure 16. Differential Output Signal Test Circuit, Timing, and Voltage Definitions

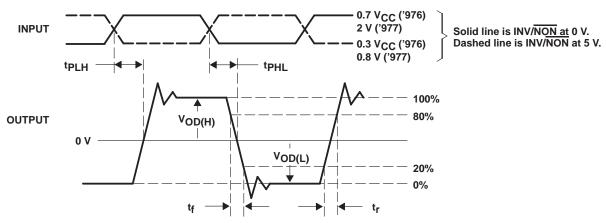

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_f$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 10 Mpps, pulsewidth = 50 ns  $\pm 5$  ns,  $Z_0 = 50 \Omega$ .

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

- C. The measurement of  $V_{OC(PP)}$  is made on test equipment with a -3 dB bandwidth of at least 300 MHz.

Figure 17. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

### **VOLTAGE WAVEFORMS**

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_f$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 1 Mpps, pulsewidth = 500 ns  $\pm 50$  ns,  $Z_0 = 50$   $\Omega$ .

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

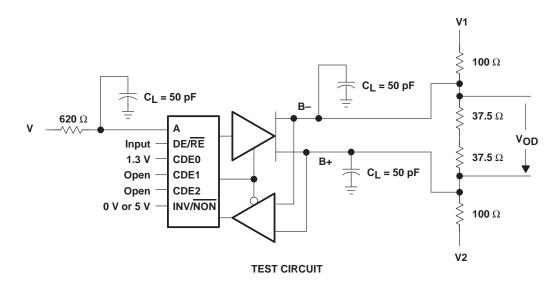

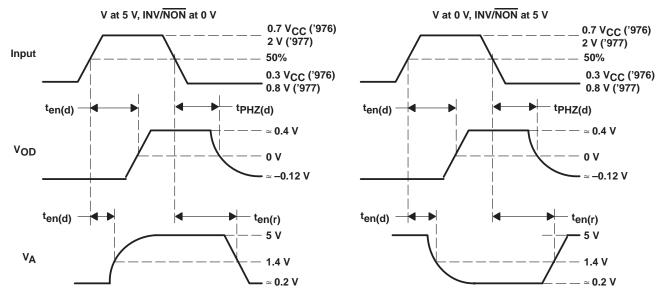

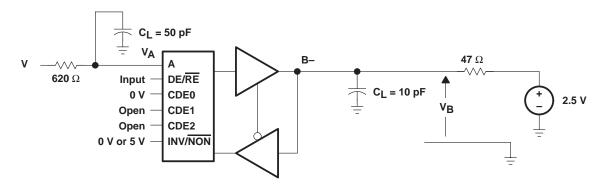

Figure 18. LVD Transceiver Enable and Disable Time Test Circuit and Definitions

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_{\Gamma}$  or  $t_{\Gamma} \le 1$  ns, pulse repetition rate (PRR) = 10 Mpps, pulsewidth = 50 ns  $\pm 5$  ns,  $Z_0$  = 50  $\Omega$ .

- B.  $C_L$  includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

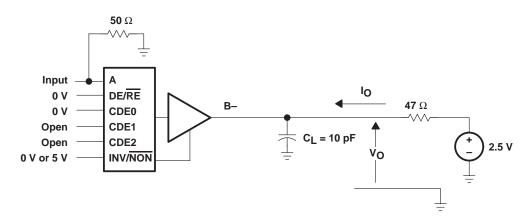

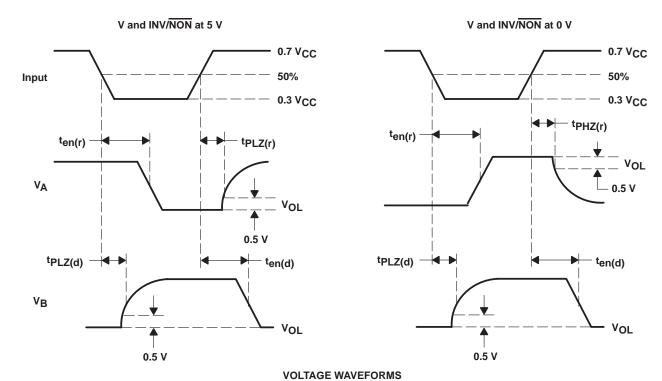

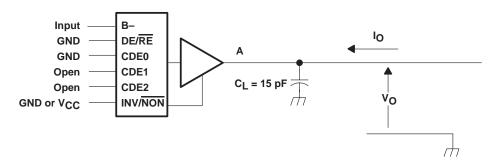

Figure 19. Single-Ended Driver Switching Test Circuit

**TEST CIRCUIT**

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_f$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 1 Mpps, pulsewidth = 500 ns  $\pm 50$  ns,  $Z_0 = 50$   $\Omega$ .

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

Figure 20. Single-Ended Transceiver Enable and Disable Timing Measurements

NOTES: A. Note: All input pulses are supplied by a generator having the following characteristics:  $t_{\Gamma}$  or  $t_{f} \leq 1$  ns, pulse repetition rate (PRR) = 10 Mpps, pulsewidth = 50 ns  $\pm 5$  ns,  $Z_0$  = 50  $\Omega$ .

B. C<sub>I</sub> includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

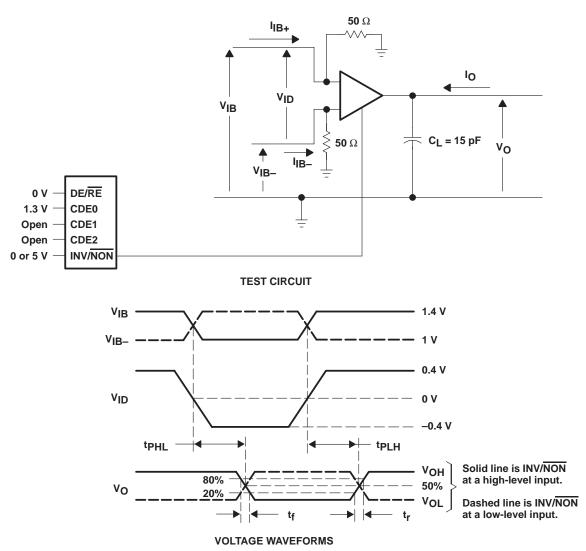

Figure 21. LVD Receiver Switching Characteristic Test Circuit

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_f$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 10 Mpps, pulsewidth = 50 ns  $\pm 5$  ns.

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within 0,06 m of the D.U.T.

Figure 22. Single-Ended Receiver Timing Test Circuit

## **APPLICATION INFORMATION**

Figure 23. Low-Pass Filter for Connecting DIFFSENS to CDE0

SLLS292B - APRIL 1998 - REVISED JANUARY 2000

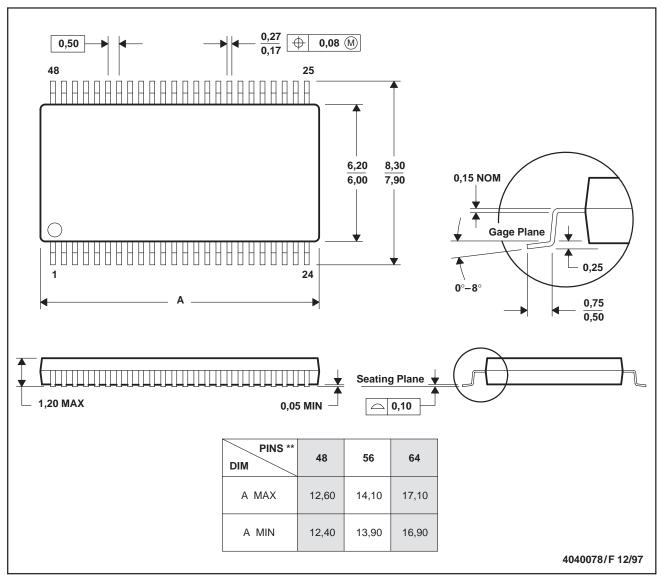

### **MECHANICAL INFORMATION**

## DGG (R-PDSO-G\*\*)

### PLASTIC SMALL-OUTLINE PACKAGE

### **48 PIN SHOWN**

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated