SN65LVDS32A

SLLS368C - JULY 1999 - REVISED JANUARY 2000

- Meets or Exceeds the Requirements of ANSI EIA/TIA-644 Standard for Signaling Rates<sup>†</sup> Up to 400 Mbps

- Operates With a Single 3.3 V Supply

- –2 V to 4.4 V Common-Mode Input Voltage Range

- Differential Input Thresholds <50 mV With 50 mV of Hysteresis Over Entire Common-Mode Input Voltage Range

- Integrated 110 $\Omega$  Line Termination Resistors Offered With the LVDT Series

- Propagation Delay Times 4 ns (typ)

- Open-Circuit and Terminated Fail Safe Assures a High-Level Output With No Input

- Bus-Pin ESD Protection Exceeds 15 kV HBM

- Outputs High-Impedance With V<sub>CC</sub> < 1.5 V</li>

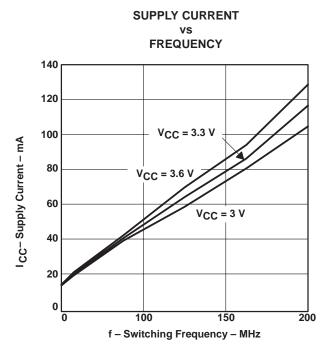

- Power Dissipation <400 mW With Four Receivers Switching at 200 MHz

- Available in Small-Outline Package With 1,27 mm Terminal Pitch

- Pin-Compatible With the AM26LS32, MC3486, or uA9637

#### description

This family of differential line receivers offer improved performance and features that implement the electrical characteristics of low-voltage differential signaling (LVDS). LVDS is defined in the TIA/EIA-644 standard. This improved performance represents the second generation of receiver products for this standard providing a better overall solution for the cabled environment. The next generation family of products is an extension to TI's overall product portfolio and is not necessarily a replacement for older LVDS receivers.

Improved features include an input commonmode voltage range 2 V wider than the minimum required by the standard. This will allow longer cable lengths by tripling the allowable ground noise tolerance to 3 V between a driver and receiver.

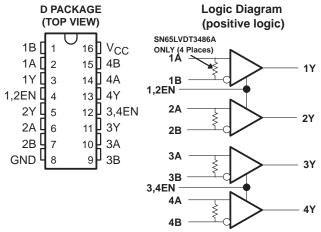

#### SN65LVDT32A **D PACKAGE Logic Diagram** (TOP VIEW) (positive logic) G 16 V<sub>CC</sub> 1B G — SN65LVDT32A 15 AB 1A 🛛 2 ONLY (4 Places) 1Y 🛮 3 14 🛮 4A G [ 13 4Y 1Y 4 1B 12 G 2Y 4 5 2A 11 3Y 6 2A 10 3A 2B 7 2Y 2B GND 8 9 3В **3A 3Y** 3B 4A 4B

#### SN65LVDS3486A SN65LVDT3486A

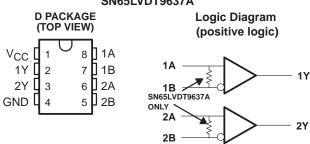

#### SN65LVDS9637A SN65LVDT9637A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

† Signaling rate, 1/t, where t is the minimum unit interval and is expressed in the units bits/s (bits per second)

SLLS368C - JULY 1999 - REVISED JANUARY 2000

#### description (continued)

Precise control of the differential input voltage thresholds now allows for inclusion of 50 mV of input voltage hysteresis to improve noise rejection on slowly changing input signals. The input thresholds are still no more than  $\pm 50$  mV over the full input common-mode voltage range. See *Application Information* for more details on this feature.

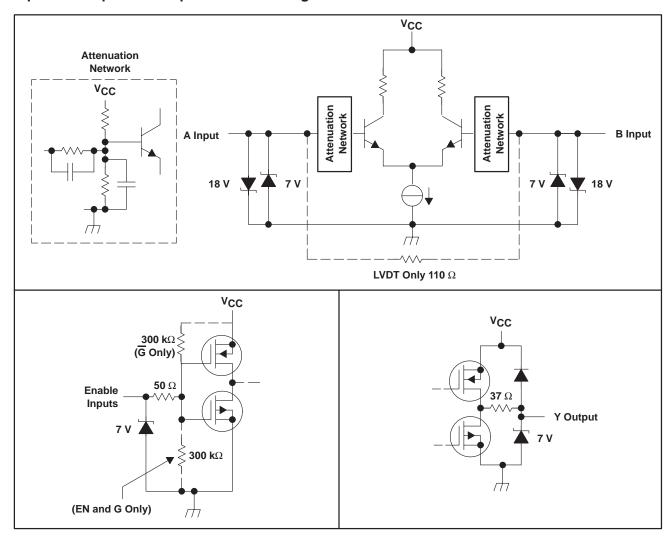

The high-speed switching of LVDS signals almost always necessitates the use of a line impedance matching resistor at the receiving-end of the cable or transmission media. The SN65LVDT series of receivers eliminates this external resistor by integrating it with the receiver. The nonterminated SN65LVDS series is also available for multidrop or other termination circuits.

The receivers can withstand  $\pm 15$  kV human-body model (HBM) and  $\pm 600$  V machine model (MM) electrostatic discharges to the receiver input pins with respect to ground without damage. This provides reliability in cabled and other connections where potentially damaging noise is always a threat.

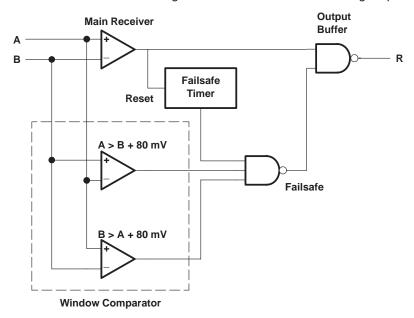

The receivers also include a (patent pending) fail-safe circuit that will provide a high-level output within 500 ns after loss of the input signal. The most common causes of signal loss are disconnected cables, shorted lines, or powered-down transmitters. This prevents noise from being received as valid data under these fault conditions. This feature may also be used for wired-OR bus signaling.

The intended application of these devices and signaling technique is for point-to-point baseband data transmission over controlled impedance media of approximately 100  $\Omega$ . The transmission media may be printed-circuit board traces, backplanes, or cables. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

The SN65LVDS32A, SN65LVDT32A, SN65LVDS3486A, SN65LVDT3486A, SN65LVDS9637A, and SN65LVDT9637A are characterized for operation from -40°C to 85°C.

Function Tables

SN65LVDS32A and SN65LVDT32A

| DIFFERENTIAL INPUT                 | ENA    | BLES   | OUTPUT |

|------------------------------------|--------|--------|--------|

| A-B                                | G      | G      | Υ      |

| V <sub>ID</sub> ≥ -70 mV           | H<br>X | X<br>L | H<br>H |

| -100 mV < V <sub>ID</sub> ≤ -70 mV | H<br>X | X<br>L | ?      |

| V <sub>ID</sub> ≤ -100 mV          | H<br>X | X<br>L | L<br>L |

| X                                  | L      | Н      | Z      |

| Open                               | H<br>X | X<br>L | H<br>H |

$H = high\ level, \quad L = low\ level, \quad X = irrelevant,$

Z = high impedance (off), ? = indeterminate

#### SN65LVDS3486A and SN65LVDT3486A

| DIFFERENTIAL INPUT                 | ENABLES | OUTPUT |

|------------------------------------|---------|--------|

| A-B                                | EN      | Υ      |

| V <sub>ID</sub> ≥ -70 mV           | Н       | Н      |

| -100 mV < V <sub>ID</sub> ≤ -70 mV | Н       | ?      |

| $V_{ID} \le -100 \text{ mV}$       | Н       | L      |

| Х                                  | L       | Z      |

| Open                               | Н       | Н      |

H = high level, L = low level, X = irrelevant,

Z = high impedance (off), ? = indeterminate

## **Function Tables (Continued)**

#### SN65LVDS9637A and SN65LVDT9637A

| DIFFERENTIAL INPUT                 | OUTPUT |  |  |

|------------------------------------|--------|--|--|

| A-B                                | Υ      |  |  |

| V <sub>ID</sub> ≥ -70 mV           | Н      |  |  |

| -100 mV < V <sub>ID</sub> ≤ -70 mV | ?      |  |  |

| V <sub>ID</sub> ≤ -100 mV          | L      |  |  |

| Open                               | Н      |  |  |

H = high level, L = low level, ? = indeterminate

## equivalent input and output schematic diagrams

SLLS368C - JULY 1999 - REVISED JANUARY 2000

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)           | 0.5 V to 4 V                   |

|--------------------------------------------------------------|--------------------------------|

| Voltage range: Enables or Y                                  | 0.5 V to V <sub>CC</sub> + 3 V |

| A or B                                                       |                                |

| Electrostatic discharge: A, B, and GND (see Note 2)          | Class 3, A: 15 kV, B: 600 V    |

| All pins                                                     | Class 3, A: 7 kV, B: 500 V     |

| Continuous power dissipation                                 | See Dissipation Rating Table   |

| Storage Temperature range                                    |                                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                          |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

- 2. Tested in accordance with MIL-STD-883C Method 3015.7.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | OPERATING FACTOR <sup>‡</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------|

| D8      | 725 mW                                                                     | 5.8 mW/°C                                                    | 377 mW                                |

| D16     | 950 mW                                                                     | 7.6 mW/°C                                                    | 494 mW                                |

<sup>&</sup>lt;sup>‡</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

## recommended operating conditions

|                                                          |         | MIN | NOM | MAX | UNIT |

|----------------------------------------------------------|---------|-----|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                          |         |     | 3.3 | 3.6 | V    |

| High-level input voltage, VIH                            | Enables | 2   |     |     | V    |

| Low-level input voltage, V <sub>IL</sub>                 | Enables |     |     | 0.8 | V    |

| Magnitude of differential input voltage, V <sub>ID</sub> |         | 0.1 |     | 3   | V    |

| Common-mode input voltage, V <sub>IC</sub>               |         | -2  |     | 4.4 | V    |

| Operating free-air temperature, T <sub>A</sub>           |         | -40 |     | 85  | °C   |

SLLS368C - JULY 1999 - REVISED JANUARY 2000

## electrical characteristics over recommended operating conditions (unless otherwise noted)

| PARAMETER            |                                         | TEST CONDITIONS   |                                                                           | MIN                             | TYP <sup>†</sup> | MAX | UNIT |    |

|----------------------|-----------------------------------------|-------------------|---------------------------------------------------------------------------|---------------------------------|------------------|-----|------|----|

| VITH1                | Positive-going differential input ve    | oltage threshold  | V <sub>IB</sub> =-2 V or 4.4 V, See Figure 1                              |                                 |                  |     | 50   | \/ |

| V <sub>ITH2</sub>    | Negative-going differential input       | voltage threshold |                                                                           |                                 | -50              |     |      | mV |

| V <sub>ITH3</sub>    | Differential input fail-safe voltage    | threshold         | See Figure 2 and                                                          | d Table 1                       | -70              |     | -100 | mV |

| V <sub>ID(HYS)</sub> | Differential input voltage hysteres     | sis,              |                                                                           |                                 |                  | 50  |      | mV |

| Vон                  | High-level output voltage               |                   | $I_{OH} = -8 \text{ mA}$                                                  |                                 | 2.4              |     |      | V  |

| V <sub>OL</sub>      | Low-level output voltage                |                   | $I_{OL} = 8 \text{ mA}$                                                   |                                 |                  |     | 0.4  | V  |

|                      |                                         | '32A or '3486A    | G or EN at V <sub>CC</sub><br>Steady-state                                | , No load,                      |                  | 16  | 23   |    |

| ICC                  | Supply current                          |                   | G or EN at GND                                                            |                                 |                  | 1.1 | 5    | mA |

|                      |                                         | '9637A            | No load,                                                                  | Steady-state                    |                  | 8   | 12   |    |

|                      |                                         |                   | $V_I = 0 V$ ,                                                             | Other input open                |                  |     | ±20  |    |

|                      | Input current (A or B inputs)           | SN65LVDS          | V <sub>I</sub> =2.4 V,                                                    | Other input open                |                  |     | ±20  | μΑ |

|                      |                                         | SNOSLVDS          | V <sub>I</sub> =-2 V,                                                     | Other input open                |                  |     | ±40  |    |

| 1.                   |                                         |                   | V <sub>I</sub> = 4.4 V,                                                   | Other input open                |                  |     | ±40  |    |

| 1                    |                                         | SN65LVDT          | V <sub>I</sub> = 0 V,                                                     | Other input open                |                  |     | ±40  | μΑ |

|                      |                                         |                   | V <sub>I</sub> =2.4 V,                                                    | Other input open                |                  |     | ±40  |    |

|                      |                                         |                   | V <sub>I</sub> =-2 V,                                                     | Other input open                |                  |     | ±80  |    |

|                      |                                         |                   | V <sub>I</sub> = 4.4 V,                                                   | Other input open                |                  |     | ±80  |    |

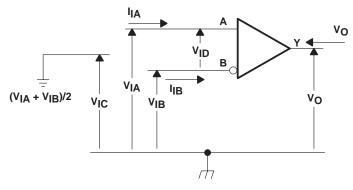

|                      | Differential input current              | SN65LVDS          | V <sub>ID</sub> = 100 mV,<br>See Figure 1                                 | $V_{IC}$ = -2 V or 4.4 V,       |                  |     | ±2   | μΑ |

| lD                   | (I <sub>IA</sub> - I <sub>IB</sub> )    | SN65LVDT          | V <sub>ID</sub> = 0.4 V,                                                  | V <sub>IC</sub> = -2 V or 4.4 V | 3.1              |     | 4.5  | mA |

|                      |                                         | SNOSLVDT          | V <sub>ID</sub> = -0.4 V,                                                 | V <sub>IC</sub> = -2 V or 4.4 V | -3.1             |     | -4.5 | mA |

| l.,                  | Power-off input current (A or B inputs) |                   | V <sub>A</sub> or V <sub>B</sub> =0 or 2                                  | 2.4 V,                          |                  |     | ±30  | 4  |

| I(OFF)               |                                         |                   | V <sub>A</sub> or V <sub>B</sub> =-2 V or 4.4 V,<br>V <sub>CC</sub> = 0 V |                                 |                  |     | ±50  | μΑ |

| lн                   | High-level input current (enables       | )                 | V <sub>IH</sub> = 2 V                                                     |                                 |                  |     | 10   | μΑ |

| Ι <sub>Ι</sub> L     | Low-level input current (enables)       |                   | V <sub>IL</sub> = 0.8 V                                                   |                                 |                  |     | 10   | μΑ |

| loz                  | High-impedance output current           |                   |                                                                           |                                 |                  |     | ±10  | μΑ |

| C <sub>IN</sub>      | Input capacitance, A or B input to      | GND               | V <sub>I</sub> = 0.4 sin (4E6πt) + 0.5 V                                  |                                 | 4E6πt) + 0.5 V 5 |     |      | pF |

<sup>†</sup> All typical values are at 25°C and with a 3.3 V supply.

SLLS368C - JULY 1999 - REVISED JANUARY 2000

## switching characteristics over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                    | TEST CONDITIONS                         | MIN | TYP <sup>†</sup> | MAX | UNIT |

|---------------------|--------------------------------------------------------------|-----------------------------------------|-----|------------------|-----|------|

| <sup>t</sup> PLH    | Propagation delay time, low-to-high-level output             |                                         | 2.5 | 4                | 6   | ns   |

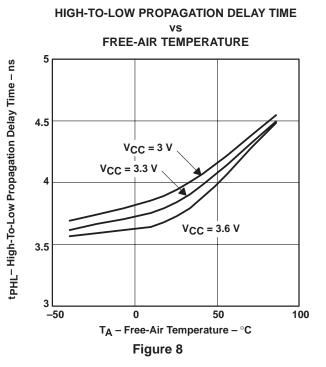

| tPHL                | Propagation delay time, high-to-low-level output             |                                         | 2.5 | 4                | 6   | ns   |

| <sup>t</sup> d1     | Delay time, fail-safe deactivate time                        |                                         |     |                  | 6.1 | ns   |

| t <sub>d2</sub>     | Delay time, fail-safe activate time                          | ]                                       | 0.3 |                  | 1   | μs   |

| t <sub>sk(p)</sub>  | Pulse skew ( tpHL1 - tpLH1 )                                 | C <sub>L</sub> = 10 pF,<br>See Figure 3 |     | 200              |     | ps   |

| t <sub>sk(o)</sub>  | Output skew§                                                 | Occ r igure o                           |     | 150              |     | ps   |

| t <sub>sk(pp)</sub> | Part-to-part skew <sup>‡</sup>                               |                                         |     |                  | 1   | ns   |

| t <sub>r</sub>      | Output signal rise time                                      |                                         |     | 600              |     | ps   |

| t <sub>f</sub>      | Output signal fall time                                      |                                         |     | 600              |     | ps   |

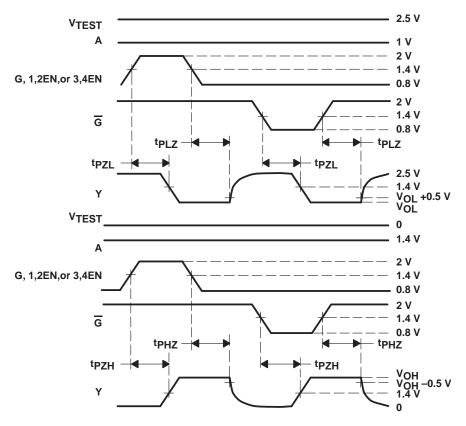

| <sup>t</sup> PHZ    | Propagation delay time, high-level-to-high-impedance output  |                                         |     | 5.5              | 9   | ns   |

| <sup>t</sup> PLZ    | Propagation delay time, low-level-to-high-impedance output   | Soo Eiguro 4                            |     | 4.4              | 9   | ns   |

| <sup>t</sup> PZH    | Propagation delay time, high-impedance -to-high-level output | See Figure 4                            |     | 3.8              | 9   | ns   |

| tPZL                | Propagation delay time, high-impedance-to-low-level output   | ]                                       |     | 7                | 9   | ns   |

<sup>†</sup> All typical values are at 25°C and with a 3.3 V supply.

### PARAMETER MEASUREMENT INFORMATION

Figure 1. Voltage and Current Definitions

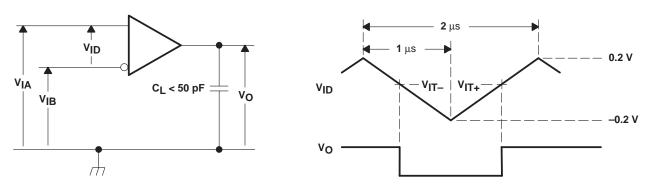

Figure 2. V<sub>ITH3</sub> Input Voltage Threshold Test Circuit and Definitions

<sup>‡</sup> t<sub>sk(pp)</sub> is the magnitude of the time difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

<sup>§</sup> tsk(o) is the magnitude of the time difference between the tplh or tphl of all receivers of a single device with all of their inputs driven together.

## PARAMETER MEASUREMENT INFORMATION

Table 1. Receiver Minimum and Maximum Fail-Safe Input Threshold Test Voltages

| APPLIED V            | OLTAGES†             | RESULTANT INPUTS     |                      |        |

|----------------------|----------------------|----------------------|----------------------|--------|

| V <sub>IA</sub> (mV) | V <sub>IB</sub> (mV) | V <sub>ID</sub> (mV) | V <sub>IC</sub> (mV) | Output |

| -2050                | -1950                | -100                 | -2000                | L      |

| -2035                | -1965                | -70                  | -2000                | Н      |

| 4350                 | 4450                 | -100                 | 4400                 | L      |

| 4365                 | 4435                 | -70                  | 4400                 | Н      |

<sup>†</sup> These voltages are applied for a minimum of 1 µs.

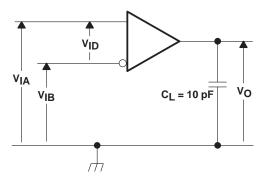

NOTE A: All input pulses are supplied by a generator having the following characteristics:  $t_{\Gamma}$  or  $t_{f} \le 1$  ns, Pulse Repetition Rate (PRR) = 50 Mpps, Pulsewidth =  $10 \pm 0.2$  ns .  $C_{L}$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 3. Timing Test Circuit and Waveforms

### PARAMETER MEASUREMENT INFORMATION

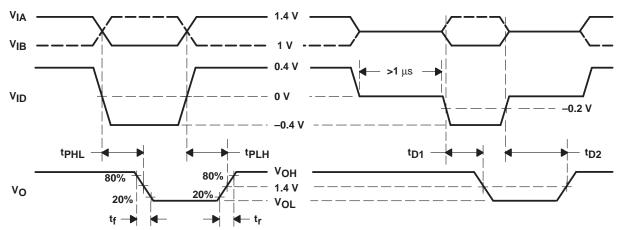

NOTE B: All input pulses are supplied by a generator having the following characteristics:  $t_\Gamma$  or  $t_\Gamma \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, Pulsewidth =  $10 \pm 0.2$  ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 mm of the D.U.T.

Figure 4. Enable/Disable Time Test Circuit and Waveforms

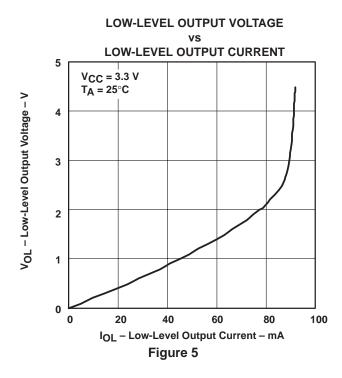

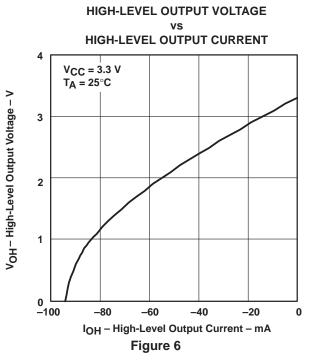

#### **TYPICAL CHARACTERISTICS**

# FREE-AIR TEMPERATURE VCC = 3 V VCC = 3.3 V VCC = 3.6 V TA – Free-Air Temperature – °C

Figure 7

**LOW-TO-HIGH PROPAGATION DELAY TIME**

## **TYPICAL CHARACTERISTICS**

Figure 9

SLLS368C - JULY 1999 - REVISED JANUARY 2000

#### **APPLICATION INFORMATION**

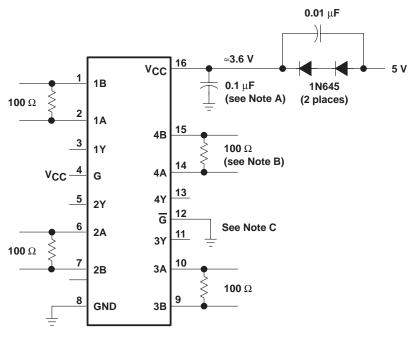

NOTES: A. Place a 0.1 μF Z5U ceramic, mica or polystyrene dielectric, 0805 size, chip capacitor between V<sub>CC</sub> and the ground plane. The capacitor should be located as close as possible to the device terminals.

- B. The termination resistance value should match the nominal characteristic impedance of the transmission media with ±10%.

- C. Unused enable inputs should be tied to V<sub>CC</sub> or GND as appropriate.

Figure 10. Operation with 5-V Supply

#### related information

IBIS modeling is available for this device. Please contact the local TI sales office or the TI Web site at www.ti.com for more information.

For more application guidelines, please see the following documents:

- Low-Voltage Differential Signalling Design Notes (TI literature number SLLA014)

- Interface Circuits for TIA/EIA-644 (LVDS) (SLLA038)

- Reducing EMI With LVDS (SLLA030)

- Slew Rate Control of LVDS Circuits (SLLA034)

- Using an LVDS Receiver With RS-422 Data (SLLA031)

- Evaluating the LVDS EVM (SLLA033)

#### **APPLICATION INFORMATION**

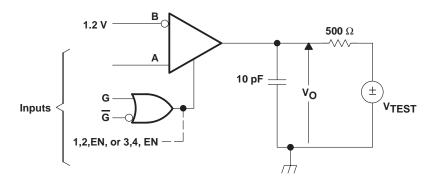

#### abstract terminated failsafe

Differential data line receivers commonly have failsafe circuits to prevent the receiver from switching on input noise. This can occur when the bus driver is turned off or the interconnecting cable is damaged or left floating. This is generally solved with an external resistor network that applies a steady state bias voltage to the undriven input pins. In addition to the cost of external components, this has the effect of lowering the input magnitude thereby reducing the differential noise margin. Current Integrated solutions will not work in wired-OR or common mode termininated bus applications. The terminated failsafe circuit works over its entire extended common mode range and will ensure a known state regardless of the common mode signal present.

Figure 11. Receiver with Terminated Failsafe

SLLS368C - JULY 1999 - REVISED JANUARY 2000

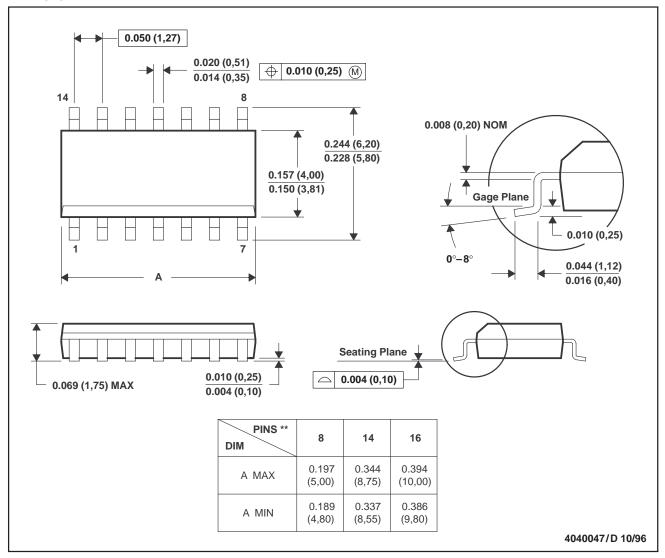

#### **MECHANICAL DATA**

### D (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### 14 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated