| •    | Nine Single-Ended SCSI Transceiver<br>Channels With Active Termination                           | _                      | L PAC<br>(TOP V |                                                                |

|------|--------------------------------------------------------------------------------------------------|------------------------|-----------------|----------------------------------------------------------------|

| •    | Programmable Drivers Provide Active<br>Negation (Totem Pole) or Wired-OR (Open<br>Drain) Outputs | GND [<br>TE [<br>GND [ | 2               | 56 8B<br>55 GND<br>54 CE                                       |

| •    | 24-mA Current-Mode Active Termination<br>With Common Nine-Channel Bus Enable                     | а –                    | 4               | 53 NC<br>52 NC                                                 |

| ٠    | Low Output Capacitance Presented to SCSI<br>Bus, 13.5 pF Typ                                     | 2A [<br>2DE/RE [       |                 | 51 NC<br>50 7B                                                 |

| •    | 3.3 V Compatible Logic Inputs Provide<br>Bridge from 3 V Controllers to 5 V SCSI<br>Bus          |                        |                 | 49   NC<br>48   6B<br>47   NC                                  |

| ٠    | Designed to Operate at 10-Million Data<br>Transfers Per Second (Fast-SCSI)                       | V <sub>CC1</sub>       | 11<br>12        | 46 5B<br>45 V <sub>CC</sub>                                    |

| ٠    | Controlled Driver Rise and Fall Times<br>5 ns Min                                                | GND [                  | 13<br>14<br>15  | 44 GND<br>43 GND                                               |

| ٠    | High-Receiver Input-Voltage Hysteresis<br>500 mV Typ                                             | GND [                  | 16<br>17        | 42 GND<br>41 GND<br>40 GND                                     |

| ٠    | Receiver Input-Noise Pulse Filter<br>5 ns Typ                                                    | 9                      | 18<br>19        | <sup>39</sup> V <sub>CC</sub><br><sup>38</sup> NC              |

| •    | Each Driver and Receiver Meets ANSI<br>X3.131-1994 (SCSI-2) and the Proposed<br>SCSI-3 Standards | 6A [                   | 20<br>21<br>22  | <sup>37</sup> ] 4B<br><sup>36</sup> ] NC<br><sup>35</sup> ] 3B |

| •    | Power-Up/Power-Down Glitch Protection                                                            | 7A [                   | 23<br>24        | <sup>34</sup> NC<br><sup>33</sup> 2B                           |

| •    | High Impedance Driver With $V_{CC}$ at 0 V                                                       | 8A [                   | 25              | <sup>32</sup> NC                                               |

| desc | ription                                                                                          |                        | 26<br>27        | <sup>31</sup> ] 1B<br><sup>30</sup> ] NC                       |

|      | The SN75LBC968 is a nine-channel transceiver with active termination that drives and receives    | · · ·                  | 28              | <sup>29</sup> 9B                                               |

with active termination that drives and receives the signals from the single-ended, parallel data buses such as the Small Computer-Systems

NC - No internal connection

Interface (SCSI) bus. The features of the line drivers, receivers, and active-termination circuits provide the optimum signal-to-noise ratios for reliable data transmission. Integration of the termination and transceivers in the LinBiCMOS<sup>™</sup> process provides the necessary analog-circuit performance, has low quiescent power, and reduces the capacitance presented to the bus over separate termination and I/O circuits.

The transceivers of the SN75LBC968 can be enabled to function as totem-pole or open-drain outputs. The open-drain mode drives the wired-OR lines of SCSI (BSY, SEL, and RST) by inputting the data to the direction control input DE/RE instead of the A input. When driving the data through the A input, the outputs become totem poles and provide active signal negation for a higher voltage level on low-to-high signal transitions on heavily loaded buses. In either mode, the turn-on and turn-off output transition times are limited to minimize crosstalk through capacitive coupling to adjacent lines and RF emissions from the cable. The receivers are also designed for optimum analog performance by precisely controlling the input-voltage thresholds, providing wide input-voltage hysteresis and including an input-noise filter. These features significantly increase the likelihood of detecting only the desired data signal and rejecting noise.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LinBiCMOS is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### description (continued)

The communication between the SN75LBC968 and the controller can be accomplished at 3.3-V logic levels provided that the  $V_{CC1}$  input connects to the same supply rail as the controller. This provides a bridge from the lower-voltage circuit and the 5-V SCSI bus. The SN75LBC968 also removes the need for special I/O buffers (and associated power dissipation) on the controller itself. The SN75LBC968 must be used with a SCSI controller with support for Differential SCSI.

The integrated, current-mode, active termination supplies a constant 24 mA of current (TERMPWR) to the bus when the bus voltage falls below 2.5 V. This makes the next low-to-high (negation) signal transition independent of the low-level (asserted) bus voltage, unlike voltage-mode terminators. The termination current is provided through the TE input and from TERMPWR and can be disabled by letting the TE input float or by connecting it to ground. The termination circuitry is independent from the line drivers and receivers and V<sub>CC</sub> or V<sub>CC1</sub>. Operational termination is present as long as TERMPWR is applied.

The switching speeds of the SN75LBC968 are sufficient to transfer data over the data bus at ten million transfers per second (Fast-SCSI). The specification,  $t_{sk(lim)}$ , is for system skew budgeting and maintenance of bus set-up and hold times. The device is available in the space-efficient shrink-small-outline package (SSOP) with 25-mil lead pitch. The SN75LBC968 meets or exceeds the requirements of ANSI X3.131–1994 (SCSI-2) and the proposed SPI (SCSI-3) standards, and is characterized for operation from 0°C to 70°C.

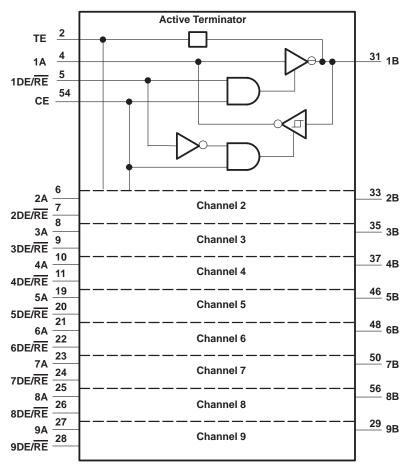

### logic diagram (positive logic)

**Function Tables**

TRANSCEIVER FUNCTIONS

|    | IN    | OUT  | PUTS |   |   |

|----|-------|------|------|---|---|

| CE | DE/RE | Α    | В    | Α | В |

| L  | Х     | Х    | Х    | Z | Z |

| н  | L     | Х    | L    | н | Z |

| Н  | L     | Х    | Н    | L | Z |

| Н  | Н     | L    | Х    | Z | н |

| Н  | Н     | Н    | Х    | Z | L |

| Н  | L     | Х    | Open | н | Z |

| н  | Н     | Open | Х    | Z | L |

H = high level L = low levelX = irrelevant Z = high impedance

#### **TERMINATION FUNCTION**

| INPUT | OUTPUT       |

|-------|--------------|

| TE    | B            |

| GND   | Z            |

| VTE   | 24-mA source |

| Open  | Z            |

# DRIVER VCC 2.85 V 2.85 V CC RECEIVER Vcc Vref Urgf

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> , V <sub>CC1</sub> , V <sub>TE</sub> (see Note 1) |                          |

|-----------------------------------------------------------------------------------------|--------------------------|

| Input voltage range, V <sub>I</sub> (A-side)                                            | V <sub>CC1</sub> + 0.3 V |

| Bus voltage range (B-side)                                                              | 0.5 V to 7 V             |

| Data I/O and control (A-side) voltage range                                             | $-0.5$ V to 7 V          |

| Continuous power dissipation (see Note 2)                                               | Internally Limited       |

| Operating free-air temperature range, T <sub>A</sub>                                    | 0°C to 70°C              |

| Storage temperature range, T <sub>stg</sub>                                             | 65°C to 150°C            |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                            | 260°C                    |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to GND.

schematics

2. The maximum operating-junction temperature is internally limited. Use the dissipation rating table to operate below this temperature.

| DISSIPATION RATING TABLE |                                    |                                                             |                                       |  |  |  |  |  |

|--------------------------|------------------------------------|-------------------------------------------------------------|---------------------------------------|--|--|--|--|--|

| PACKAGE                  | $T_A \le 25^{\circ}C$ POWER RATING | DERATING FACTOR <sup>†</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |  |  |  |  |  |

| DL                       | 2500 mW                            | 20 mW/°C                                                    | 1600 mW                               |  |  |  |  |  |

<sup>†</sup> Derating factors are the inverse of the junction-to-ambient thermal resistance when board-mounted with no air flow.

# recommended operating conditions

|                                               |                 | MIN  | NOM | MAX  | UNIT |

|-----------------------------------------------|-----------------|------|-----|------|------|

| Supply voltage, V <sub>CC</sub>               |                 | 4.75 | 5   | 5.25 | V    |

| Supply voltage, V <sub>CC1</sub> (see Note 3) |                 | 3    |     | 5.25 | V    |

| Termination voltage, V <sub>TE</sub>          |                 | 4.25 |     | 5.25 | V    |

| High-level input voltage, V <sub>IH</sub>     | DE/RE, CE, A, B | 2    |     |      | V    |

| Low-level input voltage, VIL                  | DE/RE, CE, A, B |      |     | 0.8  | V    |

| High-level output current, I <sub>OH</sub>    | A               |      |     | -8   | mA   |

|                                               | В               |      |     | 48   | m۸   |

| ow-level output current, IOL                  | А               |      |     | 8    | mA   |

| Operating free-air temperature, TA            |                 | 0    |     | 70   | °C   |

NOTE 3: All electrical characteristics are measured with  $V_{CC1} = V_{CC}$  unless otherwise noted.

# driver electrical characteristics over recommended operating conditions (unless otherwise noted) (see Figure 1)

|                | PARAMETER TEST CONDITIONS           |                                                                    | MIN MAX | UNIT |

|----------------|-------------------------------------|--------------------------------------------------------------------|---------|------|

| VOH            | High-level output voltage           | $I_{OH} = -20 \text{ mA}$                                          | 2       | V    |

| VOL            | Low-level output voltage            | I <sub>OL</sub> = 48 mA                                            | 0.5     | V    |

| Чн             | High-level input current            | $V_{IH} = 2 V$ , $V_{CC} = V_{CC1} = 5.25 V$                       | -100    | μA   |

| ١ <sub>L</sub> | Low-level input current, A          | $V_{IL} = 0.5 V$ , $V_{CC} = V_{CC1} = 5.25 V$                     | -100    | μA   |

| 107            | High-impedance-state output current | $V_{O} = 5.25 \text{ V}, \qquad V_{CC} = V_{CC1} = 5.25 \text{ V}$ | -100    | μA   |

| loz            | nigh-impedance-state output current | $V_{O} = 0 V$ , $V_{CC} = V_{CC1} = 5.25 V$                        | -100    | μΑ   |

# termination electrical characteristics over recommended operating conditions (unless otherwise noted) (see Figure 2)

|        | PARAMETER                   | TEST CONDITIONS         |                          | MIN | TYP  | MAX  | UNIT |

|--------|-----------------------------|-------------------------|--------------------------|-----|------|------|------|

| VO(OC) | Open-circuit output voltage | IO = 0 mA,              | $V_{CC} = V_{CC1} = 0 V$ | 2.5 | 2.85 | 3.24 | V    |

|        | Output current              | V <sub>O</sub> = 0 V,   | $V_{CC} = V_{CC1} = 0 V$ |     |      | -24  | mA   |

|        |                             | V <sub>O</sub> = 0.5 V, | $V_{CC} = V_{CC1} = 0 V$ | -20 |      | -24  | mA   |

| 10     |                             | V <sub>O</sub> = 3 V,   | $V_{CC} = V_{CC1} = 0 V$ |     |      | 100  | μΑ   |

|        |                             | V <sub>O</sub> = 4 V,   | $V_{CC} = V_{CC1} = 0 V$ | 2   |      | 12   | mA   |

# receiver electrical characteristics over recommended operating conditions (unless otherwise noted) (see Figure 3)

|                  | PARAMETER                                                       | TEST CONDITIONS         | MIN | TYP | MAX  | UNIT |

|------------------|-----------------------------------------------------------------|-------------------------|-----|-----|------|------|

| VOH              | High-level output voltage                                       | I <sub>OH</sub> = -8 mA | 2   | 2.5 |      | V    |

| VOL              | Low-level output voltage                                        | I <sub>OL</sub> = 8 mA  |     |     | 0.8  | V    |

| VIT+             | Positive-going input threshold voltage                          |                         | 1.2 | 1.6 | 2    | V    |

| VIT-             | Negative-going input threshold voltage                          | $V_{CC} = V_{CC1}$      | 0.8 | 1.1 | 1.4  | V    |

| V <sub>hys</sub> | Input hysteresis voltage (V <sub>IT+</sub> – V <sub>IT</sub> –) |                         | 0.2 | 0.5 |      | V    |

| Чн               | High-level input current                                        | V <sub>IH</sub> = 2 V   |     |     | 100  | μΑ   |

| ١ <sub>IL</sub>  | Low-level input current                                         | V <sub>IL</sub> = 0.5 V |     |     | 100  | μΑ   |

|                  | High impodance state output current                             | VO = 0 V                |     |     | -100 | ۸    |

| loz              | High-impedance-state output current                             | V <sub>O</sub> = 5.25 V |     |     | -100 | μA   |

#### device electrical characteristics over recommended operating conditions (unless otherwise noted)

|                 | PA                                | RAMETER                                                          | TEST CONDITIONS                                                                                | MIN | түр†                                  | MAX  | UNIT |

|-----------------|-----------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|---------------------------------------|------|------|

|                 |                                   | All drivers, receivers, and terminator disabled                  | minator All inputs at 0 V 1.3                                                                  |     | 3                                     |      |      |

|                 | Supply current to V <sub>CC</sub> | All receivers enabled, termination and drivers disabled, No load | CE at V <sub>CC</sub> , DE/ <del>RE</del> at 0 V,<br>TE at 0 V                                 |     | 14         21           33         45 | 21   |      |

| ICC             | and V <sub>CC1</sub>              | All drivers enabled, termination and                             | DE/RE and CE at V <sub>CC</sub> ,<br>A and TE at 0 V                                           |     |                                       | mA   |      |

|                 |                                   |                                                                  | $DE/\overline{RE}$ and CE at V <sub>CC</sub> ,<br>V <sub>TE</sub> = 0 V, A at V <sub>CC1</sub> |     | 15                                    | 21   |      |

| ICC             | Supply current to TE              | Termination and receivers enabled, No load                       | TE at V <sub>TE</sub> , DE/ <del>RE</del> at 0 V                                               |     | 33                                    | 45   |      |

| Co              | Bus port capacitance (se          | e Note 4)                                                        |                                                                                                |     | 13.5                                  | 16.5 | pF   |

| Чн              | High-level input current          | DE/RE, CE                                                        | V <sub>IH</sub> = V <sub>CC</sub> or 2 V                                                       |     |                                       | 100  | μΑ   |

| ١ <sub>IL</sub> | Low-level input current           | DE/RE, CE                                                        | V <sub>IL</sub> = 0.5 V                                                                        |     |                                       | 100  | μΑ   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = V<sub>CC1</sub> = 5 V, T<sub>A</sub> = 25°C. NOTE 4: Tested in accordance with Annex G X3T9.2/855D, revision 14

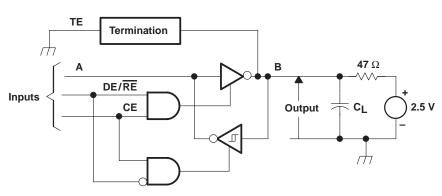

#### driver switching characteristics over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                                   | TEST CON                                                                                                                                                                         | NDITIONS                 | MIN | TYP† | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|-----|------|

| <sup>t</sup> PHL     | Propagation delay time, high- to low-level output (see Figure 4)            | C <sub>I</sub> = 15 pF                                                                                                                                                           |                          |     |      | 35  | ns   |

| <sup>t</sup> PLH     | Propagation delay time, low- to high-level output (see Figure 4)            |                                                                                                                                                                                  |                          | 15  |      | 45  | ns   |

| +                    | Skew limit <sup>‡</sup> , the maximum delay time – minimum delay            | $V_{CC} = V_{CC1} = 5 \text{ V}, \ T_A = 25^{\circ}\text{C},$<br>$C_L = 15 \text{ pF}$<br>$V_{CC} = V_{CC1} = 5 \text{ V}, \ T_A = 70^{\circ}\text{C},$<br>$C_L = 15 \text{ pF}$ |                          |     |      | 14  | ns   |

| <sup>t</sup> sk(lim) | time                                                                        |                                                                                                                                                                                  |                          |     | 14   |     | ns   |

| <sup>t</sup> sk(p)   | Pulse skew,  tpHL - tpLH                                                    | $V_{CC} = V_{CC1} = 5$                                                                                                                                                           | V, T <sub>A</sub> = 25°C |     | 8    |     | ns   |

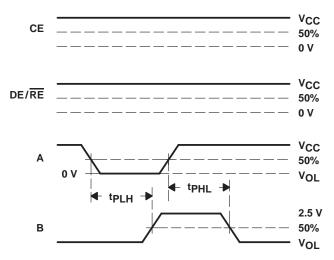

| t <sub>t</sub>       | Output transition time, 10% to 90% or 90% to 10% of the steady-state output | 15 pF < C <sub>L</sub> < 100                                                                                                                                                     | pF                       | 5   |      | 20  | ns   |

| <b>*</b>             | Propagation delay time, low-level to high-impedance                         | From CE,                                                                                                                                                                         | C <sub>L</sub> = 15 pF   | 5   |      | 150 | 20   |

| <sup>t</sup> PLZ     | output (see Figure 5)                                                       | From DE/ $\overline{RE}$ , $C_L = 15  pF$                                                                                                                                        |                          |     |      | 45  | ns   |

| tor                  | Propagation delay time, high-impedance to low-level                         | From CE,                                                                                                                                                                         | C <sub>L</sub> = 15 pF   | 5   |      | 150 | 20   |

| <sup>t</sup> PZL     | output (see Figure 5)                                                       | From DE/RE,                                                                                                                                                                      | C <sub>L</sub> = 15 pF   |     |      | 45  | ns   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = V<sub>CC1</sub> = 5 V, T<sub>A</sub> = 25°C.

<sup>‡</sup> The value for this parameter was derived from the difference between the slowest and the fastest driver delay times measured on devices from four sample wafer lots.

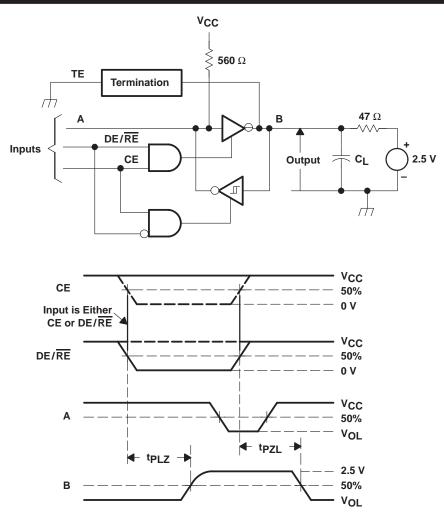

#### receiver switching characteristics over recommended of operating conditions (unless otherwise noted)

|                      | PARAMETER                                                        | TEST COND                                  | ITIONS                 | MIN | TYP† | MAX | UNIT |

|----------------------|------------------------------------------------------------------|--------------------------------------------|------------------------|-----|------|-----|------|

| <sup>t</sup> PHL     | Propagation delay time, high- to low-level output                | Coo Figure 6                               |                        | 5   |      | 20  | ns   |

| <sup>t</sup> PLH     | Propagation delay time, low- to high-level output                | See Figure 6                               |                        | 5   |      | 25  | ns   |

|                      | Skew limit <sup>‡</sup> , the maximum delay time – minimum delay | $V_{CC} = V_{CC1} = 5 V$ ,<br>See Figure 6 | T <sub>A</sub> = 25°C, |     |      | 8.5 | ns   |

| <sup>t</sup> sk(lim) | lime                                                             | $V_{CC} = V_{CC1} = 5 V,$<br>See Figure 6  | T <sub>A</sub> = 70°C, |     |      | 8.5 | ns   |

| <sup>t</sup> sk(p)   | Pulse skew,  tpHL - tpLH                                         | $V_{CC} = V_{CC1} = 5 V$ ,<br>See Figure 6 | T <sub>A</sub> = 25°C, |     | 6    |     | ns   |

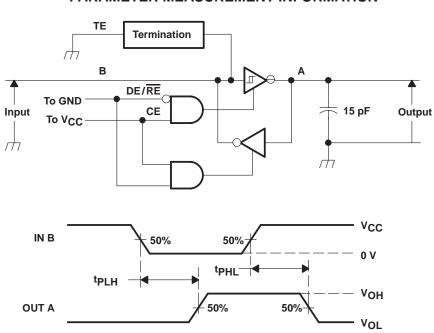

| 4                    | Propagation delay time, low-level to high-impedance              | From CE,                                   | See Figure 7           | 5   |      | 150 |      |

| <sup>t</sup> PLZ     | output                                                           | From DE/RE,                                | See Figure 7           |     |      | 45  | ns   |

| 4                    | Propagation delay time, high-impedance to low-level              | From CE,                                   | See Figure 7           | 5   |      | 150 |      |

| <sup>t</sup> PZL     | output                                                           | From DE/RE,                                | See Figure 7           |     |      | 80  | ns   |

|                      | Propagation delay time, high-level to high-impedance             | From CE,                                   | See Figure 8           | 5   |      | 150 |      |

| <sup>t</sup> PHZ     | output                                                           | From DE/RE,                                | See Figure 8           |     |      | 45  | ns   |

| 4                    | Propagation delay time, high-impedance to high-level             | From CE,                                   | See Figure 8           | 5   |      | 150 |      |

| <sup>t</sup> PZH     |                                                                  | From DE/RE,                                | See Figure 8           |     |      | 80  | ns   |

<sup>†</sup> All typical values are at  $V_{CC} = V_{CC1} = 5 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}.$

<sup>‡</sup> The value for this parameter was derived from the difference between the slowest and the fastest driver delay times measured on devices from four sample wafer lots.

#### thermal characteristics

|                 | PARAMETER                               | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|-----------------|-----------------------------------------|----------------------------|-----|-----|-----|------|

| $R_{\theta JA}$ | Junction-to-free-air thermal resistance | Board-mounted, no air flow |     | 50  |     | °C/W |

| $R_{\theta JC}$ | Junction-to-case thermal resistance     |                            |     | 12  |     | °C/W |

| T <sub>JS</sub> | Junction-shutdown temperature           |                            |     | 180 |     | °C   |

# PARAMETER MEASUREMENT INFORMATION

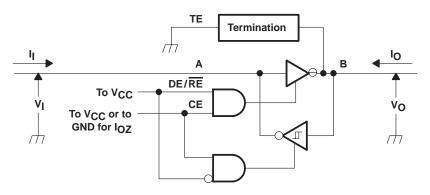

Figure 1. Driver Test Circuit Currents and Voltages.

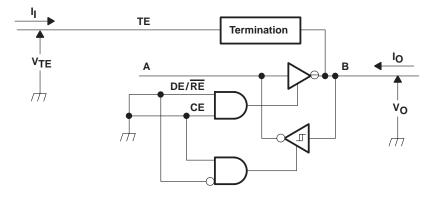

Figure 2. Active Termination Voltages, Currents, and Test Circuit.

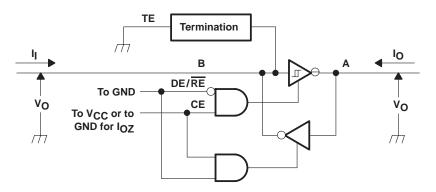

Figure 3. Receiver Voltages, Currents, and Test Circuit

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_f \le 6$  ns,  $t_f \le 6$  ns, PRR  $\le 1$  MHz, duty cycle = 50%,  $Z_O = 50 \ \Omega$ .

- B. All resistances are in ohms and  $\pm 5\%$ , unless otherwise indicated.

- C. All capacitances are in picofarads and  $\pm 10\%$ , unless otherwise indicated.

- D. All indicated voltages are  $\pm 10$  mV.

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_f \le 6$  ns,  $t_f \le 6$  ns, PRR  $\le 1$  MHz, duty cycle = 50%,  $Z_O = 50 \Omega$ .

- B. All resistances are in ohms and  $\pm 5\%$ , unless otherwise indicated.

- C. All capacitances are in picofarads and  $\pm 10\%$ , unless otherwise indicated.

- D. All indicated voltages are  $\pm 10$  mV.

#### Figure 4. Driver Delay Time Test Circuit and Waveforms

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_{f} \le 6$  ns,  $t_{f} \le 6$  ns, PRR  $\le 1$  MHz, duty cycle = 50%,  $Z_{O}$  = 50  $\Omega$ .

- B. All resistances are in ohms and  $\pm 5\%$ , unless otherwise indicated.

- C. All capacitances are in picofarads and  $\pm 10\%$ , unless otherwise indicated.

- D. All indicated voltages are  $\pm 10$  mV.

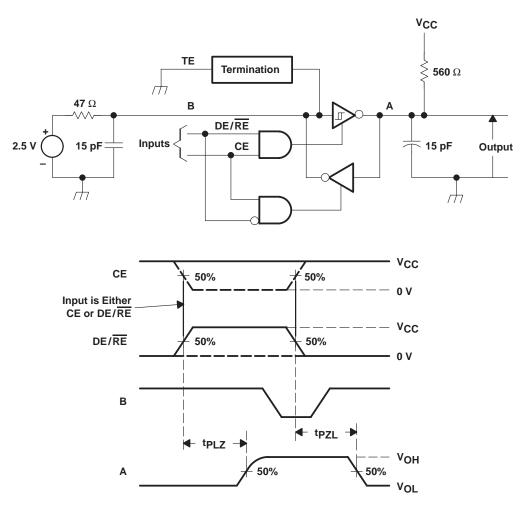

#### Figure 5. Driver Delay Time Test Circuit and Waveforms

### PARAMETER MEASUREMENT INFORMATION

NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_{f} \leq 6$  ns,  $t_{f} \leq 6$  ns, PRR  $\leq 1$  MHz, duty cycle = 50%,  $Z_O = 50 \Omega$ . B. All resistances are in ohms and ±5%, unless otherwise indicated.

- C. All capacitances are in picofarads and  $\pm 10\%$ , unless otherwise indicated.

- D. All indicated voltages are  $\pm 10$  mV.

#### Figure 6. Receiver Propagation Delay Time Test Circuit and Waveforms

# PARAMETER MEASUREMENT INFORMATION

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_r \le 6$  ns,  $t_f \le 6$  ns, PRR  $\le 1$  MHz, duty cycle = 50%,  $Z_O = 50 \ \Omega$ .

- B. All resistances are in ohms and  $\pm 5\%$ , unless otherwise indicated.

- C. All capacitances are in picofarads and  $\pm\,10\%,$  unless otherwise indicated.

- D. All indicated voltages are  $\pm 10$  mV.

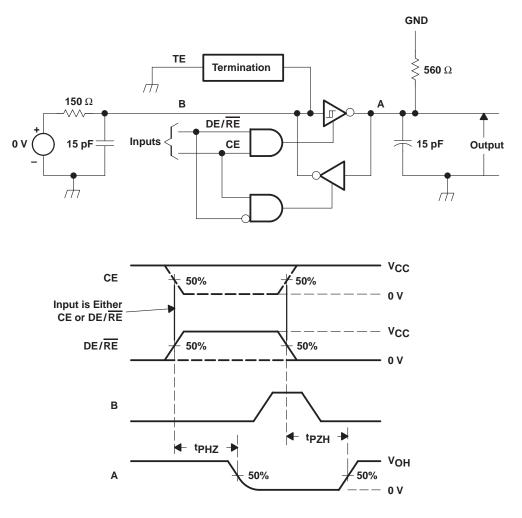

#### Figure 7. Receiver Enable and Disable Times to and From Low-Level Output Test Circuit and Waveforms

# PARAMETER MEASUREMENT INFORMATION

- NOTES: A. All input pulses are supplied by a generator having the following characteristics:  $t_f \le 6$  ns,  $t_f \le 6$  ns, PRR  $\le 1$  MHz, duty cycle = 50%,  $Z_O = 50 \Omega$ .

- B. All resistances are in ohms and  $\pm 5\%$ , unless otherwise indicated.

- C. All capacitances are in picofarads and  $\pm 10\%$ , unless otherwise indicated.

- D. All indicated voltages are  $\pm 10$  mV.

#### Figure 8. Receiver Enable and Disable Times to and From High-Level Output Test Circuit and Waveforms

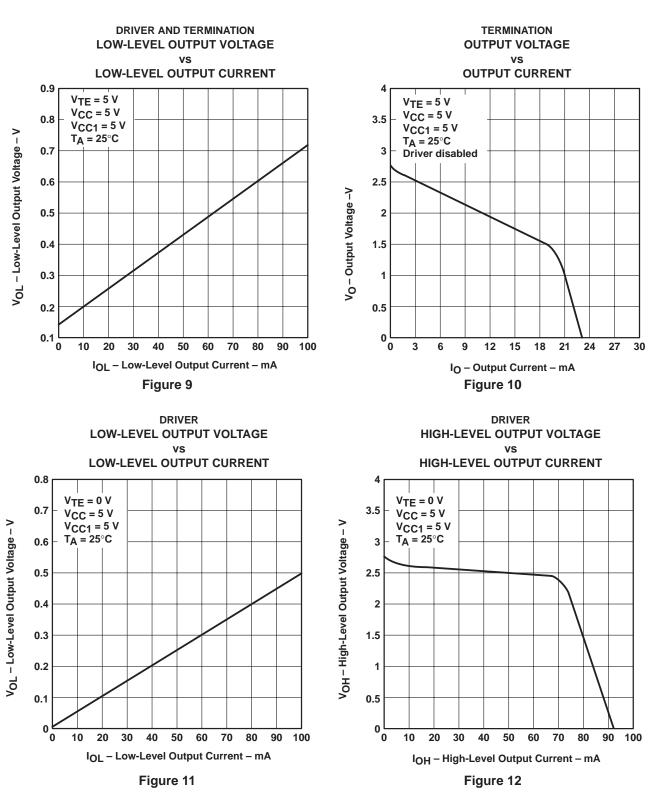

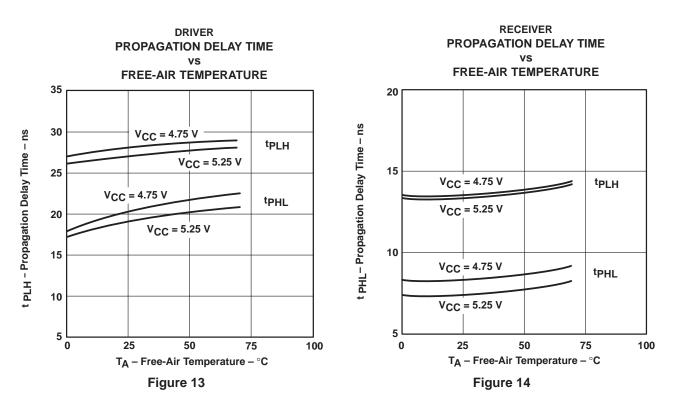

#### **TYPICAL CHARACTERISTICS**

### **TYPICAL CHARACTERISTICS**

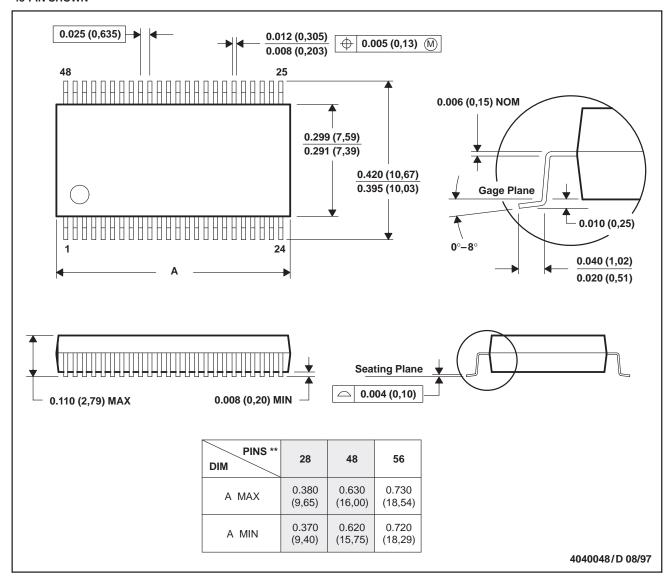

#### MECHANICAL DATA

#### PLASTIC SMALL-OUTLINE PACKAGE

DL (R-PDSO-G\*\*) 48-PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MO-118

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated