#### features

- Regulated 5 V ± 4% Output Voltage With up to 100 mA Output Current From a 1.8 V to 3.6 V Input Voltage Range

- 65-μA Quiescent Supply Current

- 0.05-μA Shutdown Current, Battery Is Isolated From Load in Shutdown

- Integrated Low-Battery or Power-Good Indicator

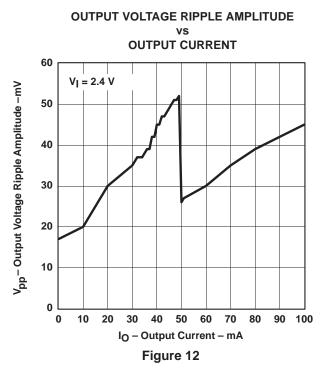

- Low Output Voltage Ripple Over Complete Output Current Range

- Easy-To-Design With Low-EMI Power Supply Since no Inductors Are Required

- Evaluation Module Available (TPS60140EVM-144)

#### description

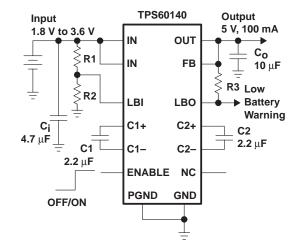

The TPS6014x step-up, regulated charge pumps generate a 5-V  $\pm 4\%$  output voltage from a 1.8 V to 3.6 V input voltage range. The devices are typically powered by two alkaline, NiCd, or NiMH battery cells and provide an output current of minimum 100 mA from a 2-V input. Only four external capacitors are needed to build a complete voltage tripler charge pump.

The devices regulate the output by using the pulse-skip topology. The controller is optimized for

#### applications

- Replaces DC/DC Converters With Inductors in Battery-Powered Applications:

- Two Battery Cells to 5 V Conversion

- Portable Instruments

- Miniature Equipment

- Backup-Battery Boost Converters

- Medical Instruments

- 5-V Smart Card Supply

- Organizers, PDAs

#### typical operating circuit

lowest output voltage ripple over the complete output current range. The output peak current and therefore the output voltage ripple are drastically reduced compared to a conventional pulse-skip topology by regulating the charge pump output resistance. At light loads the maximum output resistance is limited to assure a low quiescent current.

The TPS60140 includes a low-battery comparator that issues a warning if the battery voltage drops below a user-adjustable threshold voltage. The TPS60141 features a power-good output that goes active when the output voltage reaches 90% of its nominal value.

The logic shutdown function disables the converter, reduces the supply current to a maximum of 1  $\mu$ A and disconnects the output from the input. Special current-control circuitry prevents excessive current from being drawn from the battery during start-up. This dc-dc converter requires no inductors, therefore, EMI is of little concern. It is available in the small, thermally enhanced 20-pin TSSOP package (PWP).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated.

#### **AVAILABLE OPTIONS**

| TA            | PART NUMBER† |        | PACKAGE                         | DEVICE FEATURES         |                      |  |

|---------------|--------------|--------|---------------------------------|-------------------------|----------------------|--|

| -40°C to 85°C | TPS60140PWP  | PWP    | 20-pin thermally enhanced TSSOP | 2-cell to 5 V. 100 mA   | Low-battery detector |  |

| -40 C 10 65 C | TPS60141PWP  | 1' ''' |                                 | 2-ceii to 5 V, 100 IIIA | Power-good detector  |  |

<sup>†</sup> The PWP package is available taped and reeled. Add an R suffix to the device type (e.g. TPS60140PWPR) to order quantities of 2000 devices per reel.

#### **PWP PACKAGE (TPS60140)** PWP PACKAGE (TPS60141) (TOP VIEW) (TOP VIEW) 20 20 GND □□ 10 ☐ GND 10 ☐ GND GND □ 19 19 2 2 GND □□ ☐ GND GND □□ ☐ GND ENABLE \_\_\_ 3 18 ☐ LBI ENABLE \_\_\_ 3 18 □ NC 4 17 FB □□ 4 17 FB □ 5 5 OUT I 16 OUT $\Box$ 16 □ NC 6 C1+ □□ 15 C1+ □ 15 □ C2+ 6 □ C2+ □ IN IN $\square$ 7 14 7 14 IN $\Box$ 13 13 8 8 C1- 🗆 □ C2-C1- 🗆 □ C2-☐ PGND ☐ PGND PGND □□ 9 12 PGND $\Box$ 9 12 PGND □ ☐ PGND □ PGND 10 11 PGND $\Box$ 10 11

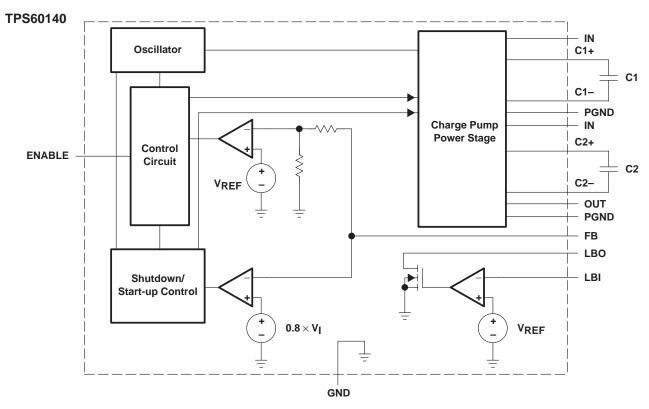

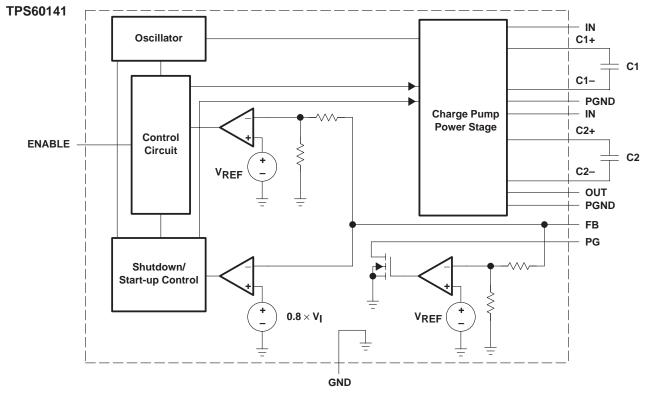

# functional block diagrams

#### **Terminal Functions**

| TERMINAL |                 | 1/0 | DECORIDATION                                                                                                                                                                                                                                                                                                              |

|----------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.             | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                               |

| C1+      | 6               |     | Positive terminal of the flying capacitor C1                                                                                                                                                                                                                                                                              |

| C1-      | 8               |     | Negative terminal of the flying capacitor C1                                                                                                                                                                                                                                                                              |

| C2+      | 15              |     | Positive terminal of the flying capacitor C2                                                                                                                                                                                                                                                                              |

| C2-      | 13              |     | Negative terminal of the flying capacitor C2                                                                                                                                                                                                                                                                              |

| ENABLE   | 3               | ı   | ENABLE input. Connect ENABLE to IN for normal operation. When ENABLE is a logic low, the device turns off and the supply current decreases to $0.05~\mu A$ . The output is disconnected from the input when the device is placed in shutdown.                                                                             |

| FB       | 4               | ı   | Feedback input. Connect FB to OUT as close to the load as possible to achieve best regulation. A resistive divider is on the chip to match the output voltage to the internal reference voltage of 1.21 V.                                                                                                                |

| GND      | 1, 2,<br>19, 20 |     | Ground. Analog ground for internal reference and control circuitry. Connect to PGND through a short trace.                                                                                                                                                                                                                |

| IN       | 7,14            | Ι   | Supply input. Bypass IN to PGND with capacitor Ci. Connect both IN terminals through a short trace.                                                                                                                                                                                                                       |

| LBO/PG   | 17              | 0   | Low battery detector output (TPS60140) or power good output (TPS60141). Open drain output of the low-battery indicator or power-good comparator. It can sink 1 mA. A 100- $k\Omega$ to 1-M $\Omega$ pullup is recommended. Leave the terminal unconnected if the low-battery or power-good detector function is not used. |

| LBI/NC   | 18              | ı   | Low battery detector input (TPS60140 only). The voltage applied to this terminal is compared to the internal 1.21-V reference voltage. Connect the terminal to ground if the low-battery comparator is not used. On the TPS60141, this terminal is not connected to the chip and should remain unconnected.               |

| NC       | 16              |     | Not connected                                                                                                                                                                                                                                                                                                             |

| OUT      | 5               | 0   | Regulated 5-V power output. Bypass OUT to PGND with the output filter capacitor C <sub>0</sub> .                                                                                                                                                                                                                          |

| PGND     | 9–12            |     | Power ground. The charge-pump current flows through this terminal. Connect all PGND terminals together.                                                                                                                                                                                                                   |

#### detailed description

The TPS6014x charge pumps provide a regulated 5-V output from a 1.8-V to 3.6-V input voltage range. They can deliver a maximum continuous load current of at least 100 mA at V<sub>I</sub> = 2 V minimum. Designed specifically for space-critical battery-powered applications, the complete charge pump circuit requires only four external capacitors.

The TPS6014x consist of an oscillator, a 1.21-V voltage reference, an internal resistive feedback circuit, an error amplifier, high current MOSFET switches, a shutdown/start-up circuit, a low-battery or power-good comparator and a control circuit (see the functional block diagrams).

### operating principle

The TPS6014x devices regulate the output voltage using an improved pulse-skip topology. In pulse-skip mode the error amplifier disables switching of the power stages when it detects an output voltage higher than 5 V. The oscillator halts and the controller skips switching cycles. The error amplifier reactivates the oscillator and starts switching of the power stages again when the output voltage drops below 5 V. The output resistance of the charge pump is controlled to improve the ripple performance. This limits the output current to the minimum that is necessary to sustain a regulated output voltage. The benefit is that the ripple performance is nearly as good as with a linear-regulation topology.

At light loads a conventional pulse-skip regulation mode is used, but the charge pump output resistance is held at a high level. The pulse-skip regulation minimizes the operating current because the charge pump does not switch continuously and hence the gate-charge losses of the MOSFETs are reduced. Additionally, all functions except voltage reference, error amplifier, and low-battery or power-good comparator are deactivated when the output is higher than 5 V. When switching is disabled by the error amplifier, the load is also isolated from the input. This improved pulse-skip control topology is also referred to as active-cycle control.

#### detailed description (continued)

#### start-up procedure and shutdown

During start-up, i.e., when ENABLE is set from logic low to logic high, the output capacitor is charged up with a limited current until the output voltage( $V_O$ ) reaches  $0.8 \times V_I$ . When the start-up comparator detects this voltage limit, the IC begins switching. This pre-charging of the output capacitor ensures a short start-up time. In addition, the inrush current into an empty output capacitor is limited because the current through the switches is limited before the charge pump starts switching.

Driving ENABLE low places the device in shutdown mode. This disables all switches, the oscillator, and control logic. The device typically draws  $0.05\,\mu\text{A}$  of supply current in this mode. Leakage current drawn from the output is as low as 1  $\mu\text{A}$  max. The device exits shutdown once ENABLE is set to a high level. When the device is in shutdown, the load is isolated from the input.

#### undervoltage lockout and short-circuit protection

The TPS6014x devices have an undervoltage lockout feature that deactivates the device and places it in shutdown mode when the input voltage falls below 1.6 V. The devices are also short-circuit protected. The output current is limited to typically 100 mA during a hard short circuit condition at the output, i.e., when  $V_O$  is GND. In this case the condition to enter the start-up mode is met, the device stops switching and controls the on-resistance of the appropriate MOSFET switches to limit the current.

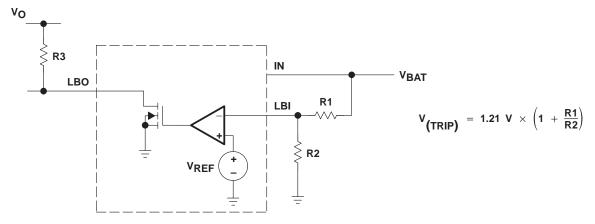

#### low-battery detector (TPS60140 only)

The internal low-battery comparator trips at 1.21 V  $\pm$ 5% when the voltage on pin LBI ramps down. The voltage V<sub>(TRIP)</sub> at which the low battery warning is issued can be adjusted with a resistive divider as shown in Figure 1. The sum of resistors R1 and R2 is recommended to be in the 100 k $\Omega$  to 1 M $\Omega$  range. When choosing R1 and R2, be aware of the input leakage current into the LBI terminal.

LBO is an open drain output. An external pullup resistor to OUT, in the 100 k $\Omega$  to 1 M $\Omega$  range, is recommended. During start-up, the LBO output signal is invalid for the first 500  $\mu$ s. LBO is high impedance when the device is disabled. If the low-battery comparator function is not used, connect LBI to ground and leave LBO unconnected.

Figure 1. Programming of the Low-Battery Comparator Trip Voltage

A 100 nF ceramic capacitor should be connected in parallel to R2 if large line transients are expected. These voltage drops can inadvertently trigger the low-battery comparator and produce a wrong low-battery warning signal at the LBO pin.

SLVS273-FEBRUARY 2000

#### low-battery detector (TPS60140 only) (continued)

Formulas to calculate the resistive divider for low battery detection, with  $V_{(LBI)} = 1.15 \text{ V}$  to 1.27 V:

$$R2 = 1 M\Omega \times \frac{V_{LBI}}{V_{Bat}}$$

(1)

$$R1 = 1 M\Omega - R2 \tag{2}$$

Formulas to calculate the minimum and maximum trip voltage:

$$V_{trip(min)} = V_{LBI(min)} \times \frac{R1_{(min)} + R2_{(max)}}{R2_{(max)}}$$

(3)

$$V_{trip(max)} = V_{LBI(max)} \times \frac{R1_{(max)} + R2_{(min)}}{R2_{(min)}}$$

(4)

Table 1. Recommended Values for the Resistive Divider From the E96 Series (±1%)

| V <sub>I</sub> /V | <b>R1/k</b> Ω | <b>R2/k</b> Ω | V <sub>(TRIP)</sub> MIN/V | V <sub>(TRIP)</sub> MAX/V |

|-------------------|---------------|---------------|---------------------------|---------------------------|

| 1.8               | 357           | 732           | 1.700                     | 1.902                     |

| 1.9               | 365           | 634           | 1.799                     | 2.016                     |

| 2.0               | 412           | 634           | 1.883                     | 2.112                     |

| 2.1               | 432           | 590           | 1.975                     | 2.219                     |

| 2.2               | 442           | 536           | 2.080                     | 2.338                     |

#### power-good detector (TPS60141)

The PG terminal is an open-drain output that is pulled low when the output is out of regulation. When the output rises to typically 90% of its nominal voltage, the power-good output is released. Power-good is high impedance in shutdown. In normal operation an external pullup resistor must be connected between PG and OUT. The resistor should be in the 100 k $\Omega$  to 1 M $\Omega$  range. If the power-good function is not used, the PG terminal should remain unconnected.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†‡

| Supply voltage range at IN to GND and PGND                      |                                              |

|-----------------------------------------------------------------|----------------------------------------------|

| Voltage range, at OUT, ENABLE, LBI, LBO, PG, FB to GND and PGND |                                              |

| Voltage range at C1+ TO GND                                     | $-0.3 \text{ V to } (V_O + 0.3 \text{ V})$   |

| Voltage range at C1– TO GND                                     | $-0.3 \text{ V to } (V_1 + 0.3 \text{ V})$   |

| Voltage range at C2+ TO GND                                     | $-0.3 \text{ V to } (V_{O} + 0.3 \text{ V})$ |

| Voltage range at C2– TO GND                                     | $-0.3 \text{ V to } (V_1 + 0.3 \text{ V})$   |

| Continuous output current                                       | 150 mA                                       |

| Storage temperature range, T <sub>stq</sub>                     | –55°C to 150°C                               |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds    |                                              |

| Maximum junction temperature, T <sub>J</sub>                    | 150°C                                        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>&</sup>lt;sup>‡</sup>V<sub>(ENABLE)</sub>, V<sub>(LBI)</sub>, V<sub>(LBO)</sub>, and V<sub>(PG)</sub> can exceed V<sub>I</sub> up to the maximum rated voltage without increasing the leakage current drawn by these inputs.

SI VS273\_ FERRUARY 2000

# recommended operating conditions

|                                                | MIN | MAX | UNIT |

|------------------------------------------------|-----|-----|------|

| Input voltage, V <sub>I</sub>                  | 1.8 | 3.6 | V    |

| Continuous output current, IOmax               |     | 100 | mA   |

| Operating junction temperature, T <sub>J</sub> |     | 125 | °C   |

# electrical characteristics at C<sub>i</sub> = 4.7 $\mu$ F, C1 = C2 = 2.2 $\mu$ F, C<sub>o</sub> = 10 $\mu$ F† at T<sub>C</sub> = -40°C to 85°C, V<sub>I</sub> = 2 V, FB = V<sub>O</sub> and ENABLE = V<sub>I</sub> (unless otherwise noted)

| PARAMETER              |                                      |          | TEST CONDITIONS                                                                                                                              | MIN                      | TYP                      | MAX                      | UNIT |

|------------------------|--------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| V(UVLO)                | Undervoltage lockout threshold       |          | T <sub>C</sub> = 25°C                                                                                                                        |                          | 1.6                      | 1.8                      | V    |

| I <sub>O</sub> max     | Maximum continuous output current    |          |                                                                                                                                              | 100                      |                          |                          | mA   |

| Vo                     | Output voltage                       |          | 1.8 V < V <sub>I</sub> < 2 V,<br>V <sub>O</sub> Start-up = 5 V,<br>0 < I <sub>O</sub> < I <sub>O</sub> max/2<br>T <sub>C</sub> = 0°C to 70°C | 4.8                      |                          | 5.2                      | V    |

|                        |                                      |          | 2 V < V <sub>I</sub> < 3.6 V,<br>0 < I <sub>O</sub> < I <sub>O</sub> max                                                                     | 4.8                      |                          | 5.2                      |      |

| l <sub>lkg</sub> (OUT) | Output leakage current               |          | $V_I = 2.4 \text{ V}, V_{(ENABLE)} = GND$                                                                                                    |                          |                          | 1                        | μΑ   |

| IQ                     | Quiescent current (no-load input cur | rent)    | V <sub>I</sub> = 2.4 V                                                                                                                       |                          | 65                       | 90                       | μΑ   |

| I(SD)                  | Shutdown current                     |          | $V_I = 2.4 \text{ V}, V_{(ENABLE)} = GND$                                                                                                    |                          | 0.05                     | 1                        | μΑ   |

| f(OSC)                 | Oscillator frequency                 |          |                                                                                                                                              | 210                      | 320                      | 450                      | kHz  |

| V <sub>IL</sub>        | ENABLE input voltage low             |          | V <sub>I</sub> = 1.8 V                                                                                                                       |                          |                          | $0.3 \times V_{I}$       | V    |

| VIH                    | ENABLE input voltage high            |          | V <sub>I</sub> = 3.6 V                                                                                                                       | $0.7 \times V_{I}$       |                          |                          | V    |

| lkg(ENABLE)            | ENABLE input leakage current         |          | V(ENABLE) = GND or VI                                                                                                                        |                          | 0.01                     | 0.1                      | μΑ   |

|                        | Output load regulation               |          | $V_I = 2.4 \text{ V},$<br>1 mA < I <sub>O</sub> < I <sub>O</sub> max,<br>$T_C = 25^{\circ}\text{C}$                                          |                          | 0.003                    |                          | %/mA |

|                        | Output line regulation               |          | 2 V < V <sub>I</sub> < 3.6 V,<br>V <sub>O</sub> = 5 V: I <sub>O</sub> = 75 mA,<br>T <sub>C</sub> = 25°C                                      |                          | 0.08                     |                          | %/V  |

| I(SC)                  | Short circuit current limit          |          | $V_I < 2.4 \text{ V},  V_O = 0 \text{ V},$<br>$T_C = 25^{\circ}\text{C}$                                                                     |                          | 100                      |                          | mA   |

| V(TRIP,LBI)            | LBI trip voltage                     | TPS60140 | $V_{\parallel}$ = 1.8 V to 2.2 V,<br>Hysteresis 0.8% for rising LBI<br>voltage,<br>$T_{C}$ = 0°C to 70°C                                     | 1.15                     | 1.21                     | 1.27                     | V    |

| I <sub>I(LBI)</sub>    | LBI input current                    | TPS60140 | LBI = 1.3 V                                                                                                                                  |                          | 20                       | 100                      | nA   |

| VO(LBO)                | LBO output voltage low <sup>‡</sup>  | TPS60140 | V <sub>(LBI)</sub> = 0 V,<br>I <sub>(LBO,SINK)</sub> = 1 mA                                                                                  |                          |                          | 0.4                      | V    |

| I <sub>lkg</sub> (LBO) | LBO output leakage current           | TPS60140 | $V_{(LBI)} = 1.3 \text{ V}, \ V_{(LBO)} = 5 \text{ V}$                                                                                       |                          | 0.01                     | 0.1                      | μΑ   |

| V(TRIP,PG)             | Power-good trip voltage              | TPS60141 | $T_C = 0$ °C to $70$ °C                                                                                                                      | 0.86 ×<br>V <sub>O</sub> | 0.90 ×<br>V <sub>O</sub> | 0.94 ×<br>V <sub>O</sub> | V    |

| V <sub>hys</sub> (PG)  | Power-good trip voltage hysteresis   | TPS60141 | V <sub>O</sub> ramping down,<br>T <sub>C</sub> = 0°C to 70°C                                                                                 |                          | 0.8%                     |                          |      |

| V <sub>O(PG)</sub>     | Power-good output voltage low        | TPS60141 | V <sub>O</sub> = 0 V, I <sub>(PG,SINK)</sub> = 1 mA                                                                                          |                          |                          | 0.4                      | V    |

| I <sub>lkg(PG)</sub>   | Power-good leakage current           | TPS60141 | $V_0 = 5 \text{ V}, V_{(PG)} = 5 \text{ V}$                                                                                                  |                          | 0.01                     | 0.1                      | μΑ   |

<sup>&</sup>lt;sup>†</sup> All capacitors are ceramic capacitors of the type X5R or X7R.

$<sup>\</sup>mbox{$^{\ddagger}$}$  During start-up the LBO signal is invalid for the first 500  $\mu s.$

# PARAMETER MEASUREMENT INFORMATION

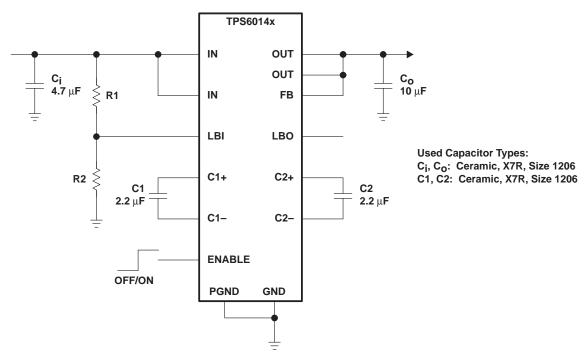

Figure 2. Circuit Used For Typical Characteristics Measurements

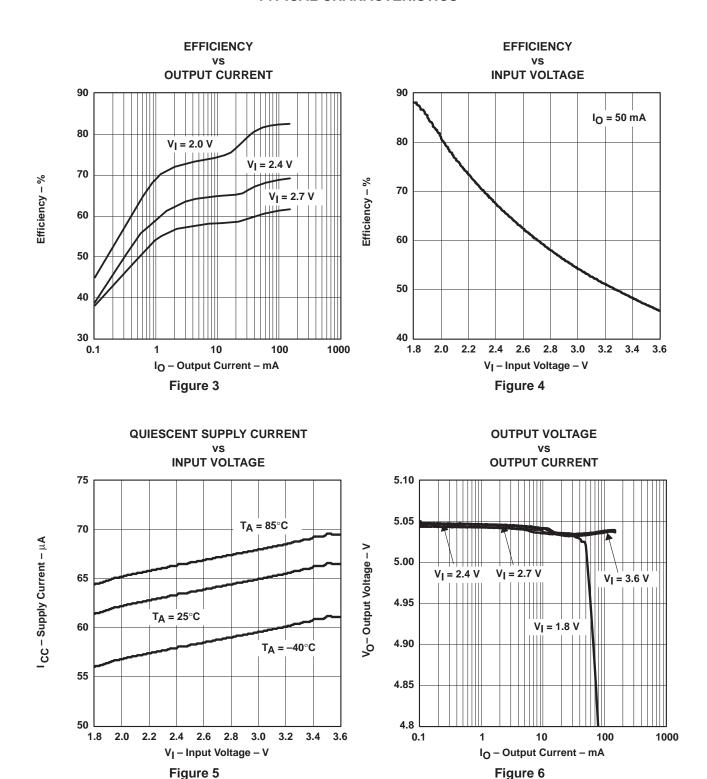

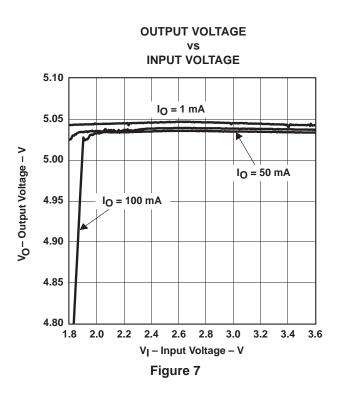

# **TYPICAL CHARACTERISTICS**

# **Table of Graphs**

|                |                                 |                           | FIGURE |

|----------------|---------------------------------|---------------------------|--------|

| _              |                                 | vs Output Current         | 3      |

| η              | Efficiency                      | vs Input Voltage          | 4      |

| IQ             | Quiescent Supply Current        | vs Input Voltage          | 5      |

| V <sub>a</sub> | Output Voltage                  | vs Output Current         | 6      |

| Vo             | Output Voltage                  | vs Input Voltage          | 7      |

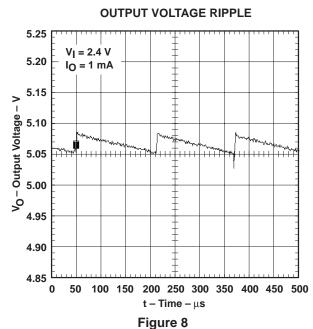

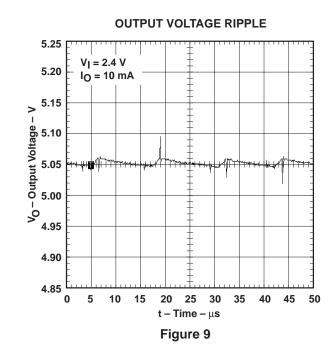

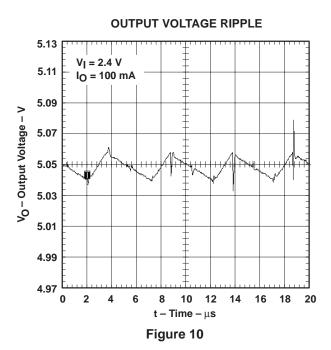

| VO             | Output Voltage Ripple           |                           | 8,9,10 |

| Vpp            | Output Voltage Ripple Amplitude | vs Input Voltage          | 11     |

| \vPP           |                                 | vs Output Current         | 12     |

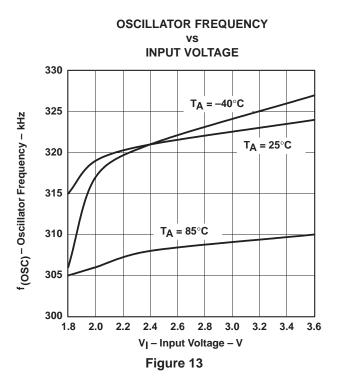

| f(OSC)         | Oscillator Frequency            | vs Input Voltage          | 13     |

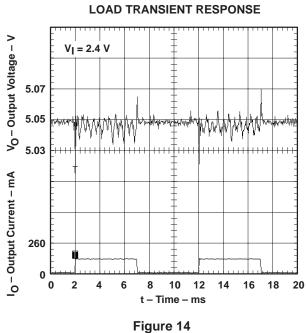

|                | Load Transient Response         |                           | 14     |

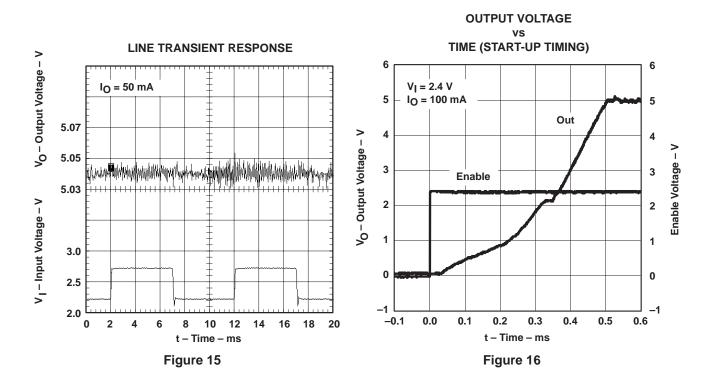

|                | Line Transient Response         |                           | 15     |

| VO             | Output Voltage                  | vs Time (Start-up Timing) | 16     |

### TYPICAL CHARACTERISTICS

#### **TYPICAL CHARACTERISTICS**

#### TYPICAL CHARACTERISTICS

# **OUTPUT VOLTAGE RIPPLE AMPLITUDE INPUT VOLTAGE** 60 Vpp – Output Voltage Ripple Amplitude –mV I<sub>O</sub> = 100 mA 50 40 30 I<sub>O</sub> = 10 mA 20 I<sub>O</sub> = 1 mA 10 0 2.2 2.6 3.4 2.0 2.8 3.0 1.8 V<sub>I</sub> - Input Voltage - V Figure 11

#### TYPICAL CHARACTERISTICS

#### **APPLICATION INFORMATION**

#### capacitor selection

The TPS6014x requires only four external capacitors as shown in the basic application circuit. Their capacitance values are closely linked to the output current and output ripple requirements. For lowest ripple, low ESR ( $<0.1~\Omega$ ) capacitors should be used at the input and output of the charge pump.

The input capacitor improves system efficiency by reducing the input impedance. It also stabilizes the input current of the power source. The input capacitor should be chosen according to the power supply used and the distance from the power source to the converter IC. The input capacitor selection also depends on the output ripple requirements.  $C_i$  is recommended to be about two to four times as large as the flying capacitors. The lower the ESR of the input capacitor  $C_i$  the lower is the output ripple.

The output capacitor  $C_0$  can be selected from 2-times to 50-times larger than the flying capacitor, depending on the ripple tolerance. The larger  $C_0$  and the lower its ESR, the lower will be the output voltage ripple.

Generally, the flying capacitors will be the smallest. Only ceramic capacitors are recommended because of their low ESR and because they retain their capacitance at the switching frequency. Please be aware that, depending on the material used to manufacture them, ceramic capacitors might lose their capacitance over temperature and voltage. Ceramic capacitors of type X7R or X5R material will keep their capacitance over temperature and voltage, whereas Z5U or Y5V-type capacitors will decrease in capacitance. Table 2 lists recommended capacitor values.

#### **APPLICATION INFORMATION**

### capacitor selection (continued)

**Table 2. Recommended Capacitor Values**

| I <sub>O</sub><br>(mA) | C <sub>i</sub><br>(μF) | C <sub>(xF)</sub><br>(μF) | C <sub>o</sub><br>(μF) | V <sub>PP</sub> TYP<br>(mV) |

|------------------------|------------------------|---------------------------|------------------------|-----------------------------|

| 0 – 50                 | 4.7                    | 2.2                       | 4.7                    | 40                          |

| 0 – 100                | 4.7                    | 2.2                       | 10                     | 40                          |

| 0 – 100                | 4.7                    | 2.2                       | 22                     | 18                          |

If the measured output voltage ripple is too high for the application, improvements can be made. The first step is to increase the capacitance at the output. If the ripple is still too high, the second step would be to increase the capacitance at the input. For lower output currents, lower value flying capacitors can be used. Tables 3 and 4 lists the manufacturers of recommended capacitors.

**Table 3. Recommended Capacitors**

| MANUFACTURER PART NUMBER |                 | CAPACITANCE | CASE SIZE | TYPE    |

|--------------------------|-----------------|-------------|-----------|---------|

| Taiyo Yuden              | LMK212BJ105KG-T | 1 μF        | 0805      | Ceramic |

|                          | LMK212BJ225MG-T | 2.2 μF      | 0805      | Ceramic |

|                          | LMK316BJ475KL-T | 4.7 μF      | 1206      | Ceramic |

|                          | LMK325BJ106MN-T | 10 μF       | 1210      | Ceramic |

|                          | LMK432226MM-T   | 22 μF       | 1812      | Ceramic |

| AVX                      | 0805ZC105KAT2A  | 1 μF        | 0805      | Ceramic |

|                          | 1206ZC225KAT2A  | 2.2 μF      | 1206      | Ceramic |

NOTE: Case code compatibility with EIA 535BAAC and CECC30801 molded chips.

**Table 4. Recommended Capacitor Manufacturers**

| MANUFACTURER | CAPACITOR TYPE  | INTERNET SITE           |

|--------------|-----------------|-------------------------|

| Taiyo Yuden  | X7R/X5R ceramic | http://www.t-yuden.com/ |

| AVX          | X7R/X5R ceramic | http://www.avxcorp.com/ |

#### APPLICATION INFORMATION

### power dissipation

The power dissipated in the TPS6014x depends mainly on input voltage and output current and is described by the following:

$$P_{(DISS)} = I_O \times (3 \times V_I - V_O)$$

(5)

By observation of the above equation, it can be seen that the power dissipation is worse for the highest input voltage  $V_I$  and the highest output current  $I_O$ . For an input voltage of 3.6 V and an output current of 100 mA, the calculated power dissipation  $P_{OISS}$  is 580 mW. This is also the point where the charge pump operates with its lowest efficiency, which is only 45%, and hence with the highest power losses.

$P_{(DISS)}$  must be less than that allowed by the package rating. The thermal resistance junction to ambient of the thermally enhanced TSSOP is 178°C/W for an unsoldered package. The thermal resistance junction to case, with the exposed thermal pad soldered to an infinitive heat sink, is 3.5°C/W.

With the recommended maximum junction temperature of 125°C and an assumed maximum ambient operating temperature of 85°C, the maximum allowed thermal resistance junction to ambient of the system can be calculated as follows:

$$R_{\Theta JA} max = \frac{T_J max - T_A}{P(DISS)^{max}} = \frac{125^{\circ}C - 85^{\circ}C}{580 \text{ mW}} = 69^{\circ}C/W$$

(6)

Using a board layout as described in the application information section,  $R_{\Theta JA}$  is typically 56°C/W for an unsoldered PowerPad and 41°C/W for a soldered PowerPad.

For more information, refer to the PowerPad application report (Literature Number: SLMA002).

#### **APPLICATION INFORMATION**

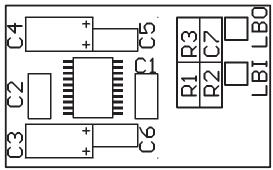

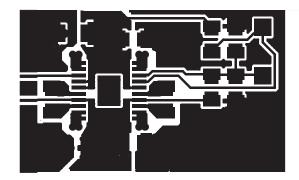

#### layout and board space

Careful board layout is necessary due to the high transient currents and switching frequency of the converter. All capacitors should be soldered in close proximity to the IC. Connect ground and power ground terminals through a short, low-impedance trace. A PCB layout proposal for a two-layer board is given in Figure 17. The bottom layer of the board carries only ground potential for best performance. The layout also provides improved thermal performance as the exposed lead frame of the PowerPad package is soldered to the PCB.

An evaluation module for the TPS60140 is available and can be ordered under product code TPS60140EVM–144. The EVM uses the layout shown in Figure 17.

NOTE: Actual size is 15 mm x 25 mm.

Figure 17. Recommended Component Placement and Board Layout

| IC1                        | TPS6014x                        |  |

|----------------------------|---------------------------------|--|

| C1, C2                     | Flying capacitors               |  |

| C3, C6                     | Input capacitors                |  |

| C4, C5                     | Output capacitors               |  |

| C7                         | Stabilization capacitor for LBI |  |

| R1, R2                     | Resistive divider for LBI       |  |

| R3 Pullup resistor for LBO |                                 |  |

**Table 5. Component Identification**

The best performance of the converter is achieved with additional bypass capacitors C5 and C6 at the input and output. Capacitor C7 should be included if the large line transients are expected. The capacitors are not required. They can be omitted in most applications.

SLVS273- FEBRUARY 2000

# **APPLICATION INFORMATION**

#### related information

### application reports

For more application information see:

- PowerPAD Application Report, Literature Number SLMA002

- TPS6010x/TPS6011x Charge Pump Application Report, Literature Number SLVA070

# device family products

Other devices in this family are:

| PART<br>NUMBER | DESCRIPTION                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------|

| TPS60100       | Regulated 3.3-V, 200-mA low-noise charge pump dc-dc converter                                   |

| TPS60101       | Regulated 3.3-V, 100-mA low-noise charge pump dc-dc converter                                   |

| TPS60110       | Regulated 5-V, 300-mA low-noise charge pump dc-dc converter                                     |

| TPS60111       | Regulated 5-V, 150-mA low-noise charge pump dc-dc converter                                     |

| TPS60120       | Regulated 3.3-V, 200-mA high efficiency charge pump dc-dc converter with low-battery comparator |

| TPS60121       | Regulated 3.3-V, 200-mA high efficiency charge pump dc-dc converter with power-good comparator  |

| TPS60122       | Regulated 3.3-V, 100-mA high efficiency charge pump dc-dc converter with low-battery comparator |

| TPS60123       | Regulated 3.3-V, 100-mA high efficiency charge pump dc-dc converter with power-good comparator  |

| TPS60130       | Regulated 5-V, 300-mA high efficiency charge pump dc-dc converter with low-battery comparator   |

| TPS60131       | Regulated 5-V, 300-mA high efficiency charge pump dc-dc converter with power-good comparator    |

| TPS60132       | Regulated 5-V, 150-mA high efficiency charge pump dc-dc converter with low-battery comparator   |

| TPS60133       | Regulated 5-V, 150-mA high efficiency charge pump dc-dc converter with power-good comparator    |

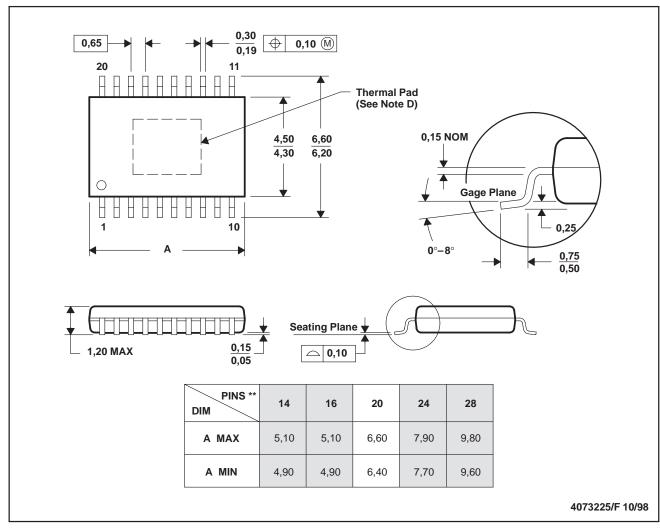

#### **MECHANICAL DATA**

## PWP (R-PDSO-G\*\*)

#### PowerPAD™ PLASTIC SMALL-OUTLINE

**20 PINS SHOWN**

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions.

- D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments Incorporated.

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated