# High Efficiency Linear Regulator

# FEATURES

- Minimum VIN VOUT Less Than 0.5V At 5A Load With External Pass Device

- Equally Usable For Either Positive or Negative Regulator Design

- Adjustable Low Threshold Current Sense Amplifier

- Under And Over-Voltage Fault Alert With Programmable Delay

- Over-Voltage Fault Latch With 100mA Crowbar Drive Output

# DESCRIPTION

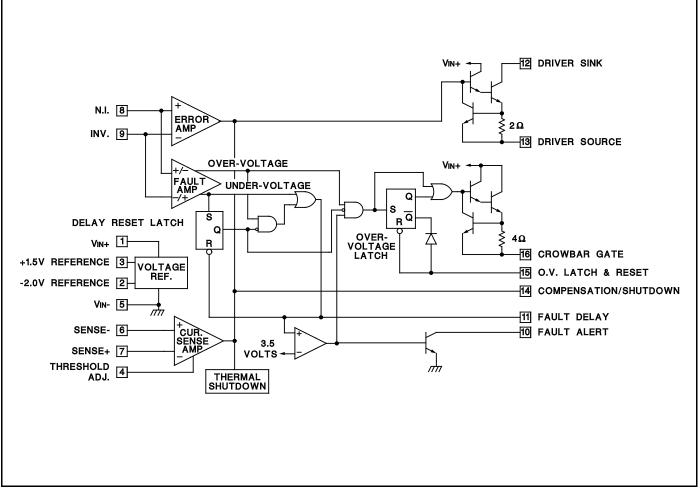

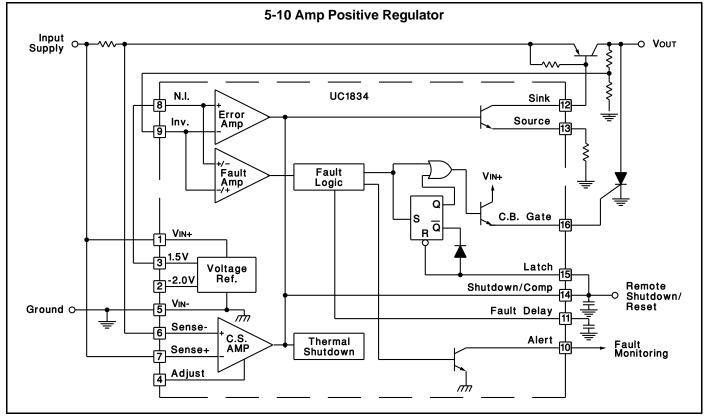

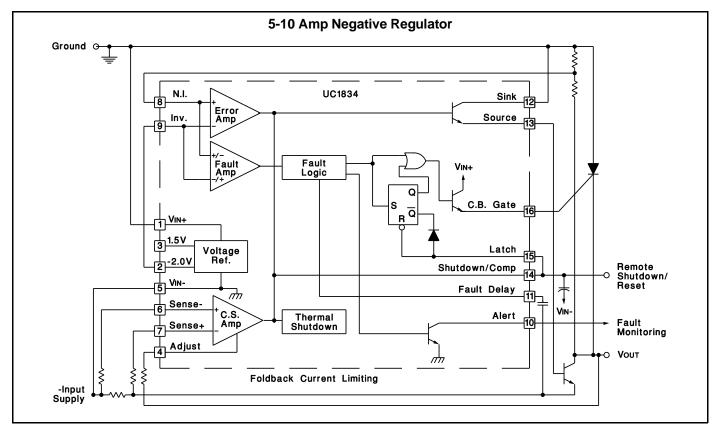

The UC1834 family of integrated circuits is optimized for the design of low input-output differential linear regulators. A high gain amplifier and 200mA sink or source drive outputs facilitate high output current designs which use an external pass device. With both positive and negative precision references, either polarity of regulator can be implemented. A current sense amplifier with a low, adjustable, threshold can be used to sense and limit currents in either the positive or negative supply lines.

In addition, this series of parts has a fault monitoring circuit which senses both under and over-voltage fault conditions. After a user defined delay for transient rejection, this circuitry provides a fault alert output for either fault condition. In the over-voltage case, a 100mA crowbar output is activated. An over-voltage latch will maintain the crowbar output and can be used to shutdown the driver outputs. System control to the device can be accommodated at a single input which will act as both a supply reset and remote shutdown terminal. These die are protected against excessive power dissipation by an internal thermal shutdown function.

# BLOCK DIAGRAM

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Input Supply Voltage, V <sub>IN</sub> + 40V |

|---------------------------------------------|

| Driver Current                              |

| Driver Source to Sink Voltage 40V           |

| Crowbar Current                             |

| +1.5V Reference Output Current              |

| Fault Alert Voltage 40V                     |

| Fault Alert Current 15mA                    |

| Error Amplifier Inputs –0.5V to 35V         |

| Current Sense Inputs –0.5V to 40V           |

| O.V. Latch Output Voltage –0.5V to 40V      |

| O.V. Latch Output Current 15mA              |

| Power Dissipation at TA = 25°C 1000mW                    |

|----------------------------------------------------------|

| 1                                                        |

| Power Dissipation at Tc = 25°C 2000mW                    |

| Operating Junction Temperature –55°C to +150°C           |

| Storage Temperature                                      |

| Lead Temperature (soldering, 10 seconds) 300°C           |

| Note 1: Voltages are reference to VIN–, Pin 5.           |

| Currents are positive into pagative out of the specified |

Currents are positive into, negative out of the specified terminals. Consult Packaging section of Databook for thermal

limitations and considerations of package.

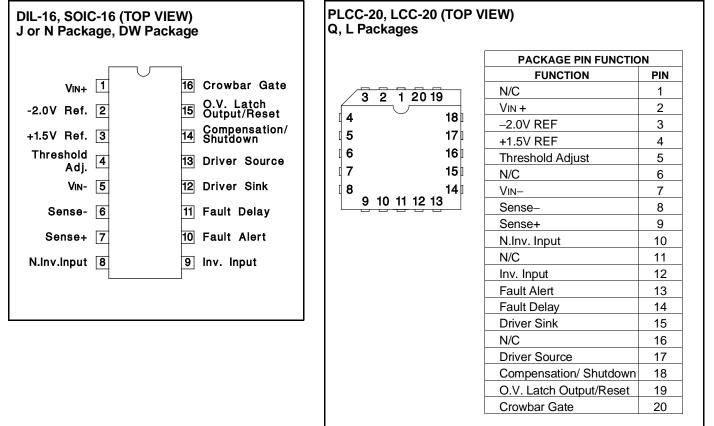

#### **CONNECTION DIAGRAMS**

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for TA=-55°C to +125°C for the UC1834, -40°C to +85°C for the UC2834, and 0°C to +70°C for the UC3834. VIN+ = 15V, VIN- = 0V, TA = TJ.

| PARAMETER                                  | TEST CONDITIONS                                                  | UC1834<br>UC2834 |      |       | UC3834 |      |       | UNITS |

|--------------------------------------------|------------------------------------------------------------------|------------------|------|-------|--------|------|-------|-------|

|                                            |                                                                  | MIN              | TYP  | MAX   | MIN    | TYP  | MAX   |       |

| Turn-on Characteristics                    |                                                                  |                  |      |       |        |      |       |       |

| Standby Supply Current                     |                                                                  |                  | 5.5  | 7     |        | 5.5  | 10    | mA    |

| +1.5 Volt Reference                        |                                                                  |                  |      |       |        | 1    |       | -     |

| Output Voltage                             | TJ = 25°C                                                        | 1.485            | 1.5  | 1.515 | 1.47   | 1.5  | 1.53  | V     |

|                                            | $T_{J}(MIN) \leq T_{J} \leq T_{J}(MAX)$                          | 1.47             |      | 1.53  | 1.455  |      | 1.545 |       |

| Line Regulation                            | VIN+ = 5 to 35V                                                  |                  | 1    | 10    |        | 1    | 15    | mV    |

| Load Regulation                            | IOUT = 0 to $2mA$                                                |                  | 1    | 10    |        | 1    | 15    | mV    |

| -2.0 Volt Reference (Note 2)               | r                                                                |                  | 1    | 1     |        | 1    | 1     |       |

| Output Voltage (Referenced                 | $T_J = 25^{\circ}C$                                              | -2.04            | -2   | -1.96 | -2.06  | -2   | -1.94 | V     |

| to Vin⁺)                                   | $T_{J}(MIN) \leq T_{J} \leq T_{J}(MAX)$                          | -2.06            |      | -1.94 | -2.08  |      | -1.92 |       |

| Line Regulation                            | VIN+ = 5 to 35V                                                  |                  | 1.5  | 15    |        | 1.5  | 20    | mV    |

| Output Impedance                           |                                                                  |                  | 2.3  |       |        | 2.3  |       | kΩ    |

| Error Amplifier Section                    |                                                                  | -                |      |       |        |      |       | -     |

| Input Offset Voltage                       | Vсм = 1.5V                                                       |                  | 1    | 6     |        | 1    | 10    | mV    |

| Input Bias Current                         | Vcm = 1.5V                                                       |                  | -1   | -4    |        | -1   | -8    | μA    |

| Input Offset Current                       | Vcm = 1.5V                                                       |                  | 0.1  | 1     |        | 0.1  | 2     | μA    |

|                                            | Output @ Pin 14, Pin 12 = VIN+<br>Pin 13, 20 $\Omega$ to VIN–    | 50               | 65   |       | 50     | 65   |       | dB    |

| CMRR                                       | Vcm = 0.5 to 33V, V <sub>IN+</sub> = 35V                         | 60               | 80   |       | 60     | 80   |       | dB    |

| PSRR                                       | VIN+ = 5 to 35V, VCM = 1.5V                                      | 70               | 100  |       | 70     | 100  |       | dB    |

| Driver Section                             | · · · · ·                                                        |                  |      |       |        |      |       |       |

| Maximum Output Current                     |                                                                  | 200              | 350  |       | 200    | 350  |       | mA    |

| Saturation Voltage                         | IOUT = 100mA                                                     |                  | 0.5  | 1.2   |        | 0.5  | 1.5   | V     |

| Output Leakage Current                     | Pin 12 = 35V, Pin 13 = VIN-, Pin 14 = VIN-                       |                  | 0.1  | 50    |        | 0.1  | 50    | μA    |

| Shutdown Input Voltage<br>at Pin 14        | IOUT $\leq$ 100µA, Pin 13 = VIN-, Pin 12 = VIN+                  | 0.4              | 1    |       | 0.4    | 1    |       | V     |

| Shutdown Input Current at Pin 14           | Pin 14 = VIN–, Pin 12 = VIN+<br>IOUT $\leq$ 100µA, Pin 13 = VIN– |                  | -100 | -150  |        | -100 | -150  | μΑ    |

| Thermal Shutdown (Note 3)                  |                                                                  |                  | 165  |       |        | 165  |       | °C    |

| Fault Amplifier Section                    |                                                                  |                  |      |       |        |      |       |       |

| Under- and Over-Voltage<br>Fault Threshold | VCM = 1.5V, @ E/A Inputs                                         | 120              | 150  | 180   | 110    | 150  | 190   | mV    |

| Common Mode Sensitivity                    | VIN+ = 35V, VCM = 1.5 to 33V                                     |                  | -0.4 | -0.8  |        | -0.4 | -1.0  | %/v   |

| Supply Sensitivity                         | Vсм = 1.5V, Vін+ = 5 to 35V                                      |                  | -0.5 | -1.0  |        | -0.5 | -1.2  | %/V   |

| Fault Delay                                |                                                                  | 30               | 45   | 60    | 30     | 45   | 60    | ms/μF |

| Fault Alert Output Current                 |                                                                  | 2                | 5    |       | 2      | 5    |       | mA    |

| Fault Alert Saturation Voltage             | IOUT = 1mA                                                       |                  | 0.2  | 0.5   |        | 0.2  | 0.5   | V     |

| O.V. Latch Output Current                  |                                                                  | 2                | 4    | -     | 2      | 4    | _     | mA    |

| O.V. Latch Saturation Voltage              | IOUT = 1mA                                                       |                  | 1.0  | 1.3   |        | 1.0  | 1.3   | V     |

| O.V. Latch Output Reset<br>Voltage         |                                                                  | 0.3              | 0.4  | 0.6   | 0.3    | 0.4  | 0.6   | V     |

| Crowbar Gate Current                       |                                                                  | -100             | -175 |       | -100   | -175 |       | mA    |

| Crowbar Gate Leakage<br>Current            | VIN+ = 35V, Pin 16 = VIN-                                        |                  | -0.5 | -50   |        | -0.5 | -50   | μA    |

Note 2: When using both the 1.5V and -2.0V references the current out of pin 3 should be balanced by an equivalent current into Pin 2. The -2.0V output will change -2.3mV per  $\mu$ A of imbalance.

Note 3: Thermal shutdown turns off the driver. If Pin 15 (O.V. Latch Output) is tied to Pin 14 (Compensation/Shutdown) the O.V. Latch will be reset.

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for TA=-55°C to +125°C for the UC1834, -40°C to +85°C for the UC2834, and 0°C to +70°C for the UC3834. VIN+ = 15V, VIN- = 0V. TA = TJ

| PARAMETER                              | TEST CONDITIONS                         | UC1834<br>UC2834 |      |      | UC3834 |      |      | UNITS |

|----------------------------------------|-----------------------------------------|------------------|------|------|--------|------|------|-------|

|                                        |                                         | MIN              | TYP  | MAX  | MIN    | TYP  | MAX  |       |

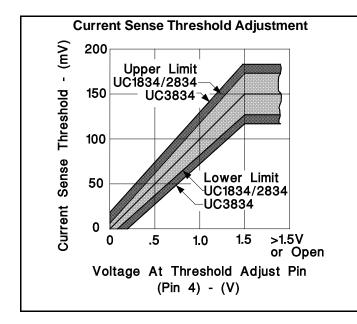

| <b>Current Sense Amplifier Section</b> | on                                      |                  |      |      |        |      |      |       |

| Threshold Voltage                      | Pin 4 Open, Vcм = VIN+ or VIN–          | 130              | 150  | 170  | 120    | 150  | 180  | mV    |

|                                        | Pin 4 = 0.5V, $V_{CM}$ = VIN+ or VIN-   | 40               | 50   | 60   | 30     | 50   | 70   |       |

| Threshold Supply Sensitivity           | Pin 4 Open, VCM = VIN-, VIN+ = 5 to 35V |                  | -0.1 | -0.3 |        | -0.1 | -0.5 | %/V   |

| Adj. Input Current                     | Pin 4 = 0.5V                            |                  | -2   | -10  |        | -2   | -10  | μA    |

| Sense Input Bias Current               | VCM = VIN+                              |                  | 100  | 200  |        | 100  | 200  | μA    |

|                                        | VCM = VIN-                              |                  | -100 | -200 |        | -100 | -200 |       |

#### **APPLICATION INFORMATION**

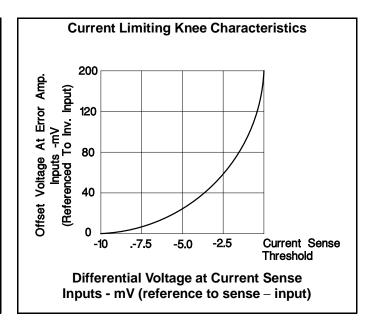

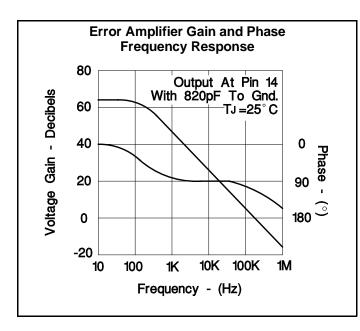

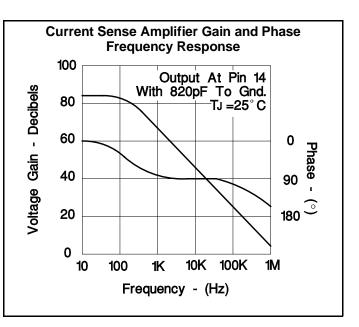

Both the current sense and error amplifiers on the UC1834 are transconductance type amplifiers. As a result, their voltage gain is a direct function of the load impedance at their shared output pin, Pin 14. Their small signal voltage gain as a function of load and frequency is nominally given by;

$$Av E/A = \frac{Z_L(f)}{700\Omega} \text{ and } Av C. S./A = \frac{Z_L(f)}{70\Omega}$$

for:  $f \le 500 \text{kHz}$  and  $|Z_L(f)| \le 1 M\Omega$

Where:

Av=Small Signal Voltage Gain to pin 14. ZL(f) = Load Impedance at Pin 14.

The UC1834 fault delay circuitry prevents the fault outputs from responding to transient fault conditions. The delay reset latch insures that the full, user defined, delay passes before an over-voltage fault response occurs. This prevents unnecessary crowbar, or latched-off conditions, from occurring following sharp under-voltage to over-voltage transients. The crowbar output on the UC1834 is activated following a sustained over-voltage condition. The crowbar output remains high as long as the fault condition persists, or, as long as the over-voltage latch is set. The latch is set with an over-voltage fault if the voltage at Pin 15 is above the latch reset threshold, typically 0.4V. When the latch is set, its Q- output will pull Pin 15 low through a series diode. As long as a nominal pull-up load exists, the series diode prevents Q- from pulling Pin 15 below the reset threshold. However, Pin 15 is pulled low enough to disable the driver outputs if Pins 15 and 14 are tied together. With Pin 15 and 14 common, the regulator will latch off in response to an over-voltage fault. If the fault condition is cleared and Pins 14 and 15 are momentarily pulled below the latch reset threshold, the driver outputs are re-enabled.

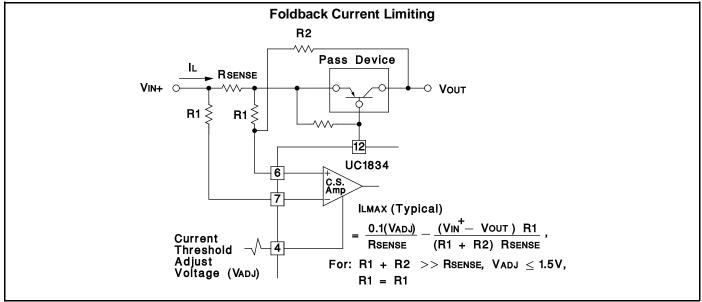

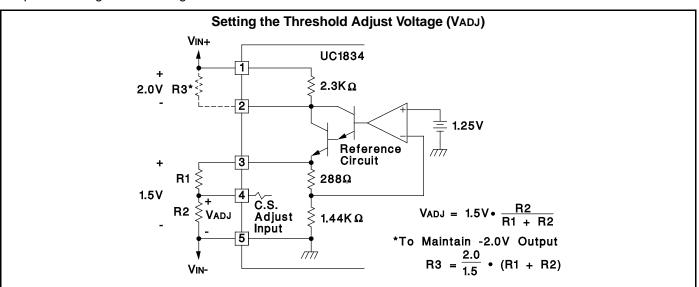

#### **TYPICAL APPLICATIONS**

UNITRODE CORPORATION 7 CONTINENTAL BLVD. • MERRIMACK, NH 03054 TEL. (603) 424-2410 • FAX (603) 424-3460

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated