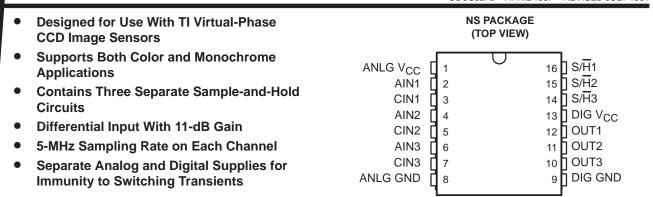

# TL1593C 3-CHANNEL SAMPLE-AND-HOLD CIRCUIT

SOCS027B - APRIL 1987 - REVISED JULY 1991

#### description

The TL1593C is a three-channel sample-and-hold integrated circuit designed for use in processing video signals generated by TI virtual-phase CCD image sensors. It can be used with one-, two-, and three-channel color and monochrome TI virtual-phase CCDs.

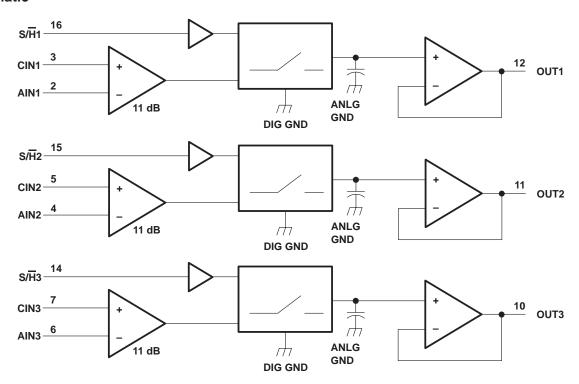

Each sample-and-hold channel consists of a differential-input buffer, a digitally controlled switch, and an output buffer that has high impedance. Separate supply and ground pins are provided for the analog and digital sections to ensure optimum isolation. Internal-hold capacitors are included to reduce the external parts count. The differential inputs allow the amplifier return pin of the imager to be connected to CIN of the sample-and-hold circuit to obtain common-mode rejection for antiblooming clock transients in the CCD. The analog inputs should be capacitively coupled from the CCD outputs to ensure optimum performance.

The TL1593C is supplied in a 16-pin plastic package and is characterized for operation from 0°C to 70°C.

This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic fields. These circuits have been qualified to protect this device against electrostatic discharges (ESD) of up to 2 kV according to MIL-STD-883C, Method 3015; however, precautions should be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits. During storage or handling, the device leads should be shorted together or the device should be placed in conductive foam. In a circuit, unused inputs should always be connected to an appropriate logic voltage level, preferably either VCC or ground.

conductive foam. In a circuit, unused inputs should always be connected to an appropriate logic voltage level, preferably either V<sub>CC</sub> or ground. Specific guidelines for handling devices of this type are contained in the publication *Guidelines for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices and Assemblies* available from Texas Instruments.

# schematic

# **Terminal Functions**

| TERMINAL             |     | 1/0 | DESCRIPTION                     |  |  |

|----------------------|-----|-----|---------------------------------|--|--|

| NAME                 | NO. | 1/0 | DESCRIPTION                     |  |  |

| AIN1                 | 2   | I   | Channel 1 analog input          |  |  |

| AIN2                 | 4   | I   | Channel 2 analog input          |  |  |

| AIN3                 | 6   | I   | Channel 3 analog input          |  |  |

| ANLG GND             | 8   |     | Analog ground                   |  |  |

| ANLG V <sub>CC</sub> | 1   |     | Analog supply voltage           |  |  |

| CIN1                 | 3   | I   | Channel 1 compensation input    |  |  |

| CIN2                 | 5   | I   | Channel 2 compensation input    |  |  |

| CIN3                 | 7   | I   | Channel 3 compensation input    |  |  |

| DIG GND              | 9   |     | Digital ground                  |  |  |

| DIG V <sub>CC</sub>  | 13  |     | Digital supply voltage          |  |  |

| OUT1                 | 12  | 0   | Channel 1 output                |  |  |

| OUT2                 | 11  | 0   | Channel 2 output                |  |  |

| OUT3                 | 10  | 0   | Channel 3 output                |  |  |

| S/H1                 | 16  | I   | Channel 1 sample-and-hold input |  |  |

| S/H2                 | 15  | I   | Channel 2 sample-and-hold input |  |  |

| S/H3                 | 14  | I   | Channel 3 sample-and-hold input |  |  |

SOCS027B - APRIL 1987 - REVISED JULY 1991

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Analog supply voltage range, ANLG V <sub>CC</sub> (see Note 1)         | 0.4 V to 16 V                                                                                                        |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Digital supply voltage range, DIG V <sub>CC</sub>                      | 0.4 V to 16 V                                                                                                        |

| Input voltage range, V <sub>I</sub> : AINn inputs                      | $\dots \dots $ |

| CINn inputs                                                            | $-0.4$ V to ANLG V <sub>CC</sub>                                                                                     |

| S/Hn inputs                                                            | 0.4 V to DIG V <sub>CC</sub>                                                                                         |

| Continuous total power dissipation at (or below) T <sub>A</sub> ≤ 25°C | 625 mW                                                                                                               |

| Operating free-air temperature range, T <sub>A</sub>                   | 30°C to 75°C                                                                                                         |

| Storage temperature range, T <sub>STG</sub>                            | –55°C to 125°C                                                                                                       |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds           | 260°C                                                                                                                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to GND.

# recommended operating conditions

|                                             |             | MIN                   | NOM             | MAX                   | UNIT |  |

|---------------------------------------------|-------------|-----------------------|-----------------|-----------------------|------|--|

| Analog supply voltage, ANLG V <sub>CC</sub> |             | 10                    | 12              | 13                    | V    |  |

| Digital supply voltage, DIG V <sub>CC</sub> |             | 10                    | 12              | 13                    | V    |  |

| High-level input voltage, VIH               |             | 2                     |                 |                       | V    |  |

| Low-level input voltage, V <sub>IL</sub>    |             |                       |                 | 0.8                   | V    |  |

| Input bias voltage, VIR                     | AINn inputs | 4.9                   | 5.1             | 5.3                   |      |  |

| Imput bias voitage, VIB                     | CINn inputs | 2.2                   | 2.4             | 2.6                   |      |  |

| Input voltage V                             | AINn inputs | V <sub>IB</sub> – 0.3 | V <sub>IB</sub> | V <sub>IB</sub> + 0.3 | V    |  |

| Input voltage, V <sub>I</sub>               | CINn inputs | V <sub>IB</sub> – 0.2 | V <sub>IB</sub> | V <sub>IB</sub> + 0.2 | V    |  |

| Sampling frequency                          |             |                       |                 | 5                     | MHz  |  |

| Sampling time                               |             | 55                    |                 |                       | ns   |  |

| Operating free-air temperature, TA          |             | 30                    |                 | 75                    | °C   |  |

### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                  | PARAMETER                |             | TEST C                      | TEST CONDITIONS             |     | TYP‡ | MAX  | UNIT |

|------------------|--------------------------|-------------|-----------------------------|-----------------------------|-----|------|------|------|

|                  | Output voltage level     |             |                             |                             | 6   | 6.75 | 7.5  | V    |

|                  | Output voltage swing     |             |                             |                             | 2   |      |      | V    |

| lіН              | High-level input current |             | V <sub>I</sub> = 2.7 V,     | DIG V <sub>CC</sub> = 12 V  |     |      | 10   | μΑ   |

| IIL              | Low-level input current  |             | V <sub>I</sub> = 0.4 V,     | DIG V <sub>CC</sub> = 12 V  |     | -160 | -300 | μΑ   |

| lo_              | Output source current    |             |                             |                             | -5  |      |      | mA   |

| I <sub>O+</sub>  | Output sink current      |             |                             |                             | 0.4 |      |      | mA   |

| Icc              | Supply current           |             | DIG V <sub>CC</sub> = 12 V, | ANLG V <sub>CC</sub> = 12 V |     | 18.5 | 28   | mA   |

| Ci               | Input capacitance        | AINn inputs |                             |                             |     | 5    | 7    | pF   |

|                  |                          | CINn inputs |                             |                             |     | 19   | 24   |      |

|                  |                          | S/Hn inputs |                             |                             |     | 13   | 18   |      |

|                  | Input impedance          | AINn inputs |                             |                             |     | 100  |      | kΩ   |

| Output impedance |                          |             |                             |                             |     | 50   | 200  | Ω    |

$<sup>\</sup>ddagger$  All typical values are at  $T_A = 25^{\circ}$  C.

SOCS027B - APRIL 1987 - REVISED JULY 1991

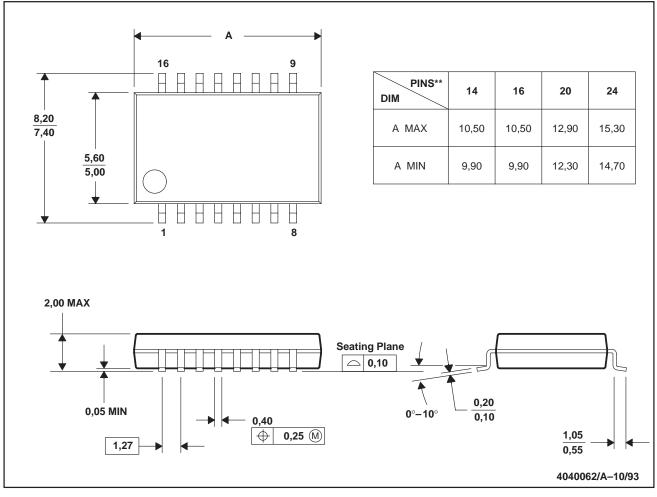

# **MECHANICAL DATA**

### NS/R-PDSO-G\*\*

#### **16 PIN SHOWN**

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated