- Single-Chip Multi-PHY Solution:

- Four 10BASE-T Physical-Layer (PHY) Interfaces in One Package Minimizing PCB Footprint for Internetworking Applications

- Each PHY is Half-Duplex and Full-Duplex Compliant

- Full-Duplex: Independent Transmit and Receive Channels for Operation at 20-Mbit/s Aggregate

- Compliant With IEEE Std 802.3 10BASE-T Specification

- Management Data Input/Output (MDIO) Serial Compliant With IEEE Std 802.3 Media-Independent Interface (MII)

- Integrated Filters on Both Receive and Transmit Circuits

- No External Filters Are Required

- Meets IEEE Std 802.3 (Section 14.3) Electrical Requirements

- Implements IEEE Std 802.3u Auto-Negotiation to Establish the Highest Common Protocol

- DSP-Based Digital Phase-Locked Loop (PLL)

- Interrupt Feature on MDIO

- Loopback Mode for Test Operations

- Integrated Manchester Encoding/Decoding

- Receive-Clock Regeneration for All Input Channels

- Smart Squelch

- Transmit Pulse Shaping

- Collision Detection

- Jabber Detection

- Link-Pulse Detection

- Auto-Polarity Control

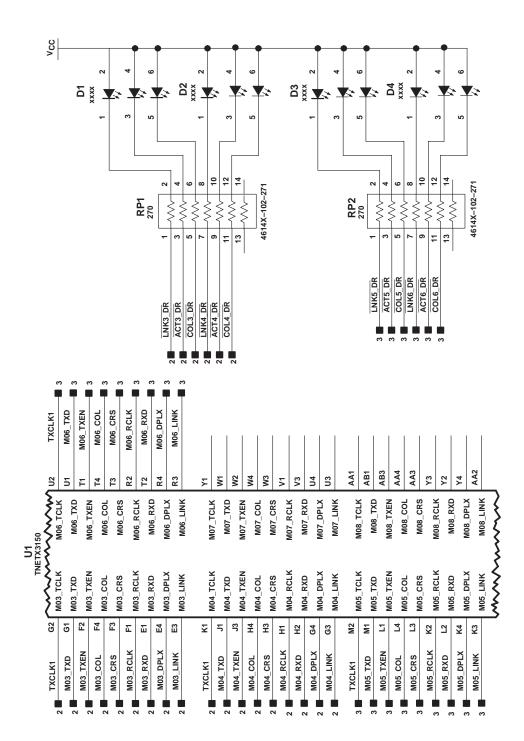

- Simple Connection for LED Status Indicators

- Sufficient Current Drive to Directly Connect LED Status Indicators

- CMOS Technology Enables Low Power Consumption

- Power-Down Mode

- IEEE Std 1149.1 (JTAG)<sup>†</sup> Test-Access Port (TAP)

- Each Serial Network Interface (SNI) Signal Is User Programmable

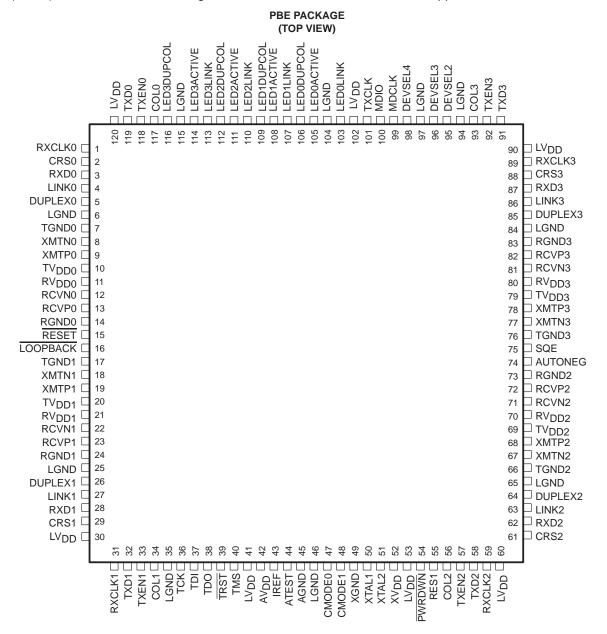

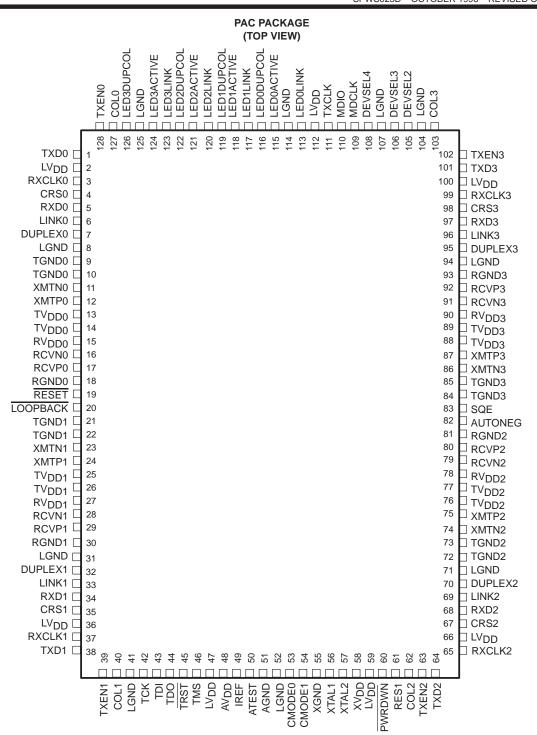

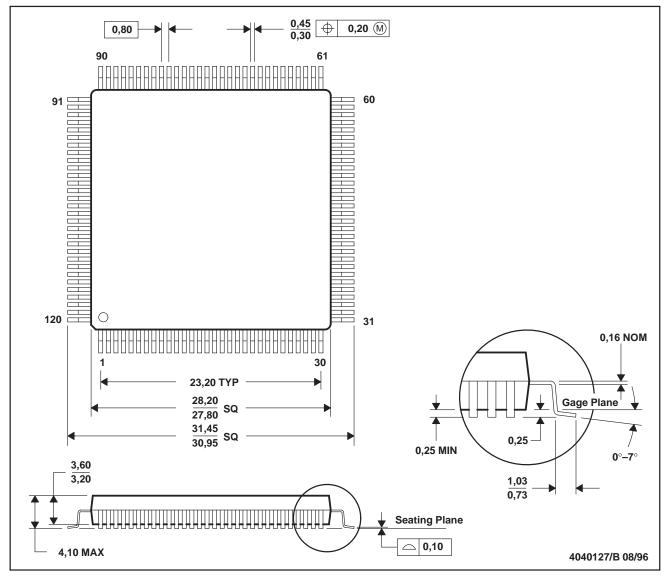

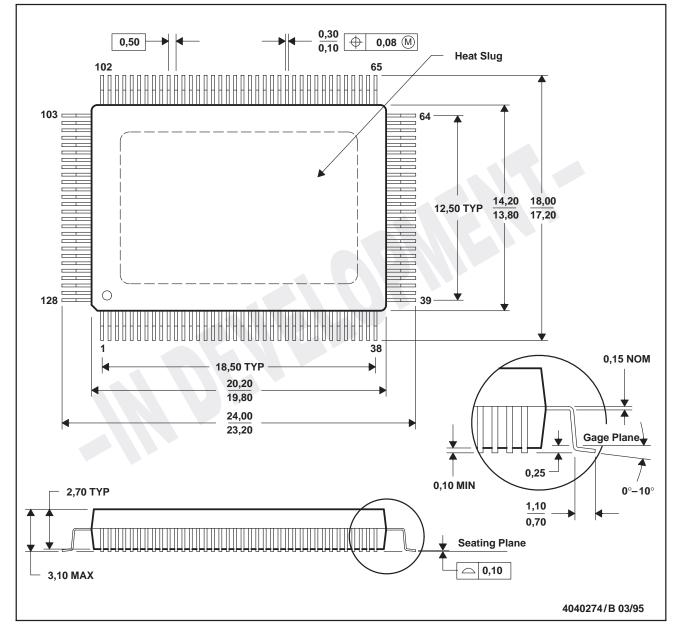

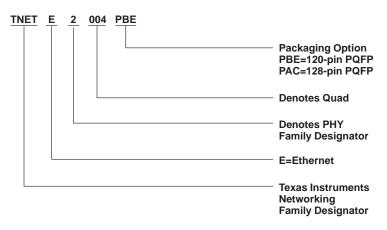

- Package Options Include 120-Pin Plastic Quad Flat Package (PBE) and 128-Pin Plastic Quad Flat Package (PAC)

# description

The TNETE2004 QuadPHY interface device is a single-chip, multi-PHY (four 10BASE-T devices), high-performance solution for designers of 10BASE-T networking systems. The highly integrated TNETE2004 includes a user-programmable SNI signal for each PHY. Each PHY interface on the device provides Manchester encoding/decoding of data via unshielded twisted-pair (UTP) balanced cable through simple isolation transformers requiring no external filtering. Additional TNETE2004 features are smart squelch, jabber detection, auto-polarity correction, transmission wave shaping, and anti-alias filtering capabilities. Each PHY interface on the TNETE2004 is individually addressable within the TNETE2004 via the MDIO.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup> IEEE Std 1149.1-1990, IEEE Standard Test-Access Port and Boundary-Scan Architecture

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# description (continued)

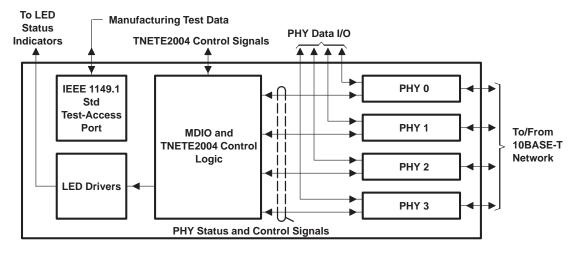

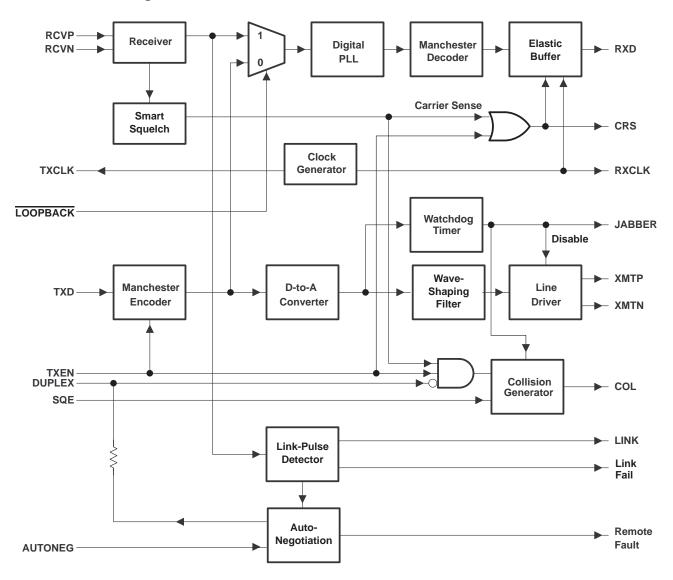

Figure 1. TNETE2004 Architecture

The TNETE2004 provides PHY-interface functions for up to four 10BASE-T half- or full-duplex ports as shown in Figure 1. The TNETE2004 contains four independent 10BASE-T transceivers in a single chip. Each transceiver is compliant with IEEE Std 802.3, Section 14, and a compliant management serial-interface port provides information for network management.

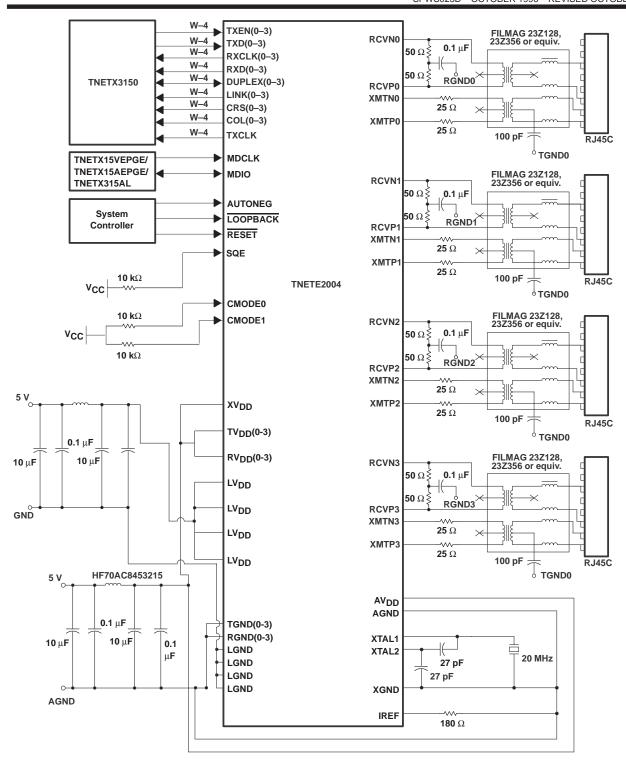

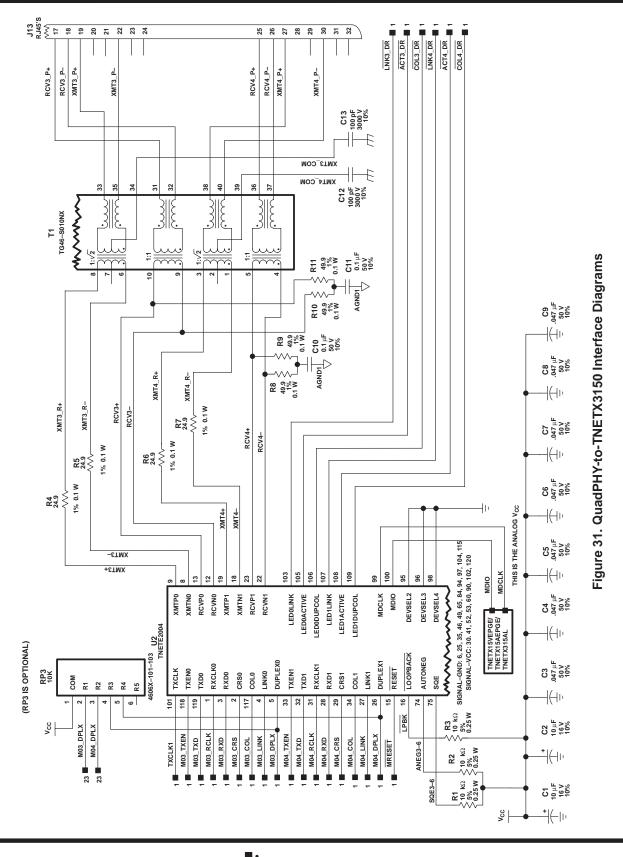

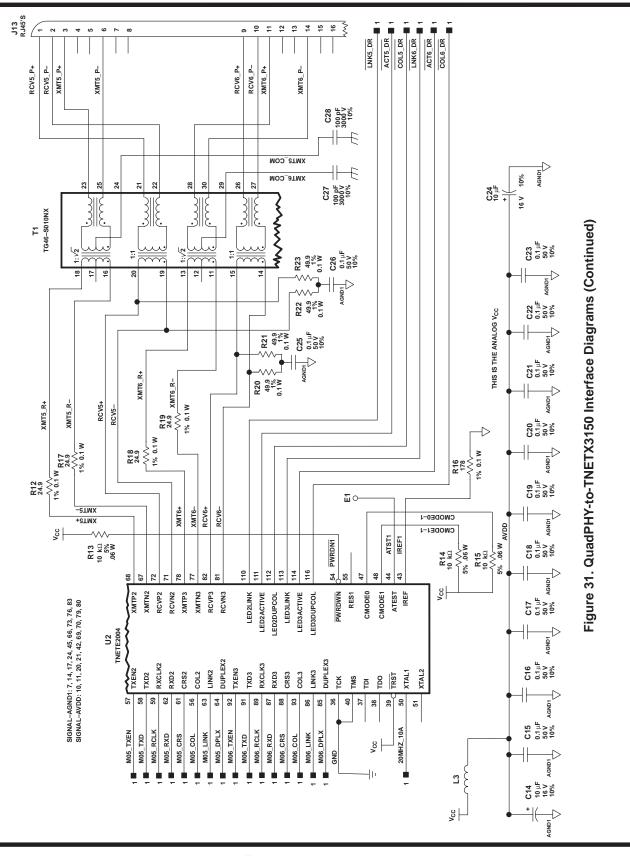

A typical application with external components is shown in Figure 2.

Figure 2. External Components for the TNETE2004

# pin assignments

TNETE2004 power supplies are identified according to the section of the device they supply. All power supplies are labeled  $V_{DD}$  or  $V_{SS}$ , and each has a single-letter prefix indicating which circuit of the device they supply. L indicates a supply for control logic, R is for receiver circuits, T is for transmitter circuits, and A is for analog circuits. Each PHY-specific signal has a suffix, which is the number of the PHY, for example, carrier sense (CRS0), CRS1, and so on. If a signal name does not include a suffix, it is applicable to all PHYs.

# **Terminal Functions**

# controller interface

| TERMINAL                                 |                       |                        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------------------------------------|-----------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                          | NO.                   |                        | ı/o† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| NAME                                     | 120                   | 128                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| AUTONEG                                  | 74                    | 82                     | I    | Auto-negotiation. When high, AUTONEG enables auto-negotiation on all four PHYs. Auto-negotiation takes place only after a reset or when a link is reestablished. AUTONEG can be overridden from the MDI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| COL0<br>COL1<br>COL2<br>COL3             | 117<br>34<br>56<br>93 | 127<br>40<br>62<br>103 | 0    | Collision sense. When asserted, COL0–COL3 indicates that PHY0–PHY3 sensed a network collision. The active level is set by the compatibility pins (see Table 2) or by setting the correct bits in pin-polarity register 0x16 (see Figure 17). Functions are described in Table 13.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CRS0<br>CRS1<br>CRS2<br>CRS3             | 2<br>29<br>61<br>88   | 4<br>35<br>67<br>98    | 0    | Carrier sense. When asserted, CRS0–CRS3 indicates that PHY0–PHY3 is receiving a frame carrier signal. The active level is set by the compatibility pins (see Table 2) or by setting the correct bits in pin-polarity register 0x16 (see Figure 17). Functions are described in Table 13.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DUPLEX0<br>DUPLEX1<br>DUPLEX2<br>DUPLEX3 | 5<br>26<br>64<br>85   | 7<br>32<br>70<br>95    | O/D  | Duplex mode. When DUPLEX0–DUPLEX3 is high, PHY0–PHY3 operates in full-duplex mode.<br>When DUPLEX0–DUPLEX3 is low, PHY0–PHY3 operates in the half-duplex mode. There is an internal weak drive on DUPLEX0–DUPLEX3 that pulls DUPLEX0–DUPLEX3 if auto-negotiation chooses the full-duplex mode, or if full duplex is chosen by writing to an MDI register. By connecting DUPLEX0–DUPLEX3 GND or V <sub>DD</sub> , this weak drive is overridden, and the type of duplex mode is permanently set, ignoring any auto-negotiation decisions or values written to the appropriate MDI registers. To set duplex mode, connect the auto-negotiation pin low. (This turns of auto-negotiation.) |  |  |  |

| LINK0<br>LINK1<br>LINK2<br>LINK3         | 4<br>27<br>63<br>86   | 6<br>33<br>69<br>96    | ο    | Link status. When LINK0–LINK3 is high, it indicates that PHY0–PHY3 has determined that a 10BASE-T link has been established. When low, LINK0–LINK3 indicates that the link has not b established.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| LOOPBACK                                 | 16                    | 20                     | I    | Loopback. When low, LOOPBACK enables internal loopback in all four PHYs. When asserted, data is internally wrapped within each PHY and does not appear on the network. While in the looped-back state, all network lines are placed in a noncontentious state. LOOPBACK can be overridden by the MDI registers.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| RXCLK0<br>RXCLK1<br>RXCLK2<br>RXCLK3     | 1<br>31<br>59<br>89   | 3<br>37<br>65<br>99    | 0    | Receive clock. Receive clock source for the receive data output RXD0–RXD3. Data is valid on RXD0–RXD3 on the edges of RXCLK0–RXCLK3 specified by the currently set compatibility mode (see Table 2) or by setting the correct bits in pin-polarity register 0x16 (see Figure 17). Functions are described in Table 13.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RXD0<br>RXD1<br>RXD2<br>RXD3             | 3<br>28<br>62<br>87   | 5<br>34<br>68<br>97    | 0    | Receive data. Bit-wise serial-data output from PHY0–PHY3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| SQE                                      | 75                    | 83                     | I    | Signal quality error. When high, SQE causes each PHY to simulate a collision condition at the end of each frame transmission to test functionality of the collision-detect circuitry. SQE is overridden by SQEEN (see Table 8). SQE must be set high to interface with the TNETX3150.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| TXCLK                                    | 101                   | 111                    | 0    | Transmit clock. TXCLK is shared by all PHYs to clock in transmit data. Data is valid on TXD0-TD2 on the edges of TXCLK specified by the currently set compatibility mode (see Table 2) or setting the correct bits in pin-polarity register 0x16 (see Figure 17). Functions are described Table 13.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| TXD0<br>TXD1<br>TXD2<br>TXD3             | 119<br>32<br>58<br>91 | 1<br>38<br>64<br>101   | I    | Transmit data. Serial-data input to PHY0–PHY3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TXEN0<br>TXEN1<br>TXEN2<br>TXEN3         | 118<br>33<br>57<br>92 | 128<br>39<br>63<br>102 | I    | Transmit enable. Assert TXEN0–TXEN3 active to indicate that valid transmit data is on TXD0–TXD3. The active level is set by the compatibility pins (see Table 2) or by setting the correct pins in pin-polarity register 0x16 (see Figure 17). Functions are described in Table 13.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

$\dagger I = input, O = output, O/D = open-drain output$

# **Terminal Functions (Continued)**

# miscellaneous interface

| TERMINAL                      |                |                   |     |                                                                                                                                                                                                                                              |  |

|-------------------------------|----------------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                          | N              | NO.               |     | DESCRIPTION                                                                                                                                                                                                                                  |  |

|                               | 120            | 128               |     |                                                                                                                                                                                                                                              |  |

| ATEST                         | 44             | 50                | А   | Analog test pin. ATEST provides access to the filter of the reference PLL. When operating correctly, ATEST presents a voltage between $1-2$ V.                                                                                               |  |

| CMODE0<br>CMODE1              | 47<br>48       | 53<br>54          | I   | Compatibility mode. Eases compatibility with third-party media-access controllers (MACs) (s Table 2).                                                                                                                                        |  |

| DEVSEL2<br>DEVSEL3<br>DEVSEL4 | 95<br>96<br>98 | 105<br>106<br>108 | I   | Device select. DEVSEL2–DEVSEL4 specifies the three most-significant bits of a 5-bit number used to address a PHY on the management-data interface. The two least-significant bits are set as 00, 01, 10, and 11 for PHY0–PHY3, respectively. |  |

| IREF                          | 43             | 49                | А   | Current reference. Used to set a current reference for the analog circuitry. IREF must be connected to ground by a 180 $\pm$ 5- $\Omega$ resistor.                                                                                           |  |

| MDCLK                         | 99             | 109               | I   | Management-data clock. MDCLK is used to clock data in and out of the MDIO port.                                                                                                                                                              |  |

| MDIO                          | 100            | 110               | I/O | Management-data I/O. MDIO is the serial management-data interface.                                                                                                                                                                           |  |

| PWRDWN                        | 54             | 60                | I   | Power down. When asserted, <u>PWRDWN</u> places all four PHYs in the lower power state<br>Transmitting and receiving are inhibited in this state.                                                                                            |  |

| RES1                          | 55             | 61                | 0   | Reserved                                                                                                                                                                                                                                     |  |

| RESET                         | 15             | 19                | I   | Global reset. RESET is used to reset all four PHY sections.                                                                                                                                                                                  |  |

| XTAL1                         | 50             | 56                | А   | Crystal oscillator pins. Connect a 20-MHz crystal across XTAL1 and GND, or drive XTAL1 from 20-MHz crystal-oscillator module.                                                                                                                |  |

| XTAL2                         | 51             | 57                | А   | Connect a 27-pF capacitor across XTAL2 and XTAL1 and connect a 27-pF capacitor between XTAL2 and GND. If a crystal-oscillator module is used, do not connect anything to XTAL2.                                                              |  |

<sup>†</sup> A = analog, I = input, O = output, I/O = 3-state input/output

# JTAG interface

| TER  | TERMINAL |    |      |                                                                                                                                 |  |  |

|------|----------|----|------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | NO.      |    | ı/o‡ | DESCRIPTION                                                                                                                     |  |  |

|      | 120 128  |    |      |                                                                                                                                 |  |  |

| тск  | 36       | 42 | Ι    | Test clock. TCK is used to clock state information and test data into and out of the device during operation of the JTAG.       |  |  |

| TDI  | 37       | 43 | I    | Test data input. TDI is used to serially shift test data and test instructions into the device during operation of the JTAG.    |  |  |

| TDO  | 38       | 44 | 0    | Test data output. TDO is used to serially shift test data and test instructions out of the device during operation of the JTAG. |  |  |

| TMS  | 40       | 46 | I    | Test mode select. TMS controls the operating state of the JTAG.                                                                 |  |  |

| TRST | 39       | 45 | I    | Test reset. TRST is used for asynchronous reset of the JTAG controller.                                                         |  |  |

$\ddagger I = input, O = output$

# **Terminal Functions (Continued)**

# LED interface

| TERMINAL                                             |                          |                          |      |                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|------------------------------------------------------|--------------------------|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                 | NO.                      |                          | ı/o† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| NAME                                                 | 120                      | 128                      |      |                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| LED0ACTIVE<br>LED1ACTIVE<br>LED2ACTIVE<br>LED3ACTIVE | 105<br>108<br>111<br>114 | 115<br>118<br>121<br>124 | 0    | LED activity indicator. The LED activity indicator is driven low for 20 ms when PHY0–PHY3 receives or transmits. LED0ACTIVE–LED3ACTIVE can sink a 10-mA current. If it receives or transmits another packet during that 20 ms, the LED does not flash, but stays on. Therefore, if packets are received or transmitted at intervals faster than 20 ms, the LED stays on continuously. |  |  |  |

| LED0DUPCOL<br>LED1DUPCOL<br>LED2DUPCOL<br>LED3DUPCOL | 106<br>109<br>112<br>116 | 116<br>119<br>122<br>126 | 0    | LED duplex/collision indicator for PHY0–PHY3. This LED status pin has different meaning when<br>in full- or half-duplex mode. In full-duplex mode, LED0DUPCOL–LED3DUPCOL is continuously<br>driven low. In half-duplex mode, it is driven low for 20 ms after a collision.<br>LED0DUPCOL–LED3DUPCOL can sink a 10-mA current.                                                         |  |  |  |

| LED0LINK<br>LED1LINK<br>LED2LINK<br>LED3LINK         | 103<br>107<br>110<br>113 | 113<br>117<br>120<br>123 | ο    | LED link indicator. The LED link indicator is driven low when PHY0–PHY3 has established a valid link. LED0LINK–LED3LINK can sink a 10-mA current.                                                                                                                                                                                                                                     |  |  |  |

†O = output

# **10BASE-T** interface

| TERMINAL |     |     |                                                  |                                                                                               |  |

|----------|-----|-----|--------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| NAME     | NO. |     | TYPE <sup>‡</sup>                                | DESCRIPTION                                                                                   |  |

| NAME     | 120 | 128 |                                                  |                                                                                               |  |

| XMTN0    | 8   | 11  |                                                  |                                                                                               |  |

| XMTN1    | 18  | 23  |                                                  |                                                                                               |  |

| XMTN2    | 67  | 74  |                                                  |                                                                                               |  |

| XMTN3    | 77  | 86  | А                                                | Transmit pair. Differential line-transmitter outputs from PHY0–PHY3.                          |  |

| XMTP0    | 9   | 12  |                                                  |                                                                                               |  |

| XMTP1    | 19  | 24  |                                                  |                                                                                               |  |

| XMTP2    | 68  | 75  |                                                  |                                                                                               |  |

| XMTP3    | 78  | 87  |                                                  |                                                                                               |  |

| RCVN0    | 12  | 16  |                                                  |                                                                                               |  |

| RCVN1    | 22  | 28  |                                                  |                                                                                               |  |

| RCVN2    | 71  | 79  |                                                  |                                                                                               |  |

| RCVN3    | 81  | 91  | Receive pair for PHY0–PHY3. Differential line-ru | Receive pair for PHY0-PHY3. Differential line-receiver inputs connect to receive pair through |  |

| RCVP0    | 13  | 17  | A                                                | transformer isolation.                                                                        |  |

| RCVP1    | 23  | 29  |                                                  |                                                                                               |  |

| RCVP2    | 72  | 80  |                                                  |                                                                                               |  |

| RCVP3    | 82  | 92  |                                                  |                                                                                               |  |

‡ A = analog

# **Terminal Functions (Continued)**

# power interface

| TERMINAL                                                                         |                                                 |                                                   |                   |                                                      |  |  |

|----------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------|-------------------|------------------------------------------------------|--|--|

| NAME                                                                             | NO.                                             |                                                   | TYPE <sup>†</sup> | DESCRIPTION                                          |  |  |

| NAME                                                                             | 120                                             | 128                                               |                   |                                                      |  |  |

| AGND                                                                             | 45                                              | 51                                                | GND               | Ground pin for analog circuitry                      |  |  |

| AV <sub>DD</sub>                                                                 | 42                                              | 48                                                | PWR               | V <sub>DD</sub> pin for analog circuitry             |  |  |

| LGND                                                                             | 6, 25<br>35, 46<br>65, 84<br>94, 97<br>104, 115 | 8, 31<br>41, 52<br>71, 94<br>104, 107<br>114, 125 | GND               | Logic ground pin                                     |  |  |

| LV <sub>DD</sub>                                                                 | 30, 41<br>53, 60<br>90, 102<br>120              | 36, 47<br>59, 66<br>100, 112<br>2                 | PWR               | Logic V <sub>DD</sub> pin                            |  |  |

| RGND0<br>RGND1<br>RGND2<br>RGND3                                                 | 14<br>24<br>73<br>83                            | 18<br>30<br>81<br>93                              | GND               | Ground pin for receiver circuitry                    |  |  |

| RV <sub>DD0</sub><br>RV <sub>DD1</sub><br>RV <sub>DD2</sub><br>RV <sub>DD3</sub> | 11<br>21<br>70<br>80                            | 15<br>27<br>78<br>90                              | PWR               | V <sub>DD</sub> pin for receiver circuitry           |  |  |

| TGND0<br>TGND1<br>TGND2<br>TGND3                                                 | 7<br>17<br>66<br>76                             | 9, 10<br>21, 22<br>72, 73<br>84, 85               | GND               | Ground pin for transmit circuitry                    |  |  |

| TV <sub>DD0</sub><br>TV <sub>DD1</sub><br>TV <sub>DD2</sub><br>TV <sub>DD3</sub> | 10<br>20<br>69<br>79                            | 13, 14<br>25, 26<br>76, 77<br>88, 89              | PWR               | V <sub>DD</sub> pin for transmit circuitry           |  |  |

| XGND                                                                             | 49                                              | 55                                                | GND               | Ground pin for crystal-oscillator circuitry          |  |  |

| XV <sub>DD</sub>                                                                 | 52                                              | 58                                                | PWR               | V <sub>DD</sub> pin for crystal-oscillator circuitry |  |  |

† GND = ground, PWR = power

# functional block diagram

# functional description

The TNETE2004 consists of four PHYs, with each PHY having several logical blocks (see the functional block diagram and Table 1).

| LOGICAL BLOCKS                           | FUNCTION                                                                                                          |  |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Transmitter function                     | Accepts data from the data terminal equipment (DTE) and transmits it onto the network                             |  |  |  |

| Receiver function                        | Receives data from the network and sends it to the DTE                                                            |  |  |  |

| Collision/signal-quality error detection | Indicates to the DTE any collision on the network/transmitter with valid link                                     |  |  |  |

| Jabber detection                         | Indicates to the DTE if a packet transmission exceeds 20-ms minimum                                               |  |  |  |

| Auto-negotiation                         | Negotiate to establish the highest common protocol                                                                |  |  |  |

| Management-data interface                | To allow register-based management operations for each PHY module                                                 |  |  |  |

| Link test                                | A link pulse is sent to indicate a valid connection.                                                              |  |  |  |

| LED status indicator                     | Indication for link, activity, and collision IEEE Std 1149.1 test-access port and boundary-scan testing           |  |  |  |

| Test port                                |                                                                                                                   |  |  |  |

| Loopback test mode                       | Loopback capabilities are provided to allow certain tests to be performed to validate operation of the TNETE2004. |  |  |  |

| Compatibility modes                      | Ease connection to third-party MACs                                                                               |  |  |  |

# Table 1. Logical Blocks

# **10BASE-T** differential line-transmitter function

Each differential line driver of the TNETE2004 drives a balanced, properly terminated twisted-pair transmission line with a characteristic impedance of 85  $\Omega$  to 111  $\Omega$  (see Figure 2). In the idle state, the driver maintains a minimum differential output voltage, while staying within the required common-mode voltage range.

The driver incorporates an on-chip wave-shaping stage and a high-frequency filtering stage to allow the outputs to be connected directly to isolation transformers through serial termination resistors. No external filters are required.

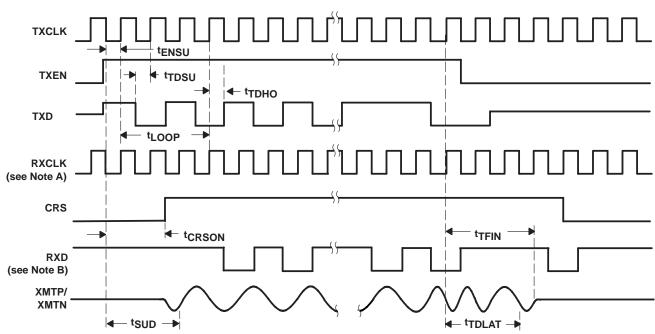

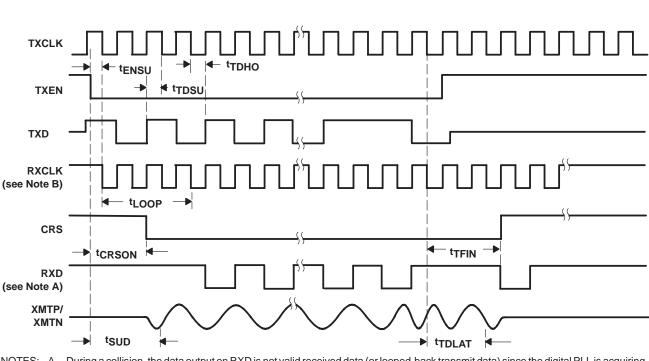

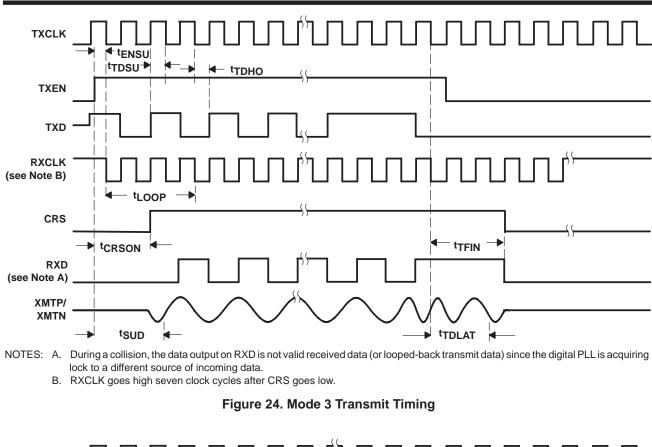

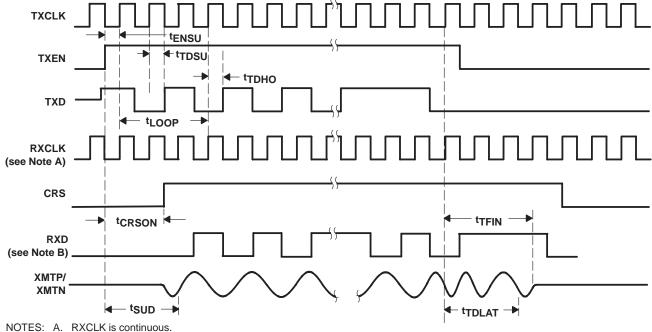

Serial data for transmission by a PHY is presented to the appropriate transmit data (TXD) input of the TNETE2004. To be valid, data must be synchronized on the appropriate edges of the transmit clock (TXCLK) signal, which depends on the compatibility-mode setting.

Once the transmit-enable (TXEN) pin is deasserted for a PHY, the driver maintains full differential outputs for a minimum of 250 ns, which then begins to decay to minimum differential levels.

The PHY also transmits regular link pulses in compliance with IEEE Std 802.3.

#### **10BASE-T** differential line-receiver function

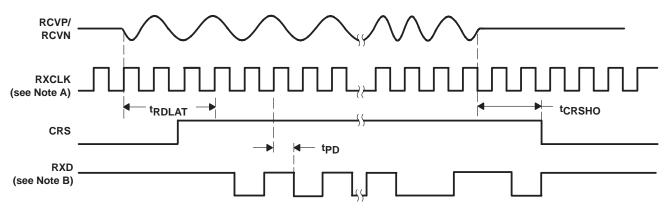

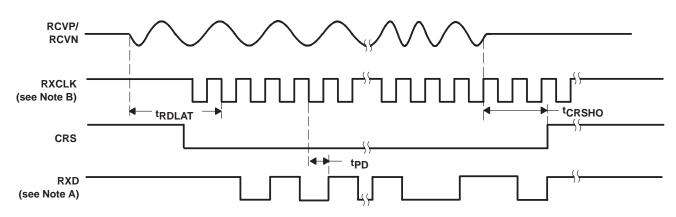

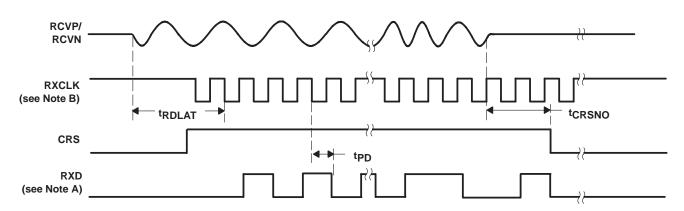

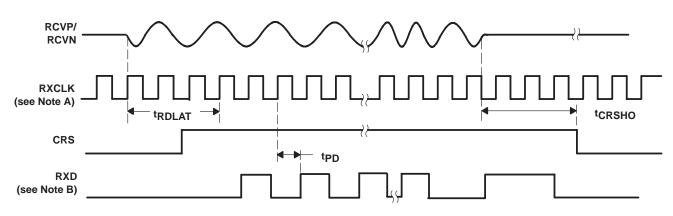

The line-receiver pins of each PHY must be connected to a properly terminated transmission line by an external isolation transformer. The receiver establishes its own common-mode input-bias voltage. Data received from the network is output on RXD of the appropriate PHY and synchronized by the appropriate edges of the corresponding RXCLK signal, which depends on the compatibility-mode setting.

The receiver incorporates a squelch function to pass incoming data. This smart squelch function passes data only if the input amplitude is greater than a minimum signal threshold and if a specific pulse sequence is received. This protects input data from impulse line noise being mistaken for signal or link activity. The squelch circuits quickly deactivate if received pulses exceed the specifications; thus, overly long pulses are not mistaken as link pulses.

Carrier sense (CRS) is driven high while the squelch function is active to indicate that the circuit is allowing data to pass from the twisted pair. CRS is driven low when the squelch circuit is disabling data low.

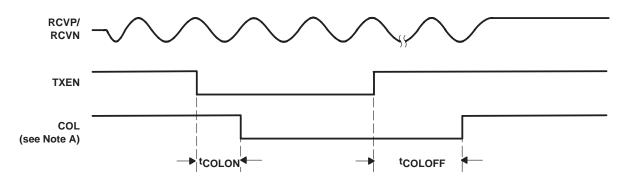

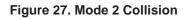

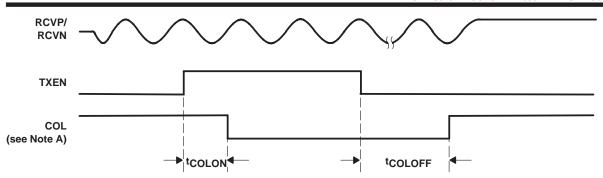

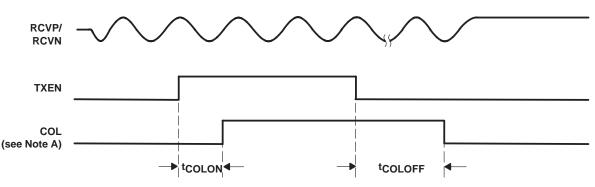

#### collision/signal-quality error detection

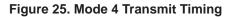

When not in full-duplex mode, collisions are detected by sensing simultaneous activity on both the transmit and the receive pins. A collision detection is signified by COL on the respective PHY being driven high for the duration of the condition and for a specified time afterwards.

The TNETE2004 device also provides a signal-quality error (SQE) function. This function can be enabled or disabled only for the whole device and not for individual PHYs. When SQE is enabled, following transmission, a simulated collision is presented to a PHY. PHY tests as much of the collision-detect circuitry as possible without affecting the attached twisted-pair channels. Each PHY asserts its COL output signal high for a defined time interval relative to the last positive data edge of its transmit data input. SQE is invoked by driving SQE high or by using the TNETE2004 registers.

#### jabber detection

Each PHY monitors the length of the packet being transmitted. If a single packet exceeds 20 ms, a jabber condition is detected. The output is disabled, and CRS is driven low. The TNETE2004 device asserts COL, while attempts are made to transmit data, and signals link-fail for the duration of the attempts. The device also asserts COL (for half-duplex mode only) when it has detected that the transmitter has entered jabber mode. To clear the jabber function, transmission must cease for a minimum of 500 ms.

#### auto-negotiation

Each PHY on the device is capable of auto-negotiation as defined in IEEE Std 802.3. When enabled, this feature allows a PHY to negotiate with another PHY on the link to establish their highest common protocol. Until a PHY has completed its negotiation, it cannot assert LINK.

The only two protocols possible for the TNETE2004 are half- or full-duplex 10BASE-T. When auto-negotiation indicates that full-duplex operation is possible, a weak pullup resistor is applied to DUPLEX on the device, allowing full-duplex operation, unless the pin is pulled low externally.

#### link-partner register

This register contains the information for the link partner. Refer to Table 6 for the link partner's ability-register bit functions.

# expansion register

Refer to Table 7 for the bit definition on the expansion register.

#### next\_page transmit

After exchanging the base page, which contains the information to make connection automatically, if both ends of the link indicate support for the next\_page function, additional data can be exchanged. This allows extensions to the standard and proprietary extensions to exist without affecting interoperability. Refer to Figure 11 for the next\_page transmit register.

#### management-data interface

The TNETE2004 incorporates a management-data interface to allow register-based management operations for each PHY module. Operation of the TNETE2004 is possible without use of the management-data interface, since all the signals necessary for complete functionality are accessible by way of the device pins; however, some additional features are accessible only through the management-data interface.

# interrupt enable cycle

The TNETE2004 can generate interrupts via the MDIO interface after the quiescent cycle. The quiescent cycle is the cycle following the data transfer in which neither the external MAC nor the PHYs drive MDIO. The TNETE2004 indicates to the host that an interrupt is pending by driving MDIO low. This happens one clock cycle after the quiescent cycle, while MDCLK is high. When MDCLK goes low, TNETE2004 stops driving MDIO so the host can determine what caused the interrupt.

#### link test

When not in auto-negotiation mode, the PHY sends link pulses, separated by an interval of 16 ms, on the data-out (DO) circuit. The receiver looks for valid link pulses on the input pair. If a link pulse is not received within a given time interval, the device enters a link-fail state. In this state, link pulses continue to be generated, and the receiver constantly looks for the link-pulse pattern. The device remains in this state until a valid receive packet or multiple legal link-test pulses are received.

# loopback test mode

By asserting the LOOPBACK pin on the device or by setting the LOOPBACK bit in the PHY generic control register, the transmit circuit of each PHY is looped to the corresponding receive circuit closest to the twisted-pair I/O pins. Thereafter, transmit drivers do not forward any further packet data but continue to send link-test pulses.

When accessing loopback test mode from the package pins, since there is only one LOOPBACK pin on the package, all four PHYs are placed in LOOPBACK mode simultaneously. Individual PHYs can be placed in LOOPBACK mode by means of the TNETE2004 registers. While in LOOPBACK mode, all receive activities, other than link-test pulses, are ignored. However, squelch information is still processed, allowing the link status to be maintained under momentary loopback self-test.

# LED status indication

The TNETE2004 has 12 pins that drive LEDs. Each PHY has the following three status LEDs:

Note: The LEDs are all off when reset is active. Once reset is inactive, all the LEDs turn on for 100ms, then turn off, and then function in the normal way. The following signals are active low.

- LEDxLINK illuminates when PHYx has established a valid link

- LEDxACTIVE illuminates when PHYx is transmitting or receiving data. This LED illuminates for a minimum duration of 20 ms for each activity, but if packets are being received or transmitted faster than 20 ms, it stays on continuously.

- LEDxDUPCOL illuminates continuously when PHYx is in full-duplex mode. Illuminates for a minimum duration of 20 ms when collisions occur in half-duplex mode. Additionally, in half-duplex mode, LED0DUPCOL–LED3DUPCOL flashes when a jabber condition is detected. This feature is not available in full-duplex mode.

#### IEEE Std 1149.1 (JTAG) test port

Compliant with the IEEE Std 1149.1, the test-access port is composed of five pins. These pins interface serially with the device and the board on which the device is installed for boundary-scan testing. The TNETE2004 implements the following JTAG instructions:

| 000 | EXTEST         | External boundary-scan test                                     |

|-----|----------------|-----------------------------------------------------------------|

| 001 | SAMPLE/PRELOAD | Initialization for boundary-scan test                           |

| 100 | IDCODE         | Scans out TNETE2004 identification code                         |

| 101 | HIGHZ          | Sets all digital output pins on the TNETE2004 to high impedance |

| 111 | BYPASS         | Connects 1-bit bypass register between TDI and TDO              |

|     |                |                                                                 |

#### autopolarity

The TNETE2004 can sense and detect reversed polarity of its receiver inputs (e.g., due to incorrect cable wiring). If, at any time, seven consecutive inverted link pulses are detected, then reversed polarity is assumed and flagged by the POLOK bit in the TNETE2004\_sts register (see Table 9). If automatic polarity correction is selected by the SWAPPOLEN bit in the TNETE2004\_ctl register (see Table 8), the TNETE2004 swaps its RCVP and RCVN input for the affected PHY. Once a single correct link pulse is received, good polarity is assumed, and the POLOK bit is set.

Automatic polarity correction is enabled by default after power on or reset. The polarity detect circuit must see link pulses to detect the polarity of the receive pair, so, in instances of high network activity where link pulses are sparse, there may be a slight delay before the correct polarity is established.

# compatibility modes

To ease connection to third-party MACs, the TNETE2004 provides options to reverse the polarity of some device pins. The compatibility mode is selected by the CMODE0 and CMODE1 pins, as defined in Table 2. The TNETE2004 can be programmed through the MDIO to change the polarity of each SNI (like COL or RXCLK, etc.) signal. Refer to Table 13 for more details on this function.

| CMODE                                            | PIN SIGNIFICANCE                                                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <b>Mode 1:</b><br>CMODE0 = Low<br>CMODE1 = Low   | CRS high to indicate carrier detected<br>COL high to indicate collision<br>TXEN high to indicate valid data on TXD<br>Data on RXD valid on rising edge of RXCLK<br>Data on TXD valid on rising edge of TXCLK<br>RXD high when no data is being received<br>RXCLK is continuously running.                                       |  |  |  |

| <b>Mode 2:</b><br>CMODE0 = High<br>CMODE1 = Low  | CRS low to indicate carrier detected<br>COL low to indicate collision<br>TXEN low to indicate valid data on TXD<br>Data on RXD valid on falling edge of RXCLK<br>Data on TXD valid on falling edge of TXCLK<br>RXD high when no data is being received<br>RXCLK runs for seven clocks after CRS is high,<br>then it stays high. |  |  |  |

| <b>Mode 3:</b><br>CMODE0 = Low<br>CMODE1 = High  | CRS high to indicate carrier detected<br>COL low to indicate collision<br>TXEN high to indicate valid data on TXD<br>Data on RXD valid on falling edge of RXCLK<br>Data on TXD valid on falling edge of TXCLK<br>RXD low when no data is being received<br>RXCLK runs for seven clocks after CRS is low,<br>then it stays high. |  |  |  |

| <b>Mode 4:</b><br>CMODE0 = High<br>CMODE1 = High | CRS high to indicate carrier detected<br>COL high to indicate collision<br>TXEN high to indicate valid data on TXD<br>Data on RXD valid on rising edge of RXCLK<br>Data on TXD valid on rising edge of TXCLK<br>RXD low when no data is being received<br>RXCLK is continuously running.                                        |  |  |  |

#### Table 2. Compatibility Mode Options

# **TNETE2004** registers

The TNETE2004 incorporates management-data interface to allow register-based management operations for each PHY module. Normal operation of the TNETE2004 is possible without use of management-data interface since all the essential signals for operation are accessible through the device pins; however, some additional features are accessible only through the management-data interface. If management-data interface is not being used, DEVSEL, MDCLK, and MDIO all can be tied low.

Some features are controllable by both pins and registers. A feature is controlled by the pin until a write operation is performed on the register controlling the feature. From then until the device is reset, the value on the pin is ignored.

The TNETE2004 registers are accessible through the MII-management interface. The IEEE Std 802.3 MII serial protocol allows for up to 32 different PHYs, with up to 32 (16-bit-wide) internal registers in each device.

The TNETE2004 implements 11 registers (three of which are hardwired) on each PHY and three additional overview registers that allow software drivers to access all four PHYs in a single operation. User programming of the SNI is implemented through the pin-polarity register. These all-PHY registers are mapped into the addressing space on PHY0.

Figure 3 shows the TNETE2004 device register map. The registers, shown shaded, are the generic registers mandated by the MII specification. The unshaded registers are TI-specific registers.

| 14, Table 10)   |

|-----------------|

| 5, Table 11)    |

| e 16, Table 12) |

|                 |

| 5               |

### Figure 3. TNETE2004 Registers

The default or IDLE state of the two-wire MII is a logic 1. All 3-state drivers are disabled, and the TNETE2004 pullup resistor pulls the MDIO line to a logic 1. Before initiating any other transaction, the station management entity sends a sequence of 32 contiguous logic 1 bits on MDIO and 32 corresponding contiguous logic 1 bits on MDCLK. This sequence provides the TNETE2004 with a pattern that it can use to establish synchronization. The TNETE2004 responds to no other transactions until it recognizes a sequence of 32 contiguous logic 1 bits on MDIO with 32

Frame format of the generic registers is in accordance with MII specifications as shown in Figures 4 and 5.

| •  | tion Code PHY Ad | dress Register Add | ress Turnaround | Data                |

|----|------------------|--------------------|-----------------|---------------------|

| 01 | 10 AAA           | AA RRRRR           | ZO              | DDDD.DDDD.DDDD.DDDD |

# Figure 4. MII Frame Format: Reads

| _ | Start Delimiter | <b>Operation Code</b> | PHY Address | Register Address | Turnaround | Data                |

|---|-----------------|-----------------------|-------------|------------------|------------|---------------------|

|   | 01              | 01                    | AAAA        | RRRR             | 10         | DDDD.DDDD.DDDD.DDDD |

|   |                 |                       |             |                  |            |                     |

# Figure 5. MII Frame Format: Writes

# start delimiter

The start of a frame is indicated by a 01 pattern. This pattern ensures transitions from the default logic 1 line state to 0 and back to 1.

# operation code

The operation code for a read is 10, while the code for a write is 01.

# PHY address

The PHY address is five bits wide, which allows 32 unique PHY addresses. The first PHY address bit transmitted and received is the most-significant bit (MSB) of the address. The two least-significant bits (LSBs) represent the PHY number within the package. The upper three bits for each internal PHY are read from the DEVSEL pins.

#### register address

The register address is five bits wide, allowing 32 individual registers to be addressed within each PHY. Refer to the address maps (Figures 4 and 5) for the addresses of individual registers.

#### turn around

An idle-bit time, during which no device actively drives the MDIO signal, must be inserted between the register address field and the data field of a read frame, to avoid contention. During a read frame, the PHY drives a 0 bit onto MDIO for the bit time following the idle bit and preceding the data field. During a write frame, this field must consist of a 1 bit followed by a 0 bit.

#### data

The data field is composed of 16 bits. The first data bit transmitted and received is the MSB of the data payload.

#### PHY generic control register – GEN\_ctl at 0x0

| BYTE 1<br>15          | 14                              | 13 | 12                                   | 11               | 10                              | 9                 | 8                          | 7             | 6 | 5 | 4 | 3      | 2   | 1 | BYTE 0<br>0 |

|-----------------------|---------------------------------|----|--------------------------------------|------------------|---------------------------------|-------------------|----------------------------|---------------|---|---|---|--------|-----|---|-------------|

| R<br>E<br>S<br>E<br>T | L<br>O<br>P<br>B<br>A<br>C<br>K | 0  | A<br>N<br>E<br>N<br>A<br>B<br>L<br>E | P<br>D<br>W<br>N | I<br>S<br>O<br>L<br>A<br>T<br>E | A N R E S T A R T | D<br>U<br>P<br>L<br>E<br>X | C O L T E S T |   |   |   | RESERV | 'ED |   |             |

# Figure 6. PHY Generic Control Register

# **Table 3. PHY Generic Control Register Bit Functions**

|     | BIT                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                 |           |         |

|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|

| NO. | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                 | DIRECTION | DEFAULT |

| 15  | RESET <sup>‡</sup> | Reset a PHY. Writing a 1 RESET resets the whole device, and all registers revert to their default values. RESET is self clearing. It is always read as 0. It is not possible to reset one PHY separately from the others. Operation of the device is not ensured for a duration of 50 ms after a software reset.                                                                                         | R/W       | 0       |

| 14  | LOOPBACK           | Internal loopback mode. LOOPBACK enables the internal loopback within the individual PHY. When LOOPBACK is set to 1, data is wrapped internally within the PHY and does not appear on the network. Collision detection is disabled, and data transmitted appears at the receive pins. While in loopback mode, the device pins are placed in noncontentious states.                                       | R/W       | Pin     |

| 13  |                    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                 | RO        | 0       |

| 12  | ANENABLE           | Auto-negotiation enable. When set, ANENABLE allows auto-negotiation to take place.                                                                                                                                                                                                                                                                                                                       | R/W       | Pin     |

| 11  | PDOWN              | Power-down mode. When set, PDOWN places the PHY in a power-down mode. In this mode, it is not possible to receive or transmit data, although it is possible to continue to process management-data frames. IEEE Std 802.3 states that the PHY must be allowed 500 ms of initialization time after it is taken out of power-down state before data transmission and reception can be started. See Note 1. | R/W       | 0       |

| 10  | ISOLATE            | PHY pin isolation. When set, the PHY electrically isolates itself from the pins. In the ISOLATE state, the PHY does not respond to TXD or TXEN but presents a high impedance on RXD, RXCLK, and COL. However, it still responds to MII data frames.                                                                                                                                                      | R/W       | 0       |

| 9   | ANRESTART          | Auto-negotiation restart. Setting ANRST causes auto-negotiation to be restarted.                                                                                                                                                                                                                                                                                                                         | R/W       | 0       |

| 8   | DUPLEX             | Full-duplex mode select. Setting DUPLEX forces this PHY into full-duplex mode.<br>Resetting it forces half-duplex. For DUPLEX to have any effect, the DUPLEX pin on<br>the package must not be driven externally.                                                                                                                                                                                        | R/W       | Pin     |

| 7   | COLTEST            | Collision-test enable. Setting COLTEST causes this PHY to assert COL when TXEN is asserted.                                                                                                                                                                                                                                                                                                              | R/W       | 0       |

| 6–0 | RESERVED           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                 |           | 0       |

<sup>†</sup>RO = read only, R/W = read/write

<sup>‡</sup> This bit is set for the TNETE2004, not for each PHY.

NOTE 1: If all four PHYs are in power-down mode simultaneously, then reset must be used to power up the device. It is not possible to power up an individual PHY if all four PHYs are in power-down mode.

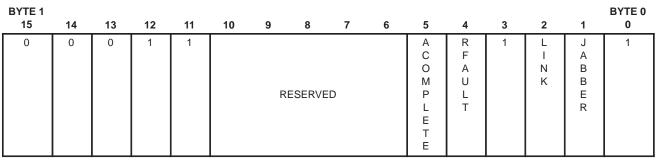

# PHY generic status register – GEN\_sts at 0x1

Figure 7. PHY Generic Status Register

# Table 4. PHY Generic Status Register Bit Functions

|      | BIT       | FUNCTION                                                                                                                                             | DIRECTION |

|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| NO.  | NAME      | FUNCTION                                                                                                                                             | DIRECTION |

| 15   |           | 100Base-T4 capable. Not supported, read as 0                                                                                                         | RO        |

| 14   |           | 100Base-T4 full-duplex capable. Not supported, read as 0                                                                                             | RO        |

| 13   |           | 100Base-T4 half-duplex capable. Not supported, read as 0                                                                                             | RO        |

| 12   |           | 10BASE-TX full-duplex capable. Supported, read as 1                                                                                                  | RO        |

| 11   |           | 10BASE-TX half-duplex capable. Supported, read as 1                                                                                                  | RO        |

| 10–6 | RESERVED  | Reserved. Read as 0.                                                                                                                                 | RO        |

| 5    | ACOMPLETE | Auto-negotiation complete. When set, ACOMPLETE indicates that auto-negotiation has been completed.                                                   | RO        |

| 4    | RFAULT    | Remote fault detected. When set, RFAULT indicates that the link partner has indicated a fault condition by way of auto-negotiation.                  | RO        |

| 3    |           | Auto-negotiation capable. Set to indicate this PHY is capable of auto-negotiation                                                                    | RO        |

| 2    | LINK      | Link status. When set, LINK indicates that the PHY is receiving valid link pulses.                                                                   | RO        |

| 1    | JABBER    | Jabber detected. When set, JABBER indicates the PHY has entered jabber mode. JABBER is cleared after a reset or after TXEN is deasserted for 500 ms. | RO        |

| 0    |           | Extended capability. This bit is hardwired to 1 to indicate that the PHY supports extensions to the IEEE Std 802.3u.                                 | RO        |

†RO = read only

# PHY generic identifier, GEN\_id\_hi, and GEN\_id\_lo at 0x2 and 0x3

These two registers are hardwired to constant values. GEN\_id\_hi is fixed at 0x4000, and GEN\_id\_lo is fixed at 0x5051.

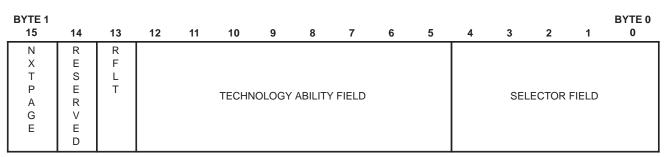

# auto-negotiation advertisement register at 0x4

# Figure 8. Auto-Negotiation Advertisement Register

#### Table 5. Auto-Negotiation Advertisement-Register Bit Functions

|      | BIT                                      | FUNCTION                                                                                                                                                                                                                                                                        | DIRECTION <sup>†</sup> | DEFAULT                                                      |

|------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------------------|

| NO.  | NAME                                     | FUNCTION                                                                                                                                                                                                                                                                        | DIRECTION              | DEFAULT                                                      |

| 15   | NXTPAGE                                  | Auto-negotiation next page. NXTPAGE should be set when there is a next page to transmit. The next page is set by writing to AN_NEXTPAGE.                                                                                                                                        | RO                     | 0                                                            |

| 14   | RESERVED                                 | Reserved                                                                                                                                                                                                                                                                        | RO                     | 0                                                            |

| 13   | RFLT                                     | Remote fault. RFLT enabled indicates to the link partner that there is a fault condition on the TNETE2004. RFLT can be set only by a management entity. This bit does not imply an internal test mode.                                                                          | R/W                    | 0                                                            |

| 12–5 | TECHNOLOGY<br>ABILITY FIELD <sup>‡</sup> | This field indicates the technology abilities advertised to the link partner.<br>Unsupported technologies cannot be transmitted, hence, only two bits have<br>significance.<br>Bit 6: Full-duplex 10BASE-T<br>Bit 5: Half-duplex 10BASE-T<br>All other bits are hardwired to 0. | R/W                    | Bits 5 and 6<br>are set to 1, all<br>others are set<br>to 0. |

| 4–0  | SELECTOR<br>FIELD                        | This field specifies the format of the page to be transmitted. This PHY supports only standard IEEE Std 802.3u base pages, so this field is hardwired to 00001.                                                                                                                 | RO                     |                                                              |

<sup>†</sup>RO = read only, R/W = read/write

After a reset, the PHY attempts to drive the duplex pin. If the pin can be driven high, then bit 6 is set. If the pin can be driven low, then bit 5 is set.

#### auto-negotiation link-partner ability register at 0x5

This register contains the most recently received link control word from the remote PHY. Writing to this register has no effect. The contents of this register are undefined unless either ACOMPLETE (bit 5, register 1) or PAGERX (bit 1, register 6) are set.

When ACOMPLETE is set, the bits in this register are as described in Table 6.

| BYTE 1<br>15                              | 14                                   | 13                         | 12 | 11 | 10    | 9 | 8                 | 7 | 6 | 5 | 4 | 3 | 2                 | 1 | BYTE 0<br>0 |

|-------------------------------------------|--------------------------------------|----------------------------|----|----|-------|---|-------------------|---|---|---|---|---|-------------------|---|-------------|

| L<br>P<br>N<br>X<br>T<br>P<br>A<br>G<br>E | R<br>E<br>S<br>E<br>R<br>V<br>E<br>D | L<br>P<br>R<br>F<br>L<br>T |    |    | TECHN |   | ARTNER<br>ABILITY |   |   |   |   |   | NK-PART<br>LECTOR |   |             |

Figure 9. Auto-Negotiation Link-Partner Ability Register

# auto-negotiation link-partner ability register at 0x5 (continued)

# Table 6. Auto-Negotiation Link-Partner Ability Register Bit Functions

|     | BIT                               | FUNCTION                                                                                                     | DIRECTION |

|-----|-----------------------------------|--------------------------------------------------------------------------------------------------------------|-----------|

| NO. | NAME                              | FUNCTION                                                                                                     | DIRECTION |

| 15  | LPNXTPAGE                         | Link-partner auto-negotiation next page. LPNXTPAGE indicates that the link partner has another page to send. | RO        |

| 14  | RESERVED                          | Reserved                                                                                                     | RO        |

| 13  | LPRFLT                            | Link-partner remote fault. LPRRFLT indicates that the link partner is reporting a fault condition.           | RO        |

| 12  | RESERVED                          | Reserved for future abilities. Read as 0.                                                                    | RO        |

| 11  | RESERVED                          | Reserved for future abilities. Read as 0.                                                                    | RO        |

| 10  | RESERVED                          | Reserved for future abilities. Read as 0.                                                                    | RO        |

| 9   | 100BASE-T4                        | 100Base-T4 is supported by the link partner.                                                                 | RO        |

| 8   | 100BASE-TXFD                      | 100Base-TX full-duplex is supported by the link partner.                                                     | RO        |

| 7   | 100BASE-TXHD                      | 100Base-TX half-duplex is supported by the link partner.                                                     | RO        |

| 6   | 10BASE-TFD                        | 10BASE-T full-duplex is supported by the link partner.                                                       | RO        |

| 5   | 10BASE-THD                        | 10BASE-T half-duplex is supported by the link partner.                                                       | RO        |

| 4–0 | LINK-PARTNER<br>SELECTOR<br>FIELD | Identifies the format of this register. The IEEE Std 802.3u base page is indicated by code 00001.            | RO        |

†RO = read only

When PAGERX is set, this register contains a direct copy of the next page received. PAGERX is cleared on a read from this register.

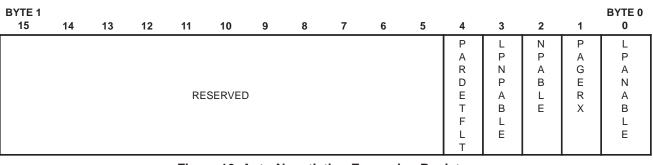

# auto-negotiation expansion register – AN\_exp at 0x6

Figure 10. Auto-Negotiation Expansion Register

# expansion register

Refer to Table 7 for the bit definition of the expansion register.

# Table 7. Auto-Negotiation Expansion-Register Bit Functions

|      | BIT       | FUNCTION                                                                                                                                                                                       | DIDECTION |

|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| NO.  | NAME      | FUNCTION                                                                                                                                                                                       | DIRECTION |

| 15–5 | RESERVED  | Reserved. Read as 0.                                                                                                                                                                           | RO        |

| 4    | PARDETFLT | Parallel detection fault. PARDETFLT indicates multiple links established. This is not supported by this PHY; hence, PARDETFLT is always read as the inverse of LINK.                           | RO        |

| 3    | LPNPABLE  | Link-partner next-page able. LPNPABLE indicates that the link partner is next-page capable.                                                                                                    | RO        |

| 2    | NPABLE    | Next-page able. This PHY is capable of exchanging next pages, so NPABLE is hardwired to 1.                                                                                                     | RO        |

| 1    | PAGERX    | Page received. PAGERX is set after three identical and consecutive link code words have been received from the link partner. PAGERX is cleared when the link-partner ability register is read. | RO        |

| 0    | LPANABLE  | Link-partner auto-negotiation able. LPANABLE is set to 1 when the PHY has received fast link pulses from the link partner.                                                                     | RO        |

†RO = read only

# auto-negotiation next\_page transmit register - AN\_NEXTPAGE at 0x07

| BYTE 1 |    |    |    |    |    |   |        |         |   |   |   |   |   |   | BYTE 0 |

|--------|----|----|----|----|----|---|--------|---------|---|---|---|---|---|---|--------|

| 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8      | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|        |    |    |    |    |    | I | NEXTPA | GE DATA | 1 |   |   |   |   |   |        |

#### Figure 11. Auto-Negotiation Next\_Page Transmit Register

When written to, this register sets the next page to be transmitted by way of auto-negotiation. Writing to this register instructs the auto-negotiation system to transmit a next page.

# TNETE2004 identification register, QUADB\_ID at 0x10

This register is hardwired to the value 0x0005. Writing to this register has no effect.

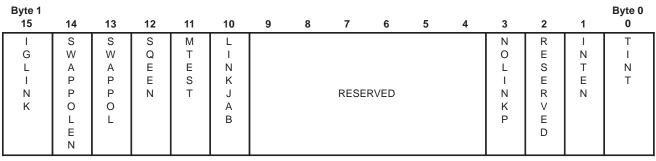

# TNETE2004 control register – QuadPHY\_ctl at 0x11

Figure 12. TNETE2004 Control Register

# Table 8. TNETE2004 Control Register Bit Functions

|     | BIT       | FUNCTION                                                                                                                                                                                                                                                                                                                                |           |         |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|

| NO. | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                | DIRECTION | DEFAULT |

| 15  | IGLINK    | Ignore link. When IGLINK is 0, the 10BASE-T PHY expects to receive link pulses and sets the LINK bit in the GEN_sts register to 0 if they are not present. When IGLINK is set to 1, link pulses are ignored, and the LINK bit always is set to 1.                                                                                       | R/W       | 0       |

| 14  | SWAPPOLEN | Swap polarity enable. When set, SWAPPOLEN enables the PHY to reverse the polarity of received signals after reception of seven inverted link pulses.                                                                                                                                                                                    | R/W       | 1       |

| 13  | SWAPPOL   | Swap polarity. When set, SWAPPOL forces the PHY to reverse the polarity of received signals. Writing to SWAPPOL has no effect when SWAPPOLEN is set to 1. However, when read, SWAPPOL always reflects the current polarity setting.                                                                                                     | R/W       | 0       |

| 12  | SQEEN     | SQE enable. Writing a 1 to SQEEN causes the 10BASE-T PHY to perform the SQE test function at the end of packet transmission.                                                                                                                                                                                                            | R/W       | Pin     |

| 11  | MTEST     | Manufacturing test. When MTEST is set to 1, the PHYs are placed in manufacturing test mode. Manufacturing test mode is reserved for Texas Instruments manufacturing test only. Operation of the device with this bit set is undefined. MTEST is common to all PHYs.                                                                     | R/W       | 0       |

| 10  | LINKJAB   | Link jabber indication for all PHYs. When LINKJAB is set to a 1, each PHY deasserts the LINK pin when in JABBER mode. When set to 0, JABBER has no effect on link status. Setting this bit has no effect on the value of the LINK bit in GEN_STS register.                                                                              | R/W       | 1       |