- High Output Drive . . . >300 mA

- Rail-To-Rail Output

- Unity-Gain Bandwidth . . . 2 MHz

- Slew Rate . . . 1.5 V/μs

- Supply Current . . . 700-µA/Per Channel

- Supply Voltage Range . . . 2.5 V to 6 V

- Specified Temperature Range:

- $T_A = 0^{\circ}C$  to  $70^{\circ}C \dots$  Commercial Grade

- $T_A = -40^{\circ}C$  to  $125^{\circ}C$  . . . Industrial Grade

- Universal OpAmp EVM

#### description

The TLV411x single supply operational amplifiers provide output currents in excess of 300 mA at 5 V. This enables standard pin-out amplifiers to be used as high current buffers or in coil driver applications. The TLV4110 and TLV4113 comes with a shutdown feature.

The TLV411x is available in the ultra small MSOP PowerPAD<sup>™</sup> package, which offers the exceptional thermal impedance required for amplifiers delivering high current levels.

All TLV411x devices are offered in PDIP, SOIC (single and dual) and MSOP PowerPAD (dual).

|                      |           | FAMIL         | Y PACKAG | E TABLE |          | -                                |

|----------------------|-----------|---------------|----------|---------|----------|----------------------------------|

| DEVICE               | NUMBER OF | PACKAGE TYPES |          |         | SHUTDOWN | UNIVERSAL                        |

| DEVICE               | CHANNELS  | MSOP          | PDIP     | SOIC    | SHOTDOWN | EVM BOARD                        |

| TLV4110 <sup>†</sup> | 1         | 8             | 8        | 8       | Yes      |                                  |

| TLV4111†             | 1         | 8             | 8        | 8       | —        | Refer to the EVM Selection Guide |

| TLV4112              | 2         | 8             | 8        | 8       | —        | (Lit# SLOU060)                   |

| TLV4113†             | 2         | 10            | 14       | 14      | Yes      | ,                                |

<sup>†</sup> This device is in the Product Preview stage of development. Contact the local TI sales office for more information.

LOW-LEVEL OUTPUT VOLTAGE vs LOW-LEVEL OUTPUT CURRENT 1.0 V<sub>DD</sub> = 3 V 0.9  $T_A = 70^{\circ}C$ 0.8  $T_A = 25^{\circ}C$ 0.7 T<sub>A</sub> = 0°C 0.6  $T_A = -40^{\circ}C$ 0.5 . T<sub>A</sub> = 125°C 0.4 0.3 0.2 0.1 0.0 150 50 100 200 250 300

I<sub>OL</sub> – Low-Level Output Current – mA

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Low-Level Output Voltage

ر م

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warrantly. Production processing does not necessarily include testing of all parameters.

Copyright  $\ensuremath{\textcircled{\odot}}$  2000, Texas Instruments Incorporated

1

#### TLV4112 D, DGN, OR P PACKAGE (TOP VIEW) 10UT II V<sub>DD</sub> 1 8 1IN-I 2 7 🔟 20UT **A** 6 1IN+ 3-2IN-GND 4 5 2IN+ П

SLOS289A - DECEMBER 1999 - REVISED APRIL 2000

#### **TLV4110 AND TLV4111 AVAILABLE OPTIONS**

|                |                                    | PACKAGED DEVI                       | CES     |                    |

|----------------|------------------------------------|-------------------------------------|---------|--------------------|

| TA             | SMALL OUTLINE<br>(D) <sup>†‡</sup> | SMALL OUTLINE<br>(DGN) <sup>†</sup> | SYMBOL  | PLASTIC DIP<br>(P) |

| 0°C to 70°C    | TLV4110CD                          | TLV4110CDGN                         | xxTIAHL | TLV4110CP          |

| 0-01070-0      | TLV4111CD                          | TLV4111CDGN                         | xxTIAHN | TLV4111CP          |

| -40°C to 125°C | TLV4110ID                          | TLV4110IDGN                         | xxTIAHM | TLV4110IP          |

| -40 0 10 123 0 | TLV4111ID                          | TLV4111IDGN                         | XXTIAHO | TLV4111IP          |

<sup>†</sup> This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TLV4110CDR).

<sup>‡</sup> In the SOIC package, the maximum RMS output power is thermally limited to 350 mW; 700 mW peaks can be driven, as long as the RMS value is less than 350 mW.

| TLV4112 AND TLV4113 AVAILABLE OPTION |

|--------------------------------------|

|--------------------------------------|

|                |                                     |                                          | PACKAGED | DEVICES                             |         |                        |

|----------------|-------------------------------------|------------------------------------------|----------|-------------------------------------|---------|------------------------|

| TA             | SMALL OUTLINE<br>(D) <sup>†</sup> § | SMALL OUT-<br>LINE<br>(DGN) <sup>†</sup> | SYMBOL   | SMALL OUTLINE<br>(DGQ) <sup>†</sup> | SYMBOL  | PLASTIC DIP<br>(P)     |

| 0°C to 70°C    | TLV4112CD                           | TLV4112DGN                               | xxTIAHP  | —                                   | —       | TLV4112CP              |

| 0-01070-0      | TLV4113CD <sup>‡</sup>              | —                                        | —        | TLV4113CDGN <sup>‡</sup>            | xxTIAHR | TLV4113CN <sup>‡</sup> |

| -40°C to 125°C | TLV4112ID                           | TLV4112IDGN                              | xxTIAHQ  | _                                   | _       | TLV4112IP              |

| -40 0 10 125 0 | TLV4113ID‡                          | —                                        | —        | TLV4113IDGN <sup>‡</sup>            | xxTIAHS | TLV4113IN <sup>‡</sup> |

<sup>†</sup> This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TLV4112CDR). <sup>‡</sup> This device is in the Product Preview stage of development. Contact the local TI sales office for more information.

§ In the SOIC package, the maximum RMS output power is thermally limited to 350 mW; 700 mW peaks can be driven, as long as the RMS value is less than 350 mW.

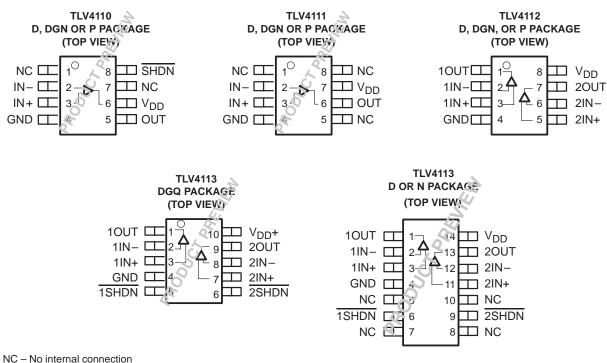

#### **TLV411x PACKAGE PINOUTS**

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage V/ (acc Note 1) 7V/                                                                |

|---------------------------------------------------------------------------------------------------|

| Supply voltage, V <sub>DD</sub> (see Note 1)                                                      |

| Differential input voltage, V <sub>ID</sub> $\pm$ V <sub>DD</sub>                                 |

| Input voltage range, V <sub>I</sub> ±V <sub>DD</sub>                                              |

| Output current,I <sub>O</sub> (see Note 2)                                                        |

| Continuous /RMS output current, I <sub>O</sub> (each output of amplifier): $T_J \le 105^{\circ}C$ |

| T <sub>J</sub> ≤ 150°C                                                                            |

| Peak output current, I <sub>O</sub> (each output of amplifier: $T_J \le 105^{\circ}C$             |

| $T_{J} \le 150^{\circ}C$                                                                          |

| Continuous total power dissipation                                                                |

| Operating free-air temperature range, T <sub>A</sub> : C suffix                                   |

| I suffix                                                                                          |

| Maximum junction temperature, T <sub>J</sub> 150°C                                                |

| Storage temperature range, T <sub>stg</sub> 65°C to 150°C                                         |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                                      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential voltages, are with respect to GND.

2. To prevent permanent damage the die temperature must not exceed the maximum junction temperature.

#### DISSIPATION RATING TABLE

| PACKAGE   | θJC<br>(°C/W) | <sup>θ</sup> ЈА<br>(°С/W) | $T_A \le 25^{\circ}C$ POWER RATING |

|-----------|---------------|---------------------------|------------------------------------|

| D (8)     | 38.3          | 176                       | 710 mW                             |

| D (14)    | 26.9          | 122.3                     | 1022 mW                            |

| DGN (8)‡  | 4.7           | 52.7                      | 2.37 W                             |

| DGQ (10)‡ | 4.7           | 52.3                      | 2.39 W                             |

| P (8)     | 41            | 104                       | 1200 mW                            |

| N (14)    | 32            | 78                        | 1600 mW                            |

<sup>‡</sup> See The Texas Instruments document, *PowerPAD Thermally Enhanced Package Application Report* (literature number SLMA002), for more information on the PowerPAD package. The thermal data was measured on a PCB layout based on the information in the section entitled *Texas Instruments Recommended Board for PowerPAD* on page 33 of the before mentioned document.

#### recommended operating conditions

|                                                | MIN      | MAX                   | UNIT |                      |    |

|------------------------------------------------|----------|-----------------------|------|----------------------|----|

| Supply voltage, V <sub>DD</sub>                | 2.5      | 6                     | V    |                      |    |

| Common-mode input voltage range, VICR          |          |                       | 0    | V <sub>DD</sub> -1.5 | V  |

| Operating free-air temperature Te              | C-suffix |                       | 0    | 70                   | °C |

| Operating free-air temperature, T <sub>A</sub> |          | I-suffix              |      | 125                  | C  |

|                                                | )//()    | V <sub>DD</sub> = 3 V | 2.1  |                      |    |

|                                                | V(on)    | V <sub>DD</sub> = 5 V | 3.8  |                      | V  |

| Shutdown turn on/off voltage level§            | V(off)   | V <sub>DD</sub> = 3 V |      | 0.9                  | v  |

|                                                | V(011)   | V <sub>DD</sub> = 5 V |      | 1.65                 |    |

§ Relative to GND

## electrical characteristics at recommend operating conditions, $V_{DD}$ = 3 V and 5 V (unless otherwise noted)

#### dc performance

|                                  | PARAMETER                                       | TEST CON                                        | DITIONS                                  | T <sub>A</sub> † | MIN | TYP | MAX  | UNITS |

|----------------------------------|-------------------------------------------------|-------------------------------------------------|------------------------------------------|------------------|-----|-----|------|-------|

| Vie                              | Input offset voltage                            |                                                 |                                          | 25°C             |     | 175 | 3500 | μV    |

| VIO                              | input onset voltage                             | $V_{IC} = V_{DD}/2,$<br>$R_{I} = 100 \Omega,$   | $V_{O} = V_{DD}/2 ,$ $R_{O} = 50 \Omega$ | Full range       |     |     | 4000 | μv    |

| αVIO                             | Offset voltage draft                            | 11( <u></u> = 100 <u>32</u> ,                   | 112 - 00 35                              | 25°C             |     | 3   |      | μV/°C |

| CMRR Common-mode rejection ratio | $V_{DD} = 3 V,$<br>R <sub>S</sub> = 50 $\Omega$ | $V_{IC} = 0$ to 2 V,                            | 25°C                                     |                  | 63  |     | dB   |       |

|                                  | Common-mode rejection ratio                     | $V_{DD} = 5 V,$<br>R <sub>S</sub> = 50 $\Omega$ | $V_{IC} = 0$ to 4 V,                     | 25°C             |     | 68  |      | uв    |

|                                  |                                                 |                                                 | B: -100 O                                | 25°C             | 78  | 84  |      |       |

|                                  |                                                 | V <sub>DD</sub> = 3 V,                          | R <sub>L</sub> =100 Ω                    | Full range       | 67  |     |      |       |

|                                  |                                                 | VO(PP)=0 to 1V                                  | R <sub>I</sub> =10 kΩ                    | 25°C             | 85  | 100 |      |       |

| A=                               | Large-signal differential voltage               |                                                 | KL=10 KS2                                | Full range       | 75  |     |      | dB    |

| AVD                              | amplification                                   |                                                 | B: -100.0                                | 25°C             | 88  | 94  |      | uБ    |

|                                  |                                                 | V <sub>DD</sub> = 5 V,                          | R <sub>L</sub> =100 Ω                    | Full range       | 75  |     |      |       |

|                                  |                                                 | VO(PP)=0 to 3V                                  |                                          | 25°C             | 90  | 110 |      |       |

|                                  |                                                 |                                                 | $R_L=10 k\Omega$                         | Full range       | 85  |     |      |       |

<sup>†</sup> Full range is 0°C to 70°C for C suffix and –40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

#### input characteristics

|                   | PARAMETER                                                                   | TEST CO                                             | NDITIONS               | T <sub>A</sub> †       | MIN            | TYP  | MAX | UNITS |

|-------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|------------------------|------------------------|----------------|------|-----|-------|

| )/                |                                                                             | Measured over                                       | V <sub>DD</sub> = 3 V  | 25°C and<br>Full range | 0<br>to<br>1.5 |      |     | V     |

| VICR              | Common-mode input voltage range CMRR range,<br>R <sub>S</sub> = 50 $\Omega$ | V <sub>DD</sub> = 5 V                               | 25°C and<br>Full range | 0<br>to<br>3.5         |                |      | V   |       |

|                   |                                                                             |                                                     | -                      | 25°C                   |                | 0.3  | 25  |       |

| lio               | Input offset current                                                        | $V_{IC} = V_{DD}/2$                                 | TLV411xC               | Eull rongo             |                |      | 50  |       |

|                   |                                                                             |                                                     | TLV411xI               | - Full range           |                |      | 250 | ~ ^   |

|                   |                                                                             |                                                     | -                      | 25°C                   |                | 0.3  | 50  | pА    |

| IIB               | Input bias current                                                          | $V_{O} = V_{DD}/2,$<br>R <sub>S</sub> = 50 $\Omega$ | TLV411xC               | E.I.I.                 |                |      | 100 |       |

|                   |                                                                             | RS = 50.22                                          | TLV411xI               | - Full range           |                |      | 500 |       |

| <sup>r</sup> i(d) | Differential input resistance                                               |                                                     |                        | 25°C                   |                | 1000 |     | GΩ    |

| CIC               | Common-mode input capacitance                                               | f = 100 Hz                                          |                        | 25°C                   |                | 5    |     | pF    |

<sup>†</sup> Full range is 0°C to 70°C for C suffix and –40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

# electrical characteristics at specified free-air temperature, $V_{DD} = 3 V$ and 5 V (unless otherwise noted) (continued)

#### output characteristics

|     | PARAMETER                     | TEST CONDITI                         | ONS                       | T <sub>A</sub> † | MIN  | TYP  | MAX  | UNITS |

|-----|-------------------------------|--------------------------------------|---------------------------|------------------|------|------|------|-------|

|     |                               |                                      | 40                        | 25°C             | 2.7  | 2.97 |      |       |

|     |                               |                                      | I <sub>OH</sub> = -10 mA  | Full range       | 2.7  |      |      | v     |

|     |                               | $V_{DD} = 3 V$ , $V_{IC} = V_{DD}/2$ | 100 m 4                   | 25°C             | 2.6  | 2.73 |      | v     |

|     |                               |                                      | I <sub>OH</sub> =-100 mA  | Full range       | 2.6  |      |      |       |

|     |                               |                                      | 10 mA                     | 25°C             | 4.7  | 4.96 |      |       |

| Vон | High-level output voltage     |                                      | I <sub>OH</sub> = -10 mA  | Full range       | 4.7  |      |      |       |

|     |                               |                                      | I <sub>OH</sub> = -100 mA | 25°C             | 4.6  | 4.76 |      |       |

|     |                               | $V_{DD} = 5 V$ , $V_{IC} = V_{DD}/2$ | 10H = -100  IIIA          | Full range       | 4.6  |      |      | V     |

|     |                               | 25°C 4.45                            | 4.6                       |                  |      |      |      |       |

|     |                               |                                      | I <sub>OH</sub> = -200 mA | -40°C to<br>85°C | 4.35 |      |      |       |

|     |                               | V <sub>DD</sub> = 3 V and 5 V,       | lot = 10  mA              | 25°C             |      | 0.03 | 0.1  |       |

|     |                               |                                      | I <sub>OL</sub> = 10 mA   | Full range       |      |      | 0.1  |       |

|     |                               | $V_{IC} = V_{DD}/2$                  | lot = 100  mA             | 25°C             |      | 0.33 | 0.4  |       |

| VOL | Low-level output voltage      |                                      | I <sub>OL</sub> = 100 mA  | Full range       |      |      | 0.55 | 1 v   |

|     |                               |                                      |                           | 25°C             |      | 0.38 | 0.6  |       |

|     |                               | $V_{DD} = 5 V$ , $V_{IC} = V_{DD}/2$ | I <sub>OL</sub> = 200 mA  | -40°C to<br>85°C |      |      | 0.7  |       |

| 1   |                               |                                      | V <sub>DD</sub> = 3 V     | 25°C             |      | ±220 |      | mA    |

| 10  | Output current <sup>‡</sup>   | Measured at 0.5 V from rail          | V <sub>DD</sub> = 5 V     | 25-0             |      | ±320 |      | mA    |

|     |                               | Sourcing                             |                           | 25°C             |      | 800  |      | mA    |

| los | Short-circuit output current‡ | Sinking                              |                           | 250              |      | 800  |      | mA    |

<sup>†</sup> Full range is 0°C to 70°C for C suffix and -40°C to 125°C for I suffix. If not specified, full range is -40°C to 125°C.

<sup>‡</sup> When driving output currents in excess of 200 mA, the MSOP PowerPAD package is required for thermal dissipation.

#### power supply

|       | PARAMETER                                                        | TEST CONDITIONS                         | Тд         | MIN | TYP | MAX  | UNITS |

|-------|------------------------------------------------------------------|-----------------------------------------|------------|-----|-----|------|-------|

|       | IDD Supply current (per channel)                                 |                                         | 25°C       |     | 700 | 1000 |       |

| DD    | Supply current (per channel)                                     | $V_{O} = V_{DD}/2$                      | Full range |     |     | 1500 | μA    |

|       |                                                                  | V <sub>DD</sub> =2.7 to 3.3 V, No load, | 25°C       | 70  | 82  |      |       |

| Kaura | Power supply rejection ratio $(A)((A)(a))$                       | $V_{IC} = V_{DD}/2 V$                   | Full range | 65  |     |      | dB    |

| KSVR  | Power supply rejection ratio ( $\Delta V_{DD} / \Delta V_{IO}$ ) | V <sub>DD</sub> =4.5 to 5.5 V, No load, | 25°C       | 70  | 79  |      | uБ    |

|       |                                                                  | $V_{IC} = V_{DD}/2 V$                   | Full range | 65  |     |      |       |

<sup>†</sup> Full range is 0°C to 70°C for C suffix and -40°C to 125°C for I suffix. If not specified, full range is -40°C to 125°C.

## electrical characteristics at specified free-air temperature, $V_{DD}$ = 3 V and 5 V (unless otherwise noted) (continued)

#### dynamic performance

|                | PARAMETER               | TEST CONDITION                                        | S                      | T <sub>A</sub> † | MIN  | TYP  | MAX | UNITS |

|----------------|-------------------------|-------------------------------------------------------|------------------------|------------------|------|------|-----|-------|

| GBWP           | Gain bandwidth product  | RL=100 Ω                                              | CL=10 pF               | 25°C             |      | 2.7  |     | MHz   |

|                |                         |                                                       | N 0.V                  | 25°C             | 0.8  | 1.57 |     |       |

| SR             |                         | $V_{O}(pp) = 2 V,$<br>R <sub>L</sub> = 100 $\Omega$ , | V <sub>DD</sub> = 3 V  | Full range       | 0.55 |      |     |       |

| SK             | Slew rate at unity gain | $R_{L} = 100 \Omega_{2},$<br>$C_{L} = 10 \text{ pF}$  |                        | 25°C             | 1    | 1.57 |     | V/μs  |

|                |                         |                                                       | V <sub>DD</sub> = 5 V  | Full range       | 0.7  |      |     | 1     |

| φM             | Phase margin            | <b>D</b> (00.0                                        | С. 10 т.               | 25°C             |      | 66   |     |       |

|                | Gain margin             | $R_{L} = 100 \Omega$ ,                                | C <sub>L</sub> = 10 pF | 25-0             |      | 16   |     | dB    |

|                | Settling time           | $V_{(STEP)pp} = 1 V,$<br>$A_V = -1,$                  | 0.1%                   | 25°C             |      | 0.7  |     |       |

| t <sub>s</sub> |                         | C <sub>L</sub> = 10 pF,<br>R <sub>L</sub> = 100 Ω     | 0.01%                  | 250              |      | 1.3  |     | μs    |

<sup>†</sup> Full range is 0°C to 70°C for C suffix and –40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

#### noise/distortion performance

|                | PARAMETER                            | TEST CONDITIONS                                                | -                    | Τ <sub>Α</sub> | MIN T | YP MAX | UNITS  |  |

|----------------|--------------------------------------|----------------------------------------------------------------|----------------------|----------------|-------|--------|--------|--|

|                |                                      | $V_{O(pp)} = V_{DD}/2 V,$<br>$R_L = 100 \Omega,$<br>f = 100 Hz | A <sub>V</sub> = 1   |                | 0.0   | 025    |        |  |

| THD+N          | Total harmonic distortion plus noise |                                                                | A <sub>V</sub> = 10  | 2500           | 0.0   | 035    |        |  |

|                |                                      |                                                                | A <sub>V</sub> = 100 |                | C     | ).15   |        |  |

| N              | f = 100 Hz                           |                                                                |                      | 25°C           |       | 55     | nV/√Hz |  |

| Vn             | Equivalent input noise voltage       | f = 10 kHz                                                     |                      |                |       | 10     | nv/vHz |  |

| I <sub>n</sub> | Equivalent input noise current       | f = 1 kHz                                                      |                      |                | C     | ).31   | fA/√Hz |  |

#### shutdown characteristics

|           | PARAMETER                                     | TEST CONDITIONS        | T <sub>A</sub> † | MIN | TYP | MAX | UNITS |

|-----------|-----------------------------------------------|------------------------|------------------|-----|-----|-----|-------|

|           | Supply current in shutdown mode (per channel) | SHDN = 0 V             | 25°C             |     | TBD |     | μA    |

| IDD(SHDN) | (TLV4110, TLV4113)                            |                        | Full range       |     | TBD |     | μΑ    |

| t(ON)     | Amplifier turnon time‡                        | D 400.0                | 25°C             |     | TBD |     |       |

| t(Off)    | Amplifier turnoff time‡                       | R <sub>L</sub> = 100 Ω | 250              |     | TBD |     | μs    |

<sup>†</sup> Full range is 0°C to 70°C for C suffix and –40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

<sup>‡</sup> Disable time and enable time are defined as the interval between application of the logic signal to SHDN and the point at which the supply current has reached half its final value.

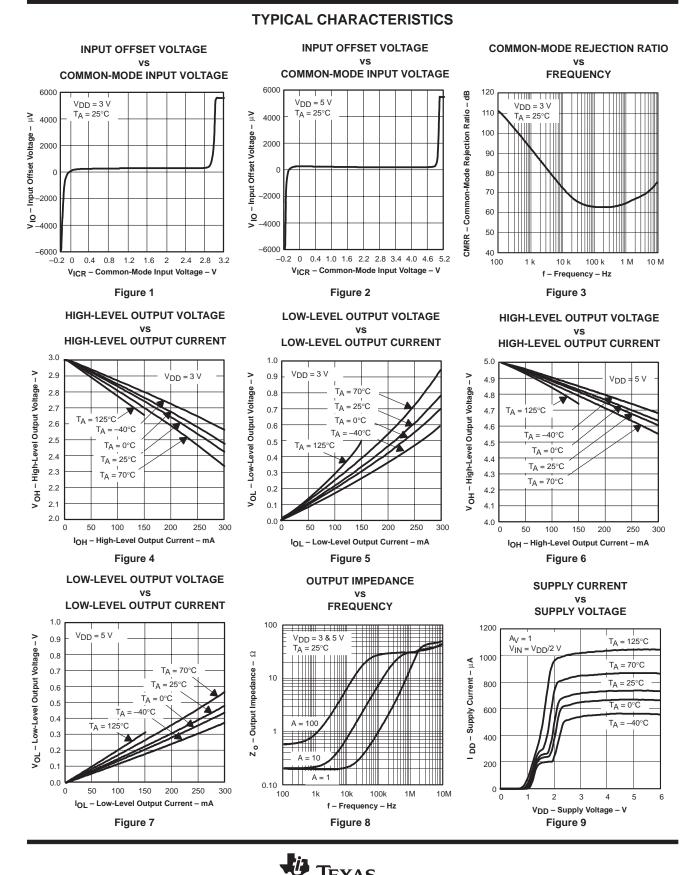

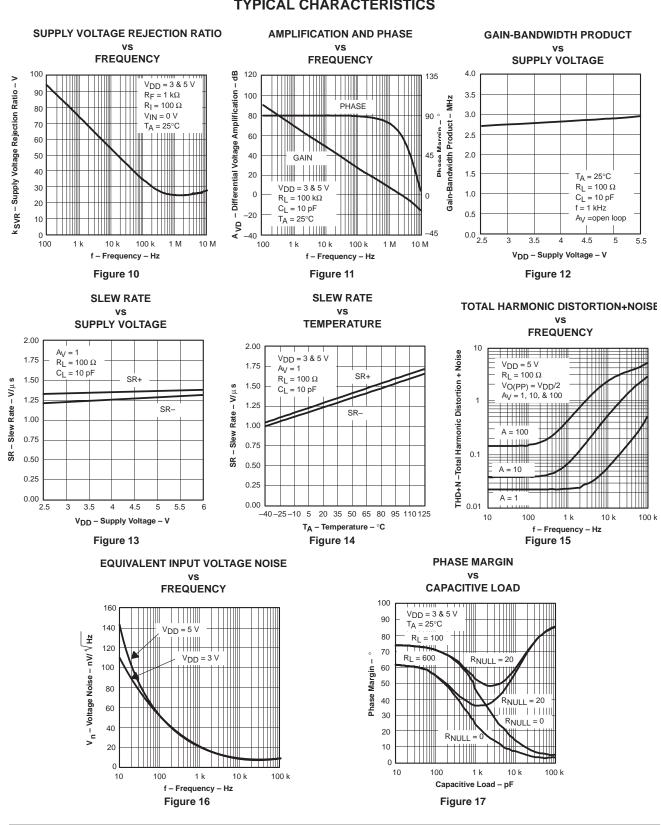

#### **TYPICAL CHARACTERISTICS**

#### **Table of Graphs**

|                |                                              |                              | FIGURE |

|----------------|----------------------------------------------|------------------------------|--------|

| VIO            | Input offset voltage                         | vs Common-mode input voltage | 1, 2   |

| CMRR           | Common-mode rejection ratio                  | vs Frequency                 | 3      |

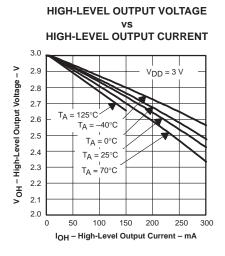

| VOH            | High-level output voltage                    | vs High-level output current | 4, 6   |

| VOL            | Low-level output voltage                     | vs Low-level output current  | 5, 7   |

| Z <sub>0</sub> | Output impedance                             | vs Frequency                 | 8      |

| IDD            | Supply current                               | vs Supply voltage            | 9      |

| <b>k</b> SVR   | Supply voltage rejection ratio               | vs Frequency                 | 10     |

| AVD            | Differential voltage amplification and phase | vs Frequency                 | 11     |

|                | Gain-bandwidth product                       | vs Supply voltage            | 12     |

| 00             |                                              | vs Supply voltage            | 13     |

| SR             | Slew rate                                    | vs Temperature               | 14     |

|                | Total harmonic distortion+noise              | vs Frequency                 | 15     |

| V <sub>n</sub> | Equivalent input voltage noise               | vs Frequency                 | 16     |

|                | Phase margin                                 | vs Capacitive load           | 17     |

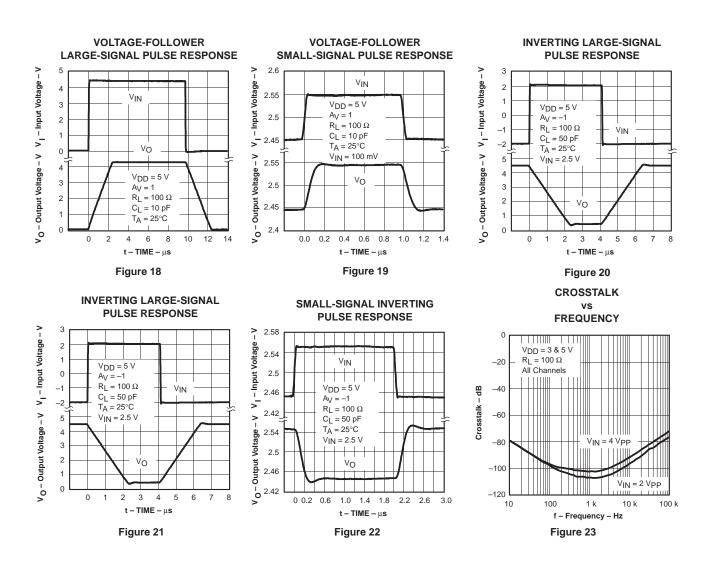

|                | Voltage-follower signal pulse response       | vs Time                      | 18, 19 |

|                | Inverting large-signal pulse response        | vs Time                      | 20, 21 |

|                | Small-signal inverting pulse response        | vs Time                      | 22     |

|                | Crosstalk                                    | vs Frequency                 | 23     |

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

INSTRUMENTS POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SLOS289A - DECEMBER 1999 - REVISED APRIL 2000

**TYPICAL CHARACTERISTICS**

#### **TYPICAL CHARACTERISTICS**

#### **APPLICATION INFORMATION**

#### shutdown function

Two members of the TLV411x family (TLV4110/3) have a shutdown terminal for conserving battery life in portable applications. When the shutdown terminal is tied low, the supply current is reduced to just nano amps per channel, the amplifier is disabled, and the outputs are placed in a high impedance mode. In order to save power in shutdown mode, an external pullup resistor is required, therefore, to enable the amplifier the shutdown terminal must be pulled high. When the shutdown terminal is left floating, care should be taken to ensure that parasitic leakage current at the shutdown terminal does not inadvertently place the operational amplifier into shutdown.

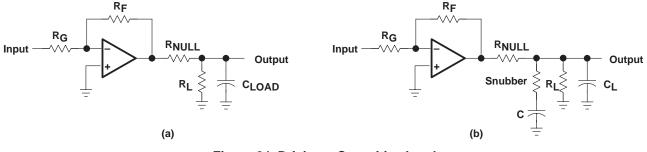

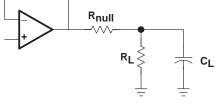

#### driving a capacitive load

When the amplifier is configured in this manner, capacitive loading directly on the output will decrease the device's phase margin leading to high frequency ringing or oscillations. Therefore, for capacitive loads of greater than 1 nF, it is recommended that a resistor be placed in series ( $R_{NULL}$ ) with the output of the amplifier, as shown in Figure 24. A maximum value of 20  $\Omega$  should work well for most applications.

Figure 24. Driving a Capacitive Load

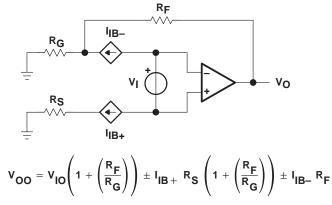

#### offset voltage

The output offset voltage, ( $V_{OO}$ ) is the sum of the input offset voltage ( $V_{IO}$ ) and both input bias currents ( $I_{IB}$ ) times the corresponding gains. The following schematic and formula can be used to calculate the output offset voltage:

Figure 25. Output Offset Voltage Model

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

#### **APPLICATION INFORMATION**

Figure 26

#### general power design considerations

When driving heavy loads at high junction temperatures there is an increased probability of electromigration affecting the long term reliability of ICs. Therefore for this not to be an issue either

- the output current must be limited (at these high junction temperatures) or

- the junction temperature must be limited.

The maximum continuous output current at a die temperature 150°C will be 1/3 of the current at 105°C.

The junction temperature will be dependent on the ambient temperature around the IC, thermal impedance from the die to the ambient and power dissipated within the IC.

$$T_J = T_A + \theta_{JA} \times P_{DIS}$$

Where

P<sub>DIS</sub> is the IC power dissipation and is equal to the output current multiplied by the voltage dropped across the output of the IC.

$\theta_{JA}$  is the thermal impedance between the junction and the ambient temperature of the IC.

$T_{J}$  is the junction temperature.

T<sub>A</sub> is the ambient temperature.

Reducing one or more of these factors will result in a reduced die temperature. The 8-pin SOIC (small outline integrated circuit) has a thermal impedance from junction to ambient of 176°C/W. For this reason we recommend that the maximum power dissipation of the 8-pin SOIC package be limited to 350 mW, with peak dissipation of 700 mW as long as the RMS value is less than 350 mW.

The use of the MSOP PowerPAD<sup>™</sup> dramatically reduces the thermal impedance from junction to case. And with correct mounting, the reduced thermal impedance will greatly increase the IC's permissible power dissipation and output current handling capability. For example, the power dissipation of the PowerPAD<sup>™</sup> is increased to above 1 W. Sinusoidal and pulse-width modulated output signals will also increase the output current capability. The equivalent dc current is proportional to the square-root of the duty cycle:

| I <sub>DC(EQ)</sub> <sup>■</sup> | = $I_{Cont} \times$ | √(duty | cycle) |

|----------------------------------|---------------------|--------|--------|

|----------------------------------|---------------------|--------|--------|

| CURRENT DUTY CYCLE<br>AT PEAK RATED CURRENT | EQUIVALENT DC CURRENT<br>AS A PERCENTAGE OF PEAK |

|---------------------------------------------|--------------------------------------------------|

| 100                                         | 100                                              |

| 70                                          | 84                                               |

| 50                                          | 71                                               |

Note that with an operational amplifier, a duty cycle of 70% would often result in the op amp sourcing current 70% of the time and sinking current 30%, therefore, the equivalent dc current would still be 0.84 times the continuous current rating at a particular junction temperature.

#### **APPLICATION INFORMATION**

#### general PowerPAD design considerations

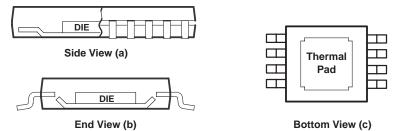

The TLV411x is available in a thermally-enhanced PowerPAD family of packages. These packages are constructed using a downset leadframe upon which the die is mounted [see Figure 27(a) and Figure 27(b)]. This arrangement results in the lead frame being exposed as a thermal pad on the underside of the package [see Figure 27(c)]. Because this thermal pad has direct thermal contact with the die, excellent thermal performance can be achieved by providing a good thermal path away from the thermal pad.

The PowerPAD package allows for both assembly and thermal management in one manufacturing operation. During the surface-mount solder operation (when the leads are being soldered), the thermal pad can also be soldered to a copper area underneath the package. Through the use of thermal paths within this copper area, heat can be conducted away from the package into either a ground plane or other heat dissipating device.

The PowerPAD package represents a breakthrough in combining the small area and ease of assembly of surface mount with the, heretofore, awkward mechanical methods of heatsinking.

NOTE A: The thermal pad is electrically isolated from all terminals in the package.

Although there are many ways to properly heatsink the PowerPAD package, the following steps illustrate the recommended approach.

**Thermal Pad Area**

Single or Dual

SLOS289A - DECEMBER 1999 - REVISED APRIL 2000

#### **APPLICATION INFORMATION**

#### general PowerPAD design considerations (continued)

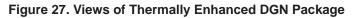

- 1. Prepare the PCB with a top side etch pattern as shown in Figure 28. There should be etch for the leads as well as etch for the thermal pad.

- 2. Place five holes (dual) or nine holes (quad) in the area of the thermal pad. These holes should be 13 mils in diameter. Keep them small so that solder wicking through the holes is not a problem during reflow.

- 3. Additional vias may be placed anywhere along the thermal plane outside of the thermal pad area. This helps dissipate the heat generated by the TLV411x IC. These additional vias may be larger than the 13-mil diameter vias directly under the thermal pad. They can be larger because they are not in the thermal pad area to be soldered so that wicking is not a problem.

- 4. Connect all holes to the internal ground plane.

- 5. When connecting these holes to the ground plane, **do not** use the typical web or spoke via connection methodology. Web connections have a high thermal resistance connection that is useful for slowing the heat transfer during soldering operations. This makes the soldering of vias that have plane connections easier. In this application, however, low thermal resistance is desired for the most efficient heat transfer. Therefore, the holes under the TLV411x PowerPAD package should make their connection to the internal ground plane with a complete connection around the entire circumference of the plated-through hole.

- 6. The top-side solder mask should leave the terminals of the package and the thermal pad area with its five holes (dual) or nine holes (quad) exposed. The bottom-side solder mask should cover the five or nine holes of the thermal pad area. This prevents solder from being pulled away from the thermal pad area during the reflow process.

- 7. Apply solder paste to the exposed thermal pad area and all of the IC terminals.

- 8. With these preparatory steps in place, the TLV411x IC is simply placed in position and run through the solder reflow operation as any standard surface-mount component. This results in a part that is properly installed.

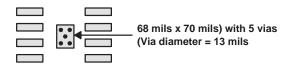

For a given  $\theta_{JA}$ , the maximum power dissipation is shown in Figure 30 and is calculated by the following formula:

$$\mathsf{P}_{\mathsf{D}} = \left(\frac{\mathsf{T}_{\mathsf{MAX}} - \mathsf{T}_{\mathsf{A}}}{\theta_{\mathsf{JA}}}\right)$$

Where:

$\begin{array}{ll} \mathsf{P}_{\mathsf{D}} &= \mathsf{Maximum power dissipation of TLV411x IC (watts)} \\ \mathsf{T}_{\mathsf{MAX}} &= \mathsf{Absolute maximum junction temperature (150°C)} \\ \mathsf{T}_{\mathsf{A}} &= \mathsf{Free-ambient air temperature (°C)} \\ \theta_{\mathsf{JA}} &= \theta_{\mathsf{JC}} + \theta_{\mathsf{CA}} \\ &\quad \theta_{\mathsf{JC}} &= \mathsf{Thermal coefficient from junction to case} \\ &\quad \theta_{\mathsf{CA}} &= \mathsf{Thermal coefficient from case to ambient air (°C/W)} \end{array}$

#### **APPLICATION INFORMATION**

#### general PowerPAD design considerations (continued)

NOTE A: Results are with no air flow and using JEDEC Standard Low-K test PCB.

#### Figure 29. Maximum Power Dissipation vs Free-Air Temperature

The next consideration is the package constraints. The two sources of heat within an amplifier are quiescent power and output power. The designer should never forget about the quiescent heat generated within the device, especially muti-amplifier devices. Because these devices have linear output stages (Class A-B), most of the heat dissipation is at low output voltages with high output currents.

The other key factor when dealing with power dissipation is how the devices are mounted on the PCB. The PowerPAD devices are extremely useful for heat dissipation. But, the device should always be soldered to a copper plane to fully use the heat dissipation properties of the PowerPAD. The SOIC package, on the other hand, is highly dependent on how it is mounted on the PCB. As more trace and copper area is placed around the device,  $\theta_{JA}$  decreases and the heat dissipation capability increases. The currents and voltages shown in these graphs are for the total package. For the dual or quad amplifier packages, the sum of the RMS output currents and voltages should be used to choose the proper package.

SLOS289A - DECEMBER 1999 - REVISED APRIL 2000

#### **APPLICATION INFORMATION**

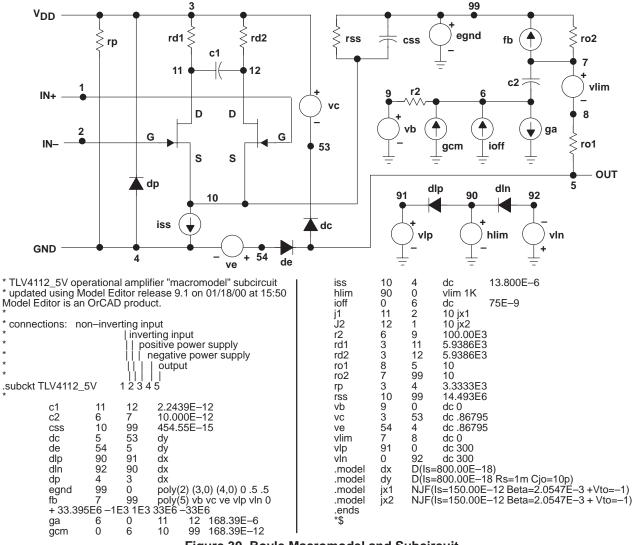

#### macromodel information

Macromodel information provided was derived using Microsim *Parts*<sup>TM</sup>, the model generation software used with Microsim *PSpice*<sup>TM</sup>. The Boyle macromodel (see Note 3) and subcircuit in Figure 30 are generated using the TLV411x typical electrical and operating characteristics at  $T_A = 25^{\circ}$ C. Using this information, output simulations of the following key parameters can be generated to a tolerance of 20% (in most cases):

- Maximum positive output voltage swing

- Maximum negative output voltage swing

- Slew rate

- Quiescent power dissipation

- Input bias current

- Open-loop voltage amplification

- Unity-gain frequency

- Common-mode rejection ratio

- Phase margin

- DC output resistance

- AC output resistance

- Short-circuit output current limit

- NOTE 3: G. R. Boyle, B. M. Cohn, D. O. Pederson, and J. E. Solomon, "Macromodeling of Integrated Circuit Operational Amplifiers," *IEEE Journal* of Solid-State Circuits, SC-9, 353 (1974).

#### Figure 30. Boyle Macromodel and Subcircuit

PSpice and Parts are trademarks of MicroSim Corporation.

#### MECHANICAL DATA

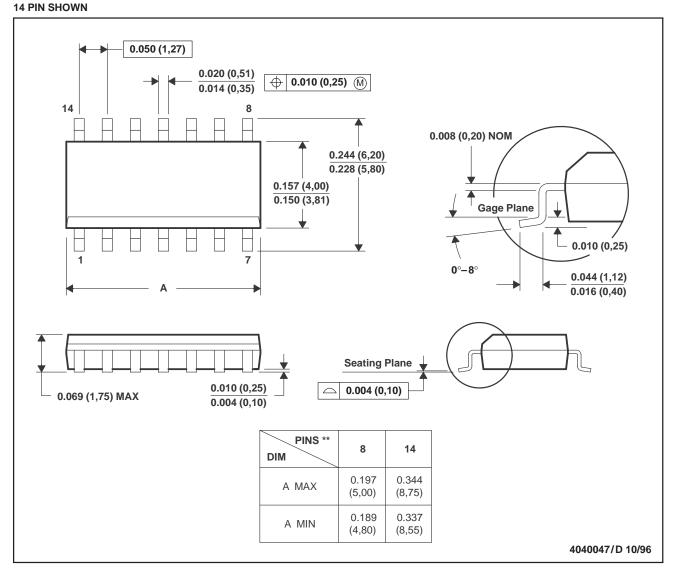

#### PLASTIC SMALL-OUTLINE PACKAGE

### D (R-PDSO-G\*\*)

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-012

#### **MECHANICAL INFORMATION**

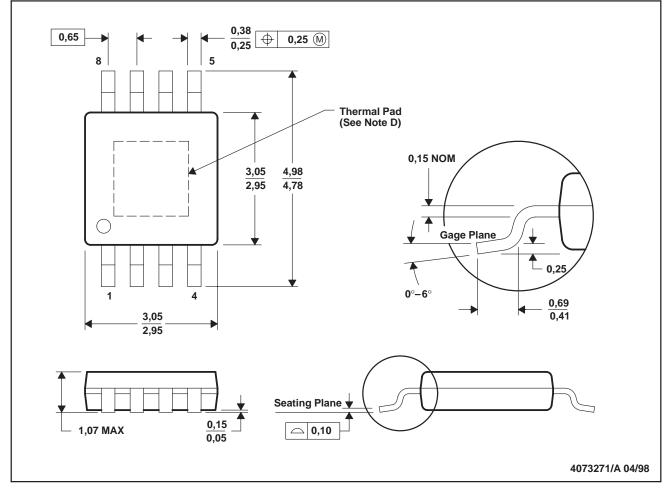

#### DGN (S-PDSO-G8)

#### PowerPAD<sup>™</sup> PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions include mold flash or protrusions.

- D. The package thermal performance may be enhanced by attaching an external heat sink to the thermal pad. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MO-187

PowerPAD is a trademark of Texas Instruments.

#### MECHANICAL INFORMATION

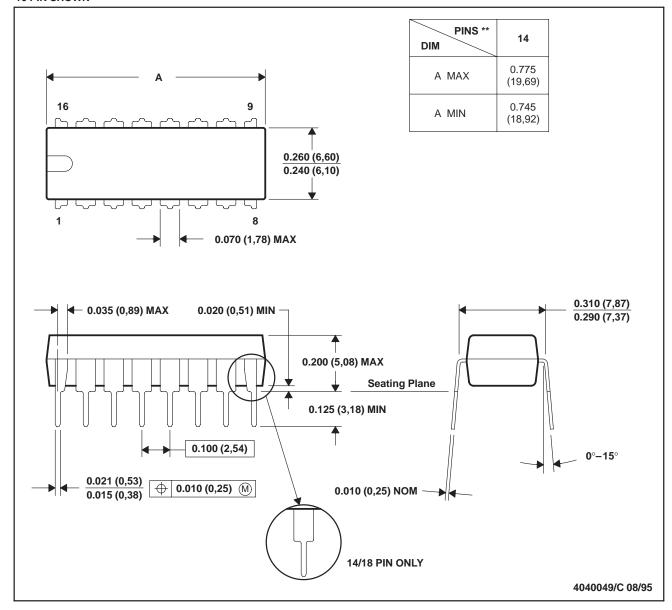

#### PLASTIC DUAL-IN-LINE PACKAGE

N (R-PDIP-T\*\*) 16 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001 (20 pin package is shorter then MS-001.)

#### MECHANICAL INFORMATION

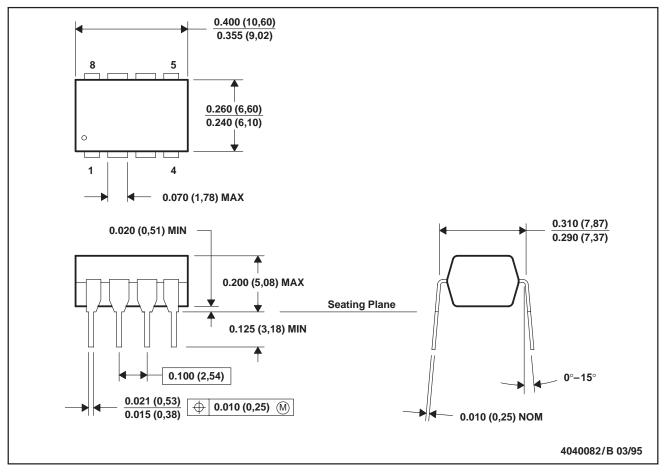

#### P (R-PDIP-T8)

#### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated