# GC4014

# **QUAD RECEIVER CHIP**

# DATASHEET

April 27, 1999

Rev 0.5

This datasheet contains information which may be changed at any time without notice.

# **REVISION HISTORY**

| Revision | Date        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0.0      | 1 Dec. 1997 | Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 0.1      | 14 Jan 1998 | Page iii, added mask revision table to list of tables<br>Pages 8, last line, added non-symmetry mode errata<br>Page 10, footnote, changed "1 milliseconds" to "10 microseconds".<br>Page 11, modified Figure 10 (c)<br>Page 12, first line Section 3.7, changed "output" to "input".<br>Page 18, address 1, bit 6, added non-symmetry errata<br>Page 19, address 4, bits 4-7, corrected bit assignments<br>Pages 20-21, corrected address numbering for blanking and flush registers<br>Page 22, address 12, bits 0,1, changed "12 LSBs" to "14 LSBs".<br>Page 24, address 16, added mask revision table.<br>Throughout, corrected table and figure reference |  |  |

| 0.2      | 21 Jan 1998 | Page 30, Changed data setup time from 4 to 2 ns.<br>Page 8, 18 Non-symmetry mode works for parts marked with all mask codes<br>except 55532B<br>Page 24, Changed Table 5 to add mask code 55532C<br>Page 28, Table 7 min and max recommended Vcc changed to 3.1 to 3.5 volts.<br>Page 28, Table 7 max junction temperature changed to 125C.                                                                                                                                                                                                                                                                                                                   |  |  |

| 0.3      | 5 Feb 1998  | Page 38, Changed 800 to 8000 in Table 17.<br>Page 38, Changed E5 to EA in note 1, Table 16.<br>Page 37, Checksum for test4 changed to D2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 0.4      | 23 Apr 1999 | Page 38, Changed CS to CE in the control interface timing description, Table 10<br>Pages 9,19, Changed GAIN equation from "NARROW*1.97" to "NARROW*0.97 + 1"<br>Page 28, Table 7, Changed max Vup voltage to 5.5v.<br>Page 39, New gain application note.<br>Pages 5, 25, Positive frequency to downconvert.<br>Pages 36, 37, changed 26 -> 2A for address 00<br>Page 29, Table 9, changed V <sub>IH</sub> for CK, CK2X to 2.4V from 2.0V.<br>Page 29, Table 9, changed I <sub>OH/L</sub> to +/- 4mA from 2.0mA<br>Page 30, $F_{CK}$ changed to 64MHz, clock to output changed to 20ns.                                                                       |  |  |

| 0.5      | 27 Apr 1999 | Pages 9,19,33,35,39, changed gain equation G/64 -> G/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 0.6      |             | Pages 6, 38 changed 55 to 56 in gain equations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

## **CONTACTING GRAYCHIP**

# **CORPORATE OFFICES:**

GRAYCHIP, Inc.

2185 Park Blvd.

Palo Alto, CA 94306

## PHONE:

(650) 323-2955

# FAX:

(650) 323-0206

#### WEB PAGE:

www.graychip.com

### E-MAIL:

sales@graychip.com

tech-support@graychip.com

| <u>1.0</u> |      | KEY FEATURES                                      | <u>1</u> |

|------------|------|---------------------------------------------------|----------|

| <u>2.0</u> |      | BLOCK DIAGRAM                                     | 1        |

| 3.0        |      | FUNCTIONAL DESCRIPTION                            | 2        |

|            | 3.1  | CONTROL INTERFACE                                 |          |

|            | 3.2  | INPUT FORMAT                                      |          |

|            | 3.3  | THE DOWN CONVERTERS                               |          |

|            | 3.4  | FINAL GAIN ADJUSTMENT                             |          |

|            | 3.5  | SUMMATION MODES                                   |          |

|            | 3.6  | OUTPUT MODES                                      |          |

|            | 3.7  | CLOCKING                                          |          |

|            | 3.8  | POWER DOWN MODES                                  |          |

|            | 3.9  | SYNCHRONIZATION                                   |          |

|            | 3.10 | DATA LATENCY                                      |          |

|            | 3.11 | DIAGNOSTICS                                       |          |

|            | 0.11 |                                                   |          |

| <u>4.0</u> |      | PACKAGING                                         |          |

| <u>5.0</u> |      | CONTROL REGISTERS                                 |          |

|            | 5.1  | SYNC MODE REGISTER                                |          |

|            | 5.2  | DECIMATION MODE REGISTER                          |          |

|            | 5.3  | CIC DECIMATION REGISTERS                          |          |

|            | 5.4  | SCALE CONTROL REGISTER                            |          |

|            | 5.5  | CHANNEL GAIN REGISTER                             | -        |

|            | 5.6  | OUTPUT FORMAT REGISTER                            |          |

|            | 5.7  | OUTPUT MODE REGISTER                              |          |

|            | 5.8  | BLANKING CONTROL REGISTER                         |          |

|            | 5.9  | CHANNEL FLUSH CONTROL REGISTER                    |          |

|            | 5.10 | COUNTER MODE REGISTERS                            |          |

|            | 5.11 | TEST MODE REGISTER                                |          |

|            | 5.12 |                                                   |          |

|            | 5.13 | STATUS CONTROL REGISTER                           |          |

|            | 5.14 |                                                   |          |

|            | 5.15 | CHANNEL OUTPUT PAGE (PAGE = 0)                    |          |

|            | 5.16 | KEEPALIVE STATUS PAGE (PAGE = 1)                  |          |

|            | 5.17 | CHANNEL CONTROL PAGES (PAGES 4, 5, 6, 7)          |          |

|            | 5.18 | COEFFICIENT STORAGE PAGES (PAGES 8, 9, 10 and 11) |          |

| <u>6.0</u> |      | SPECIFICATIONS                                    |          |

|            | 6.1  | ABSOLUTE MAXIMUM RATINGS                          |          |

|            | 6.2  | RECOMMENDED OPERATING CONDITIONS                  |          |

|            | 6.3  | THERMAL CHARACTERISTICS                           |          |

|            | 6.4  | DC CHARACTERISTICS                                |          |

|            | 6.5  | AC CHARACTERISTICS                                |          |

| <u>7.0</u> |      | APPLICATION NOTES                                 |          |

|            | 7.1  | POWER AND GROUND CONNECTIONS                      |          |

|            | 7.2  | STATIC SENSITIVE DEVICE                           |          |

|            | 7.3  | SYNCHRONIZING MULTIPLE GC4014 CHIPS               |          |

|            | 7.4  |                                                   | • •      |

|            | 7.5  | GSM APPLICATION                                   |          |

|            | 7.6  | DAMPS APPLICATION                                 | -        |

|            | 7.7  |                                                   |          |

|            | 7.8  |                                                   |          |

|            | 7.9  | OPTIMAL GAIN SETTINGS                             | 39       |

# LIST OF FIGURES

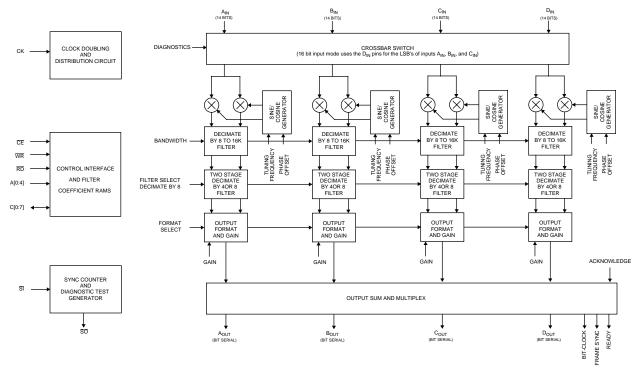

| Figure 1:  | GC4014 Block Diagram                     | 1  |

|------------|------------------------------------------|----|

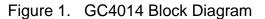

| Figure 2:  | Control I/O Timing                       | 3  |

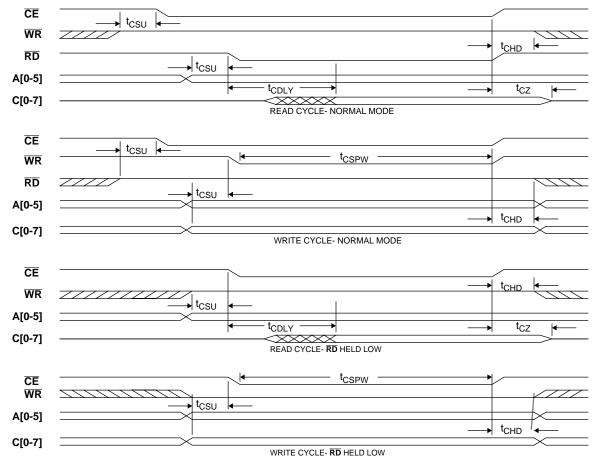

| Figure 3:  | The Down Converter Channel               | 4  |

| Figure 4:  | NCO Circuit                              | 5  |

| Figure 5:  | Example NCO Spurs                        | 5  |

| Figure 6:  | NCO Peak Spur Scan Plot                  | 6  |

| Figure 7:  | Four Stage CIC Decimate by N Filter      | 6  |

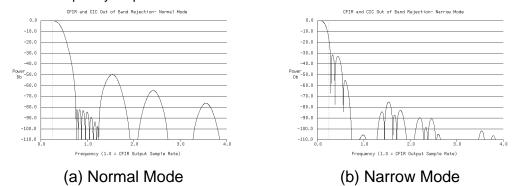

| Figure 8:  | Combined CFIR and CIC Frequency Response | 7  |

| Figure 9:  | Overall CIC-CFIR-PFIR Response           | 8  |

| Figure 10: | Serial Output Formats                    | 11 |

| Figure 11: | Overall Frequency Response for GSM       |    |

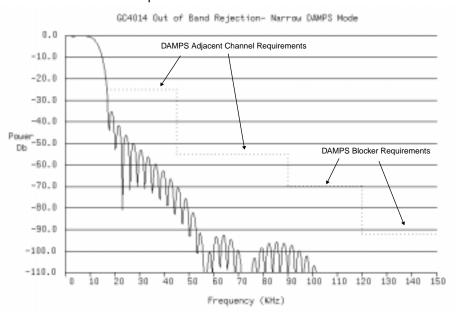

| Figure 12: | Overall Frequency Response for DAMPS     | 34 |

|            |                                          |    |

# LIST OF TABLES

| Table 1:  | Output Summation Modes                                 | 9  |

|-----------|--------------------------------------------------------|----|

| Table 2:  | TDM Modes                                              | 10 |

| Table 3:  | Latency                                                | 13 |

| Table 4:  | Sync Modes                                             | 17 |

| Table 5:  | Mask Revision History                                  | 24 |

| Table 6:  | Absolute Maximum Ratings                               |    |

| Table 7:  | Recommended Operating Conditions                       |    |

| Table 8:  | Thermal Data                                           |    |

| Table 9:  | DC Operating Conditions                                | 29 |

| Table 10: | AC Characteristics (-40 To +85C Ambient, unless noted) |    |

| Table 11: | GSM Configuration                                      |    |

| Table 12: | DAMPS Configuration                                    | 35 |

| Table 13: | Diagnostic Test 1 Configuration                        |    |

| Table 14: | Diagnostic Test 2 Configuration                        |    |

| Table 15: | Diagnostic Test 3 Configuration                        |    |

| Table 16: | Diagnostic Test 4 Configuration                        |    |

| Table 17: | Output Test Configuration                              |    |

| Table 18: | Test Output Sequence                                   |    |

# **GC4014 DATASHEET**

# 1.0 KEY FEATURES

- Input rates up to 64 MSPS

- Four real input down-convert channels or Two complex input downconvert channels

- Independent tuning frequencies

- Independent phase/gain controls

- 4 by 4 14 bit Input Crossbar switch or 3 by 4 16 bit Input Crossbar switch

- Decimation factors of 16 to 32,768 in the real output mode 32 to 65,536 in the complex output mode

- Zero padding for lower decimation factors

- Outputs can be either: bit serial, nibble serial (link port) or memory mapped

- Output summing for beamforming

- 8 to 16 bit output samples

- 0.02 Hz tuning resolution

- 0.14 dB gain resolution

- Less than 0.05 dB peak to peak passband ripple

- Greater than 100 dB far image rejection

- Greater than 95 dB spur free dynamic range

- User programmable 63 tap output filter

- Nyquist filtering for QPSK or QAM symbol data

- Meets GSM, AMPS and DAMPS Cellular specifications

- Microprocessor interface for control, output, and diagnostics

- Built in diagnostics

- Microprocessor interface will accept either 3.3 or 5 volt input levels

- 250 mW per channel at 50 MHz, 3.3 volts

- 100 pin thin QFP package

# 2.0 BLOCK DIAGRAM

A block diagram illustrating the major functions of the chip is shown in Figure 1.

GRAYCHIP, INC. - 1 - APRIL 27, 1999 This document contains information which may be changed at any time without notice

#### 3.0 FUNCTIONAL DESCRIPTION

The GC4014 quad receive chip contains four identical down-conversion circuits. Each down-convert circuit accepts a real sample rate up to 62.5 MHz, down converts a selected carrier frequency to zero, decimates the signal rate by a programmable factor ranging from 16 to 32768 (32 to 65,536 for complex outputs), and optionally sums it with other down converted samples. The chip outputs the four down-converted signals, or their sum. The chip contains a user programmable output filter which can be used to arbitrarily shape the received data's spectrum. This filter can be used as a Nyquist receive filter for digital data transmission.

Two down-converter paths can be merged to be used as a single complex input down-conversion circuit.

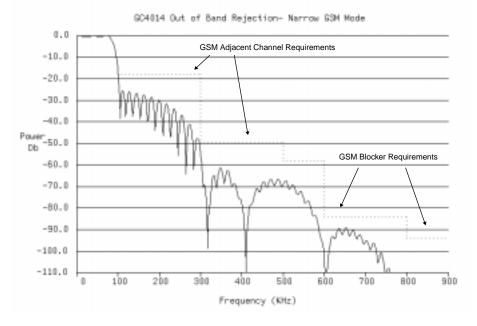

The down-converters are designed to maintain over 95 dB of spur free dynamic range and over 100 dB of out of band rejection. Each down-convert circuit accepts 16 bit inputs and produces 16 bit outputs (bit serial). The frequencies and phase offsets of the four sine/cosine sequence generators can be independently specified, as can the gain of each circuit. The down converters share the same bandwidth, filter coefficients and input formats. A special mode allows the downconverters to support GSM and DAMPS blocker requirements (see Sections 7.5 and 7.6).

On chip diagnostic circuits are provided to simplify system debug and maintenance.

The chip receives configuration and control information over a microprocessor compatible bus consisting of an 8 bit data I/O port, a 5 bit address port, a chip enable strobe, a read strobe and a write strobe. The chip's control registers (8 bits each) are memory mapped into the 5 bit address space of the control port.

Section 7.5 Describes a typical application, including control register values and the proper sequence of operations required to use the chip.

# 3.1 CONTROL INTERFACE

The chip is configured by writing control information into sixty four control registers within the chip. The contents of these control registers and how to use them are described in Section 5. The registers are written to or read from using the C[0:7], A[0:4],  $\overline{CE}$ ,  $\overline{RD}$  and  $\overline{WR}$  pins. Each control register has been assigned a unique address within the chip. This interface is designed to allow the GC4014 to appear to an external processor as a memory mapped peripheral (the pin  $\overline{RD}$  is equivalent to a memory chip's  $\overline{OE}$  pin).

An external processor (a microprocessor, computer, or DSP chip) can write into a register by setting A[0:4] to the desired register address, selecting the chip using the  $\overline{CE}$  pin, setting C[0:7] to the desired value and then pulsing  $\overline{WR}$  low. The data will be written into the selected register when both  $\overline{WR}$  and  $\overline{CE}$  are low and will be held when either signal goes high.

To read from a control register the processor must set A[0:4] to the desired address, select the chip with the  $\overline{CE}$  pin, and then set  $\overline{RD}$  low. The chip will then drive C[0:7] with the contents of the selected register. After the

processor has read the value from C[0:7] it should set  $\overline{RD}$  and  $\overline{CE}$  high. The C[0:7] pins are turned off (high impedance) whenever  $\overline{CE}$  or  $\overline{RD}$  are high or when  $\overline{WR}$  is low. The chip will only drive these pins when both  $\overline{CE}$  and  $\overline{RD}$  are low and  $\overline{WR}$  is high.

One can also ground the  $\overline{RD}$  pin and use the  $\overline{WR}$  pin as a read/write direction control and use the  $\overline{CE}$  pin as a control I/O strobe. Figure 2 shows timing diagrams illustrating both I/O modes.

Figure 2. Control I/O Timing

The setup, hold and pulse width requirements for control read or write operations are given in Section 6.0.

The C, A,  $\overline{WR}$ ,  $\overline{RD}$  and  $\overline{CE}$  pins will accept either 5 volt or 3.3 volt input levels. A separate power supply voltage pin (V<sub>UP</sub>) is provided on the chip to enable this feature.

## 3.2 INPUT FORMAT

Both 14 bit and 16 bit input formats are accepted. In the 14 bit mode the inputs are 14 bit samples from four different sources. In the 16 bit mode, the inputs are 16 bit samples from three different sources. In either case, a crossbar switch allows the user to route any input to any down-converter channel. The input samples are normally clocked into the chip at the clock rate, i.e., the input sample rate is equal to the clock rate. Input rates lower than the clock rate can be accepted by using the zero pad mode. The zero pad mode will insert up to 15 zeroes between

## GRAYCHIP, INC. - 3 - APRIL 27, 1999 This document contains information which may be changed at any time without notice

each input sample, allowing input data rates down to 1/16th the clock rate. Zero padding also lowers the effective decimation ratio. For example, the minimum decimation is normally factor of 32. If the input data rate is 5 MSPS and the chip can be clocked at 40 MHz, then the zero pad function can be used to pad the 5 MSPS input data up by a factor of 8 to 40 MSPS. The minimum decimation of 32, once the zero padding is done, becomes a minimum decimation of 4 relative to the original 5 MSPS data.

# 3.3 THE DOWN CONVERTERS

Each down converter uses an NCO and mixer to quadrature down convert a signal to baseband and then uses a 4 stage CIC<sup>1</sup> filter and a two-stage decimate by 4 or 8 filter to lowpass filter and to isolate the desired signal. A block diagram of each filter is shown below:

Figure 3. The Down Converter Channel

The CIC filter reduces the sample rate by a programmable factor ranging from 8 to 16,384. The CIC outputs are followed by a coarse gain stage and then followed by a two stage decimate by 4 or 8 filter. The coarse gain circuit allows the user to boost the gain of weak signals up to 42 dB in 6 dB steps. The first stage of the two stage filter is a compensating 21 tap decimate by 2 filter (CFIR) with a choice of two sets of fixed tap weights. The first set is designed to be flat from  $-0.5F_S$  to  $+0.5F_S$ , where  $F_S$  is the output sample rate, and to reject out of band energy by at least 80dB. The second set has a narrower output passband ( $-0.25F_S$  to  $+0.25F_S$ ), but more out of band rejection. The second set is ideal for systems such as GSM, which require more far band rejection (>97 dB), but with relaxed adjacent band rejection. The second stage is a 63 tap decimate by 2 or 4 programmable filter (PFIR) with either internal or user supplied tap weights. The internal filter is designed to be flat from  $-0.4F_S$  to  $+0.4F_S$  of the output sample rate and to reject out of band energy by at least 85 dB. The user can also design and download their own final filter to customize the channel's spectral response. Typical uses of the programmable filter include matched (root-raised cosine) filtering, or filtering to generate oversampled outputs with greater out of band rejection. The 63 tap symmetrical filter is downloaded into the chip as 32 words, 16 bits each. The programmable PFIR coefficients must be used to bandlimit the output in the decimate by 4 mode.

<sup>1.</sup> Hogenauer, Eugene B., An Economical Class of Digital Filters for Decimation and Interpolation, IEEE transactions on Acoustics, Speech and Signal Processing, April 1981.

The PFIR will also, if desired, convert the complex output data to real. The complex to real conversion also doubles the output sample rate so that the PFIR decimation is 1 or 2 in the real mode.

The PFIR filter is followed by a gain and output format circuit. The gain circuit allows the user to add an additional 18 dB of gain in 0.14 dB steps. The output format circuit can also delete every other sample without filtering. Anti-aliasing filtering must have already been performed (in the second stage filter). This is useful to achieve deeper far-band rejection since the stopband performance of the CIC filter is a function of the decimation that follows it.

# 3.3.1 The Numerically Controlled Oscillator (NCO)

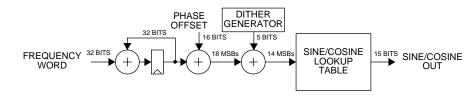

The tuning frequency of each down converter is specified as a 32 bit word and the phase offset is specified as a 16 bit word. The NCOs can be synchronized with NCOs on other chips. This allows multiple down converter outputs to be coherently combined, each with a unique phase and amplitude. A block diagram of the NCO circuit is shown in Figure 4.

Figure 4. NCO Circuit

The tuning frequency is set to FREQ according to the formula FREQ =  $2^{32}$ F/F<sub>CK</sub>, where F is the desired tuning frequency and F<sub>CK</sub> is the chip's clock rate. The 16 bit phase offset setting is PHASE =  $2^{16}$ P/2 $\pi$ , where P is the desired phase in radians ranging between 0 and  $2\pi$ . Note that a positive tuning frequency is used to downconvert the signal. A negative tuning frequency can be used to upconvert the negative image of a real signal (inverting the spectrum).

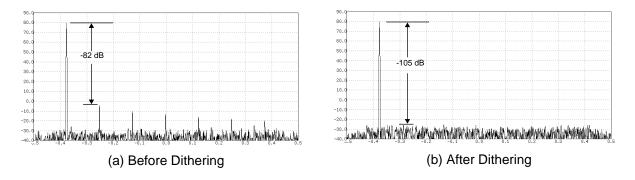

The NCO's spur level is reduced to below -92 dBc through the use of phase dithering. The spectrums in Figure 5 show the NCO spurs for an example tuning frequency before and after dithering has been turned on. Notice that the spur level decreases from -82 dB to -105 dB.

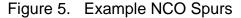

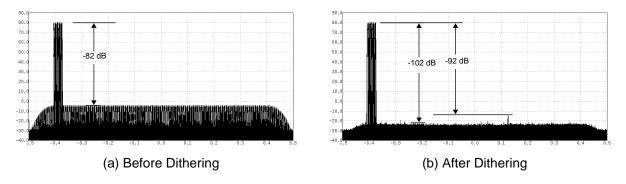

GRAYCHIP, INC. - 5 - APRIL 27, 1999 This document contains information which may be changed at any time without notice Figure 6 shows the maximum spur levels as the tuning frequency is scanned over a portion of the frequency range with the peak hold function of the spectrum analyzer turned on. Notice that the peak spur level is -82 dB before dithering and is between -92 and -102 after dithering has been turned on.

The worst case NCO spurs at -92 dB, such as the one shown in figure 6(b), are due to a few frequencies that are related to the sampling frequency by small rational numbers (for example FREQ = 3/16 \* Fck). In these cases the rounding errors in the sine/cosine lookup table repeat in a regular fashion, thereby concentrating the error power into a single frequency, rather than spreading it across the spectrum. These worst case spurs can be eliminated by selecting an initial phase that minimizes the errors or by changing the tuning frequency by a small amount (50 Hz). All spurs can be made to fall below -96 dB with the selection of a proper initial phase or tuning frequency.

## 3.3.2 Four Stage CIC Filter

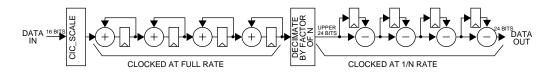

The mixer outputs are decimated by a factor of N in a four stage CIC filter, where N is any integer between 8 and 16,384. The programmable decimation allows the chip's usable output bandwidth to range from less than a kilo-Hertz to 1.5 MHz when the input rate (which is equal to the chip's clock rate) is 62.5 MHz. A block diagram of the CIC filter is shown in Figure 7.

# Figure 7. Four Stage CIC Decimate by N Filter

The CIC filter has a gain equal to N<sup>4</sup> which must be compensated for in the "CIC\_SCALE" circuit shown in Figure 7. This circuit has a gain equal to  $2^{(SCALE+6*BIG_SCALE-56)}$ , where SCALE ranges from 0 to 5 and BIG\_SCALE ranges from 0 to 7. The gain of the CIC circuit is equal to: GAIN = N<sup>4</sup>2<sup>(SCALE + 6 × BIG\_SCALE - 56)</sup>. The user must select values for SCALE and BIG\_SCALE such that GAIN is less than one, i.e., SCALE and BIG\_SCALE must be selected such that: (SCALE + 6 × BIG\_SCALE) ≤ (56 - 4log<sub>2</sub>N). Overflows due to improper gain settings will go undetected if this relationship is violated. For example, if N is equal to 8, then this restriction means that BIG\_SCALE and SCALE

## GRAYCHIP, INC.

This document contains information which may be changed at any time without notice

should be less than or equal to 7 and 2 respectively. The BIG\_SCALE and SCALE settings are common to all channels.

## 3.3.3 Coarse Channel Gain

The gain of each channel can be boosted up to 42 dB by shifting the output of the CIC filter up by 0 to 7 bits prior to rounding it to 16 bits. The coarse gain is:  $GAIN = 2^{COARSE}$ , where COARSE ranges from 0 to 7. Overflows in the coarse gain circuit are saturated to plus or minus full scale. The coarse gain is used to increase the gain of an individual signal after the input bandwidth of the downconverter has been reduced by a factor of N in the CIC filter. If the signal power across the input bandwidth is relatively flat, as is the case in most frequency division multiplexed (FDM) systems, then one would want to boost the signal power out of the CIC filter by a factor of GAIN =  $\sqrt{N}$ . Each channel can be given its own coarse gain setting. Note that the final gain stage described in Section 3.4 can boost the overall gain by up to 24 more dB.

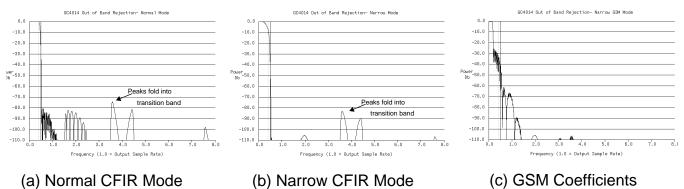

## 3.3.4 The Compensating Decimate By Two Filter (CFIR)

The CIC/Coarse gain outputs are filtered by two stages of filtering. The first stage is a 21 tap decimate by 2 filter with two sets of fixed coefficients. The first set of coefficients is used in the normal mode to give a passband which is flat (0.01 dB ripple) over 100% of the final output bandwidth and which has 85 dB of out of band rejection. The filter also compensates for the droop associated with the CIC programmable decimation filter. The filter is symmetric with the following taps:

29, -85, -308, -56, 1068, 1405, -2056, -6009, 1303, 21121, 32703

The narrow set of coefficients are intended for applications that need deeper stop bands or need oversampled outputs. These requirement are common in cellular systems where out of band rejection requirements can exceed 100 dB. The filter coefficients for the narrow mode are:

-98, -679, -2016, -3234, -2537, 850, 6053, 12060, 18230, 23239, 25212 The combined frequency response of the CIC and CFIR filter for both modes is shown below:

GRAYCHIP, INC. - 7 - APRIL 27, 1999 This document contains information which may be changed at any time without notice The dashed vertical line in the plots shows the output Nyquist rate for the chip when the PFIR is in the decimate by 2 mode. The narrow mode filter introduces a gain of 1.97 (5.9 dB).

#### 3.3.5 The Programmable Final Filter (PFIR)

The second stage decimate by two or four filter uses either internal ROM based coefficients, or externally downloaded filter coefficients. The internal 80% bandwidth filter has 80 dB of out of band image rejection and 0.03 dB peak to peak passband ripple. The internal filter is a 63 tap symmetric filter. The 32 unique coefficients are:

```

-14, -20, 19, 73, 43, -70, -82, 84, 171, -49, -269, -34, 374, 192, -449,

-430, 460, 751, -357, -1144, 81, 1581, 443, -2026, -1337, 2437, 2886,

-2770, -6127, 2987, 20544, 29647

```

Figure 9(a) shows the overall response for the internal PFIR when the CFIR is in the normal mode. Figure 9(b) shows the overall response when the CFIR is in the narrow mode. Note that the peaks in the stop band at 3.5 times the output sample rate will, after decimation, fold into the transition band from 0.4 to 0.5 of the output sample rate. This out of band power, if necessary, can be filtered out by either using a custom PFIR filter with a narrower passband, or by post-filtering.

An overall response using custom coefficients suitable to meet the stringent GSM Cellular requirements is shown in Figure 9(c). See Sections 7.5 and 7.6 for more details on GSM and DAMPS configurations.

#### Figure 9. Overall CIC-CFIR-PFIR Response

The externally downloaded coefficients can be used to tailor the spectral response to the user's needs. For example, it can be programmed as a Nyquist (typically a root-raised-cosine) filter for matched filtering digital data. The user downloaded filter coefficients are 16 bit 2's complement numbers. Unity gain will be achieved through the filter if the sum of the 63 coefficients is equal to 65536. If the sum is not 65536, then the PFIR will introduce a gain equal to (sum of coefficients)/65536.

The 63 coefficients are identified as coefficients  $h_0$  through  $h_{62}$ , where  $h_{31}$  is the center tap. The coefficients are assumed to be symmetric, so only the first 32 coefficients ( $h_0$  through  $h_{31}$ ) are loaded into the chip. A non-symmetric mode allows the user to download a 32 tap non-symmetric filter as taps  $h_0$  through  $h_{31}$ . ERRATA: The non-symmetry mode does not work properly for parts marked with mask code 55532B, Contact GRAYCHIP for details.

### 3.3.6 Real Mode

The PFIR will output either complex or real data. Complex data is output at a rate equal to  $F_{CK}/(4N)$  or  $F_{CK}/(8N)$  in the decimate by 4 mode. If the output samples are real, then the filter translates the output spectrum up by multiplying the filtered data by the complex sequence +1, -j, -1, +j, ..., and then outputting the real part at a rate equal to  $F_{CK}/2N$ . The real output mode can be used to create double sided signals out of single sideband data. The real outputs are packed into complex words for output. The first sample of a real pair is put into the I-half and the second is put into the Q-half. Note that the decimate by 4 mode is invalid in the real mode.

# 3.4 FINAL GAIN ADJUSTMENT

The final gain of each channel is adjusted by multiplying each output sample by G/32, where G is a 10bit 2's complement gain word. Since G can range between -512 and +511, the gain adjustment will range from -16.0 to +15.98. Setting G to zero clears the channel. This provides a final gain adjustment range from - $\infty$  to +24 dB in approximately 0.28 dB steps. A different gain can be specified for each channel. Note that the overall gain of the chip is also a function of the amount of decimation programmed into the chip (N), the scale circuit setting in the CIC filter, the coarse gain setting, the narrow mode in the CFIR, and the sum of the PFIR coefficients. The overall gain is shown below where the first term in braces is fixed for all four channels and must be less than or equal to unity. The terms in square brackets can be different for each channel. NARROW is "1" in the narrow CFIR mode, "0" otherwise. See Section 7.9 for a discussion on properly setting the chip's gain.

GAIN = { $N^{4}2^{(\text{SCALE} + 6 \times \text{BIG}_{\text{SCALE} - 56)}}$  [ $2^{\text{COARSE}}$ ]{1.0 + NARROW × 0.97}} { $\frac{\text{PFIR}_{\text{SUM}}}{\frac{65526}{5576}}}$  [ $\frac{G}{32}$ ]

# 3.5 SUMMATION MODES

The chip can be programmed to output the four individual channels, the sum of pairs of channels, or the sum of all four channels. These modes are used to process four real input signals, two complex input signals, or one beamformed signal. When processing two complex input signals, the I inputs are put in channels A and C, and the Q inputs are put in channels B and D. The summation mode then adds channels A and B together and channels C and D together.

Summation is disabled in Sum Mode 0. In Sum Mode 1 the channel A output is replaced by the sum of channels A and B, the channel B output is replaced by the sum of channels C and D, and the channel C and D outputs are left alone. In Sum Mode 2 the channel A output becomes the sum of all four channels and channels B, C and D are left alone. These modes are summarized in the following table:

| SUM MODE | CHANNEL OUTPUT                    |                                   |                  |                  |  |

|----------|-----------------------------------|-----------------------------------|------------------|------------------|--|

|          | OUT <sub>A</sub>                  | OUT <sub>B</sub>                  | OUT <sub>C</sub> | OUT <sub>D</sub> |  |

| 0        | CH <sub>A</sub>                   | CH <sub>B</sub>                   | CH <sub>C</sub>  | CHD              |  |

| 1        | CH <sub>A</sub> + CH <sub>B</sub> | CH <sub>C</sub> + CH <sub>D</sub> | СН <sub>С</sub>  | CH <sub>D</sub>  |  |

| 2        | $CH_A + CH_B + CH_C + CH_D$       | CH <sub>B</sub>                   | CH <sub>C</sub>  | CH <sub>D</sub>  |  |

**Table 1: Output Summation Modes**

This document contains information which may be changed at any time without notice

# 3.6 OUTPUT MODES

The channel or summation outputs are accessible either through internal control registers, through bit serial outputs, or through nibble serial (link mode) outputs. Note that the bit serial and link mode outputs start, after power up, in a tri-state condition and must be turned on when the chip is configured.

## 3.6.1 Internal Control Registers

The internal control registers are loaded by the chip once every output sample period (OSP)<sup>1</sup> and held for the rest of the period. The user is notified that new samples are ready and a new OSP has begun, either through an interrupt signal provided by the chip's "READY" pin (RDY/ACK pin), or through a control register bit.

# 3.6.2 Serial Outputs

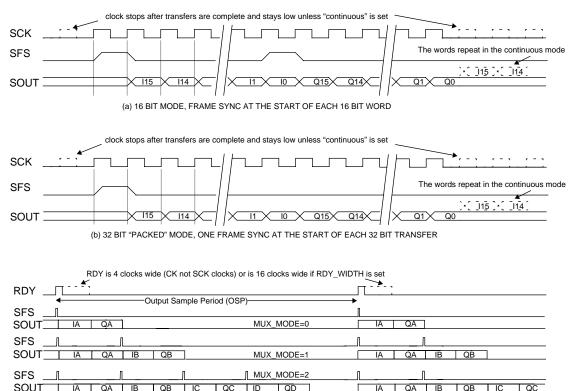

The chip provides a bit serial clock (SCK), a frame strobe (SFS) and four data bit lines (SOUT A,B,C and D) to output the data. A MUX\_MODE control specifies whether the four data outputs are transmitted on four separate bit-serial pins, or multiplexed onto two, or just one pin in a TDM format. Separate output pins are not provided for the I and Q halves of complex data. The I and Q outputs are always multiplexed onto the same bit-serial pin. The 16 bit I-component is output first, followed by the Q-component. The "packed mode" allows a complex pair to be treated as a single 32 bit word. The "READY" signal is used to identify the first word of a complex pair or of the TDM formatted output. The TDM modes are summarized in the following table (See Table 1 for a definition of OUT in the summation modes):

| MUX MODE | SERIAL OUTPUT                                                             |                  |                    |                  |  |

|----------|---------------------------------------------------------------------------|------------------|--------------------|------------------|--|

|          | A <sub>OUT</sub>                                                          | B <sub>OUT</sub> | C <sub>OUT</sub>   | D <sub>OUT</sub> |  |

| 0        | OUT <sub>A</sub>                                                          | OUT <sub>B</sub> | OUT <sub>C</sub>   | OUT <sub>D</sub> |  |

| 1        | OUT <sub>A</sub> ,                                                        | OUT <sub>B</sub> | OUT <sub>C</sub> , | OUT <sub>D</sub> |  |

| 2        | OUT <sub>A</sub> , OUT <sub>B</sub> , OUT <sub>C</sub> , OUT <sub>D</sub> |                  |                    |                  |  |

The bit serial outputs use the format shown in Figure 10. Figure 10(a) shows the standard output mode (the PACKED mode bit is low). The chip clocks the frame and data out of the chip on the rising edge of SCK (or falling edge if the SCK\_POL bit in the input control register is set). The chip sends the 16 bits (I data first) by setting SFS high (or low if SFS\_POL in the input control register is set) for one clock cycle, and then transmitting the data, MSB first, on the next 16 clocks. The I/Q data is transmitted "back to back" as shown in Figure 10(a). If the PACKED control bit is high, then the I and Q components are sent as a single 32 bit word with only one SFS strobe as shown in Figure 10(b). If two or more channels are multiplexed out the same serial pins, then the subsequent I/Q channel

<sup>1.</sup> Output sample period (OSP) refers to the interval between output samples at the decimated output rate. For example, if the input rate (and clock rate) is 10 MHz and the overall decimation factor is 100 (N=25) the OSP will be10 microseconds. An OSP starts when a new sample is ready and stops when the next one is ready.

words will be transmitted immediately following the first I/Q pair as shown in Figure 10(c). Figure 10(c) also shows how the RDY signal can be used to identify the I and Q channels in the TDM serial transmission. The bit-serial output rate is programmable as a power-of-2 division of the input clock.

(c) ONE, TWO OR FOUR CHANNEL MUX MODES (PACKED MODE IS ON)

## Figure 10. Serial Output Formats

The serial clock (SCK) will normally stop after the last bit transfer of each OSP. The user can force a continuous clock by setting the CONTINUOUS control bit in the output control register. In the continuous mode the data is repeated until the next OSP. This may be useful if the user wants to multiplex the outputs from multiple chips onto the same serial bus. Note: The frame syncs are not intended to be used in the continuous mode. After the proper number of frame syncs have been output as shown in Figure 10, the next frame sync will be missing in the continuous mode. The frame syncs will then repeat every 16 (or 32 in the packed mode) bit clocks. Note also that the number of bit clocks per output frame may not be a rational number, resulting in a truncated bit clock at the end of the OSP.

## 3.6.3 Link Mode Output

The four serial output pins and the bit clock and frame sync pins can be configured as an ADSP-2106x SHARC DSP chip link port. These pins are in a tri-state condition when the chip powers up. A control bit is set to enable these pins and another control bit is set to enable the link port mode. In the link mode the READY output pin becomes the ACK (acknowledge) input which is used to receive the link port "LACK" signal.

The link port's timing is as follows: The GC4014 checks the state of the ACK pin at the start of an OSP. If ACK is low, the chip does nothing. If ACK is high, then the chip will transmit one, two or four complex words out of the link port. The words are either the channel outputs or the sums of channels depending upon the summation mode settings. The number of outputs transmitted is determined by the MUX\_MODE settings. If MUX\_MODE is 0, only  $OUT_A$  will be transmitted. If MUX\_MODE is 1, then  $OUT_A$  and  $OUT_B$  will be transmitted. If MUX\_MODE is 2, then all four will be transmitted. See Table 1 for a definition of OUT in the summation modes.

The data is transmitted in four bit nibbles on the rising edge of the bit clock. The transmission is completed in 8, 16 or 32 clocks to transmit one, two or four complex pairs. If the ACK signal is low at the end of a word (after clocks 8, 16, 24 and 32), then the clock will remain high and the transmission of the next word will be delayed until ACK goes high again. If the ACK signal is low at the start of an OSP, then the transmission will be held off until the next OSP. The clock remains low at the end of the transmission until the next OSP starts. The bit clock rate is programmable as a division of the chip's clock.

# 3.7 CLOCKING

The chip can be clocked in one of two modes. In the standard mode, the clock rate is equal to the input data rate which can be up to 62.5 MHz. An internal clock doubler doubles the clock rate so that the internal circuitry is clocked at twice the data rate. To use the standard mode the CKMODE pin must be grounded and the internal control register bit EN\_DOUBLER must be set high (See Section 5.10).

The alternate clock mode (pin CKMODE is high) accepts a double rate clock on the CK2X pin and bypasses the clock doubler circuit. The EN\_DOUBLER control bit should be low. In the alternate mode the user must provide both the standard clock and the double rate clock.

# 3.8 POWER DOWN MODES

The chip has a power down and keep alive circuit. This circuit contains a slow, nominally 1 KHz, oscillator and a clock-loss detect cell. This circuit is used to detect the loss of clock and provide a slow keep-alive clock to the chip. The circuit is also used to power down the chip by switching from the high speed input clock to the low speed keep-alive clock. The low speed clock rate is slow enough to power down the chip while fast enough to refresh the dynamic nodes within the chip. The user can select whether this circuit is in the automatic clock-loss detect mode, is always on (power down mode), or is disabled (the slow clock never kicks in). The whole chip, or individual down converter channels can be powered down. Using the power down mode for individual channels can save significant power.

### 3.9 SYNCHRONIZATION

Each GC4014 chip can be synchronized through the use of a sync input signal, an internal one shot sync generator, or a sync counter. Each circuit within the chip, such as the sine/cosine generators or the decimation

control counter can be synchronized to one of these sources. These syncs can also be output from the chip so that multiple chips can be synchronized to the syncs coming from a designated "master" GC4014 chip.

# 3.10 DATA LATENCY

The latency through the chip, including all pipeline delays and filtering group delays, is shown in the following table (N is the CIC filter's decimation ratio, see Section 3.5,  $\overline{SI}$  is the sync input to the chip,  $\overline{SO}$  is the sync output from the chip, and the **RDY** signal marks the beginning of each output frame, See Figure 10):

| FROM INPUT      | TO OUTPUT              | LATENCY | UNITS   | COMMENT                                                                                      |

|-----------------|------------------------|---------|---------|----------------------------------------------------------------------------------------------|

| SI              | SO                     | 3       | Clocks  | sync in to sync out, Register settings:<br>OUTPUT_SYNC = 1,SO_INT_MODE =0                    |

| SI              | RDY                    | 3.5N+9  | Clocks  | Sync in to first valid RDY out                                                               |

| IN[0:13] at RDY | OUT (First)            | 5       | Outputs | Data sample input coincident with <b>RDY</b> , to the first output affected by it            |

| IN[0:13] at RDY | OUT (Midpoint)         | 22      | Outputs | -to the closest midpoint output affected by IN                                               |

| IN[0:13] at RDY | OUT (Last)             | 37      | Outputs | -to the last output affected by <b>IN</b>                                                    |

| IN[0:13] at RDY | OUT<br>(Step Response) | 86N+15  | Clocks  | Step function delay, step edge is input coincident with <b>RDY</b> , to the step edge output |

Table 3: Latency

The last entry can be used to identify the group delay through the chip for time tagging events which pass through the chip, where the time tag needs to be accurate to fractions of the output sample. Note that the overall decimation in the complex output mode is one sample every 4N inputs. This means that the step edge will come out 21 samples plus (2N+15) clocks later. A good time tag algorithm would be to count the number of clock cycles between the tagged input sample and the next **RDY** signal (the number D), and then tag the output sample that comes 21 **RDY** signals later with a time tag which is adjusted by (D - 2N-15) clocks. To insure that the adjustment is always positive, one would wait 22 **RDY** signals (22 outputs) and tag the sample with an adjustment of (D+2N-15) clocks. Note that the output sample to be tagged is the sample that is output between the 22nd **RDY** signal and the next **RDY** signal (see Figure 10).

# 3.11 DIAGNOSTICS

The chip has an internal ramp generator which can be used in place of the data inputs for diagnostics. An internal checksum circuit generates a checksum of the output data to verify the chip's operation. Section 7.7 gives suggested checksum configurations and their expected checksums.

Besides the internal diagnostics, the chip can support board level testing, an output test configuration which can help initial debug as well as production test is described in Section 7.8.

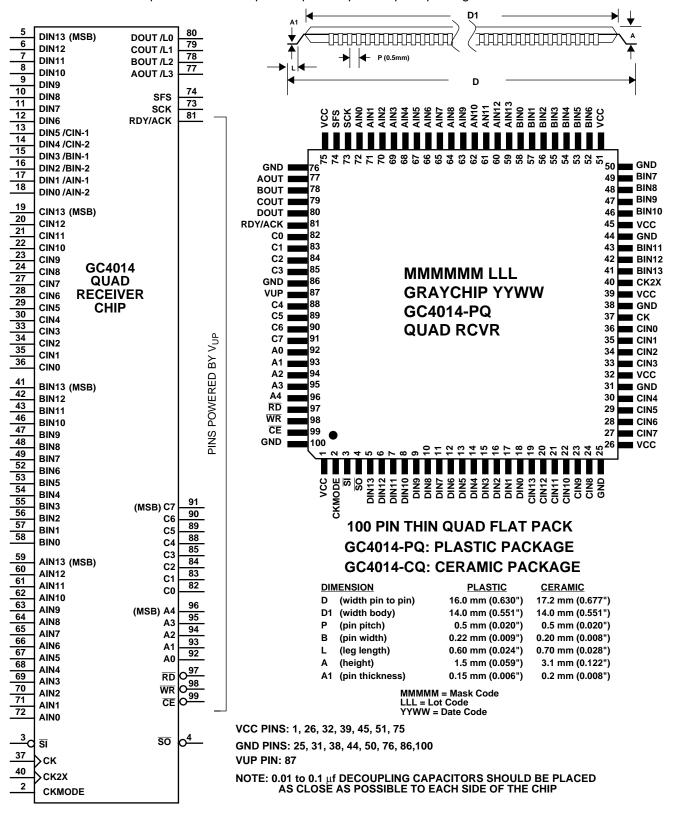

# 4.0 PACKAGING

The GC4014 chip comes in a 100 pin thin plastic quad flatpack package

GRAYCHIP, INC.

APRIL 27, 1999

This document contains information which may be changed at any time without notice

| SIGNAL              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIN, BIN, CIN, DIN  | INPUT DATA, Active high<br>The 14 bit 2's complement input data for the four channels. The data is clocked into the chip on the rising edge<br>of the clock (CK). The LSBs of DIN are used as the LSBs of AIN, BIN and CIN in the16 bit input mode (the pins<br>DIN0/AIN-2, DIN2/BIN-2 and DIN4/CIN-2 are the LSBs of the 16 bit AIN, BIN and CIN inputs).                                                                                                                                                                                                                                                                                                           |

| AOUT, BOUT, COUT, D | OUT<br>BIT SERIAL OUTPUT DATA, Active high<br>The bit serial output data are transmitted on these pins. In the serial mode these are individual outputs, in the link<br>mode these form a four bit nibble (DOUT/L0 is the LSB of the Nibble, AOUT/L3 is the MSB). The output bits are<br>clocked out on the rising edge of SCK (falling edge if SCK_POL=1). These pins are tri-stated at power up and are<br>enabled by the OUTPUT_ENABLE control register bit.                                                                                                                                                                                                      |

| SCK                 | <b>BIT SERIAL DATA CLOCK</b> , <i>Active high or low</i><br>The serial data bits are clocked out of the chip by this clock. The active edge of the clock is user programmable.<br>This pin is tri-stated at power up and is enabled by the OUTPUT_ENABLE control register bit.                                                                                                                                                                                                                                                                                                                                                                                       |

| SFS                 | <b>BIT SERIAL FRAME STROBE</b> , <i>Active high or low</i><br>The bit serial word strobe. This strobe delineates the 16 or 32 bit words within the bit serial output streams. This strobe is a pulse at the beginning of each bit serial word. The polarity of this signal is user programmable. This pin is tri-stated at power up and is enabled by the OUTPUT_ENABLE control register bit.                                                                                                                                                                                                                                                                        |

| RDY/ACK             | <b>READY OR ACKNOWLEDGE FLAG</b> , <i>programmable active high or low</i><br>The chip asserts this signal in the serial output mode to identify the beginning of an output sample period (OSP).<br>The width in input clock cycles and polarity of this signal are user programmable. This signal is typically used as<br>an interrupt to a DSP chip, but can also be used as a start pulse to dedicated circuitry. In the link mode this pin is<br>an input pin and is tied to the LACK handshake output from an ADSP-2106x SHARC DSP link port. This pin is<br>tri-stated at power up and is enabled in the serial mode by the OUTPUT_ENABLE control register bit. |

| СК                  | <b>INPUT CLOCK.</b> Active high<br>The clock input to the chip. The AIN, BIN, CIN, DIN and $\overline{SI}$ input signals are clocked into the chip on the rising edge of this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| СК2Х                | <b>DOUBLE RATE INPUT CLOCK.</b> Active high<br>The double rate clock input to the chip. Used in the alternate clock mode to clock the chip. This clock must be<br>exactly twice the frequency of the <b>CK</b> clock. Should be grounded in the normal clock mode.                                                                                                                                                                                                                                                                                                                                                                                                   |

| CKMODE              | <b>CLOCK MODE</b> , <i>Active high</i><br>The clock mode control. The chip uses <b>CK2X</b> when this pin is tied high (alternate mode) to clock the internal circuitry. When this signal is grounded (normal mode) the chip doubles the <b>CK</b> clock to use as the internal clock.                                                                                                                                                                                                                                                                                                                                                                               |

| SI                  | <b>SYNC IN</b> . Active low<br>The sync input to the chip. All timers, accumulators, and control counters are, or can be, synchronized to $\overline{SI}$ . This sync is clocked into the chip on the rising edge of the input clock ( <b>CK</b> ).                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <u>50</u>           | <b>SYNC OUT</b> . Active low<br>This signal is either a delayed version of the input sync $\overline{SI}$ , the sync counter's terminal count (TC), or a one-shot strobe. The $\overline{SO}$ signal is clocked out of the chip on the rising edge of the input clock (CK).                                                                                                                                                                                                                                                                                                                                                                                          |

| C[0:7]              | <b>CONTROL DATA I/O BUS</b> . Active high<br>This is the 8 bit control data I/O bus. Control register data is loaded into the chip or read from the chip through<br>these pins. The chip will only drive these pins when $\overline{CE}$ is low and $\overline{RD}$ is low and $\overline{WR}$ is high.                                                                                                                                                                                                                                                                                                                                                              |

| A[0:4]              | <b>CONTROL ADDRESS BUS</b> . Active high<br>These pins are used to address the control registers within the chip. Each of the control registers within the chip<br>are assigned a unique address. A control register can be written to or read from by setting <b>A[0:4]</b> to the register's<br>address.                                                                                                                                                                                                                                                                                                                                                           |

| RD                  | <b>READ ENABLE</b> . Active low<br>This pin enables the chip to output the contents of the selected register on the C[0:7] pins when $\overline{CE}$ is also low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WR                  | <b>WRITE ENABLE</b> . Active low<br>This pin enables the chip to write the value on the C[0:7] pins into the selected register when $\overline{CE}$ is also low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CE                  | <b>CHIP ENABLE</b> . Active low<br>This control strobe enables the read or write operation. The contents of the register selected by A[0:4] will be<br>output on C[0:7] when $\overline{RD}$ is low and $\overline{CE}$ is low. If $\overline{WR}$ is low and $\overline{CE}$ is low, then the selected register will be<br>loaded with the contents of C[0:7].                                                                                                                                                                                                                                                                                                      |

| Vup                 | <b>MICROPROCESSOR INTERFACE POWER SUPPLY</b> . <i>Power Supply</i><br>This pin provides power for the microprocessor interface to allow it to interface to 5 volt logic. Input pins (A[0:4], $\overline{\text{RD}}, \overline{\text{WR}}, \overline{\text{CE}}, C[0:7]$ , and $\overline{\text{RDY}}/ACK$ ) must not be driven above Vup+0.3V. The output pins (C[0:7], RDY/ACK) will drive a logic one to Vup under no load.                                                                                                                                                                                                                                        |

GRAYCHIP, INC.

# - 15 -

APRIL 27, 1999

This document contains information which may be changed at any time without notice

# 5.0 CONTROL REGISTERS

The chip is configured and controlled through the use of eight bit control registers. These registers are accessed for reading or writing using the control bus pins ( $\overline{CE}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , A[0:4], and C[0:7]) described in the previous section. The register names and their addresses are:

The Mode and Control Registers are addresses 0 to 15

| ADDRESS | NAME              | ADDRESS | NAME                  |

|---------|-------------------|---------|-----------------------|

| 0       | Sync Mode         | 8       | Blank Control         |

| 1       | Decimation Mode   | 9       | Channel Flush Control |

| 2       | Decimation Byte 0 | 10      | Counter Byte 0        |

| 3       | Decimation Byte 1 | 11      | Counter Byte 1        |

| 4       | Scale Control     | 12      | Test Mode             |

| 5       | Channel Gain      | 13      | Page Map              |

| 6       | Output Format     | 14      | Status                |

| 7       | Output Mode       | 15      | Checksum              |

Addresses 16 to 31 are used in sixteen pages as determined by the page select control bits in the page map register. The page assignments are:

| PAGE | NAME              | PAGE | NAME                  |

|------|-------------------|------|-----------------------|

| 0    | Channel Outputs   | 8    | Coefficients 0 to 7   |

| 1    | Keepalive Status  | 9    | Coefficients 8 to 15  |

| 2    | unused            | 10   | Coefficients 16 to 23 |

| 3    | unused            | 11   | Coefficients 24 to 31 |

| 4    | Channel Control A | 12   | unused                |

| 5    | Channel Control B | 13   | unused                |

| 6    | Channel Control C | 14   | unused                |

| 7    | Channel Control D | 15   | unused                |

The following sections describe each of these registers. The type of each register bit is either R, W, or R/W indicating whether the bit is read only, write only, or read/write. All bits are active high.

# 5.1 SYNC MODE REGISTER

The Sync mode control register determines how the circuits within the chip are synchronized. Each circuit which requires synchronization can be configured to be synchronized to the sync input **(SI)**, or to the terminal count of the sync counter **(TC)**. The sync to each circuit can also be set to be always on or always off. Each circuit is given a two bit sync mode control which is defined as:

| MODE | SYNC DESCRIPTION                  |

|------|-----------------------------------|

| 0    | "0" (never asserted)              |

| 1    | SI                                |

| 2    | TC (or OS, if USE_ONESHOT is set) |

| 3    | "1" (always active)               |

| Table | 4: | Sync | c Modes |

|-------|----|------|---------|

|-------|----|------|---------|

NOTE: the internal syncs are active high. The  $\overline{SI}$  input has been inverted to be the active high sync SI.

#### **ADDRESS 0:** Sync Mode, suggested default = 0x65

| <u>BIT</u> | <u>TYPE</u> | NAME         | DESCRIPTION                                                                                                                                                 |

|------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0,1 (LSBs) | R/W         | DEC_SYNC     | Synchronizes the decimation control counter. The decimation counter controls the filter timing of each channel and the serial timing of the output signals. |

| 2,3        | R/W         | COUNTER_SYNC | Synchronizes the sync counter. This counter is used to generate the periodic "TC" sync pulses. Mode 2 in Table 4 is always OS.                              |

| 4,5        | R/W         | OUTPUT_SYNC  | The selected sync is inverted and output on the $\overline{\textbf{SO}}$ pin.                                                                               |

| 6          | R/W         | USE_ONESHOT  | The terminal count mode in table 4 is replaced by the one shot pulse (OS) when this bit is set.                                                             |

| 7          | R/W         | ONE_SHOT     | The one shot sync pulse (OS) is generated when this bit is set. This<br>bit must be cleared before another one shot pulse can be generated.                 |

If the user wishes to allow the chip to free run, asynchronous to other chips, then the sync settings can be set to zero. If one wishes to synchronize several chips to a single sync source, then the sync mode selections should be set to one. The suggested default is to output the one-shot (USE\_ONESHOT = 1, OUTPUT\_SYNC=2) and set all other syncs to SI. The user should tie the  $\overline{SO}$  output pin of one GC4014 chip to the  $\overline{SI}$  input pin of all other GC4014 chips in a system in order to cleanly synchronize and initialize one or more GC4014 chips. If there is only a single GC4014 chip, then all sync mode selections can be set to "2" to receive the one-shot directly. A one-shot should be sent after initialization and each time the decimation ratio is changed.

# 5.2 DECIMATION MODE REGISTER

Registers 1 and 2 control the decimation modes for the chip. These settings are common to all channels

| ). |

|----|

| )  |

| <u>BIT</u> | <u>TYPE</u> | NAME          | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|------------|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 LSB      | R/W         | REAL          | Enables the PFIR's real output mode. (See Section 3.3.6). The real outputs are formatted into complex pairs in the real mode. The I-output words contain are the even-time real outputs and the Q-outputs contain the odd-time real outputs.                                                               |

| 1          | R/W         | FILTER_SELECT | The user downloaded filter coefficients are used instead of the built in filter coefficients for the second stage FIR filter when this bit is set.                                                                                                                                                         |

| 2          | R/W         | RDY_POL       | This control bit inverts the polarity of the <b>RDY</b> output. Normally <b>RDY</b> pulses high when a new sample is ready and an output sample period (OSP) is starting. <b>RDY</b> will pulse low when RDY_POL is high.                                                                                  |

| 3          | R/W         | RDY_WIDTH     | Normally the <b>RDY</b> pin will pulse active for four clock cycles. This control bit forces <b>RDY</b> to be active for 16 clocks.                                                                                                                                                                        |

| 4          | R/W         | LINK_MODE     | Output the data in the nibble-serial link mode. The RDY/ACK pin becomes an input pin in this mode. NOTE: To use the link mode this bit must be set before the OUTPUT_ENABLE control bit in register 8 is set, otherwise the RDY/ACK pin will be driven as an output, possibly damaging the pin.            |

| 5          | R/W         | SO_INT_MODE   | The $\overline{SO}$ output pin is used as an overflow interrupt pin when this bit is set. If an overflow due to gain settings occurs in any of the channels the $\overline{SO}$ pin will go low if this bit is set.                                                                                        |

| 6          | R/W         | NO_SYMMETRY   | The second stage decimate by two filter is normally a 63 tap symmetric filter. It becomes a 32 tap non-symmetric filter when this bit is set. ERRATA: The non-symmetry mode does not work properly for parts marked with mask code 55532B, parts with other mask codes work. Contact GRAYCHIP for details. |

| 7 MSB      | R/W         | EN_DOUBLER    | This bit must be set to enable the clock doubler circuit when the <b>CKMODE</b> pin is low. This bit is ignored when <b>CKMODE</b> pin is tied high.                                                                                                                                                       |

# 5.3 CIC DECIMATION REGISTERS

Registers 2, and 3 contain the 14 bit CIC decimation ratio control.

| ADDRESS 2  | Decimation   | n Byte 0, suggested a | lefault = 0x07                       |

|------------|--------------|-----------------------|--------------------------------------|

| <u>BIT</u> | TYPE         | NAME                  | DESCRIPTION                          |

| 0-7        | R/W          | <b>DEC</b> [0:7]      | The LSBs of the decimation control   |

| ADDRESS 3  | : Decimation | n Byte 1, suggested a | lefault = 0x00                       |

| <u>BIT</u> | TYPE         | NAME                  | DESCRIPTION                          |

| 0-5        | R/W          | <b>DEC</b> [8:13]     | The 6 MSBs of the decimation control |

| 6,7        | R            | zero                  | These bits are read only zeros.      |

Where **DEC** is equal to **N**-1. The chip decimates the input data by a factor of 2N for real output data and 4N for complex output data (or 8N if DEC\_BY\_4 is set in Register 13), where **N** ranges from 8 to 16384. This provides an decimation range from 32 to 65,536 for complex output signals and 16 to 32,768 for real output signals.

.....

## 5.4 SCALE CONTROL REGISTER

Register 4 controls the CIC filter gain for the chip. These settings are common to all channels

. . . . . . . . . .

| ADDRESS 4: |             | <b>CIC Scale</b> , suggested default = 0x71 |                               |  |

|------------|-------------|---------------------------------------------|-------------------------------|--|

| <u>BIT</u> | <u>TYPE</u> | NAME                                        | DESCRIPTION                   |  |

| 0-2        | R/W         | SCALE                                       | SCALE ranges from 0 to 5.     |  |

| 3          | R/W         | unused                                      |                               |  |

| 4-6        | R/W         | BIG_SCALE                                   | BIG_SCALE ranges from 0 to 7. |  |

| 7          | R/W         | unused                                      |                               |  |

|            |             |                                             |                               |  |

The CIC filter has a gain which is equal to N<sup>4</sup>. To remove this gain the CIC inputs are pre-scaled down by (56-SCALE-6\*BIG\_SCALE) bits before filtering. The overall gain of each channel is equal to:

$GAIN = \{N^{4}2^{(SCALE + 6 \times BIG\_SCALE - 56)}\}[2^{COARSE}]\{1.0 + NARROW \times 0.97\}\{\frac{PFIR\_SUM}{65536}\}[\frac{G}{32}]$

where COARSE and G are unique for each channel (See Section 5.17). PFIR\_SUM is the sum of the 63 PFIR coefficients if FILTER\_SELECT in Register 1 is set, and NARROW is the CFIR narrow mode bit in Register 13. The values of SCALE and BIG\_SCALE must be such that the term in braces is less than unity, i.e.,  $(SCALE + 6 \times BIG\_SCALE) \le (56 - 4\log_2 N)$ . Overflows due to improper gain settings will go undetected if this relationship is violated. For example, this restriction means that BIG\_SCALE and SCALE should be less than or equal to 7 and 2 respectively for N equal to 8. The BIG\_SCALE and SCALE settings are common to all channels. See Section 7.9 for a discussion on how to optimally set the gain of the chip.

# 5.5 CHANNEL GAIN REGISTER

Register 5 contains the most significant 2 bits of each channel's gain setting G. The least significant bits are stored in each channel's control page (See Section 5.17).

#### **ADDRESS 5:** Channel Gain, suggested default = 0x00

| <u>BIT</u> | <u>TYPE</u> | NAME    | DESCRIPTION                 |

|------------|-------------|---------|-----------------------------|

| 0,1        | R/W         | GA[8:9] | 2 MSBs of Channel A's gain. |

| 3,4        | R/W         | GB[8:9] | 2 MSBs of Channel B's gain. |

| 4,5        | R/W         | GC[8:9] | 2 MSBs of Channel C's gain. |

| 6,7        | R/W         | GD[8:9] | 2 MSBs of Channel D's gain. |

Since the gain is G/32, and these bits are only used if G is greater than 256 (except for negative values), then setting this register to zero still allows the user to add up to 18 dB of gain by just using the 8 LSB's set in the channel control pages. If more than 18 dB is desired, then these control register bits can be used. See Section 7.9 for a discussion on how to optimally set the gain of the chip.

# 5.6 OUTPUT FORMAT REGISTER

This register controls the output bit serial format.

| ADDRESS 6: | Output Format Register, | suggested default = 0x01 |

|------------|-------------------------|--------------------------|

|------------|-------------------------|--------------------------|

| <u>BIT</u> | <u>TYPE</u> | NAME       | DESCRIPTION                                                                                                                                                                                                                             |

|------------|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3 LSB    | R/W         | RATE[0:3]  | The bit serial rate is set at F <sub>CK</sub> 2 <sup>-RATE</sup> , where RATE can range from 0 to 10. If RATE=0, the SCK pin will not toggle and the serial rate is equal to the clock rate.                                            |

| 4          | R/W         | PACKED     | Puts the serial outputs into 32 bit transfer mode where each complex pair is packed into 32 bit words. The complex pair is formatted as I word in the upper byte and the Q word in the lower byte. Each word is formatted as MSB first. |

| 5          | R/W         | CONTINUOUS | The serial clock normally stops when the last bit of each transmission is complete and<br>stays low until the next OSP.                                                                                                                 |

| 6          | R/W         | SCK_POL    | This bit inverts the polarity of the serial clock. Normally SOUT and SFS change on the rising edge of <b>SCK</b> . They change on the trailing edge when this bit is set.                                                               |

| 7 MSB      | R/W         | SFS_POL    | The <b>SFS</b> signal is treated as active low when this bit is set. Otherwise the signal is treated as active high.                                                                                                                    |

# 5.7 OUTPUT MODE REGISTER

This register controls the output summation, multiplexing and rounding.

| ADDRESS 7: | Output Mode Register, | suggested default = 0x00 |

|------------|-----------------------|--------------------------|

|------------|-----------------------|--------------------------|

| <u>BIT</u> | <u>TYPE</u> | NAME     | DESCRIPTION                                                                               |

|------------|-------------|----------|-------------------------------------------------------------------------------------------|

| 0,1 LSB    | R/W         | SUM_MODE | The channel outputs are replaced by the sum of outputs as shown in Table 1 of Section 3.5 |

| 2,3        | R/W         | MUX_MODE | The outputs are multiplexed as described in Section 3.6.2.                                |

| 4          | R/W         | RND8     | Round into the 8 MSBs of the 16 bit output words.                                         |

| 5          | R/W         | RND10    | Round into the 10 MSBs of the 16 bit output words.                                        |

| 6          | R/W         | RND12    | Round into the 12 MSBs of the 16 bit output words.                                        |

| 7 MSB      | R/W         | RND14    | Round into the 14 MSBs of the 16 bit output words.                                        |

Only one round control bit can be set. If none are set the output is 16 bits. Bits below the rounding point are set to zero.

# 5.8 BLANKING CONTROL REGISTER

This register controls the blanking mode.

#### **ADDRESS 8:** Blank Control Register, suggested default = 0x50, power up reset to 0.

| <u>BIT</u> | TYPE | NAME          | DESCRIPTION                                                                                                                               |

|------------|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3 LSB    | R/W  | BLANK_RATE    | The number of zeroes to insert between each sample in the blanking mode. Ranges from 0 to 15.                                             |

| 4,5        | R/W  | BLANK_SYNC    | The sync selection from Table 4 for synchronizing the zero stuffing.                                                                      |

| 6          | R/W  | OUTPUT_ENABLE | Turns on the serial output pins including <b>SFS</b> and <b>SCK</b> . <b>RDY</b> is also turned on if LINK_MODE is off (See Section 5.2). |

| 7 MSB      | R/W  | RAM_TEST      | Used for factory tests. Should be kept low.                                                                                               |

Blanking is turned on for each channel using the channel mode register in each channel's control page.

# GRAYCHIP, INC.

APRIL 27, 1999

This document contains information which may be changed at any time without notice

# 5.9 CHANNEL FLUSH CONTROL REGISTER

This register controls flushing the four channels. Each channel is flushed when the selected sync occurs The sync is selected according to Table 4 in Section 5.1.

| ADDRESS 9: | Channel Flush Register, | suggested default = 0x55 |

|------------|-------------------------|--------------------------|

|------------|-------------------------|--------------------------|