# *CC1010*

# Single Chip Very Low Power RF Transceiver with 8051-Compatible Microcontroller

## Applications

- Very low power UHF wireless data transmitters and receivers

- 315 / 433 / 868 and 915 MHz ISM/SRD band systems

- Home automation and security

- AMR Automatic Meter Reading

## **Product Description**

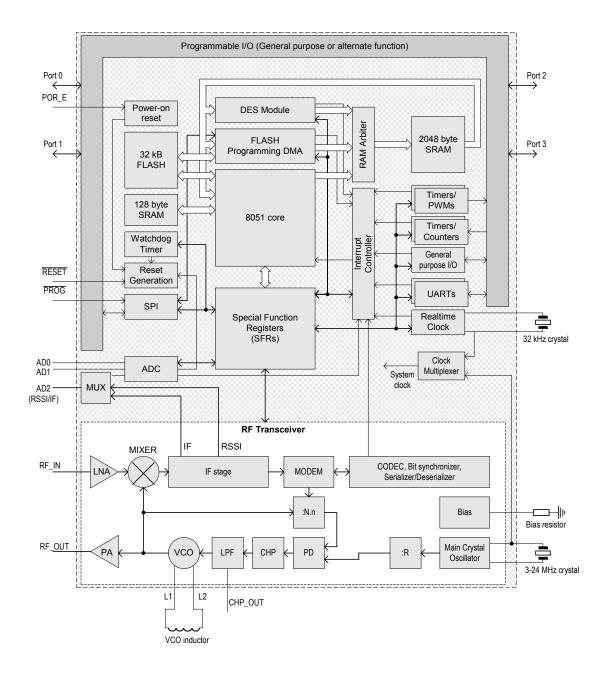

The **CC1010** is a true single-chip UHF transceiver with an integrated high performance 8051 microcontroller with 32 kB of Flash program memory. The RF transceiver can be programmed for operation in the 300 – 1000 MHz range, and is designed for very low power wireless applications.

The **CC1010** together with a few external passive components constitutes a powerful embedded system with wireless communication capabilities.

*CC1010* is based on Chipcon's SmartRF<sup>®</sup>02 technology in 0.35  $\mu$ m CMOS.

## **Key Features**

- 300-1000 MHz RF Transceiver

- Very low current consumption (9.1 mA in RX)

- High sensitivity (typically -107 dBm)

- Programmable output power up to +10 dBm

- Data rate up to 76.8 kbps

- Very few external components

- Fast PLL settling allowing frequency hopping protocols

- RSSI

- EN 300 220 and FCC CFR47 part 15 compliant

- RKE Remote Keyless Entry with acknowledgement

- Low power telemetry

- Toys

- 8051-Compatible Microcontroller

- Typically 2.5 times the performance of a standard 8051

- 32 kB Flash, 2048 + 128 Byte SRAM

- 3 channel 10 bit ADC, 4 timers / 2 PWMs, 2 UARTs, RTC, Watchdog, SPI, DES encryption, 26 general I/O pins

- In-circuit interactive debugging is supported for the Keil μVision2 IDE through a simple serial interface.

- 2.7 3.6 V supply voltage

- 64-lead TQFP

## **Table Of Contents**

| 1. FE | ATURES                                | 4  |

|-------|---------------------------------------|----|

| 2. AE | BSOLUTE MAXIMUM RATINGS               | 5  |

| 3. RE | ECOMMENDED OPERATING CONDITIONS       | 5  |

|       | CHARACTERISTICS                       |    |

| 5. EL | ECTRICAL SPECIFICATIONS               | 7  |

| 6. AI | DC                                    | 8  |

| 7. RF | SECTION, GENERAL                      | 8  |

|       | TRANSMIT SECTION                      |    |

|       | RECEIVE SECTION                       |    |

|       | SECTION                               |    |

|       | REQUENCY SYNTHESIZER SECTION          |    |

|       | N CONFIGURATION                       |    |

|       | N CONFIGURATION                       |    |

|       |                                       |    |

|       | OCK DIAGRAM                           |    |

|       | 51 CORE                               |    |

| 15.1  | GENERAL DESCRIPTION                   |    |

| 15.2  | Reset                                 |    |

| 15.3  | MEMORY MAP                            |    |

| 15.4  | CPU REGISTERS                         | 23 |

| 15.5  | INSTRUCTION SET SUMMARY               | 24 |

| 15.6  | INTERRUPTS                            | 28 |

| 15.7  | EXTERNAL INTERRUPTS                   | 32 |

| 15.8  | MAIN CRYSTAL OSCILLATOR               | 32 |

| 15.9  | POWER AND CLOCK MODES                 |    |

| 15.10 | FLASH PROGRAM MEMORY                  |    |

| 15.11 | SPI FLASH PROGRAMMING                 |    |

| 15.12 | Serial Programming Algorithm          |    |

| 15.12 | 8051 FLASH PROGRAMMING                |    |

| 15.13 | FLASH POWER CONTROL                   |    |

| 15.14 |                                       |    |

|       |                                       |    |

| 15.16 | CHIP VERSION / REVISION               |    |

|       | 51 PERIPHERALS                        |    |

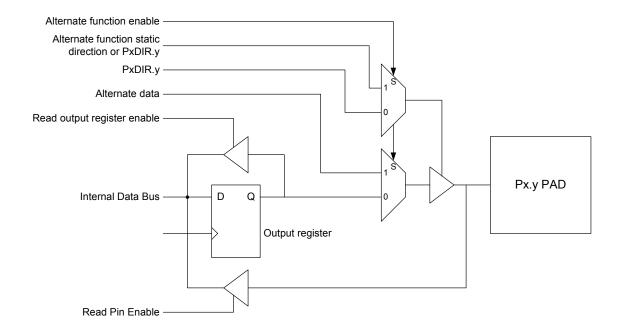

| 16.1  | General Purpose I/O                   |    |

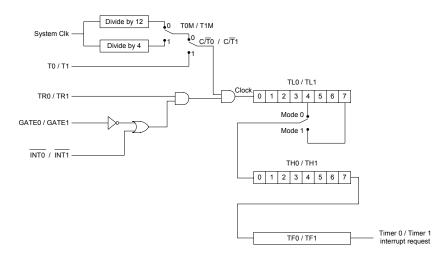

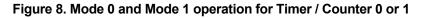

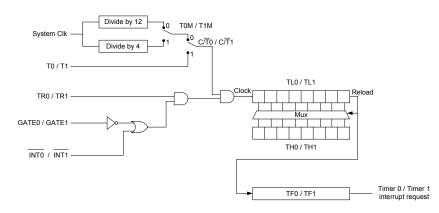

| 16.2  | TIMER 0 / TIMER 1                     |    |

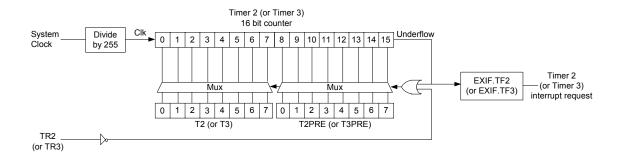

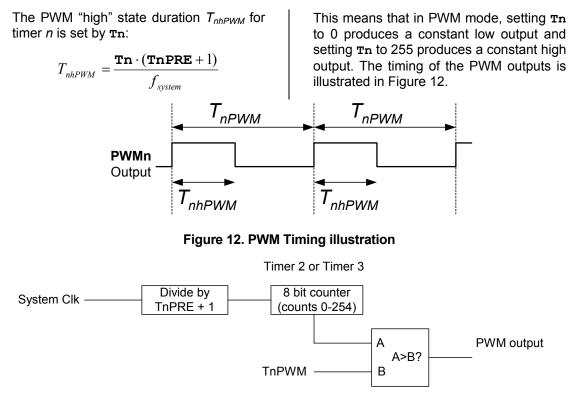

| 16.3  | TIMER 2 / 3 WITH PWM                  |    |

| 16.4  | Power On Reset (Brown-Out Detection)  |    |

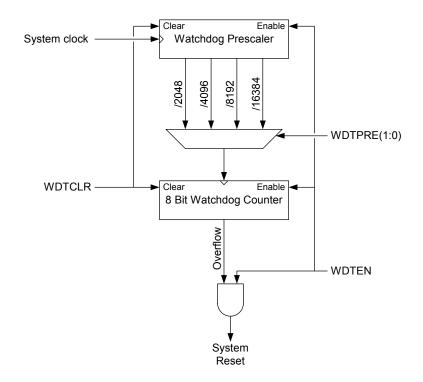

| 16.5  | WATCHDOG TIMER                        | 63 |

| 16.6  | REAL-TIME CLOCK                       | 65 |

| 16.7  | Serial Port 0 and 1                   | 66 |

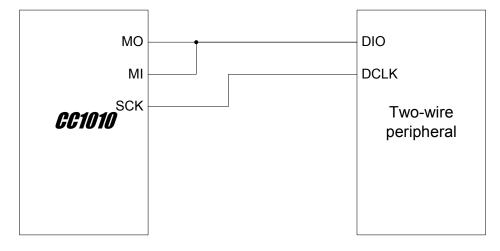

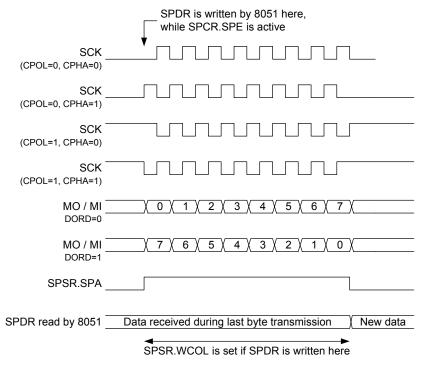

| 16.8  | SPI MASTER                            | 71 |

| 16.9  | DES ENCRYPTION / DECRYPTION           | 75 |

| 16.10 | RANDOM BIT GENERATION                 | 78 |

| 16.11 | ADC                                   |    |

|       | TRANSCEIVER                           | -  |

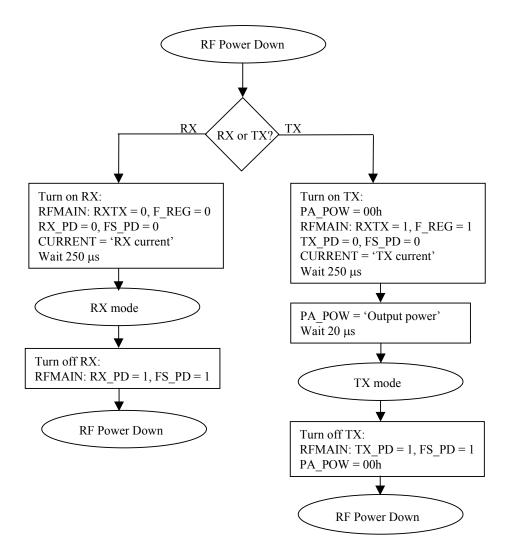

| 17.1  | GENERAL DESCRIPTION                   |    |

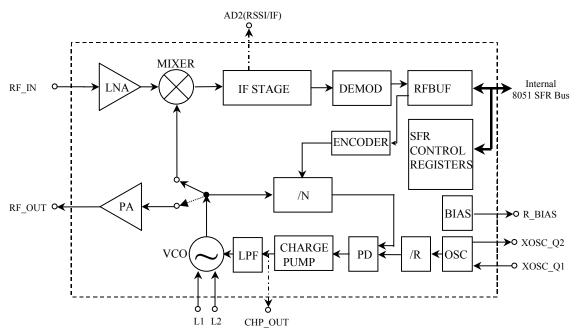

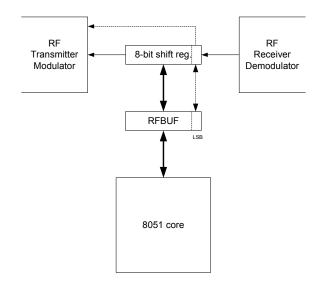

| 17.2  | RF TRANSCEIVER BLOCK DIAGRAM          |    |

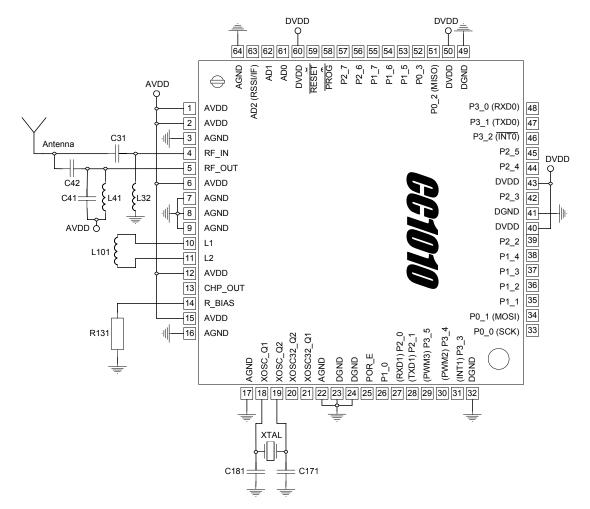

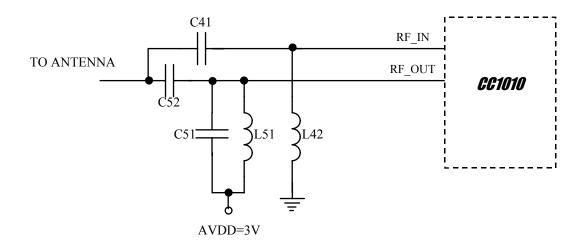

| 17.2  | RF APPLICATION CIRCUIT                |    |

| 17.3  | TRANSCEIVER CONFIGURATION OVERVIEW    |    |

| 17.4  | RF TRANSCEIVER CONFIGURATION OVERVIEW |    |

|       |                                       |    |

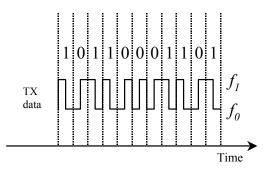

| 17.6  | DATA MODEM AND DATA MODES             |    |

| 17.7  |                                       |    |

| 17.8  | TRANSMITTING AND RECEIVING DATA       | 95 |

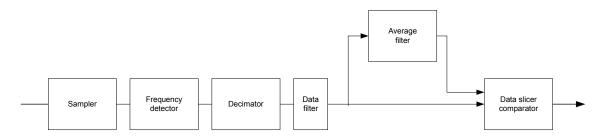

| 17.9 | DEMODULATION AND DATA DECISION                                   | . 97 |

|------|------------------------------------------------------------------|------|

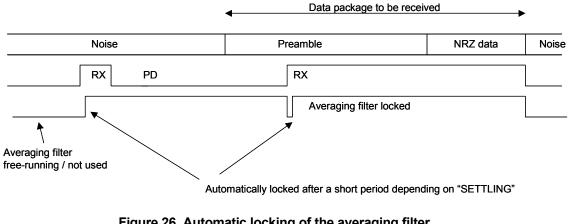

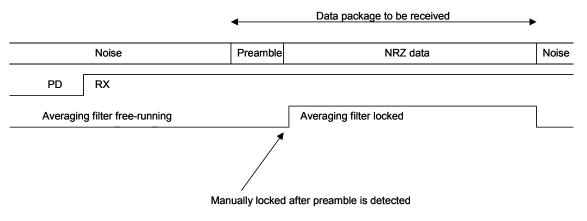

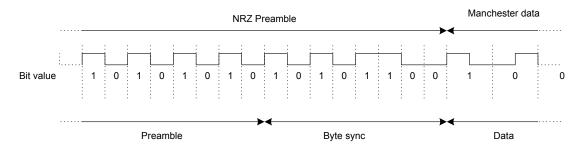

| 17.1 | 0 SYNCHRONIZATION AND PREAMBLE DETECTION                         | 102  |

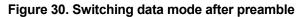

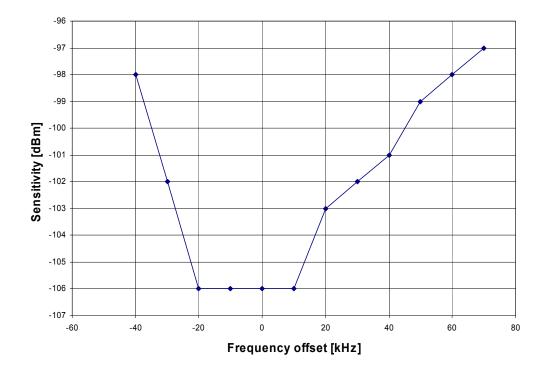

| 17.1 | 1 RECEIVER SENSITIVITY VERSUS DATA RATE AND FREQUENCY SEPARATION | 105  |

| 17.1 | 2 FREQUENCY PROGRAMMING                                          | 107  |

| 17.1 | 3 LOCK INDICATION                                                | 110  |

| 17.1 |                                                                  |      |

| 17.1 |                                                                  |      |

| 17.1 |                                                                  |      |

| 17.1 |                                                                  |      |

| 17.1 |                                                                  |      |

| 17.1 |                                                                  |      |

| 17.2 |                                                                  |      |

| 17.2 |                                                                  |      |

| 17.2 |                                                                  |      |

| 18.  | RESERVED REGISTERS AND TEST REGISTERS                            |      |

| 19.  | SYSTEM CONSIDERATIONS AND GUIDELINES                             |      |

| 19.1 |                                                                  |      |

| 19.1 |                                                                  |      |

| 19.2 |                                                                  |      |

| 19.3 |                                                                  |      |

| 19.4 |                                                                  |      |

| 19.0 |                                                                  |      |

| 19.0 |                                                                  |      |

| 19.7 |                                                                  |      |

|      |                                                                  |      |

| 19.9 |                                                                  |      |

| 19.1 |                                                                  |      |

| 19.1 |                                                                  |      |

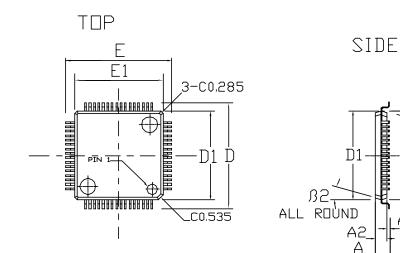

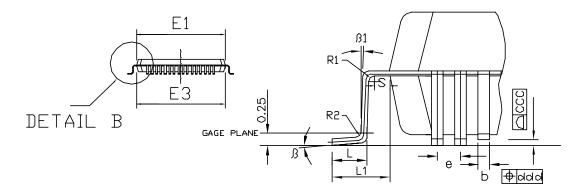

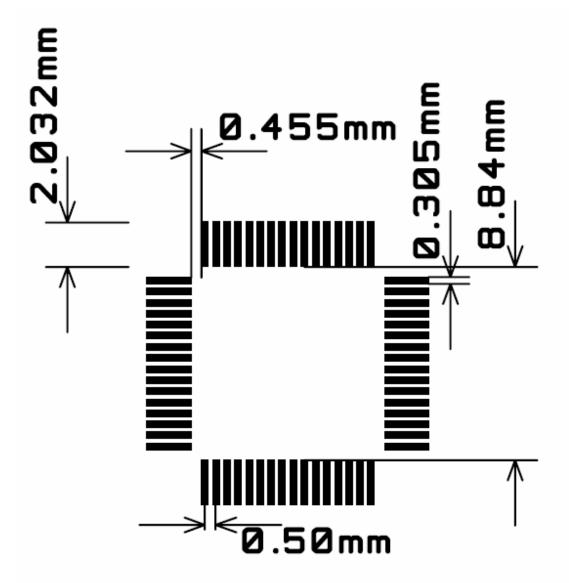

| 20.  | PACKAGE DESCRIPTION (TQFP-64)                                    |      |

| 21.  |                                                                  |      |

| 22.  |                                                                  |      |

| 22.1 |                                                                  |      |

| 22.2 |                                                                  |      |

| 23.  |                                                                  | 138  |

| 24.  | PACKAGE THERMAL COEFFICIENTS                                     |      |

| 25.  | TRAY SPECIFICATION                                               | 139  |

| 26.  | CARRIER TAPE AND REEL SPECIFICATION                              |      |

| 27.  | LIST OF ABBREVIATIONS                                            | -    |

| 28.  | SFR SUMMARY                                                      |      |

| 29.  | ALPHABETIC REGISTER INDEX                                        |      |

| 30.  | ORDERING INFORMATION                                             |      |

| 31.  | GENERAL INFORMATION                                              | -    |

| 31.1 |                                                                  | -    |

| 31.2 |                                                                  |      |

| 31.3 |                                                                  |      |

| 31.4 |                                                                  |      |

| 31.5 |                                                                  | 150  |

| 32.  | ADDRESS INFORMATION                                              | 152  |

## 1. Features

## Fully Integrated UHF RF Transceiver

- Programmable frequency in the range 300 1000 MHz

- High sensitivity (typically -107 dBm at 2.4 kBaud)

- Programmable output power –20 to +10 dBm

- Very low current consumption (RX: 9.1 mA)

- Very few external components required and no external RF switch or IF filter required

- Single port antenna connection

- Fast PLL settling allows frequency hopping protocols

- FSK modulation with a data rate of up to 76.8 kBaud

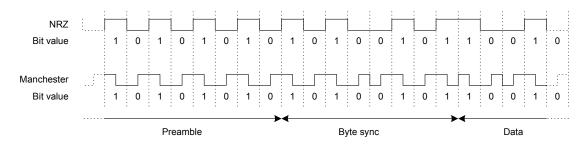

- Manchester or NRZ coding and decoding of data performed in hardware. Byte delineation of data can be performed in hardware to lessen the processor burden

- RSSI output which can be sampled by on-chip ADC

- Complies with EN 300 220 and FCC CFR47 part 15

# High-Performance and Low-Power 8051-Compatible Microcontroller

- Optimised 8051-core which typically gives 2.5x the performance of a standard 8051

- Dual data pointers

- Idle and sleep modes

- In-circuit interactive debugging is supported for the Keil μVision IDE through a simple serial interface

## Data and Non-volatile Program Memory

- 32 kB of non-volatile Flash memory in-system programmable through a simple SPI interface or by the 8051 core.

- Typical Flash memory endurance: 20 000 write/erase cycles

- Programmable read and write lock of portions of Flash memory for software security

- 2048 + 128 Byte of internal SRAM

## Hardware DES Encryption / Decryption

- DES supported in hardware

- Output Feedback Mode or Cipher Feedback Mode DES to avoid the requirement that data length must be a multiple of eight bytes

## Peripheral Features

- Power On Reset / Brown-Out Detection

- Three channel, max 23 kSample/s, 10 bit ADC

- Programmable watchdog timer.

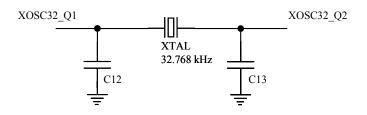

- Real time clock with 32 kHz crystal oscillator

- Two timers / pulse counters and two timers / pulse width modulators

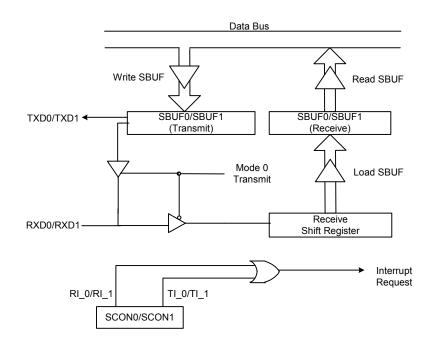

- Two programmable serial UARTs.

- Master SPI interface

- 26 configurable general-purpose I/O-pins

- Random bit generator in hardware

## Low Power

- 8051 core and peripherals can use the RTC's 32 kHz clock

- Idle and sleep modes for reduced power consumption. System can wake up on interrupt or when ADC input exceeds a set threshold

- Low-power fully static CMOS design

## Operating Conditions

- 2.7 3.6 V supply voltage

- -40 85 °C operational temperature

- 3 24 MHz crystal (up to 50 ppm) for the main crystal oscillator

## Packaging

64-lead TQFP

*CC1010*

## 2. Absolute Maximum Ratings

Under no circumstances must the absolute maximum ratings given in Table 1 be violated. Stress exceeding one or more of the limiting values may cause permanent damage to the device.

| Parameter                 | Min. | Max.                | Units | Condition                                                     |

|---------------------------|------|---------------------|-------|---------------------------------------------------------------|

| Supply voltage, VDD       | -0.3 | 5.0                 | V     |                                                               |

| Voltage on any pin        | -0.3 | VDD+0.3,<br>max 5.0 | V     |                                                               |

| Input RF level            |      | 10                  | dBm   |                                                               |

| Storage temperature range | -50  | 150                 | °C    | Un-programmed device                                          |

| Storage temperature range | -40  | 125                 | °C    | Programmed device, data<br>retention > 0.49 years at<br>125°C |

| Lead temperature          |      | 260                 | °C    | T = 10 s                                                      |

#### Table 1. Absolute Maximum Ratings

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

## 3. Recommended Operating Conditions

Tc = -40 to  $85^{\circ}$ C, VDD = 2.7 to 3.6 V if nothing else stated

| Parameter                       | Min | Тур   | Max | Unit | Condition                                    |

|---------------------------------|-----|-------|-----|------|----------------------------------------------|

| Supply voltage, DVDD, AVDD      | 2.7 | 3.3   | 3.6 | V    | Supply voltage during normal operation       |

| Supply voltage, DVDD, AVDD      | 2.7 |       | 3.6 | V    | Supply voltage during<br>program/erase Flash |

| Operating temperature, free-air | -40 |       | 85  | °C   | memory                                       |

| Main oscillator frequency       | 3   |       | 24  | MHz  |                                              |

| RTC oscillator frequency        |     | 32768 |     | Hz   |                                              |

Table 2. Recommended Operating Conditions

*CC1010*

## 4. DC Characteristics

The DC Characteristics of **CC1010** are listed in Table 3 below.

Tc = 25°C, VDD = 3.3 V if nothing else stated

| Digital Inputs/Outputs   | Min     | Мах     | Unit | Condition                                                                           |

|--------------------------|---------|---------|------|-------------------------------------------------------------------------------------|

| Logic "0" input voltage  | 0       | 0.3*VDD | V    |                                                                                     |

| Logic "1" input voltage  | 0.7*VDD | VDD     | V    |                                                                                     |

| Logic "0" output voltage | 0       | 0.4     | V    | Output current -2.0 mA,<br>ports P0.3-P0.0, P1.7-<br>P1.0, P2.7-P2.4, P2.2-<br>P2.0 |

| Logic "1" output voltage | 2.5     | VDD     | V    | Output current 2.0mA,<br>ports P0.3-P0.0, P1.7-<br>P1.0, P2.7-P2.4, P2.2-<br>P2.0   |

| Logic "0" output voltage | 0       | 0.4     | V    | Output current -8.0 mA, port P2.3                                                   |

| Logic "1" output voltage | 2.5     | VDD     | V    | Output current 8.0mA, port P2.3                                                     |

| Logic "0" input current  | NA      | -1      | μA   | Input signal equals GND                                                             |

| Logic "1" input current  | NA      | 1       | μA   | Input signal equals VDD                                                             |

**Table 3. DC Characteristics**

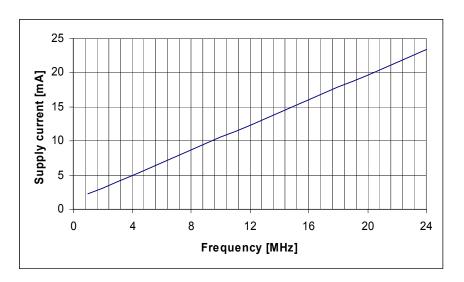

Figure 1. Typical CPU core supply current vs. clock frequency

*CC1010*

## 5. Electrical Specifications

## Tc = $25^{\circ}$ C, VDD = 3.3 V if nothing else stated

All electrical specifications are measured on Chipcon's CC1010EM reference design.

| Parameter                                                            | Min. | Тур.          | Max. | Unit     | Condition                                                                                                                                                           |

|----------------------------------------------------------------------|------|---------------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power on reset (POR) voltage                                         | 2.7  | 2.9           | 3.1  | V        | Tc = -40 to 85°C                                                                                                                                                    |

| Brown out voltage                                                    | 2.7  | 2.9           | 3.1  | V        | Tc = -40 to 85°C                                                                                                                                                    |

| RTC start-up time                                                    |      | 160           |      | ms       |                                                                                                                                                                     |

| Current consumption MCU,<br>Active mode                              |      | 14.8<br>1.3   |      | mA<br>mA | 14.7456 MHz, main oscillator<br>32 kHz, RTC oscillator<br>See page 33 for explanation<br>of modes. See Figure 1 page<br>6 for supply current vs. clock<br>frequency |

| Current consumption MCU, Idle mode                                   |      | 12.8<br>29.4  |      | mA<br>μA | 14.7456 MHz, main oscillator<br>32 kHz, RTC oscillator                                                                                                              |

| Current consumption, Power<br>Down mode                              |      | 0.2           | 1    | μA       |                                                                                                                                                                     |

| Current consumption, Power-<br>on reset circuit (when enabled)       |      | 34            |      | uA       |                                                                                                                                                                     |

| Current consumption Main<br>crystal oscillator                       |      | 67            |      | μA       | 14.7456 MHz crystal                                                                                                                                                 |

| Current consumption RF<br>Transceiver, Receive mode,<br>433/868 MHz  |      | 9.1/<br>11.9  |      | mA       | Current for RF transceiver alone                                                                                                                                    |

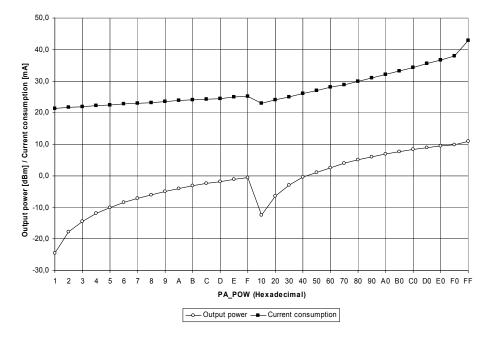

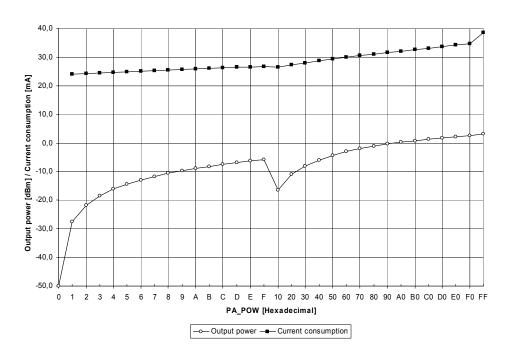

| Current consumption RF<br>Transceiver, Transmit mode,<br>433/868 MHz |      |               |      |          | The output power is delivered to a single-ended $50\Omega$ load, see also page 123. Current is                                                                      |

| P=0.01 mW (-20 dBm)                                                  |      | 5.3/8.6       |      | mA       | for RF transceiver alone                                                                                                                                            |

| P=0.3 mW (-5 dBm)                                                    |      | 8.9/13.8      |      | mA       |                                                                                                                                                                     |

| P=1 mW (0 dBm)                                                       |      | 10.4/17       |      | mA       |                                                                                                                                                                     |

| P=2.5 mW (4 dBm)                                                     |      | 24.8/<br>23.5 |      | mA       |                                                                                                                                                                     |

| P=10 mW (10 dBm)                                                     |      | 26.6/NA       |      | mA       |                                                                                                                                                                     |

| 32 kHz oscillator crystal load capacitance                           |      | 12            |      | pF       |                                                                                                                                                                     |

| Table 4. Electrical specifications | Table 4. | Electrical | specifications |

|------------------------------------|----------|------------|----------------|

|------------------------------------|----------|------------|----------------|

## 6. ADC

| Parameter                          | Min. | Тур.    | Max. | Unit       | Condition                                                                                                                                                             |

|------------------------------------|------|---------|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of bits                     |      | 10      |      | bits       |                                                                                                                                                                       |

| Differential Nonlinearity (DNL)    |      | +/-0.2  |      | LSB        | VDD is reference voltage                                                                                                                                              |

| Integral Nonlinearity (INL)        |      | +/-1.3  |      | LSB        | VDD is reference voltage                                                                                                                                              |

| Offset                             |      | 3       |      | LSB        | 7 Hz test tone                                                                                                                                                        |

| Total Harmonic Distortion<br>(THD) |      | 59      |      | dB         | 7 Hz test tone                                                                                                                                                        |

| SINAD                              |      | 54<br>9 |      | dB<br>bits | 7 Hz test tone                                                                                                                                                        |

| Internal reference tolerance       |      | ± 10    |      | %          |                                                                                                                                                                       |

| Conversion time                    | 44   |         |      | μs         | When ADC is operated at 250<br>kHz                                                                                                                                    |

| Clock frequency                    | 32   | 250     | 250  | kHz        | 250 kHz recommended for full<br>10-bit performance                                                                                                                    |

| External reference voltage         |      | 1.3     | 2.7  | V          | External reference voltage<br>should never exceed 2.7 V. It<br>is recommended to use a<br>reference voltage close to 1.3<br>V to have the best possible<br>linearity. |

| Input voltage                      | 0    |         | Vref | V          |                                                                                                                                                                       |

## Table 5. ADC characteristics

# 7. RF section, general

| Parameter          | Min. | Тур. | Max. | Unit  | Condition                                                                                      |

|--------------------|------|------|------|-------|------------------------------------------------------------------------------------------------|

| RF Frequency Range | 300  |      | 1000 | MHz   | Programmable in steps of<br>< 250 Hz                                                           |

| Data rate          | 0.6  |      | 76.8 | kBaud | NRZ or Manchester encoding.<br>76.8 kBaud equals 76.8 kbps<br>using NRZ coding. See page<br>94 |

Table 6 General RF characteristics

## 8. RF transmit section

| Parameter                                                                                       | Min. | Тур.              | Max. | Unit | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------|------|-------------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

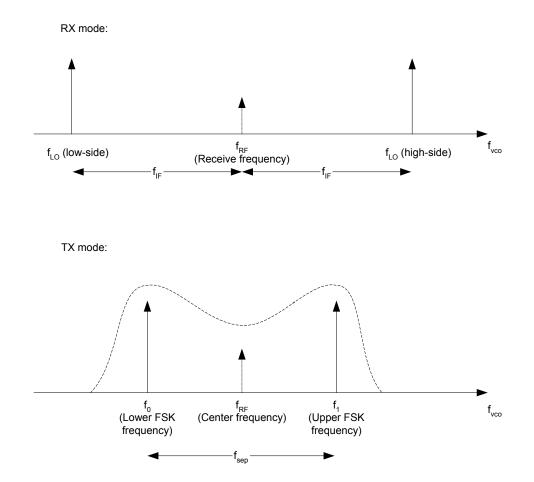

| Binary FSK frequency<br>separation                                                              | 0    | 64                | 65   | kHz  | The frequency corresponding<br>to the digital "0" is denoted $f_0$ ,<br>while $f_1$ corresponds to a<br>digital "1".<br>The frequency separation is<br>$f_1-f_0$ . The RF carrier<br>frequency, $f_c$ , is then given by<br>$f_c=(f_0+f_1)/2$ .<br>(The frequency deviation is<br>given by $f_d=+/-(f_1-f_0)/2$ )<br>The frequency separation is<br>programmable in 250 Hz<br>steps. Separations up to 65<br>kHz are guaranteed at 1 MHz<br>reference frequency. Larger<br>separations can be achieved<br>at higher reference<br>frequencies |

| Output power<br>433 / 868 MHz                                                                   | -20  | 0                 | 10/4 | dBm  | Delivered to single-ended 50 $\Omega$ load.<br>The output power is programmable, see page 123                                                                                                                                                                                                                                                                                                                                                                                                                                                |

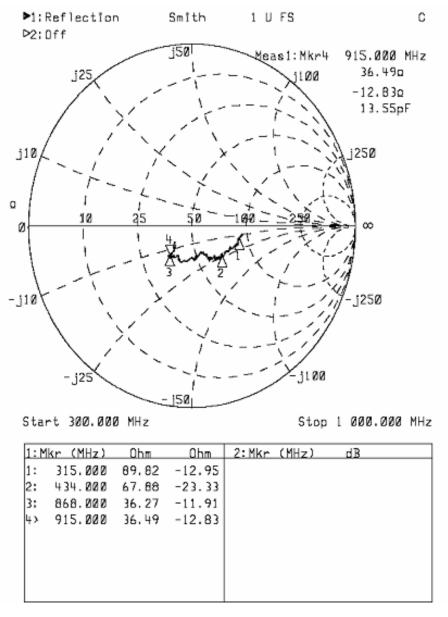

| RF output impedance<br>433 / 868 MHz                                                            |      | 140/80            |      | Ω    | Transmit mode, optimum load<br>impedance. For matching<br>details see "Input/ output<br>matching" p.120                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Harmonics<br>2 <sup>nd</sup> harmonic, 433 / 868 MHz<br>3 <sup>rd</sup> harmonic, 433 / 868 MHz |      | -7/-15<br>-27/-29 |      | dBm  | Conducted measur at<br>maximum output power. An<br>external LC filter should be<br>used to reduce harmonics<br>emission to comply with SRD<br>requirements. See p.128                                                                                                                                                                                                                                                                                                                                                                        |

Table 7. RF transmit characteristics

## 9. RF receive section

| Parameter                              | Min. | Тур.                                 | Max. | Unit             | Condition                                                                                                                                                                                      |

|----------------------------------------|------|--------------------------------------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver Sensitivity,<br>433 / 868 MHz |      | -107/<br>-106                        |      | dBm              | 2.4 kBaud, Manchester coded<br>data, 64 kHz frequency<br>separation, BER = 10 <sup>-3</sup><br>See Table 33 and Table<br>34page 105 for typical<br>sensitivity figures at other<br>data rates. |

| System noise bandwidth                 |      | 30                                   |      | kHz              | 2.4 kBaud, Manchester coded data                                                                                                                                                               |

| Cascaded noise figure<br>433/868 MHz   |      | 12/13                                |      | dB               | uala                                                                                                                                                                                           |

| Saturation (maximum input<br>level)    | 10   |                                      |      | dBm              | 2.4 kBaud, Manchester coded data, BER = $10^{-3}$                                                                                                                                              |

| Input IP3                              |      | -1<br>-26                            |      | dBm<br>dBm       | 76.8 kBaud NRZ, BER = 10 <sup>-3</sup><br>From LNA to IF output                                                                                                                                |

| Blocking                               |      | 40                                   |      | dBc              | At +/- 1 MHz                                                                                                                                                                                   |

| LO leakage                             |      |                                      | -57  | dBm              |                                                                                                                                                                                                |

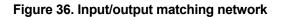

| Input impedance                        |      | 90-j13<br>68-j24<br>36-j11<br>36-j13 |      | Ω<br>Ω<br>Ω<br>Ω | Receive mode, series<br>equivalent<br>at 315 MHz<br>at 433 MHz<br>at 868 MHz<br>at 915 MHz                                                                                                     |

|                                        |      |                                      |      |                  | For matching details see<br>"Input/ output matching" p.<br>120.                                                                                                                                |

| Turn on time                           | 11   |                                      | 128  | Baud             | The demodulator settling<br>time, which is programmable,<br>determines the turn-on time.<br>See page 97 for details.                                                                           |

Table 8. RF receive characteristics

## 10. IF section

| Parameter                                  | Min. | Тур.        | Max. | Unit      | Condition                                     |

|--------------------------------------------|------|-------------|------|-----------|-----------------------------------------------|

| Intermediate frequency (IF)<br>433/868 MHz |      | 150/<br>130 |      | kHz       | Internal IF filter                            |

|                                            |      |             | 10.7 | MHz       | External IF filter                            |

| IF bandwidth (noise bandwidth)             |      | 175         |      | kHz       |                                               |

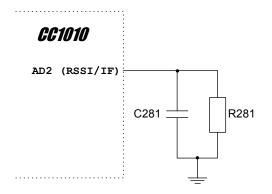

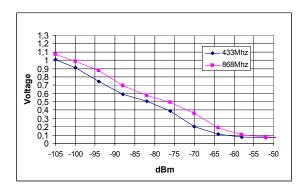

| RSSI dynamic range                         | -105 |             | -60  | dBm       |                                               |

| RSSI 3-dB bandwidth<br>RSSI accuracy       |      | 260<br>± 6  |      | kHz<br>dB | 868 MHz CW, -70 dBm<br>See p. 126 for details |

|                                            |      | ± 0         |      | uв        |                                               |

| RSSI linearity                             |      | ± 2         |      | dB        |                                               |

Table 9 IF characteristics

# **11. Frequency synthesizer section**

| Parameter                              | Min.                 | Тур.                 | Max.                 | Unit                 | Condition                                                                                                                                                                          |

|----------------------------------------|----------------------|----------------------|----------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal Oscillator Frequency           | 3                    |                      | 24                   | MHz                  | Crystal frequency can be 3-4,<br>6-8 or 9-24 MHz.<br>Recommended frequencies<br>are 3.6864, 7.3728, 11.0592,<br>14.7456, 18.4320 and<br>22.1184 MHz. See page 32<br>for details    |

| Crystal frequency accuracy requirement |                      | ± 50<br>± 25         |                      | ppm                  | 433 MHz<br>868 MHz<br>The crystal frequency<br>accuracy and drift (ageing<br>and temperature<br>dependency) will determine<br>the frequency accuracy of the<br>transmitted signal. |

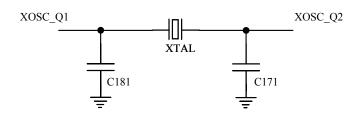

| Crystal operation                      |                      | Parallel             |                      |                      | C171 and C181 are loading capacitors                                                                                                                                               |

| Crystal load capacitance               | 12<br>12<br>12<br>12 | 20<br>16<br>16<br>12 | 30<br>30<br>16<br>16 | pF<br>pF<br>pF<br>pF | 3-4 MHz, 20 pF recommended<br>6-8 MHz, 16 pF recommended<br>9-16 MHz, 16 pF recommended<br>16-24 MHz, 12 pF recommended                                                            |

| Crystal oscillator start-up time       |                      | 5<br>1.5<br>2        |                      | ms<br>ms<br>ms       | 3.6864 MHz, 16 pF load<br>7.3728 MHz, 16 pF load<br>16 MHz, 16 pF load                                                                                                             |

| Output signal phase noise              |                      | -85                  |                      | dBc/Hz               | At 100 kHz offset from carrier                                                                                                                                                     |

| PLL lock time (RX / TX turn time)      |                      | 200                  |                      | μS                   |                                                                                                                                                                                    |

| PLL turn-on time                       |                      | 250                  |                      | μS                   |                                                                                                                                                                                    |

| Table 10. Frequency synthesizer characteristic | cs |

|------------------------------------------------|----|

|------------------------------------------------|----|

*CC1010*

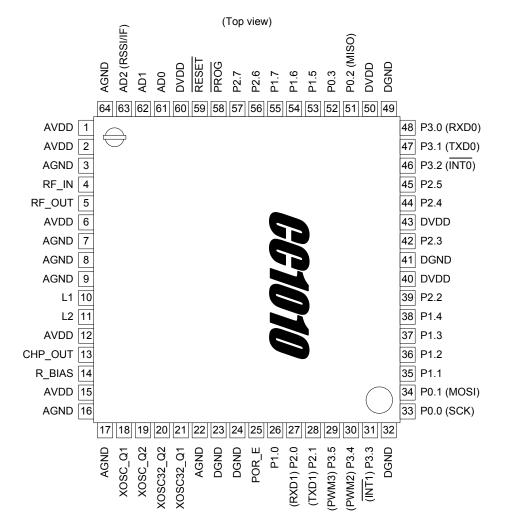

## 12. Pin Configuration

| Pin<br># | Pin name | Alternate function | Pin type  | Description                                             |

|----------|----------|--------------------|-----------|---------------------------------------------------------|

| 1        | AVDD     | -                  | Power (A) | Power supply ADC                                        |

| 2        | AVDD     | -                  | Power (A) | Power supply Mixer and IF                               |

| 3        | AGND     | -                  | Power (A) | Ground connection Mixer and IF                          |

| 4        | RF_IN    | -                  | RF input  | RF signal input from antenna (external AC-<br>coupling) |

| 5        | RF_OUT   | -                  | RF output | RF signal output to antenna                             |

| 6        | AVDD     | -                  | Power (A) | Power supply LNA and PA                                 |

| 7        | AGND     | -                  | Power (A) | Ground connection LNA and PA                            |

| 8        | AGND     | -                  | Power (A) | Ground connection PA                                    |

| 9        | AGND     | -                  | Power (A) | Ground connection VCO and prescaler                     |

| 10       | L1       | -                  | Analog    | Connection #1 for external VCO tank<br>inductor         |

| 11       | L2       | -                  | Analog    | Connection #2 for external VCO tank<br>inductor         |

| 12       | AVDD     | -                  | Power (A) | Power supply VCO and prescaler                          |

| Pin<br># | Pin name      | Alternate function | Pin type                                         | Description                                                                                                      |

|----------|---------------|--------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 13       | CHP_OUT       | -                  | Analog output                                    | Charge pump current output when external loop filter is used                                                     |

| 14       | R_BIAS        | -                  | Analog                                           | Connection for external precision bias resistor (82 k $\Omega$ , ± 1%)                                           |

| 15       | AVDD          | -                  | Power (A)                                        | Power supply misc. analog modules                                                                                |

| 16       | AGND          | -                  | Power (A)                                        | Ground connection misc. analog modules                                                                           |

| 17       | AGND          | -                  | Power (A)                                        | Analog ground connection                                                                                         |

| 18       | XOSC_Q1       | -                  | Analog input                                     | 3-24 MHz crystal, pin 1 or external clock input                                                                  |

| 19       | XOSC Q2       | -                  | Analog output                                    | 3-24 MHz crystal, pin 2                                                                                          |

| 20       | XOSC32_Q<br>2 | -                  | Analog output                                    | 32 kHz crystal pin2                                                                                              |

| 21       | XOSC32_Q<br>1 | -                  | Analog input                                     | 32 kHz crystal pin1 or external clock input                                                                      |

| 22       | AGND          | -                  | Power (A)                                        | Analog ground connection                                                                                         |

| 23       | DGND          | -                  | Power (D)                                        | Digital ground connection                                                                                        |

| 24       | DGND          | -                  | Power (D)                                        | Digital ground connection                                                                                        |

| 25       | POR_E         | -                  | Digital input                                    | Power-on reset enable.<br>0: Disable internal power-on reset module<br>1: Enable internal power-on reset module  |

| 26       | P1.0          | -                  | Digital high-Z I/O                               | 8051 port 1, bit 0                                                                                               |

| 27       | P2.0          | RXD1 (I)           | Digital high-Z I/O                               | 8051 port 2, bit 0 or RX of serial port 1                                                                        |

| 28       | P2.1          | TXD1 (Ó)           | Digital high-Z I/O                               | 8051 port 2, bit 1 or TX of serial port 1                                                                        |

| 29       | P3.5          | PWM3 (O)<br>T1 (I) | Digital high-Z I/O                               | 8051 port 3, bit 5 or pulse width modulator<br>3's output or Timer / Counter 1 external input                    |

| 30       | P3.4          | PWM2 (O)<br>T0 (I) | Digital high-Z I/O                               | 8051 port 3, bit 4 or pulse width modulator<br>2's output or Timer / Counter 0 external input                    |

| 31       | P3.3          | INT1 (I)           | Digital high-Z I/O                               | 8051 port 3, bit 3 or interrupt 1 input configurable as level or edge sensitive                                  |

| 32       | DGND          | -                  | Power (D)                                        | Ground connection digital part                                                                                   |

| 33       | P0.0          | SCK (O)<br>SCK (I) | Digital high-Z I/O                               | 8051 port 0, bit 0 or SPI master interface<br>serial clock output or Flash programming<br>SPI slave clock input. |

| 34       | P0.1          | MO (O)<br>SI (I)   | Digital high-Z I/O                               | 8051 port 0, bit 1 or SPI interface master<br>output or Flash programming SPI slave<br>serial data input         |

| 35       | P1.1          | -                  | Digital high-Z I/O                               | 8051 port 1, bit 1                                                                                               |

| 36       | P1.2          | -                  | Digital high-Z I/O                               | 8051 port 1, bit 2                                                                                               |

| 37       | P1.3          | -                  | Digital high-Z I/O                               | 8051 port 1, bit 3                                                                                               |

| 38       | P1.4          | -                  | Digital high-Z I/O                               | 8051 port 1, bit 4                                                                                               |

| 39       | P2.2          | -                  | Digital high-Z I/O<br>(Schmitt trigger<br>input) | 8051 port 2, bit 2                                                                                               |

| 40       | DVDD          | -                  | Power (D)                                        | Digital power supply                                                                                             |

| 41       | DGND          | -                  | Power (D)                                        | Ground connection digital part                                                                                   |

| 42       | P2.3          | -                  | Digital high-Z I/O (8<br>mA)                     | 8051 port 2, bit 3                                                                                               |

| 43       | DVDD          | -                  | Power (D)                                        | Digital power supply                                                                                             |

| 44       | P2.4          | -                  | Digital high-Z I/O                               | 8051 port 2, bit 4                                                                                               |

| 45       | P2.5          | -                  | Digital high-Z I/O                               | 8051 port 2, bit 5                                                                                               |

| 46       | P3.2          | INTO (I)           | Digital high-Z I/O                               | 8051 port 3, bit 2 or interrupt 0 input configurable as level or edge sensitive                                  |

| 47       | P3.1          | TXD0 (O)           | Digital high-Z I/O                               | 8051 port 3, bit 1 or TX of serial port 0                                                                        |

| 48       | P3.0          | RXD0 (I)           | Digital high-Z I/O                               | 8051 port 3, bit 0 or RX of serial port 1                                                                        |

| 49       | DGND          | -                  | Power (D)                                        | Digital ground connection                                                                                        |

| 50       | DVDD          | -                  | Power (D)                                        | Digital power supply                                                                                             |

| Pin<br># | Pin name | Alternate function  | Pin type                | Description                                                                                                         |

|----------|----------|---------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------|

| 51       | P0.2     | MI (I)<br>SO (O)    | Digital high-Z I/O      | 8051 port 0, bit 2 or SPI interface master<br>input or Flash programming SPI slave serial<br>data output            |

| 52       | P0.3     | -                   | Digital high-Z I/O      | 8051 port 0, bit 3                                                                                                  |

| 53       | P1.5     | -                   | Digital high-Z I/O      | 8051 port 1, bit 5                                                                                                  |

| 54       | P1.6     | -                   | Digital high-Z I/O      | 8051 port 1, bit 6                                                                                                  |

| 55       | P1.7     | -                   | Digital high-Z I/O      | 8051 port 1, bit 7                                                                                                  |

| 56       | P2.6     | -                   | Digital high-Z I/O      | 8051 port 2, bit 6                                                                                                  |

| 57       | P2.7     | -                   | Digital high-Z I/O      | 8051 port 2, bit 7                                                                                                  |

| 58       | PROG     | -                   | Digital input           | Flash program enable pad, active low                                                                                |

| 59       | RESET    | -                   | Digital input (pull-up) | System reset pin, active low                                                                                        |

| 60       | DVDD     | -                   | Power (D)               | Digital power supply                                                                                                |

| 61       | AD0      | -                   | Analog input            | ADC input channel 0                                                                                                 |

| 62       | AD1      | -                   | Analog input            | ADC input channel 1                                                                                                 |

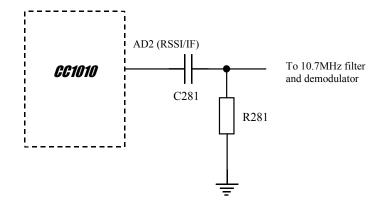

| 63       | AD2      | RSSI (O),<br>IF (O) | Analog input/output     | ADC input channel 2, RSSI (Receiver signal strength indicator) output, or IF output when using external demodulator |

| 64       | AGND     | -                   | Power (A)               | Analog ground connection ADC                                                                                        |

A = Analog, D = Digital, I = input, O= Output

## 13. Pin description

## AVDD, DVDD

Supply voltages for analog and digital modules respectively. All supply pins should be decoupled by capacitors. In particular, the digital and analog supply domains should be properly decoupled from each other (a ferrite bead can be used to prevent high-frequency noise from coupling from one supply domain to another). The placement and size of decoupling capacitors and supply filtering are critical with respect to LO leakage and sensitivity. Chipcon's reference layout designs should be used (available from Chipcon's website). See also page 133 for layout recommendations.

## AGND, DGND

Ground for analog and digital modules respectively. Normally one common ground plane is recommended. If two separate analog and digital grounds are used they should be interconnected in one place, and one place only.

#### RFIN

This is the RF input, internally connected to the low noise amplifier (LNA). The signal source (antenna) should be matched to the input impedance. A DC ground is needed for LNA biasing.

## RFOUT

This is the RF output, internally connected to the power amplifier (PA). The external load (antenna) should be matched to the output impedance (optimum load impedance). This pin must be DC coupled to AVDD for PA biasing (open drain output).

## L1, L2

Connection to internal voltage controlled oscillator (VCO). An inductor should be connected between these pins. The inductor value will determine the VCO tuning range. The inductor should be place very close to the pins in order to minimize paracitic inductance.

## CHP\_OUT

Charge Pump output. If the RF transceiver is configured for external loop filter this is the current output from the charge pump. Normally the internal loop filter should be used and this pin should be left open (not connected).

## RBIAS

Current output from internal band gap cell bias generator. A precision resistor (82 k $\Omega$ , ±1%) should be connected between this pin and ground to set the correct bias current level.

## XOSC\_Q1, XOSC\_Q2

These are the main oscillator connection pins. An external crystal should be connected between these pins, and load capacitors should be connected between each pin and ground. If an external oscillator is used, the clock signal should be connected to the XOSC\_Q1 pin, and XOSC\_Q2 should be left open (not connected).

#### XOSC32\_Q1, XOSC32\_Q2

These are the real time clock (RTC) oscillator connection pins. An external crystal should be connected between these pins, and load capacitors should be connected between each pin and ground. If an external oscillator is used, the clock signal should be connected to the XOSC32\_Q1 pin, and XOSC32\_Q2 should be left open (not connected).

## POR\_E

Enable signal for the on-chip power-on reset module. The power-on reset is enabled when **POR\_E** is connected to **DVDD** and disabled when connected to **DGND**.

## PROG

Active low Flash programming enable pin. When this signal is active (driven to DGND) a Flash programmer can be connected to the SPI interface. Under normal operation it must be driven to DVDD.

#### RESET

Active low asynchronous system reset. It has an internal pull-up resistor and can be left unconnected during normal operation.

#### AD0, AD1

Analog inputs to A/D converter channels 0 and 1 respectively. When not used these pins can be left open (not connected).

#### AD2 (RSSI/IF)

Analog input to A/D converter channel 2. This pin can also be configured to be RSSI output or IF output. The pin is configured by the **FREND** register. When not used this pin can be left open (not connected).

#### PORT 0

Port 0 is a 4-bit (P0.3-P0.0) bi-directional CMOS I/O port with 2 mA drivers. A direction register (P0DIR) controls whether each pin is an output or input and the register P0 is used to read the input or control the logical value of the output.

Pins P0.0 - P0.2 can be configured to become a master SPI interface in register SPCR and will then override P0(2:0), P0DIR(2) and P0DIR(1).

Used as SPI interface, **P0.0** is SCK, **P0.1** is MOSI, and **P0.2** is MISO.

#### PORT 1

Port 1 is an 8-bit (P1.7-P1.0) bidirectional CMOS I/O port with 2 mA drivers. A direction register (P1DIR) controls whether each pin is an output or input and the register P1 is used to read the input or control the logical value of the output.

#### PORT 2

Port 2 is an 8-bit (P2.7-P2.0) bidirectional CMOS I/O port with 2 mA drivers, except for P2.3 that has an 8 mA output buffer. A direction register (P2DIR) controls whether each pin is an output or input and the register P2 is used to read the input or control the logical value of the output.

Pins **P2.0** and **P2.1** can be configured to become the RXD1 and TXD1 pin, respectively, of UART 1.

Pin **P2.2** has a Schmitt-trigger input stage. Note that while this pin does have hysteresis, it will draw a large input current (~0.5 mA) if the input voltage is close to VDD/2.

## PORT 3

Port 3 is a 6-bit (P3.5-P3.0) bi-directional CMOS I/O port with 2 mA drivers. A direction register (P3DIR) controls whether each pin is an output or input. The register P3 is used to read the input or control the logical value of the output.

Pins **P3.0** and **P3.1** can be configured to become the RXD0 and TXD0 pin, respectively, of UART 0.

Pins P3.2 and P3.3 are connected to the

external interrupt inputs **INTO** and **INT1**, respectively, and can cause interrupts if the corresponding interrupt enable flags are set in register **IE**. The interrupts inputs

can be configured to be either levelsensitive or edge-sensitive.

Pins P3.4 and P3.5 can be configured to become the pulse width modulator (PWM) outputs of Timer/PWM 2 and Timer/PWM 3, respectively. When pulse width modulation is enabled the corresponding bits in P3DIR and P3 are overridden.

CC1N1N

## 14. Block Diagram

The *CC1010* Block Diagram is shown in Figure 2 below.

Figure 2. CC1010 Block Diagram

## 15. 8051 Core

#### 15.1 General description

The **CC1010** microcontroller core is based industry-standard on the 8051 architecture. The MCU core is 8-bit, with program and data memory located in separate memory spaces (Harvard architecture). The internal registers are organised as four banks of 8 registers each. The instruction set supports direct, indirect and register addressing modes. Program memory can be addressed using indexed addressing. The core registers are comprised of an accumulator, a stack pointer and dual data pointer registers in addition to the general registers.

Data memory is split into internal and external RAM. The name "external RAM" is in fact misleading since in the case of the **CC1010** all the RAM is internal to the chip. The difference between external and internal is that external RAM can only be accessed by a few instructions. Therefore, frequently-accessed variables as well as the stack should be kept in internal RAM.

## 15.2 Reset

**CC1010** must be reset at start-up. There are several sources for reset in **CC1010**:

- External reset pin, RESET . Applying a low signal to this pin at any time will reset almost all registers in CC1010. Exceptions can be found in Table 41 page 144. The input on is asynchronous and is synchronised internally, so that the reset can be released independent of the timing of the active clock signal. If the main crystal oscillator is inactive, the reset input should be held long enough for the oscillator to start up and stabilize. See Electrical Specifications page 7 for oscillator start-up timing.

- Power On Reset (POR). The internal POR module can generate reset upon power-up. Special requirements for power consumption or power supply voltage may require an external POR

The various peripherals are controlled through Special Function Registers (SFRs) located in the internal RAM space.

The 8051 core is instruction set compatible with the industry standard 8051. It also has one additional instruction, **TRAP**, to enable advanced in-circuitdebugging features. This is described on page 44.

The instruction cycle time is 4 clock cycles, which typically gives a 2.5X average reduction in instruction execution time over the original Intel 8051.

Peripheral units, including general purpose I/O, 2 standard 8051 timers, 2 extra timers with PWM functionality, a watchdog timer, a real-time clock, an SPI master interface, hardware DES encryption, a true random bit generator and ADC are all described from page 47 and out. Dual data pointers are available for faster data transfer.

module, as described in the Power On Reset (Brown-Out Detection) section at page 62.

- Brown-out detection reset. The POR will also detect low supply voltage and generate a reset.

- Watchdog timer reset. The watchdog timer can generate a reset, as described in the section on page 63.

- ADC reset. The ADC module can be programmed to generate a reset signal if its inputs exceed a programmed threshold. See the ADC section on page 79 for details.

The POR and ADC reset signals will be held for 1024 clock periods after the signal is released. This will ensure a safe clock start-up if the crystal oscillator is currently not running.

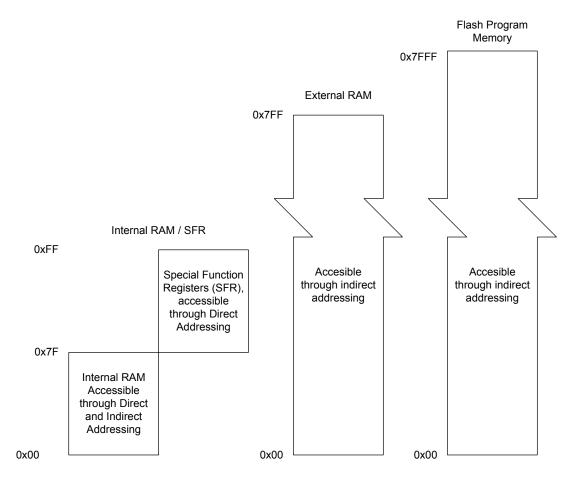

#### 15.3 Memory Map

The *CC1010* memory map is shown in Figure 3.

**CC1010** has 2 blocks of RAM on chip. This includes the 128 bytes Internal RAM and the 2048 bytes External RAM. (The 2048-byte RAM will be referred to as External RAM, although it is on-chip. Direct access to off-chip RAM is not implemented.)

Access to the internal RAM is performed using the MOV instruction. MOV A, @Ri, MOV @Ri, A and MOV @Ri, #data use indirect addressing. MOV A, direct, MOV Rn, direct, MOV direct, A, MOV direct, Rn, MOV direct, direct and MOV direct, #data use direct addressing. MOV @Ri, direct uses indirect and direct addressing.

All direct addressing instructions can also be used to access the SFRs. **CC1010** also implements the option to access SFRs indirectly, as described in the In Circuit Debugging section on page 44. **CC1010** has dual data pointers to external RAM, provided in the 16 bit registers DPTR0 and DPTR1 (SFRs DPH0, DPL0, DPH1 and DPL1). If a high-level language compilator is used, it should be set up to make use of both pointers for better performance. The data pointer is selected through DPS.SEL.

Access to the external RAM is performed using the MOVX instruction and indirect addressing using either the 16 bit data pointers or the 8 bit registers R0 or R1 together with MPAGE. MOVX A, @DPTR and MOVX @DPTR, A moves data to (from) the accumulator, from (to) the address pointed to by the currently selected data pointer.

The instructions MOVX A, @Ri and MOVX @Ri, A moves data to (from) the accumulator, from (to) the address given by the memory page address register **MPAGE** and the register Ri (R0 or R1). **MPAGE** gives the 8 most significant address bits, while the register Ri gives the 8 least significant bits. In many 8051 implementations, this type of external RAM access is performed using **P2** to give the most significant address bits. Existing software may therefore have to be adapted to make use of **MPAGE** instead of **P2**.

The program memory can be read using the MOVC A, @A+DPTR and MOVC A, @A+PC instructions, which moves a byte from the program memory address given by A+DPTR or A+PC respectively. The program memory can not be written using MOV commands, but uses the method described in the 8051 Flash Programming section on page 42.

**CC1010** also provides a possibility to stretch the access cycle to external RAM, through CKCON.MD(2:0) (see page 55). The default value for CKCON.MD is "001". It is recommended to set CKCON.MD to "000" for faster RAM access.

Figure 3. Memory Map

| DPL0 (0x82) - | <b>Data Pointer</b> | 0, low byte |

|---------------|---------------------|-------------|

|---------------|---------------------|-------------|

| Bit | Name      | R/W | Reset value | Description              |

|-----|-----------|-----|-------------|--------------------------|

| 7:0 | DPL0(7:0) | R/W | 0x00        | Data Pointer 0, low byte |

## DPH0 (0x83) - Data Pointer 0, high byte

| Bit | Name      | R/W | Reset value | Description               |

|-----|-----------|-----|-------------|---------------------------|

| 0   | DPH0(7:0) | R/W | 0x00        | Data Pointer 0, high byte |

## DPL1 (0x84) - Data Pointer 1, low byte

| Bit | Name      | R/W | Reset value | Description              |

|-----|-----------|-----|-------------|--------------------------|

| 7:0 | DPL1(7:0) | R/W | 0x00        | Data Pointer 1, low byte |

## DPH1 (0x85) - Data Pointer 1, high byte

| Bit | Name      | R/W | Reset value | Description               |

|-----|-----------|-----|-------------|---------------------------|

| 7:0 | DPH1(7:0) | R/W | 0x00        | Data Pointer 1, high byte |

| Bit | Name | R/W | Reset value | Description                                                                                             |

|-----|------|-----|-------------|---------------------------------------------------------------------------------------------------------|

| 7:1 | -    | R0  | 0x00        | Reserved, read as 0                                                                                     |

| 0   | SEL  | R/W | 0x00        | Data Pointer Select for external RAM access<br>0 : DPH0 and DPL0 are used<br>1 : DPH1 and DPL1 are used |

#### DPS (0x86) - Data Pointer Select

#### MPAGE (0x92) - Memory Page Select Register

| Bit | Name        | R/W | Reset value | Description |

|-----|-------------|-----|-------------|-------------|

| 7:0 | MPAGE (7:0) | R/W | 0x00        | Memory Page |

A total of 119 Special Function Registers (SFRs) are accessible from the microcontroller core. The names and addresses of all SFRs are listed in Table 11. All standard 8051 registers are available, in addition to SFRs which are **CC1010** specific, controlling modules such as the RF Transceiver, DES encryption, ADC and Real-Time Clock.

All SFRs will be described in the following sections. A more detailed overview is provided in Table 41 on page 144, which also includes all reset values. SFRs with addresses ending with 0 or 8 (leftmost column of Table 11) are bit adressable.

| ADC a | illu Real-I | ппе сюск. |         |         |         |         |           |          |

|-------|-------------|-----------|---------|---------|---------|---------|-----------|----------|

|       | 0/8         | 1/9       | 2/A     | 3/B     | 4/C     | 5/D     | 6/E       | 7/F      |

| 0xF8  | EIP         | TEST0     | TEST1   | TEST2   | TEST3   | TEST4   | TEST5     | TEST6    |

| 0xF0  | В           | FSHAPE7   | FSHAPE6 | FSHAPE5 | FSHAPE4 | FSHAPE3 | FSHAPE2   | FSHAPE1  |

| 0xE8  | EIE         | FSDELAY   | FSEP0   | FSEP1   | FSCTRL  | RTCON   | FREND     | TESTMUX  |

| 0xE0  | ACC         | CURRENT   | PA_POW  | PLL     | LOCK    | CAL     | PRESCALER | RESERVED |

| 0xD8  | EICON       | MODEM2    | MODEM1  | MODEM0  | MATCH   | FLTIM   | -         | -        |

| 0xD0  | PSW         | X32CON    | WDT     | PDET    | BSYNC   | -       | -         | -        |

| 0xC8  | RFMAIN      | RFBUF     | FREQ_0A | FREQ_1A | FREQ_2A | FREQ_0B | FREQ_1B   | FREQ_2B  |

| 0xC0  | SCON1       | SBUF1     | RFCON   | CRPCON  | CRPKEY  | CRPDAT  | CRPCNT    | RANCON   |

| 0xB8  | IP          | RDATA     | RADRL   | RADRH   | CRPINI4 | CRPINI5 | CRPINI6   | CRPINI7  |

| 0xB0  | P3          | -         | -       | -       | CRPINI0 | CRPINI1 | CRPINI2   | CRPINI3  |

| 0xA8  | IE          | TCON2     | T2PRE   | T3PRE   | т2      | т3      | FLADR     | FLCON    |

| 0xA0  | P2          | SPCR      | SPDR    | SPSR    | PODIR   | P1DIR   | P2DIR     | P3DIR    |

| 0x98  | SCON0       | SBUF0     | -       | -       | -       | -       | -         | CHVER    |

| 0x90  | P1          | EXIF      | MPAGE   | ADCON   | ADDATL  | ADDATH  | ADCON2    | ADTRH    |

| 0x88  | TCON        | TMOD      | TLO     | TL1     | THO     | TH1     | CKCON     | -        |

| 0x80  | PO          | SP        | DPL0    | DPH0    | DPL1    | DPH1    | DPS       | PCON     |

Table 11 **CC1010** SFR Overview

#### 15.4 CPU Registers

**CC1010** provides 4 register banks of 8 registers each. These register banks are mapped in the the internal data memory (see the Memory section on page 33) at addresses 0x00 - 0x07, 0x08 - 0x0F, 0x10 - 0x17 and 0x18 - 0x1F. Each register bank contains the 8 8-bit registers R0 through R7. The different register banks are selected through the Program Status Word **PSW.RS(1:0)** as shown below. **PSW** also contains carry, overflow and

## PSW (0xD0) - Program Status Word

parity flags that reflect the current CPU state.

In addition, the CPU uses the accumulator register A (accessed via the SFR space as ACC), B (for multiplication and division) and the stack pointer sp. These registers are shown below. Note that the hardware stack pointer sp is increased when pushing and decreased when popping data, unlike many other microcontroller architectures.

| Bit | Name | R/W | Reset value | Description                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----|------|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | CY   | R/W | 0           | Carry Flag, set to 1 when the last arithmetic operation resulted in a carry (during addition) or borrow (during subtraction), otherwise cleared to 0 by all arithmetic operations. <b>CY</b> is also used for rotation instructions.                                              |  |  |  |  |

| 6   | AC   | R/W | 0           | Auxiliary carry flag. Set to 1 when the last<br>arithmetic operation resulted in a carry into<br>(during addition) or borrow from (during<br>subtraction) the high order nibble, otherwise<br>cleared to 0 by all arithmetic operations.                                          |  |  |  |  |

| 5   | F0   | R/W | 0           | Flag 0 (Available to the user for general purpose)                                                                                                                                                                                                                                |  |  |  |  |

| 4   | RS1  | R/W | 0           | Register bank select.                                                                                                                                                                                                                                                             |  |  |  |  |

| 3   | RS0  | R/W | 0           | RS1         RS0         Working register bank and address           0         0         Bank0         0x00-0x07           0         1         Bank1         0x08-0x0F           1         0         Bank2         0x10-0x17           1         1         Bank3         0x18-0x1F |  |  |  |  |

| 2   | ov   | R/W | 0           | Overflow flag. Set to 1 when the last arithmetic<br>operation resulted in a carry (addition), borrow<br>(subtraction), or overflow (multiply or divide).<br>Otherwise, the bit cleared to 0 by all arithmetic<br>operations.                                                      |  |  |  |  |

| 1   | F1   | R/W | 0           | Flag 1 (Available to the user for general purpose)                                                                                                                                                                                                                                |  |  |  |  |

| 0   | P    | R/W | 0           | Parity flag. Set to 1 when the modulo-2 sum of the 8 bits in the accumulator is 1 (odd parity), cleared to 0 on even parity.                                                                                                                                                      |  |  |  |  |

#### ACC (0xE0) - Accumulator Register

| Bit | Name      | R/W | Reset value | Description |

|-----|-----------|-----|-------------|-------------|

| 7:0 | ACC (7:0) | R/W | 0x00        | Accumulator |

#### B (0xF0) - B Register

| Bit | Name   | R/W | Reset value | Description                               |

|-----|--------|-----|-------------|-------------------------------------------|

| 7:0 | B(7:0) | R/W | 0x00        | B is used for multiplication and division |

#### SP (0x81) - Stack Pointer

| Bit | Name    | R/W | Reset value | Description                                                                                                            |

|-----|---------|-----|-------------|------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP(7:0) | R/W | 0x07        | Stack Pointer, used for pushing and poping data to and from the stack. Note that the reset value for <b>SP</b> is 0x07 |

#### 15.5 Instruction Set Summary

The 8051 instruction set is summarised in Table 12 below. All mnemonics are Copyright © Intel Corporation 1980. One non-standard 8051 instruction, TRAP,

with opcode 0xA5 is included to enable setting of breakpoints. This instruction is described in the In Circuit Debugging section at page 44. Symbols used in the table are:

- A Accumulator

- AB Register pair A and B

- B Multiplication register

- C Carry flag

- DPTR Data pointer

- Rn Register R0 R7

- PC Program counter

- direct 8-bit data address (Internal RAM 0x00 0x7F, SFRs 0x80-0xFF)

- @Ri Internal register pointed to by R0 or R1 (except MOVX)

- rel Two's complement offset byte used by SJMP and conditional jumps

- bit Direct bit address

- #data 8-bit constant

- #data 16 16-bit constant

- addr 16 16-bit destination address

- addr 11 11-bit destination address, used by ACALL and AJMP. The branch will be within the same 2 kB block of program memory of the first byte of the following instruction.

The 'Bytes' column shows the number of bytes of Flash memory used. Further, the number of instruction cycles is shown. Each instruction cycle requires four clock cycles. The 4 rightmost columns shows which flags in the program status word **PSW** (see page 23) are affected by the instructions.

| Mnemonic       | Description                                |       |               |            |    |    |   |   |

|----------------|--------------------------------------------|-------|---------------|------------|----|----|---|---|

|                |                                            | Bytes | Instr. Cycles | Hex Opcode | сҮ | AC | ٥ | ď |

|                | Arithmetic                                 |       |               |            |    |    |   |   |

| ADD A, Rn      | Add register to A                          | 1     | 1             | 28-2F      | х  | х  | х | х |

| ADD A, direct  | Add direct byte to A                       | 2     | 2             | 25         | х  | х  | х | Х |

| ADD A, @Ri     | Add data memory to A                       | 1     | 1             | 26-27      | х  | х  | х | х |

| ADD A, #data   | Add immediate to A                         | 2     | 2             | 24         | х  | х  | х | Х |

| ADDC A, Rn     | Add register to A with carry               | 1     | 1             | 38-3F      | х  | х  | х | х |

| ADDC A, direct | Add direct byte to A with carry            | 2     | 2             | 35         | х  | х  | х | Х |

| ADDC A, @Ri    | Add data memory to A with carry            | 1     | 1             | 36-37      | х  | х  | х | х |

| ADDC A, #data  | Add immediate to A with carry              | 2     | 2             | 34         | х  | х  | х | х |

| SUBB A, Rn     | Subtract register from A with<br>borrow    | 1     | 1             | 98-9F      | х  | х  | х | x |

| SUBB A, direct | Subtract direct byte from A with<br>borrow | 2     | 2             | 95         | х  | х  | х | х |

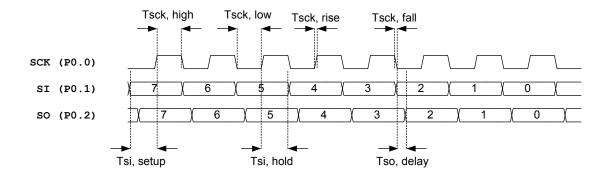

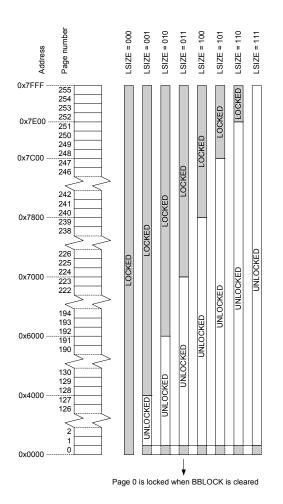

| SUBB A, @RiSubtract data memory from A with<br>borrow11196-97XXXXXSUBB A, #dataSubtract data memory from A with<br>borrow2294XXXXXSUBB A, #dataSubtract immediate from A with<br>borrow2294XXXXXXINC AIncrement Register1104-07LLLXINC RnIncrement data memory1106-07LLLXDEC ADecrement Register1118-17LLXDEC ADecrement direct byte2215LLLDEC GRIDecrement direct byte2215LLXDEC GRIDecrement direct byte1118-17LLXDEC RNDecrement direct byte15A4XXXXDIV ABDivide A by B15A4XXXXAADecimal adjust A11D4XXXXANL A, RinAND register to A2255LXXANL A, RifAND do direct byte to A2255LXXANL A, ReiAND do direct byte to A2255LXXANL A, RefiAND to direct byte to A2245L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Mnemonic      | Description                 |      |      |          |          |    |   |   |