#

# SYNCHRONOUS BURST SRAM

# 32K x 32 SRAM

**Pipeline and Flow-Through Burst Mode**

### **FEATURES**

**»VFT** pin for user configurable pipeline or flow-through operation.

»V1 Fast Access times:

- Pipeline – 3.8 / 4 / 4.5 ns

- Flow-through – 9 / 10 / 11ns

»VSingle 3.3V +0.3V/-0.165V power supply

- »VCommon data inputs and data outputs

- »VIndividual BYTE WRITE ENABLE and GLOBAL WRITE control

- **»VT**hree chip enables for depth expansion and address pipelining

- »VClock-controlled and registered address, data I/Os and control signals

- »VInternally self-timed WRITE CYCLE

- **»VBurst control pins ( interleaved or linear burst sequence)**

- **»V**High 30pF output drive capability at rated access time

$\ensuremath{\text{*VSNOOZE}}$  MODE for reduced power standby

»VBurst Sequence :

- Interleaved (MODE=NC or VCC)

- >1]z€vr.19^ `UVNX\_U:1

#### 1

#### **OPTIONS**

| MARF                            | KING          | -3.8   | -4    | -4.5  |  |  |

|---------------------------------|---------------|--------|-------|-------|--|--|

| Pipeline<br>3-1-1-1 Access 3.8n |               | 3.8ns  | 4ns   | 4.5ns |  |  |

| 5-1-1-1                         | Cycle<br>time | 6.6ns  | 7.5ns | 8.5ns |  |  |

| Flow-                           | time          | 10ns   | 11ns  |       |  |  |

| through<br>2-1-1-1              | Cycle<br>time | 10.5ns | 15ns  | 15ns  |  |  |

Q

Т

Package

100-pin QFP

#### 100-pin TQFP Part Number Examples

# PART NO. Pkg. T35L3232B-3.8Q Q T35L3232B-4T T

#### **GENERAL DESCRIPTION**

The Taiwan Memory Technology Synchronous Burst RAM family employs high-speed, low power CMOS design using advanced triple-layer polysilicon, double-layer metal technology. Each memory cell consists of four transistors and two high valued resistors.

The T35L3232B SRAM integrates 32,768 x 32 bits SRAM cells with advanced synchronous peripheral circuitry and a 2-bit counter for internal burst operation. All synchronous inputs are gated by registers controlled by a positive-edge-triggered clock input (CLK). The synchronous inputs include all addresses, all data inputs, address-pipelining chip enable ( $\overline{CE2}$  and  $\overline{CE2}$ ), depth-expansion chip enables ( $\overline{CE2}$  and  $\overline{CE2}$ ), burst control inputs ( $\overline{ADSC}$ ,  $\overline{ADSP}$ , and  $\overline{ADV}$ ), write enables ( $\overline{BW1}$ ,  $\overline{BW2}$ ,  $\overline{BW3}$ ,  $\overline{BW4}$ , and  $\overline{BWE}$ ), and global write ( $\overline{GW}$ ).

Asynchronous inputs include the output enable  $(\overline{OE})$ , Snooze enable (ZZ) and burst mode control (MODE). The data outputs (Q), enabled by  $\overline{OE}$ , are also asynchronous.

Addresses and chip enables are registered with either address status processor ( $\overline{ADSP}$ ) or address status controller ( $\overline{ADSC}$ ) input pins. Subsequent burst addresses can be internally generated as controlled by the burst advance pin ( $\overline{ADV}$ ).

Address and write controls are registered on-chip to initiate self-timed WRITE cycle. WRITE cycles can be one to four bytes wide as controlled by the write control inputs. Individual byte write

allows individual byte to be written.  $\overline{BW1}$  controls DQ1-DQ8.  $\overline{BW2}$  controls DQ9-DQ16.  $\overline{BW3}$  controls DQ17-DQ 24.  $\overline{BW4}$  controls DQ25-DQ32.  $\overline{BW1}$ ,  $\overline{BW2}$ ,  $\overline{BW3}$ , and  $\overline{BW4}$  can be active only with  $\overline{BWE}$  being LOW.  $\overline{GW}$  being LOW causes all bytes to be written. WRITE pass-through capability allows written data available at the output for the immediately next READ cycle. This device also incorporates pipelined enable circuit for easy depth expansion without penalizing system performance.

**P.**1

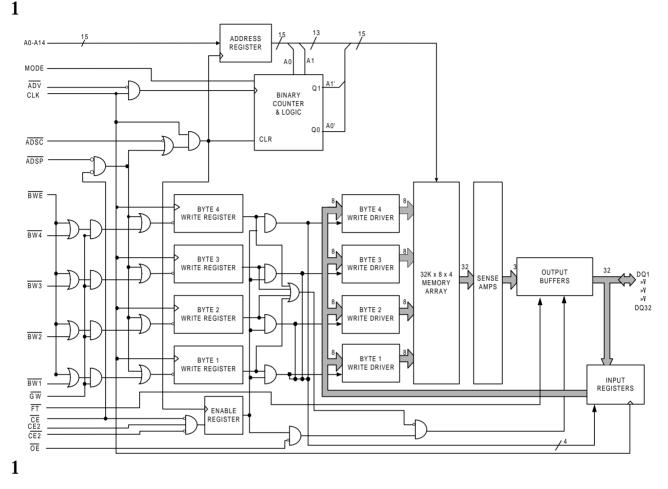

# FUNCTIONAL BLOCK DIAGRAM

Note: The Functional Block Diagram illustrates simplified device operation. See Truth Table, pin descriptions and timing diagrams for detailed information.

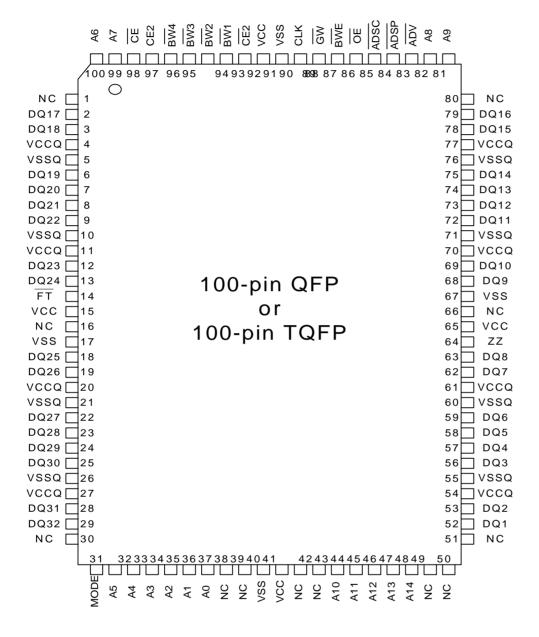

### PIN ASSIGNMENT (Top View)

# **tm***ï*#

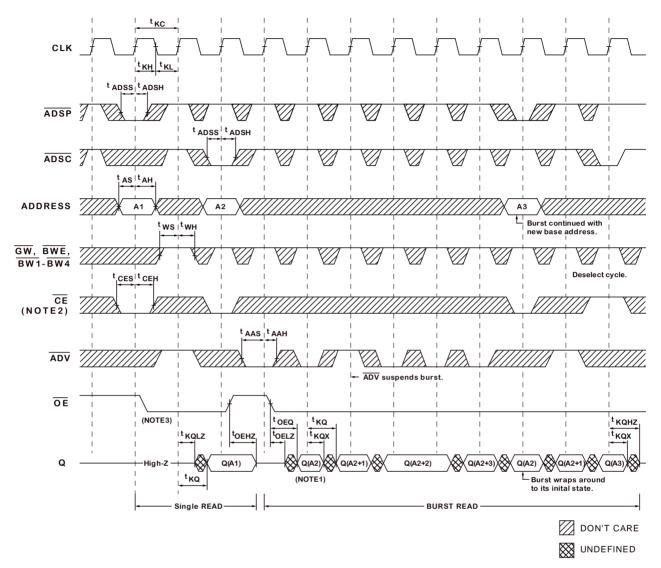

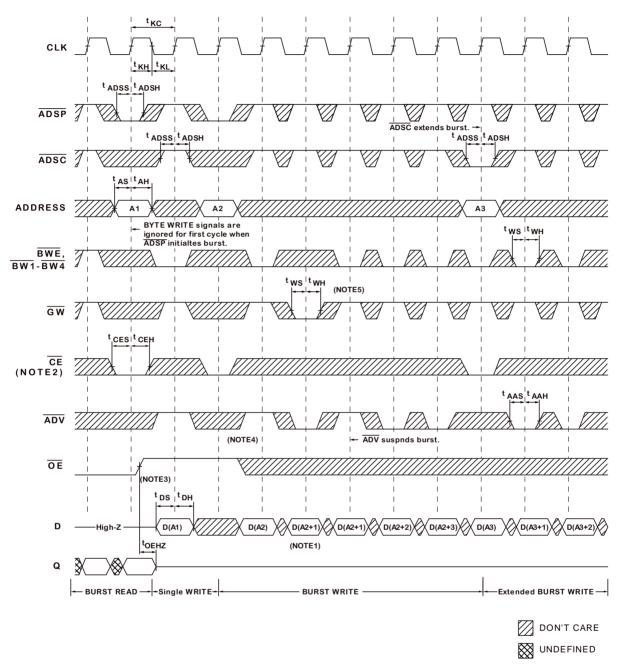

### PIPELINE READ TIMING

- **Note:** 1. Q(A2) refers to output from address A2. Q (A2 + 1) refers to output from the next internal burst address following A2.

- 2.  $\overline{CE2}$  and CE2 have timing identical to  $\overline{CE}$ . On this diagram, when  $\overline{CE}$  is LOW,  $\overline{CE2}$  is LOW and CE2 is HIGH. When  $\overline{CE}$  is HIGH,  $\overline{CE2}$  is HIGH and CE2 is LOW.

- 3. Timing is shown assuming that the device was not enabled before entering into this sequence.  $\overline{OE}$  does not cause Q to be driven until after the following clock rising edge.

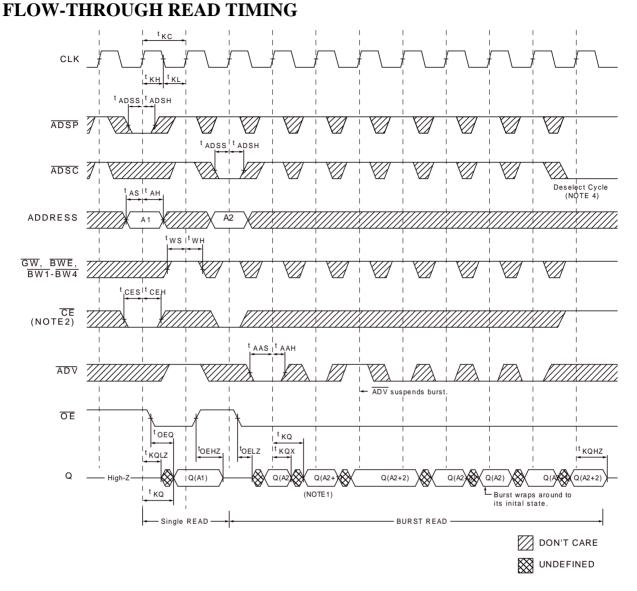

# **tm**&#

- **Note:** 1. Q(A2) refers to output from address A2. Q (A2 + 1) refers to output from the next internal burst address following A2.

- 2.  $\overline{CE2}$  and CE2 have timing identical to  $\overline{CE}$ . On this diagram, when  $\overline{CE}$  is LOW,  $\overline{CE2}$  is LOW and CE2 is HIGH. When  $\overline{CE}$  is HIGH,  $\overline{CE2}$  is HIGH and CE2 is LOW.

- 3. Timing is shown assuming that the device was not enabled before entering into this sequence.  $\overline{OE}$  does not cause Q to be driven until after the following clock rising edge.

- 4. Output are disabled <sup>t</sup>KQHZ after diselect.

# Preliminary T35L3232B

WRITE TIMING

- Note: 1. Q(A2) refers to output from address A2. Q(A2 + 1) refers to output from the next internal burst address following A2.

- 2.  $\overline{CE2}$  and CE2 have timing identical to  $\overline{CE}$ . On this diagram, when  $\overline{CE}$  is LOW,  $\overline{CE2}$  is LOW and CE2 is HIGH. When  $\overline{CE}$  is HIGH,  $\overline{CE2}$  is HIGH and CE2 is LOW.

- 3.  $\overline{OE}$  must be HIGH before the input data setup and hold HIGH throughout the data hold time. This prevents input/output data contention for the time period to the byte write enable inputs being sampled.

- 4.  $\overline{\text{ADV}}$  must be HIGH to permit a WRITE to the loaded address.

- 5. Full width WRITE can be initiated by  $\overline{GW}$  LOW or  $\overline{GW}$  HIGH and  $\overline{BWE}$ ,  $\overline{BW1}$ - $\overline{BW4}$  LOW.

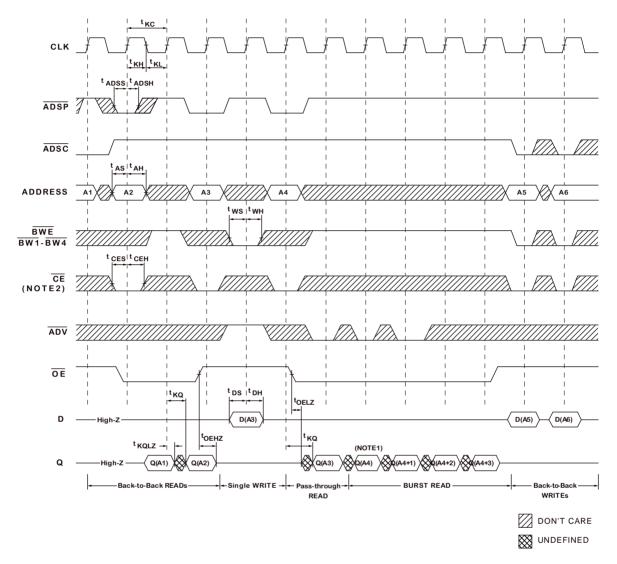

#### **PIPELINE READ/WRITE TIMING**

- Note: 1. Q(A4) refers to output from address A4. Q(A4 + 1) refers to output from the next internal burst address following A4.

- 2.  $\overline{CE2}$  and CE2 have timing identical to  $\overline{CE}$ . On this diagram, when  $\overline{CE}$  is LOW,  $\overline{CE2}$  is LOW and CE2 is HIGH. When  $\overline{CE}$  is HIGH,  $\overline{CE2}$  is HIGH and CE2 is LOW.

- 3. The data bus (Q) remains in High-Z following a WRITE cycle unless an ADSP, ADSC or ADV cycle is performed.

- 4.  $\overline{\text{GW}}$  is HIGH.

- 5. Back-to-back READs may be controlled by either  $\overline{\text{ADSP}}$  or  $\overline{\text{ADSC}}$ .

Preliminary T35L3232B

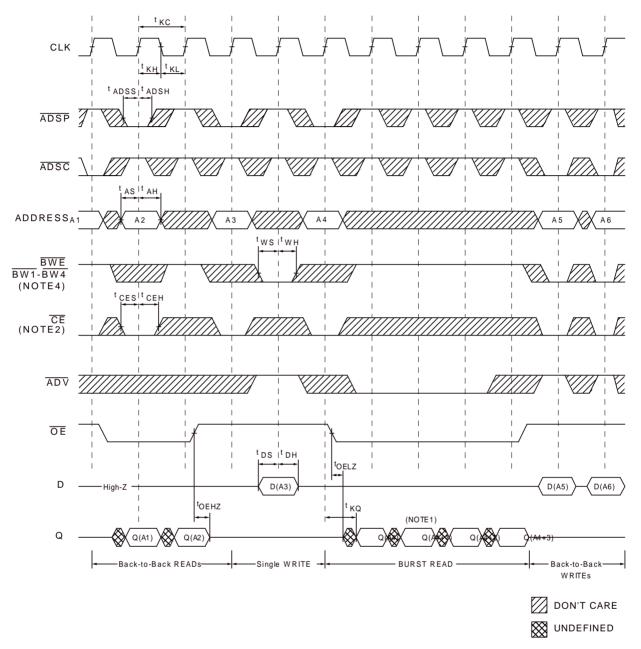

### FLOW-THROUGH READ/WRITE TIMING

- **Note:** 1. Q(A4) refers to output from address A4. Q (A4 + 1) refers to output from the next internal burst address following A4.

- 2.  $\overline{CE2}$  and CE2 have timing identical to  $\overline{CE}$ . On this diagram, when  $\overline{CE}$  is LOW,  $\overline{CE2}$  is LOW and CE2 is HIGH. When  $\overline{CE}$  is HIGH,  $\overline{CE2}$  is HIGH and CE2 is LOW.

- 3. The data bus (Q) remains in High-Z following a WRITE cycle unless an ADSP, ADSC or ADV cycle is performed.

- 4.  $\overline{\text{GW}}$  is HIGH.

- 5. Back-to-back READs may be controlled by either  $\overline{\text{ADSP}}$  or  $\overline{\text{ADSC}}$ .

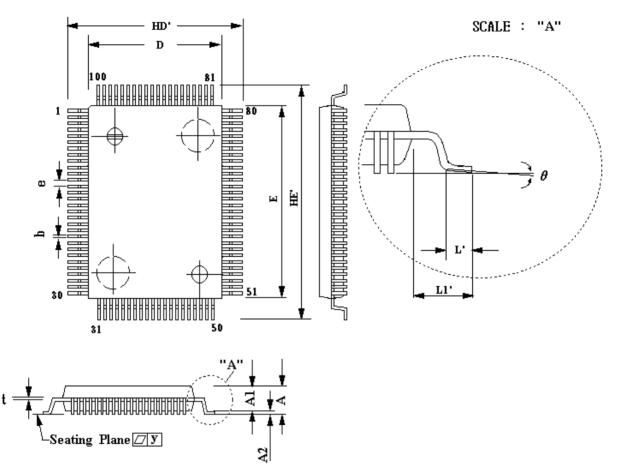

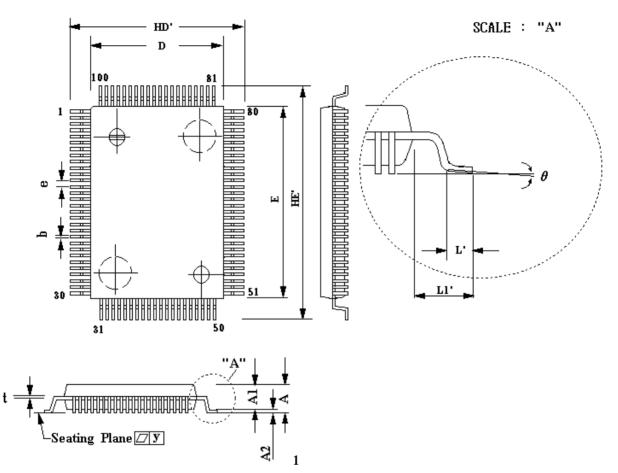

# PACKAGE DIMENSIONS 100-LEAD QFP SSRAM (14 x 20 mm)

| SYMBOL           | DIMENSIONS IN INCHES       | DIMENTION IN MM           |

|------------------|----------------------------|---------------------------|

| А                | 0.130(MAX)                 | 3.302(MAX)                |

| A1               | 0.112»10.005               | 2.845 <b>Ȓ</b> 0.127      |

| A2               | 0.004(MIN)                 | 0.102(MIN)                |

| b                | 0.012+0.004-0.002          | 0.300+0.102-0.051         |

| D                | 0.551»10.005               | 14.000Ȓ0.127              |

| Е                | 0.787»10.005               | 20.000»10.127             |

| е                | 0.026»10.006               | 0.650 <b>Ȓ</b> 0.152      |

| HD'              | 0.677 <b>»</b> 10.008      | 17.200»10.203             |

| HE'              | 0.913 <b>»1</b> 0.008      | 23.200»10.203             |

| L'               | 0.032 <b>»1</b> 0.008      | 0.800 <b>Ȓ</b> 0.203      |

| L1'              | 0.063»10.008               | 1.600 <b>Ȓ</b> 0.203      |

| t                | 0.006+0.004-0.002          | 0.150+0.102-0.051         |

| У                | 0.004(MAX)                 | 0.102(MAX)                |

| <sup>1</sup> ⁄at | 0 <b>»T</b> ∼12 <b>»</b> T | 0 <b>»T</b> ∼12 <b>»T</b> |

# PACKAGE DIMENSIONS 100-LEAD TQFP SSRAM (14 x 20 mm)

| SYMBOL | DIMENSIONS IN INCHES  | DIMENTION IN MM           |

|--------|-----------------------|---------------------------|

| А      | 0.063(MAX)            | 1.600(MAX)                |

| A1     | 0.055»10.005          | 1.400»10.050              |

| A2     | 0.002(MIN)            | 0.050(MIN)                |

| b      | 0.013+0.002-0.004     | 0.320+0.060-0.100         |

| D      | 0.551»10.004          | 14.000 <b>Ȓ</b> 0.100     |

| Е      | 0.787 <b>Ȓ</b> 0.004  | 20.000Ȓ0.100              |

| е      | 0.026»10.006          | 0.650»10.152              |

| HD'    | 0.630 <b>Ȓ</b> 0.004  | 16.000 <b>Ȓ</b> 0.100     |

| HE'    | 0.866»10.004          | 22.000 <b>Ȓ</b> 0.100     |

| L'     | 0.024 <b>»1</b> 0.006 | 0.600»10.150              |

| L1'    | 0.039 <b>»1</b> 0.006 | 1.000»10.150              |

| t      | 0.006 <b>»1</b> 0.002 | 0.150+0.050-0.060         |

| у      | 0.003(MAX)            | 0.080(MAX)                |

| ¹∕at   | 0 <b>»T~7»T</b>       | 0 <b>»T</b> ∼7 <b>»</b> T |

## **PIN DESCRIPTIONS**

| PINS                                 | SYM.                     | TYPE                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|--------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-37, 44-48,<br>81, 82, 99,<br>100, | A0-A14                   | Input-<br>Synchronous | Addresses: These inputs are registered and must meet the setup and<br>hold times around the rising edge of CLK. The burst counter<br>generates internal addresses associated with A0 and A1, during<br>burst cycle and wait cycle.                                                                                                                   |

| 93-96                                | BW1<br>BW2<br>BW3<br>BW4 | Input-<br>Synchronous | Byte Writes: A byte write is LOW for a WRITE cyle and HIGH for<br>a READ cycle. $\overline{BW1}$ controls DQ1-DQ8. $\overline{BW2}$ controls DQ9-<br>DQ16. $\overline{BW3}$ controls DQ17-DQ24. $\overline{BW4}$ controls DQ25-DQ32.<br>Data I/O are high impedance if either of these inputs are LOW,<br>conditioned by $\overline{BWE}$ being LOW. |

| 87                                   | BWE                      | Input-<br>Synchronous | Write Enable: This active LOW input gates byte write operations<br>and must meet the setup and hold times around the rising edge of<br>CLK.                                                                                                                                                                                                          |

| 88                                   | GW                       | Input-<br>Synchronous | Global Write: This active LOW input allows a full 32-bit WRITE to occur independent of the $\overline{BWE}$ and $\overline{BWn}$ lines and must meet the setup and hold times around the rising edge of CLK.                                                                                                                                         |

| 89                                   | CLK                      | Input-<br>Synchronous | Clock: This signal registers the addresses, data, chip enables, writecontrol and burst control inputs on its rising edge. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                                                      |

| 98                                   | CE                       | Input-<br>Synchronous | Synchronous Chip Enable: This active LOW input is used to enable the device and conditions internal use of $\overline{\text{ADSP}}$ . This input is sampled only when a new external address is loaded.                                                                                                                                              |

| 92                                   | CE2                      | Input-<br>Synchronous | Synchronous Chip Enable: This active LOW input is used to enable<br>the device. This input is sampled only when a new external address<br>is loaded. This input can be used for memory depth expansion.                                                                                                                                              |

| 97                                   | CE2                      | Input-<br>Synchronous | Synchronous Chip Enable: This active HIGH input is used to enable<br>the device. This input is sampled only when a new external address<br>is loaded. This input can be used for memory depth expansion.                                                                                                                                             |

| 86                                   | ŌĒ                       | Input                 | Output enable: This active LOW asynchronous input enables the data output drivers.                                                                                                                                                                                                                                                                   |

| 83                                   | ADV                      | Input-<br>Synchronous | Address Advance: This active LOW input is used to control the internal burst counter. A HIGH on this pin generates wait cycle (no address advance).                                                                                                                                                                                                  |

| 84                                   | ADSP                     | Input-<br>Synchronous | Address Status Processor: This active LOW input, along with $\overline{CE}$ being LOW, causes a new external address to be registered and a READ cycle is initiated using the new address.                                                                                                                                                           |

# PIN DESCRIPTIONS (continued)

| QFP PINS                                                                                               | SYM.         | TYPE                  | DESCRIPTION                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------|--------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 85                                                                                                     | ADSC         | Input-<br>Synchronous | Address Status Controller: This active LOW input causes<br>device to be deselected or selected along with new external<br>address to be registered. A READ or WRITE cycle is<br>initiated depending upon write control inputs. |

| 14                                                                                                     | FT           | Input-<br>Static      | A LOW on this pin selects in flow-through mode. A NC or<br>HIGH on this pin selects in pipeline mode.                                                                                                                          |

| 31                                                                                                     | MODE         | Input-<br>Static      | Mode: This input selects the burst sequence. A LOW on this<br>pin selects LINEAR BURST. A NC or HIGH on this pin<br>selects INTERLEAVED BURST. Do not alter input state<br>while device is operating.                          |

| 64                                                                                                     | ZZ           | Input                 | Snooze Enable: This active HIGH asynchronous input causes<br>the device to enter a low-power standby mode in which all<br>data in the memory arry is retained.                                                                 |

| 2, 3, 6-9, 12, 13,<br>18, 19, 22-25,<br>28, 29, 52, 53,<br>56-59, 62, 63,<br>68, 69, 72-75,<br>78, 79, | DQ1-<br>DQ32 | Input/<br>Output      | Data Inputs/Outputs: First Byte is DQ1-DQ8. Second Byte is DQ9-DQ16. Third Byte is DQ17-DQ24. Fourth Byte is DQ25-DQ32. Input data must meet setup and hold times around the rising edge of CLK.                               |

| 15,41,65,91                                                                                            | VCC          | Supply                | Power Supply: 3.3V +10%/-5%                                                                                                                                                                                                    |

| 17,40,67,90                                                                                            | VSS          | Ground                | Ground: GND                                                                                                                                                                                                                    |

| 4,11,20,27,54,<br>61,70,77                                                                             | VCCQ         | I/O Supply            | Output Buffer Supply: 3.3V +10%/-5%                                                                                                                                                                                            |

| 5,10,21,26,55,<br>60,71,76                                                                             | VSSQ         | I/O Ground            | Output Buffer Ground: GND                                                                                                                                                                                                      |

| 1,16,30,38,<br>39,42,43,49,<br>50, 51, 66,80                                                           | NC           | -                     | No Connect: These signals are not internally conntected.                                                                                                                                                                       |

# **INTERLEAVED BURST ADDRESS TABLE** (MODE = NC/VCC)

| First Address<br>(external) | Second Address<br>(internal) | Third Address<br>(internal) | Fourth Address<br>(internal) |  |  |

|-----------------------------|------------------------------|-----------------------------|------------------------------|--|--|

| AA00                        | AA01                         | AA10                        | AA11                         |  |  |

| AA01                        | AA00                         | AA11                        | AA10                         |  |  |

| AA10                        | AA11                         | AA00                        | AA01                         |  |  |

| AA11                        | AA10                         | AA01                        | AA00                         |  |  |

### **LINEAR BURST ADDRESS TABLE** (MODE = GND)

| First Address<br>(external) | Second Address<br>(internal) | Third Address<br>(internal) | Fourth Address<br>(internal) |  |  |

|-----------------------------|------------------------------|-----------------------------|------------------------------|--|--|

| AA00                        | AA01                         | AA10                        | AA11                         |  |  |

| AA01                        | AA10                         | AA11                        | AA00                         |  |  |

| AA10                        | AA11                         | AA00                        | AA01                         |  |  |

| AA11                        | AA00                         | AA01                        | AA10                         |  |  |

#### PARTIAL TRUTH TABLE FOR READ/WRITE

| Function       | $\overline{\mathrm{GW}}$ | BWE | BW1 | BW2 | BW3 | BW4 |

|----------------|--------------------------|-----|-----|-----|-----|-----|

| READ           | Н                        | Н   | Х   | Х   | Х   | Х   |

| READ           | Н                        | L   | Н   | Н   | Н   | Н   |

| WRITE one byte | Н                        | L   | L   | Н   | Н   | Н   |

| WRITE all byte | Н                        | L   | L   | L   | L   | L   |

| WRITE all byte | L                        | Х   | Х   | Х   | Х   | Х   |

# TRUTH TABLE

| OPERATION                    | ADDRESS<br>USED | CE | CE2 | CE2 | ZZ | ADSP | ADSC | ADV | WRITE | ŌĒ | CLK | DQ     |

|------------------------------|-----------------|----|-----|-----|----|------|------|-----|-------|----|-----|--------|

| Deselected Cycle, Power Down | None            | Н  | Х   | Х   | L  | Х    | L    | Х   | Х     | Х  | L-H | High-Z |

| Deselected Cycle, Power Down | None            | L  | Х   | L   | L  | L    | Х    | Х   | Х     | Х  | L-H | High-Z |

| Deselected Cycle, Power Down | None            | L  | Н   | Х   | L  | L    | Х    | Х   | Х     | Х  | L-H | High-Z |

| Deselected Cycle, Power Down | None            | L  | Х   | L   | L  | Н    | L    | Х   | Х     | Х  | L-H | High-Z |

| Deselected Cycle, Power Down | None            | L  | Н   | Х   | L  | Н    | L    | Х   | Х     | Х  | L-H | High-Z |

| Snooze Cycle, Power Down     | None            | Х  | Х   | Х   | Н  | Х    | Х    | Х   | Х     | Х  | Х   | High-Z |

| READ Cycle, Begin Burst      | External        | L  | L   | Н   | L  | L    | Х    | Х   | Х     | L  | L-H | Q      |

| READ Cycle, Begin Burst      | External        | L  | L   | Н   | L  | L    | Х    | Х   | Х     | Η  | L-H | High-Z |

| WRITE Cycle, Begin Burst     | External        | L  | L   | Н   | L  | Н    | L    | Х   | L     | Х  | L-H | D      |

| READ Cycle, Begin Burst      | External        | L  | L   | Н   | L  | Н    | L    | Х   | Н     | L  | L-H | Q      |

| READ Cycle, Begin Burst      | External        | L  | L   | Н   | L  | Н    | L    | Х   | Н     | Н  | L-H | High-Z |

| READ Cycle, Continue Burst   | Next            | Х  | Х   | Х   | L  | Н    | Н    | L   | Н     | L  | L-H | Q      |

| READ Cycle, Continue Burst   | Next            | Х  | Х   | Х   | L  | Н    | Н    | L   | Н     | Н  | L-H | High-Z |

| READ Cycle, Continue Burst   | Next            | Н  | Х   | Х   | L  | Х    | Н    | L   | Н     | L  | L-H | Q      |

| READ Cycle, Continue Burst   | Next            | Н  | Х   | Х   | L  | Х    | Н    | L   | Н     | Н  | L-H | High-Z |

| WRITE Cycle, Continue Burst  | Next            | Х  | Х   | Х   | L  | Н    | Н    | L   | L     | Х  | L-H | D      |

| WRITE Cycle, Continue Burst  | Next            | Н  | Х   | Х   | L  | Х    | Н    | L   | L     | Х  | L-H | D      |

| READ Cycle, Suspend Burst    | Current         | Х  | Х   | Х   | L  | Н    | Н    | Η   | Н     | L  | L-H | Q      |

| READ Cycle, Suspend Burst    | Current         | Х  | Х   | Х   | L  | Н    | Н    | Н   | Н     | Н  | L-H | High-Z |

| READ Cycle, Suspend Burst    | Current         | Н  | Х   | Х   | L  | Х    | Н    | Н   | Н     | L  | L-H | Q      |

| READ Cycle, Suspend Burst    | Current         | Н  | Х   | Х   | L  | Х    | Н    | Н   | Н     | Н  | L-H | High-Z |

| WRITE Cycle, Suspend Burst   | Current         | Х  | Х   | Х   | L  | Н    | Н    | Н   | L     | Х  | L-H | D      |

| WRITE Cycle, Suspend Burst   | Current         | Н  | Х   | Х   | L  | Х    | Н    | Н   | L     | Х  | L-H | D      |

- Note: 1. X means "don't care." H means logic HIGH. L means logic LOW. WRITE = L means any one or more byte write enable signals ( $\overline{BW1}$ ,  $\overline{BW2}$ ,  $\overline{BW3}$  or  $\overline{BW4}$ ) and  $\overline{BWE}$  are LOW, or  $\overline{GW}$  equals LOW. WRITE = H means all byte write signal are HIGH.

- 2.  $\overline{BW1}$  = enables write to DQ1-DQ8.  $\overline{BW2}$  = enables write to DQ9-DQ16.  $\overline{BW3}$  = enables write to DQ17-DQ24.  $\overline{BW4}$  = enables write to DQ25-DQ32.

- 3. All inputs except  $\overline{OE}$  and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

- 4. Suspending burst generates wait cycle.

- 5. For a write operation following a read operation.  $\overrightarrow{OE}$  must be HIGH before the input data required setup time plus High-Z time for  $\overrightarrow{OE}$  and staying HIGH throughout the input data hold time.

- 6. <u>This device contains circuitry that will ensure the outputs will be High-Z during power-up.</u>

- 7. ADSP = LOW along with chip being selected always initiates an internal READ cycle at the L-H edge of CLK. A WRITE cycle can be performed by setting WRITE LOW for the CLK L-H edge of the subsequent wait cycle. Refer to WRITE timing diagram for clarification.

# **ABSOLUTE MAXIMUM RATINGS\***

Voltage on VCC Supply Relative to VSS.

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# DC ELECTRICAL CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS

$(0^{\circ}C \le Ta \le 70^{\circ}C; VCC = 3.3V + 10\% / -5\%$  unless otherwise noted)

| DESCRIPTION                   | CONDITIONS                                         | SYM. | MIN  | MAX        | UNITS | NOTES |

|-------------------------------|----------------------------------------------------|------|------|------------|-------|-------|

| Input High (Logic)<br>voltage |                                                    | VIH  | 2    | VCCQ + 0.3 | V     | 1, 2  |

| Input Low (Logic)<br>voltage  |                                                    | VIL  | -0.3 | 0.8        | V     | 1, 2  |

| Input Leakage Current         | $0V \le V_{IN} \le VCC$                            | ILI  | -2   | 2          | μA    | 14    |

| Output Leakage Current        | Output(s) disabled, 0V<br>≤ V <sub>OUT</sub> ≤ VCC | ILO  | -2   | 2          | μΑ    |       |

| Output High Voltage           | $I_{OH} = -4.0 \text{ mA}$                         | VOH  | 2.4  |            | V     | 1, 11 |

| Output Low Voltage            | IOL = 8.0  mA                                      | VOL  |      | 0.4        | V     | 1, 11 |

| Supply Voltage                |                                                    | Vcc  | 3.1  | 3.6        | V     | 1     |

|                                     |                                                                                                                                                                                                                                                                                                                                  |                  |     |      | MAX. |      |       |           |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------|------|------|-------|-----------|

| DESCRIPTION                         | CONDITIONS                                                                                                                                                                                                                                                                                                                       | SYM.             | ТҮР | -3.8 | -4   | -4.5 | UNITS | NOTES     |

| Power Supply<br>Current : Operating | Device selected; all inputs ≤V <sub>IL</sub> or<br>≥ V <sub>IH</sub> ; cycle time ≥ <sup>t</sup> KC MIN; VCC<br>= MAX; outputs open                                                                                                                                                                                              | ICC              | TBD | 250  | 200  | 150  | mA    | 3, 12, 13 |

| Power Supply<br>Current: Idle       | $\frac{\text{Device selected}; \overline{\text{ADSC}}, \overline{\text{ADSP}},}{\overline{\text{ADV}}, \overline{\text{GW}}, \overline{\text{BWE}} \ge V_{\text{IH}}; \text{ all other}}$ inputs $\le V_{\text{IL}}$ or $\ge V_{\text{IH}}; \text{ VCC} = \text{MAX};$ cycle time $\ge {}^{\text{t}}\text{KC}$ MIN: outputs open | I <sub>SB1</sub> | TBD | 60   | 60   | 60   | mA    | 12, 13    |

| CMOS Standby                        | Device deselected; VCC = MAX; all<br>inputs $\leq$ VSS + 0.2 or $\geq$ VCC - 0.2;<br>all inputs static; CLK frequency =0                                                                                                                                                                                                         | I <sub>SB2</sub> | TBD | 10   | 10   | 10   | mA    | 12, 13    |

| TTL Standby                         | Device deselected; all inputs $\leq V_{IL}$<br>or $\geq V_{IH}$ ; all inputs static; VCC =<br>MAX;CLK frequency = 0                                                                                                                                                                                                              | I <sub>SB3</sub> | TBD | 25   | 25   | 25   | mA    | 12, 13    |

| Clock Running                       | Device deselected; all inputs $\leq V_{IL}$<br>or $\geq V_{IH}$ ; VCC =MAX; CLK cycle<br>time $\geq {}^{t}KCMIN$                                                                                                                                                                                                                 | I <sub>SB4</sub> | TBD | 60   | 60   | 60   | mA    | 12, 13    |

# AC ELECTRICAL CHARACTERISTICS (Note 5) ( $0^{\circ}C \le T_A \le 70^{\circ}C$ ; VCC=3.3V +0.3V/-0.165V)

| DESCRIPTION                                                                              |                   | -3   | -3.8 |     | -4  |     | .5  | UNITS | NOTES |

|------------------------------------------------------------------------------------------|-------------------|------|------|-----|-----|-----|-----|-------|-------|

|                                                                                          | SYM.              | MIN  | MAX  | MIN | MAX | MIN | MAX |       |       |

| Clock(pipeline)                                                                          | <b>I</b>          |      |      |     |     |     | 11  |       |       |

| Clock cycle time                                                                         | tKC               | 6.6  |      | 7.5 |     | 8.5 |     | ns    |       |

| Clock to output valid                                                                    | tKQ               |      | 3.8  |     | 4   |     | 4.5 |       |       |

| Clock to output invalid                                                                  | tKQX              | 1.5  |      | 2   |     | 2   |     | ns    |       |

| Clock to output in Low-Z                                                                 | <sup>t</sup> KQLZ | 1.5  |      | 2   |     | 2   |     | ns    |       |

| Clock(flow-through)                                                                      |                   |      |      |     |     |     |     |       |       |

| Clock cycle time                                                                         | tKC               | 10.5 |      | 15  |     | 15  |     | ns    |       |

| Clock to output valid                                                                    | tKQ               |      | 9.0  |     | 10  |     | 11  |       |       |

| Clock to output invalid                                                                  | tKQX              | 3    |      | 3   |     | 3   |     | ns    |       |

| Clock to output in Low-Z                                                                 | <sup>t</sup> KQLZ | 3    |      | 3   |     | 3   |     | ns    |       |

| Output Times                                                                             |                   |      |      |     |     |     |     |       |       |

| Clock HIGH time                                                                          | <sup>t</sup> KH   | 1.8  |      | 1.9 |     | 2.0 |     | ns    |       |

| Clock LOW time                                                                           | tKL               | 1.8  |      | 1.9 |     | 2.0 |     | ns    | 6, 7  |

| Clock to output in High-Z                                                                | <sup>t</sup> KQHZ |      | 5    |     | 5   |     | 5   | ns    | 6, 7  |

| OE to output valid                                                                       | tOEQ              |      | 5    |     | 5   |     | 5   | ns    | 9     |

| OE to output in Low-Z                                                                    | tOELZ             | 0    |      | 0   |     | 0   |     | ns    | 6, 7  |

| OE to output in High-Z                                                                   | tOEHZ             |      | 5    |     | 5   |     | 5   | ns    | 6, 7  |

| Setup Times                                                                              |                   |      |      |     |     |     |     |       |       |

| Address                                                                                  | t <sub>AS</sub>   | 1.7  |      | 2.0 |     | 2.0 |     | ns    | 8, 10 |

| Address Status( ADSC , ADSP )                                                            | tADSS             | 1.7  |      | 2.0 |     | 2.0 |     | ns    | 8, 10 |

| Address Advance ( $\overline{\text{ADV}}$ )                                              | tAAS              | 1.7  |      | 2.0 |     | 2.0 |     | ns    | 8, 10 |

| Byte Write Enables $(\overline{BW1} \sim \overline{BW4}, \overline{BWE}, \overline{GW})$ | tws               | 1.7  |      | 2.0 |     | 2.0 |     | ns    | 8, 10 |

| Data-in                                                                                  | tDS               | 1.7  |      | 2.0 |     | 2.0 |     | ns    | 8, 10 |

| Chip Enables( $\overline{CE}$ , $\overline{CE2}$ , CE2)                                  | tCES              | 1.7  |      | 2.0 |     | 2.0 |     | ns    | 8, 10 |

| Hold Times                                                                               |                   |      | T    | T   | T   | T   |     |       |       |

| Address                                                                                  | tAH               | 0.5  |      | 0.5 |     | 0.5 |     | ns    | 8, 10 |

| Address Status( ADSC , ADSP )                                                            | tADSH             | 0.5  |      | 0.5 |     | 0.5 |     | ns    | 8,10  |

| Address Advance ( ADV )                                                                  | tAAH              | 0.5  |      | 0.5 |     | 0.5 |     | ns    | 8, 10 |

| Byte Write Enables                                                                       | tWH               | 0.5  |      | 0.5 |     | 0.5 |     | ns    | 8, 10 |

| $(\overline{BW1} \sim \overline{BW4}, \overline{BWE}, \overline{GW})$                    |                   |      |      |     |     |     |     |       |       |

| Data-in                                                                                  | <sup>t</sup> DH   | 0.5  |      | 0.5 |     | 0.5 |     | ns    | 8, 10 |

| Chip Enables( $\overline{CE}, \overline{CE2}, CE2$ )                                     | tCEH              | 0.5  |      | 0.5 |     | 0.5 |     | ns    | 8, 10 |

# CAPACITANCE

| DESCRIPTION                      | CONDITIONS                     | SYM. | TYP | MAX | UNITS | NOTES |

|----------------------------------|--------------------------------|------|-----|-----|-------|-------|

| Input Capacitance                | $T_A = 25^{\circ}C; f = 1 MHz$ | CI   | 3   | 4   | pF    | 4     |

| Input/ Output<br>Capacitance(DQ) | VCC = 3.3V                     | CO   | 6   | 7   | pF    | 4     |

#### THERMAL CONSIDERATION

| DESCRIPTION                              | CONDITIONS                     | SYM.          | QFP TYP | UNITS | NOTES |

|------------------------------------------|--------------------------------|---------------|---------|-------|-------|

| Thermal Resistance - Junction to Ambient | Still air, soldered on         | $\Theta_{JA}$ | 20      | °C/W  |       |

| Thermal Resistance - Junction to Case    | 4.25x1.125 inch 4-layer<br>PCB | $\Theta_{JB}$ | 1       | °C/W  |       |

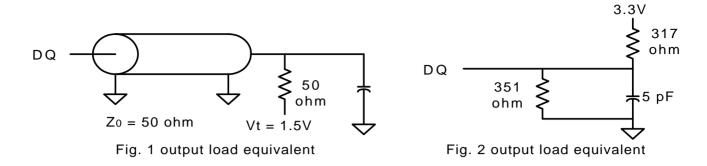

### AC TEST CONDITIONS

| Input pulse levels            | 0V to 3.0V        |

|-------------------------------|-------------------|

| Input rise and fall times     | 1.5ns             |

| Input timing reference levels | 1.5V              |

| Output reference levels       | 1.5V              |

| Output load                   | See Figures 1 and |

| -                             | 2                 |

#### Notes:

- 1. All voltages referenced to VSS (GND).

- 2. Overshoot:  $V_{IH} \le +3.6 \text{ V}$  for  $t \le {}^{t}\text{KC}/2$ .

Undershoot:  $V_{IL} \leq -1.0 \text{ V}$  for  $t \leq {}^{t}\text{KC}/2$ .

- 3. Icc is given with no output current. Icc increases with greater output loading and faster cycle times.

- 4. This parameter is sampled.

- 5. Test conditions as specified with the output loading as shown in Fig. 1 unless otherwise noted.

- 6. Output loading is specified with CL = 5 pF as in Fig. 2.

#### At any given temperature and voltage condition, <sup>t</sup>KQHZ is less than <sup>t</sup>KQLZ and <sup>t</sup>OEHZ is less than <sup>t</sup>OELZ.

- 8. A READ cycle is defined by byte write enables all HIGH or ADSP LOW along with chip enables being active for the required setup and hold times. A WRITE cycle is defined by at one byte or all byte WRITE per READ/WRITE TRUTH TABLE.

- 9. OE is a "don't care" when a byte write enable is sampled LOW.

- 10. This is a synchronous device. All synchronous inputs must meet specified setup and hold time, except for "don't care" as defined in the truth table.

- 11.AC I/O curves are available upon request.

- 12."Device Deselected means the device is in POWER-DOWN mode as defined in the truth table. "Device Selected" means the device is active.

- 13.Typical values are measured at 3.3V, 25°C and 20ns cycle time.

- 14.MODE pin has an internal pull-up and exhibits an input leakage current of  $\pm 10\mu A$ .

# **OUTPUT LOADS**

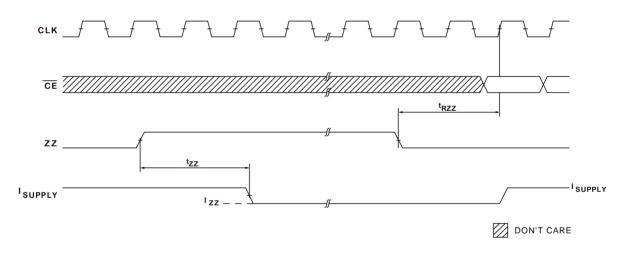

#### **SNOOZE MODE**

SNOOZE MODE is a low current, "power down" mode in which the device is deselected and current is reduced to  $I_{ZZ}$ . The duration of SNOOZE MODE is dictated by the length of time the ZZ pin is in a HIGH state. After entering SNOOZE MODE, the clock and all other inputs are ignored. The ZZ pin (pin 64) is an asynchronous, active HIGH input that causes the

device to enter SNOOZE MODE. When the ZZ pin becomes a logic HIGH,  $I_{ZZ}$  is guaranteed after the setup time <sup>t</sup>ZZ is met. Any access pending when entering SNOOZE MODE is not guaranteed to successfully complete. Therefore, SNOOZE MODE must not be initiated until valid pending operations are completed.

## **SNOOZE MODE ELECTRICAL CHARACTERISTICS**

| DESCRIPTION                            | CONDITIONS      | SYMBOL           | MIN    | MAX    | UNITS | NOTES |

|----------------------------------------|-----------------|------------------|--------|--------|-------|-------|

| Current during<br>SNOOZE MODE          | $ZZ \ge V_{IH}$ | I <sub>ZZ</sub>  |        | 5      | mA    |       |

| ZZ HIGH to<br>SNOOZE MODE time         |                 | tZZ              | 2(tKC) |        | ns    | 4     |

| SNOOZE MODE<br>Operation Recovery Time |                 | <sup>t</sup> RZZ |        | 2(tKC) | ns    | 4     |

### SNOOZE MODE WAVEFORM

Note: 1. The  $\overline{CE}$  signal shown above refers to a TRUE state on all chip selects for the device. 2. All other inputs held to static CMOS levels (VIN  $\leq$  Vss + 0.2 V or  $\geq$  Vcc -0.2 V).