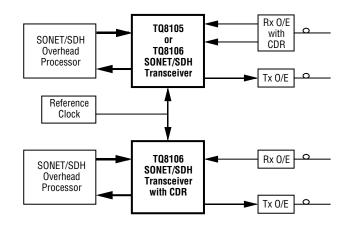

The TQ8105/TQ8106 are SONET/SDH transceivers that integrate multiplexing, demultiplexing, SONET/SDH framing, clock-synthesis PLL, and enhanced line and clock diagnostic functions into a single monolithic device. The TQ8106 is a pin-compatible upgrade of the TQ8105 that includes a Clock and Data Recovery (CDR) function. The TQ8105 and TQ8106 allow maximum flexibility in the selection of internal/external Clock and Data Recovery, Opto-Electronic (O/E) Module, and Reference Clock Sources.

On-chip PLLs use external RC-based loop filters to allow custom tailoring of loop response and support the wide range of reference clock frequencies found in SONET/SDH/ATM systems. For transmit clock synthesis or for CDR, the PLLs exceed ANSI, Bellcore, and ITU jitter specifications for systems when combined with industry-typical O/E devices such as Sumitomo, AT&T, HP, and AMP. The TQ8105/TQ8106 PLLs provide byte clocks and constantrate 38.88 MHz and 51.84 MHz, synthesized clock outputs, providing clocking for UTOPIA and other system busses. Transmit data may also be clocked into the devices with respect to the reference clock.

Operating from a single +5V supply, the TQ8105/TQ8106 provides fully compliant functionality and performance, utilizing direct-connected PECL levels (differential or single-ended) for high-speed I/O. As compared to AC-coupled schemes, the direct-coupled connections reduce jitter and switching-level offsets due to data patterns. The TQ8105/TQ8106 can also provide direct connection to high-speed I/O utilizing ECL levels with a –5V supply. Low-speed bus, control, and clock I/O utilize TTL levels. (An ECL/ PECL reference clock input is also provided; at 155.52 MHz the input should be only PECL/ECL.) Output TTL pins can be tristated and may also be configured for V<sub>OH</sub> with a 3.3V supply connection.

# TQ8105/8106

PRELIMINARY DATA SHEET

# SONET/SDH Transceivers

# Features

- Single-chip, byte-wide Mux, Demux, Framer, and Tx clocksynthesis PLL with enhanced diagnostics

- TQ8106 includes monolithic Clock and Data Recovery

- SONET/SDH/ATM compliant for STS-12/STM-4 (622 Mb/s) or STS-3/STM-1 (155 Mb/s) rates

- 155.52, 77.76, 51.84, 38.88, or 19.44 MHz reference clock inputs with TTL, PECL, or ECL level

- 38.88 MHz and 51.84 MHz clock outputs for UTOPIA as well as byte clock rate (77.76 or 19.44 MHz)

- External RC-based loop filters

- Integrated loopbacks with enhanced line and reference clock diagnostics

- Direct-coupled standard, PECL, high-speed I/O with ECL option

- Clean TTL interface to PMC-Sierra devices

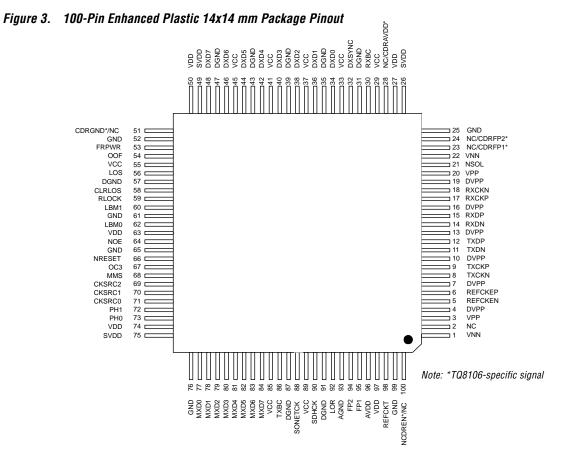

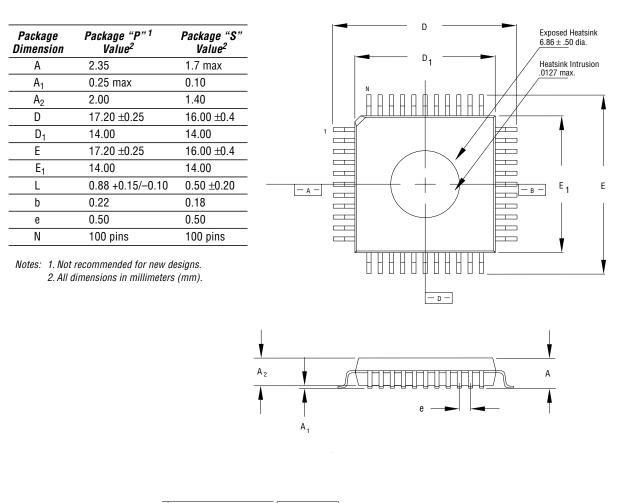

- 100-pin 14x14 mm JEDEC plastic package

- +5V-only supply for PECL I/O (-5.2V required for ECL I/O option)

- -40 to +125°C case operating temperature

### PRELIMINARY DATA SHEET

The combination of a thermally enhanced, 100-pin JEDEC, metric, plastic package, the low-power dissipation of the device, and the wide casetemperature range permits operation without a heat sink in most designs.

The TQ8106 uses the same pinout as the TQ8105 and is compatible with it.

The TQ8105/TQ8106 provides comprehensive, integrated, loopback functionality and enhanced line and reference clock diagnostics required of SONET/ SDH systems, minimizing additional external circuitry. TQ8105/TQ8106 diagnostics include:

- Loss of Reference clock detector (LOR) output to indicate that the PLL Reference Clock is not toggling

- Lock Indicator (RLOCK), which permits monitoring of the receiver clock frequency, flagging when the frequency drifts beyond approximately 500 ppm

- Loss of Signal (LOS) detector output to indicate that the incoming data stream has no data transitions in 128-bit periods

- ECL/PECL input (NSOL) to allow LOS from an O/E module to force the data stream to all zeroes, eliminating the need for external glue logic.

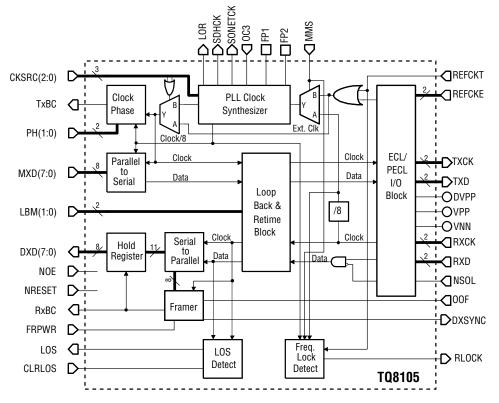

# Figure 1. TQ8105 Block Diagram

PRELIMINARY DATA SHEET

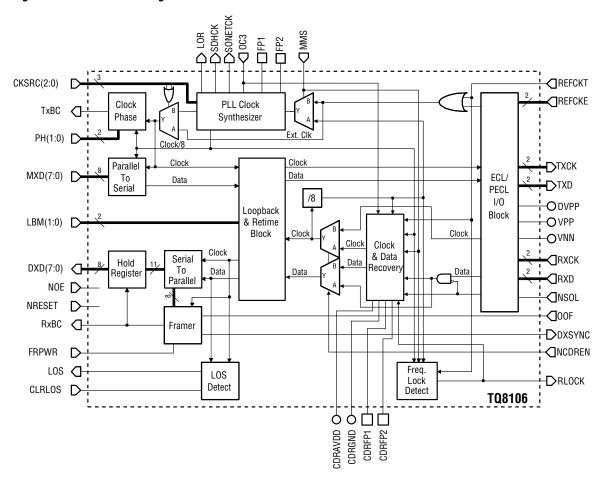

### Figure 2. TQ8106 Block Diagram

PRELIMINARY DATA SHEET

Table 1. Signal Descriptions (continues on next page)

| Pin | Signal  | Function       | Description                               |

|-----|---------|----------------|-------------------------------------------|

| 1   | VNN     | –5.2V/Ground   | ECL/PECL section power                    |

| 2   | NC      | No Connect     | Do not connect                            |

| 3   | VPP     | Ground/+5V     | ECL/PECL Positive Supply (see Table 6B)   |

| 4   | DVPP    | Ground/+5V     | ECL/PECL Driver Return (see Table 6B)     |

| 5   | REFCKEN | ECL/PECL Input | Tx Ref. Clock or Bypass Clock, Complement |

| 6   | REFCKEP | ECL/PECL Input | Tx Ref. Clock or Bypass Clock, True       |

| 7   | DVPP    | Ground/+5V     | ECL/PECL Driver Return (see Table 6B)     |

| 8   | TXCKN   | ECL/PECL Out   | Transmit Clock, Complement                |

| 9   | ТХСКР   | ECL/PECL Out   | Transmit Clock, True                      |

| 10  | DVPP    | Ground/+5V     | ECL/PECL Driver Return (see Table 6B)     |

| 11  | TXDN    | ECL/PECL Out   | Transmit Data, Complement                 |

| 12  | TXDP    | ECL/PECL Out   | Transmit Data, True                       |

| 13  | DVPP    | Ground/+5V     | ECL/PECL Driver Return (see Table 6B)     |

| 14  | RXDN    | ECL/PECL Input | Receive Data, Complement                  |

| 15  | RXDP    | ECL/PECL Input | Receive Data, True                        |

Note: \*TQ8106-specific signal

4

PRELIMINARY DATA SHEET

| Pin      | Signal       | Function                      | Description                                                      |

|----------|--------------|-------------------------------|------------------------------------------------------------------|

| 16       | DVPP         | Ground/+5V                    | ECL/PECL Driver Return (see Table 6B)                            |

| 17       | RXCKP        | ECL/PECL Input                | Receive Clock, True (Ignored when CDR used)                      |

| 18       | RXCKN        | ECL/PECL Input                | Receive Clock, Complement (Ignored when CDR used)                |

| 19       | DVPP         | Ground/+5V                    | ECL/PECL Driver Return (see Table 6B)                            |

| 20       | VPP          | Ground/+5V                    | ECL/PECL Positive Supply (see Table 6B)                          |

| 21       | NSOL         | ECL/PECL Input                | Loss of Signal — zeroes serial data in when low; RXBC=TXCK/8     |

| 22       | VNN          | –5.2V/Ground                  | ECL/PECL section power (see Table 6B)                            |

| 23       | NC/CDRFP1*   | Analog Output                 | CDR Loop Filter Pin 1 — Charge Pump Out (ignored by TQ8105)      |

| 24       | NC/CDRFP2*   | Analog Input                  | CDR Loop Filter Pin 2 — VCO Tune (ignored by TQ8105)             |

| 25       | GND          | GND                           | Core Ground                                                      |

| 26       | SVDD         | +5V                           | Output Driver Internal Positive Supply                           |

| 27       | VDD          | +5V                           | Core Positive Supply                                             |

| 28       | CDRAVDD*     | Analog +5V                    | TQ8106 CDR Analog +5V Supply                                     |

|          |              |                               | (not connected if CDR not used; ignored by TQ8105)               |

| 29       | VCC          | +5V/+3.3V                     | TTL Driver Positive Supply                                       |

| 30       | RxBC         | Tristate TTL Out              | Demultiplexer Byte Clock                                         |

| 31       | DGND         | GND                           | TTL Driver Ground                                                |

| 32       | DXSYNC       | Tristate TTL Out              | Frame Synchronization Signal                                     |

| 33       | VCC          | +5V/+3.3V                     | TTL Driver Positive Supply                                       |

| 34       | DXD0         | Tristate TTL Out              | Demultiplexer Data Bit 0 (LSB)                                   |

| 35       | DGND         | GND                           | TTL Driver Ground                                                |

| 36       | DXD1         | Tristate TTL Out              | Demultiplexer Data Bit 1                                         |

| 37       | VCC          | +5V/+3.3V                     | TTL Driver Positive Supply                                       |

| 38       | DXD2         | Tristate TTL Out              | Demultiplexer Data Bit 2                                         |

| 39       | DGND         | GND                           | TTL Driver Ground                                                |

| 40       | DXD3         | Tristate TTL Out              | Demultiplexer Data Bit 3                                         |

| 41       | VCC          | +5V/+3.3V                     | TTL Driver Positive Supply                                       |

| 42       | DXD4         | Tristate TTL Out              | Demultiplexer Data Bit 4                                         |

| 43       | DGND         | GND                           | TTL Driver Ground                                                |

| 44       | DXD5         | Tristate TTL Out              | Demultiplexer Data Bit 5                                         |

| 45       | VCC<br>DXD6  | +5V/+3.3V<br>Tristate TTL Out | TTL Driver Positive Supply Demultiplexer Data Bit 6              |

| 46       | DXD6         | GND                           | TTL Driver Ground                                                |

| 47       | DGND<br>DXD7 | Tristate TTL Out              | Demultiplexer Data Bit 7 (MSB)                                   |

| 48       | SVDD         | +5V                           | Output Driver Internal Positive Supply                           |

| 49<br>50 | VDD          | +5V<br>+5V                    | Core Positive Supply                                             |

| 50       | NC/CDRGND*   | GND                           | GND for TQ8106 to powerup CDR (ignored by TQ8105)                |

| 52       | GND          | GND                           | Core Ground                                                      |

| 53       | FRPWR        | TTL Input                     | Framer Power Control (power on when high)                        |

| 54       | 00F          | TTL Input                     | Out-of-Frame: Initiates Frame Search/Bit Alignment               |

| 55       | VCC          | +5V/+3.3V                     | TTL Driver Positive Supply                                       |

| 56       | LOS          | Tristate TTL Output           | Loss of Signal (high when > 128 bit periods without transitions) |

| 57       | DGND         | GND                           | TTL Driver Ground                                                |

|          | DUND         |                               |                                                                  |

# Table 1. Signal Descriptions (continued)

Note: \*TQ8106-specific signal

5

## PRELIMINARY DATA SHEET

# Table 1. Signal Descriptions (continued)

| Pin | Signal     | Function            | Description                                                                                 |

|-----|------------|---------------------|---------------------------------------------------------------------------------------------|

| 58  | CLRLOS     | TTL Input           | Active-high Clear LOS output                                                                |

| 59  | RLOCK      | Tristate TTL Output | Receive Clock meets lock criteria when high                                                 |

| 60  | LBM1       | TTL Input           | Loopback Mode Control (see Table 3)                                                         |

| 61  | GND        | GND                 | Core Ground                                                                                 |

| 62  | LBM0       | TTL Input           | Loopback Mode Control (see Table 3)                                                         |

| 63  | VDD        | +5V                 | Core Positive Supply                                                                        |

| 64  | NOE        | TTL Input           | TTL tristate control (active low to enable)                                                 |

| 65  | GND        | GND                 | Core Ground                                                                                 |

| 66  | NRESET     | TTL Input           | Global Reset (active low)                                                                   |

| 67  | 0C3        | TTL Input           | OC3/OC12 Mode Select                                                                        |

| 68  | MMS        | TTL Input           | Master/Slave Mode Control                                                                   |

| 69  | CKSRC2     | TTL Input           | Clock Source Select (see Table 3)                                                           |

| 70  | CKSRC1     | TTL Input           | Clock Source Select (see Table 3)                                                           |

| 71  | CKSRC0     | TTL Input           | Clock Source Select (see Table 3)                                                           |

| 72  | PH1        | TTL Input           | TxBC Phase Select (see Table 3)                                                             |

| 73  | PH0        | TTL Input           | TxBC Phase Select (see Table 3)                                                             |

| 74  | VDD        | +5V                 | Core Positive Supply                                                                        |

| 75  | SVDD       | +5V                 | Output Driver Internal Positive Supply                                                      |

| 76  | GND        | GND                 | Core Ground                                                                                 |

| 77  | MXD0       | TTL Input           | Multiplexer Data Bit 0 (LSB)                                                                |

| 78  | MXD1       | TTL Input           | Multiplexer Data Bit 1                                                                      |

| 79  | MXD2       | TTL Input           | Multiplexer Data Bit 2                                                                      |

| 80  | MXD3       | TTL Input           | Multiplexer Data Bit 3                                                                      |

| 81  | MXD4       | TTL Input           | Multiplexer Data Bit 4                                                                      |

| 82  | MXD5       | TTL Input           | Multiplexer Data Bit 5                                                                      |

| 83  | MXD6       | TTL Input           | Multiplexer Data Bit 6                                                                      |

| 84  | MXD7       | TTL Input           | Multiplexer Data Bit 7 (MSB)                                                                |

| 85  | VCC        | +5V/+3.3V           | TTL Driver Positive Supply                                                                  |

| 86  | TxBC       | Tristate TTL Out    | Transmit Byte Clock                                                                         |

| 87  | DGND       | GND                 | TTL Driver Ground                                                                           |

| 88  | SONETCK    | Tristate TTL Out    | 51.84 MHz Clock Output                                                                      |

| 89  | VCC        | +5V/+3.3V           | TTL Driver Positive Supply                                                                  |

| 90  | SDHCK      | Tristate TTL Out    | 38.88 MHz Clock Output                                                                      |

| 91  | DGND       | GND                 | TTL Driver Ground                                                                           |

| 92  | LOR        | Tristate TTL Out    | Indicates Reference Clock is Absent                                                         |

| 93  | AGND       | Analog Ground       | VCO Analog Ground                                                                           |

| 94  | FP2        | Analog Output       | Transmit PLL Loop Filter, Charge Pump Out                                                   |

| 95  | FP1        | Analog Input        | Transmit PLL Loop Filter, VCO Tune                                                          |

| 96  | AVDD       | Analog +5V          | VCO & Filter Analog VDD Supply                                                              |

| 97  | VDD        | +5V                 | Core Positive Supply                                                                        |

| 98  | REFCKT     | TTL Input           | Tx Reference Clock or Bypass Clock                                                          |

| 99  | GND        | GND                 | Core Ground                                                                                 |

| 100 | NC/NCDREN* | TTL Input           | Internal Pull-up, Low = CDR receiver clock; Float = Pin 17/18 Rx Clk<br>(ignored by TQ8105) |

Note: \*TQ8106-specific signal

TriQuint () SEMICONDUCTOR

PRELIMINARY DATA SHEET

### **Function Description**

### PLL

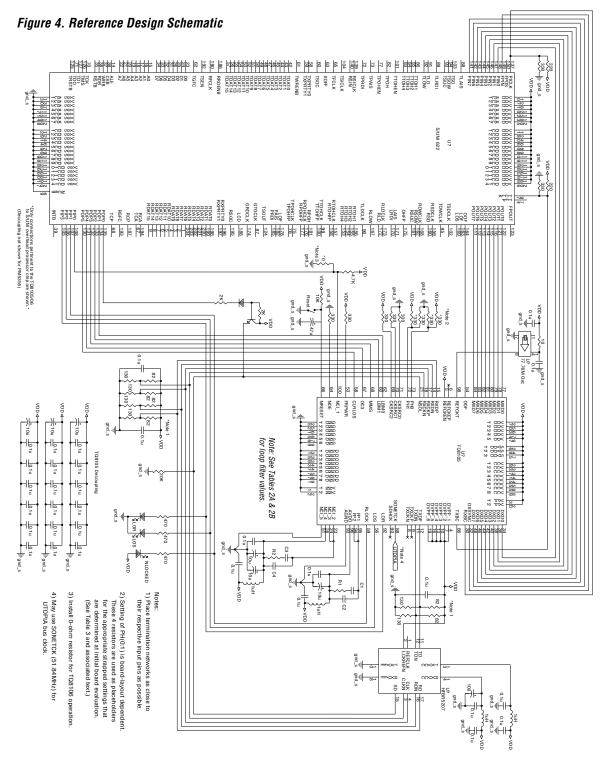

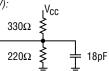

The TQ8105 & TQ8106 incorporate high-stability, lowjitter Phase Locked Loops (PLLs) running at 2488.32 MHz. The PLLs use external surface mounted loop filters consisting of an RC network as shown in the diagrams that accompany the values shown in Table 2. Analog design principles should be applied to the loop filter portions of the circuit to ensure optimal jitter generation performance. To reduce cross-coupling of clocks, both CDR clocks and analog pins should be isolated from the transmit PLL clock and analog pins. An analog ground plane under the two capacitors and the resistor, along with guards around the filter pins is excellent practice, as is a well-filtered analog supply (AVDD) and a clean analog ground (AGND). The loop filter values specified in this preliminary data sheet may change.

Reference clock sourcing can be through a variety of mechanisms. As shown in Table 3, the MMS pin determines whether the device operates in Master mode (where the PLL reference comes in on either a TTL or PECL/ECL pin), or a Slave mode (where the PLL reference is derived from the DEMUX high-speed line clock input). If the external reference clock pins are used, note that they are logical ORs and that the unused pin should be tied to (a) GND for unused REFCKT, or (b) REFCKEN should be tied to VPP for TTL reference operation. The reference clock frequency can be selected from any number of values, as indicated in Table 3. Note that the PLL may be bypassed, allowing use of an external clock reference.

Internal dividers determine the operating line rate, as shown in Table 3. The device is capable of operating at STM1/STS-3 or STM4/STS-12 rates. The transmit PLL provides high performance and compliance with ITU/ Bellcore requirements found in the first-generation TQ8101. The TQ8106 receiver's CDR can be disabled for backwards pin-compatibility with the TQ8105. For circuits not requiring the TQ8106's CDR, the CDR is disabled by floating NCDREN (pin 100). Further, the CDR section of the TQ8106 can be powered down by disconnecting the CDRGND and CDRAVDD pins, thereby reducing power consumption. If the TQ8106 CDR is not used, the CDR filter pins may be left unconnected.

The transmit PLL also provides constant-rate 38.88 MHz and 51.84 MHz TTL outputs which may be tristated. The 38.88 MHz & 51.84 MHz output may also be achieved by using high-speed receiver timing in Clock Source Mode 011 (see Table 3).

### Framer

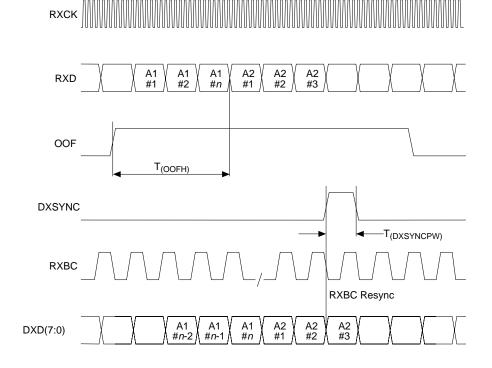

The TQ8105 and TQ8106 provide a clean interface to devices from PMC-Sierra and others. The Out-of-Frame (OOF) input is a state (level)-initiated event, rather than the edge-triggered event found on TriQuint's first-generation TQ8101 transceiver. When OOF is high, the TQ8105/TQ8106 initiates a frame search for a serial bit pattern of twelve A1s (three A1s in OC3 mode) followed by three A2s. If a match occurs, the device realigns byte boundaries and issues a logic high on the DXSYNC pin during the third A2. In the absence of OOF, the device will not realign byte boundaries, but will report any bit-level matching of twelve A1s (three A1s in OC3 mode) followed by three A2s as a DXSYNC pulse.

Framer circuit power may be switched off by a TTL low on the FRPWR pin, saving approximately 0.25W. No further DXSYNC pulses will be issued, though bit alignment is preserved in the demux. Note that the OOF and FRPWR pins may be tied together, powering the framer only when bit realignment is required (this is not recommended practice, however, due to the inrush currents that may result).

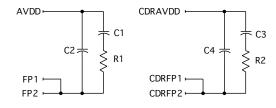

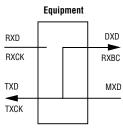

### Loopbacks

As part of the TQ8105 and TQ8106 on-chip diagnostics, four loopback modes are supported. These are selected by the dedicated pins LBM0 and LBM1, as shown in Table 3. The loopback modes are shown in Figure 5.

7

TELECOM PRODUCTS

PRELIMINARY DATA SHEET

### Functional Description (continued)

### **Enhanced Diagnostics**

The TQ8105 and TQ8106 incorporate on-chip clock diagnostics, allowing fast, efficient fault detection and isolation at the systems level.

The LOR (Loss Of Reference) output goes high when the reference clock is absent. Note that this signal is not latched and is only high when the reference clock is missing. A reference clock is required for the TQ8106 CDR to function correctly.

The NSOL (Loss-of-signal input, active low, PECL/ECL level) input allows the receiver to force zeroes onto the demux outputs. A TTL-level signal may also be used for NSOL if the resistor network, shown in the applications section of this data sheet, is used. NSOL is useful when a Loss Of Signal occurs on the receive optics, and a quieting of invalid data is desired. The receiver is clocked from the transmit clock when NSOL is active, and the output RXBC clock is obtained from the transmit portion of the TQ8105/TQ8106. This ensures compatibility with devices, such as the PMC-Sierra S/UNI-622 and STTX components, which may contain dynamic registers that lose contents if clocks are removed. NSOL forces the CDR to lock on REFCLK, except when in slave mode.

The LOS (Loss Of Signal) output goes high whenever 128-bit periods occur without transitions on the data input to the demux. CLRLOS forces LOS low.

The RLOCK (Receiver LOCK) output goes low whenever the signal on RXCK or the recovered clock drifts more than 500 ppm from the reference frequency. This output returns high whenever the frequency accuracy is within 100 ppm.

### Demux

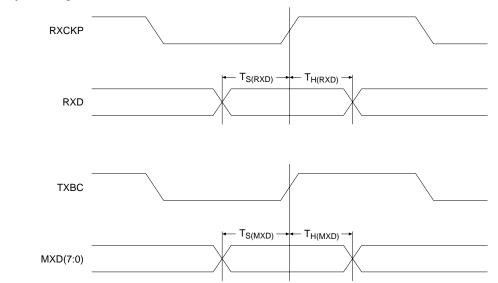

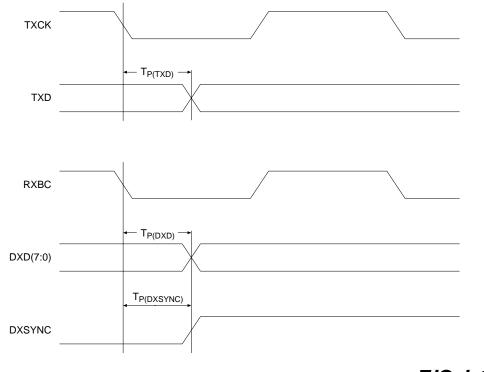

The TQ8105/TQ8106 demultiplexer converts an NRZ PECL/ECL data input, at either 155 Mb/s or 622 Mb/s, and its corresponding PECL/ECL clock into a byte-parallel

78 MHz or 19 MHz tristatable TTL data bus. The timing is shown in Figures 6 through 8. See the previous "Framer" description for bit alignment details. The TQ8106 can recover both clock and data from a NRZ data stream, whereas the TQ8105 requires NRZ data and a recovered clock.

### Mux

The TQ8105/TQ8106 multiplexer converts a 78 MHz or 19 MHz byte-wide bus to a serial NRZ PECL/ECL data stream. The bytes are clocked into the device with the TXBC byte clock output. The timing is shown in Figures 6 through 8. Note that the TXBC output can be adjusted in 90-degree phase increments to accommodate variations in interface requirements. See Table 3 for settings on the PHO and PH1 pins controlling this function. Data may also be clocked into the TQ8105/ TQ8106 by a 77 MHz reference, oscillator-clock source, provided the data is within the timing limits shown in the timing diagram labelled "Reference Clock Based Transmit Timing." The TQ8105 and TQ8106 do not require the transmit latch found on earlier TQ8101 reference designs and are backwards compatible with designs that have the latch incorporated.

### High-Speed I/O and TTL Interfaces

The TQ8105/06P will operate with either PECL or ECL operation on the high-speed I/O. With a single +5V supply, the part interfaces directly with TTL and PECL (Positive Emitter Coupled Logic). By providing an additional -5.2V supply, the device's high-speed I/O becomes ECL, instead of PECL. The TQ8105/06S is designed only for PECL high-speed I/O operation with a single +5V supply. The power supply connections for PECL and ECL are shown in Table 6B.

The TTL outputs (Vcc) may be connected to either +5V or +3.3V supplies. True TTL may be obtained with the +5V connection; clamped operation, when connected to +3.3V, ensures that maximum Voh levels do not exceed +3.3V.

PRELIMINARY DATA SHEET

# TQ8105/TQ8106 Design Notes

These design notes are provided to assist the circuit designer in achieving the highest possible performance while reducing design time. Unless noted otherwise, references to the TQ8105 apply equally to the TQ8106.

### Interfacing to PMC-Sierra Devices

The transmit timing of the TQ8105 is such that the PMC-Sierra byte outputs (POUT(0:7)) may be directly connected to the TQ8105 mux inputs (MXD(0:7)). The TQ8105 uses an Out-Of-Frame (OOF) input as a signal to reframe while high, allowing direct connection of the PM5355's OOF output to the TQ8105 OOF input. The following summarizes connectivity between the devices.

| PM5355    | TQ8105/TQ8106                          |

|-----------|----------------------------------------|

| POUT(0:7) | MXD(0:7)                               |

| PIN(0:7)  | DXD(0:7)                               |

| 00F       | 00F                                    |

| PICLK     | RXBC                                   |

| FPIN      | DXSYNC                                 |

| TCLK      | ТХВС                                   |

| POP(0:5)  | Any TQ8105 modes to be programmable    |

| PIP(0:3)  | Any TQ8105 diag outputs to be readable |

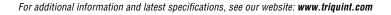

### **Reference Design**

A reference design (see Figure 4) and evaluation board are available from TriQuint. They incorporate a 1x9 or 2x9 fiber optic transceiver (with the option of clock recovery), the PM5355 PMC Sierra framer device, and a TQ8105 or TQ8106.

### **Thermal Considerations**

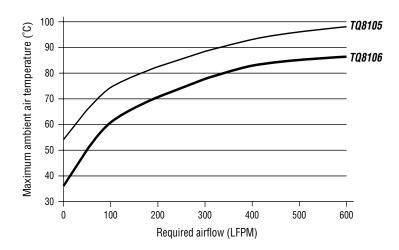

Figure 9 shows the region where the use of a heatsink is not required. For example, the TQ8105 does not require a heatsink for ambient temperatures up to  $55^{\circ}$ C in still air. An airflow of 100 LFPM raised this temperature to approximately 75°C, eliminating heatsink requirements.

In applications requiring a heatsink, a standard pin-fin heat-sink is appropriate. To attach the sink, use spring clips soldered to the board to cross and hold the heatsink. The clip holes in the board are at the corners of a 1.275" x 1.5" rectangle. Another alternative is the circular heatsink, #2288B from Thermalloy attached with their Thermattach #19686-3.

### **Power Supplies**

Good decoupling practices should be observed, with a 0.1 uF decoupling capacitor at each supply pin, ideally on the component side of the board. Keep the analog supplies (Vdd and AVdd) pristine. Proper design will isolate the supply groups using point grounding to tie supplies together (*all* grounds at a single point having multiple vias).

For the analog supply, flood copper under the loop filter on the component side of the board, tying the flood to the analog ground pin, with the point ground away from the filter and analog pin, so that any switching currents are kept away from these areas. If any switching, power-supply frequencies below 500 kHz are used in the system, use a supply filter on the analog supply pin. These practices help minimize the generation of jitter.

### **High-Speed Connections**

Connections to E/O modules (and clock reference, if used) are direct-coupled PECL and need to be terminated with decoupled 50 ohms to 3V at the receiving end of the 50 ohm transmission line. Ensure that each 50 ohm resistor (or Thevenin equivalent) has its own decoupling capacitor. Place the resistor at the end of a 50 ohm transmission line (use a controlled impedance layer), ideally with a minimal-length stub attached to either the resistor or the receiving device.

If there is no room for the resistor, use a minimallength stub to drop the signal at the receiving device pins, continue the 50 ohm transmission line to an area where the termination resistors can be placed, and terminate at the endpoint of that line. If in doubt, contact factory applications for assistance.

PRELIMINARY DATA SHEET

PRELIMINARY DATA SHEET

#### Capacitor Reference Resistor Capacitor Divide Frequency Value R1 Value C1 Value C2 (MHz) Ratio (ohms) (μ**F**) (pF) 32 19.44 1200 0.082 82 38.88 16 620 0.15 150 51.84 12 470 0.22 220 77.76 8 300 0.33 330 4 155.52\* 300 0.33 330

### Table 2A. TQ8105/TQ8106 Recommended Transmit Loop Filter Values (Preliminary)

Note: \*Internal divide by two on Reference

### Table 2B. TQ8106 Recommended CDR Loop Filter Values (Preliminary)

| Incoming<br>NRZ Data Rate<br>(Mbs) | Resistor<br>Value R2<br>(ohms) | Capacitor<br>Value C3<br>(µF) | Capacitor<br>Value C4<br>(pF) |

|------------------------------------|--------------------------------|-------------------------------|-------------------------------|

| 155.52                             | 470                            | 1.0                           | 39                            |

|                                    |                                |                               |                               |

### Figure 5. Loopback Modes

|      | NUTITIAL |      |

|------|----------|------|

| RXD  |          | DXD  |

| RXCK |          | RXBC |

| TXD  |          | MXD  |

| TXCK |          |      |

Normal

For additional information and latest specifications, see our website: www.triquint.com

11

### PRELIMINARY DATA SHEET

### Table 3. Mode Selection

| Signals                                                               | Mode                                                                                          |  |  |  |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| LBM(1:0)                                                              | Loopback: 00 = Normal, 01 = Equipment, 10 = Facility, 11 = Split                              |  |  |  |  |

| PH(1:0)                                                               | 00 = 0 degrees delay, 01 = 90 degrees delay, 10 = 180 degrees delay, 11 = 270 degrees delay   |  |  |  |  |

| MMS                                                                   | 1 = Master (use REFCKT/E as reference), 0 = Slave (use receive clock as reference)            |  |  |  |  |

| CKSRC(2:0)                                                            | Clock Source: 000 = PLL bypass                                                                |  |  |  |  |

|                                                                       | 001 = 51.84 MHz PLL reference, SONETCK & SDHCK tristate                                       |  |  |  |  |

|                                                                       | 010 = 155.52 MHz PLL reference                                                                |  |  |  |  |

| 011 = 51.84 MHz PLL reference, SONETCK=8, SDHCK derived from receiver |                                                                                               |  |  |  |  |

|                                                                       | 100 = 77.76 MHz PLL reference                                                                 |  |  |  |  |

|                                                                       | 101 = 51.84 MHz PLL reference                                                                 |  |  |  |  |

|                                                                       | 110 = 38.88 MHz PLL reference                                                                 |  |  |  |  |

|                                                                       | 111 = 19.44 MHz PLL reference                                                                 |  |  |  |  |

| 00F                                                                   | 1 = Initiate frame search, 0 = Do not permit reframing (see FRPWR pin in Table 1)             |  |  |  |  |

| NSOL                                                                  | 1 = Pass receive data, 0 = Force receive data to 0                                            |  |  |  |  |

| 0C3                                                                   | 1 = Operate at STM1/STS-3 (or PLL bypass divided by 4), 0 = Operate at STM4/STS-12/PLL bypass |  |  |  |  |

| NRESET                                                                | 1 = Normal operation, 0 = Reset internal counters                                             |  |  |  |  |

| NCDREN                                                                | 1 = TQ8105/CDR Off mode, 0 = Enable CDR (TQ8106 only)                                         |  |  |  |  |

|                                                                       |                                                                                               |  |  |  |  |

### Table 4. Absolute Maximum Ratings

12

| Parameter                        | Symbol                                                               | Level    | Minimum              | Maximum              | Unit |

|----------------------------------|----------------------------------------------------------------------|----------|----------------------|----------------------|------|

| Positive supply                  | V <sub>CC,</sub> V <sub>PP</sub> , V <sub>DD,</sub> AV <sub>DD</sub> | GND      | 7                    | V                    |      |

| Negative supply $(V_{PP} = 0 V)$ | V <sub>NN</sub>                                                      |          | -7                   | GND                  | V    |

| Output voltage                   | V <sub>0</sub>                                                       | ECL/PECL | V <sub>NN</sub> -0.5 | V <sub>PP</sub> +0.5 | V    |

| Output current                   | I <sub>0</sub>                                                       | ECL/PECL | —                    | 40                   | mA   |

| Input voltage                    | VI                                                                   | ECL/PECL | V <sub>NN</sub> -0.5 | V <sub>PP</sub> +0.5 | V    |

| Input current                    | l <sub>l</sub>                                                       | ECL/PECL | -1                   | 1                    | mA   |

| Output voltage                   | V <sub>0</sub>                                                       | TTL      | -0.5                 | V <sub>CC</sub> +0.5 | V    |

| Output current                   | l <sub>0</sub>                                                       | TTL      | —                    | 100                  | mA   |

| Input voltage                    | VI                                                                   | TTL      | -0.5                 | V <sub>CC</sub> +0.5 | V    |

| Input current                    | I <sub>I</sub>                                                       | TTL      | -1                   | 1                    | mA   |

| Biased junction temperature      | Tj                                                                   | _        | -55                  | +150                 | ° C  |

| Storage temperature              | T <sub>S</sub>                                                       | _        | -65                  | +150                 | ° C  |

PRELIMINARY DATA SHEET

| Symbol           | Function                                      | Minimum | Typical | Maximum | Unit |

|------------------|-----------------------------------------------|---------|---------|---------|------|

| I <sub>DD</sub>  | +5V supply                                    | _       | 0.323   | TBD     |      |

| I <sub>CC</sub>  | +5V / +3V supply                              | _       | 0.016   | TBD     | I    |

| I <sub>PP</sub>  | +5V / 0V supply                               | —       | 0.055   | TBD     | I    |

| I <sub>ADD</sub> | +5V supply                                    | —       | 0.018   | TBD     | I    |

| P <sub>DF</sub>  | Power dissipation, Framer on, TQ8106 CDR off  | —       | 1.9     | 2.3     | W    |

| PD               | Power dissipation, Framer off, TQ8106 CDR off | _       | 1.7     | 2.1     | W    |

| Р                | Power dissipation, Framer on, TQ8106 CDR on   |         |         | 2.75    | W    |

### Table 5. Power Consumption

# Table 6A. Recommended Operating Conditions

| Parameter                              | Symbol          | Minimum | Typical | Maximum | Unit |

|----------------------------------------|-----------------|---------|---------|---------|------|

| Positive supply                        | V <sub>PP</sub> | 4.75    | 5.0     | 5.25    | V    |

| Output driver positive supply          | V <sub>CC</sub> | 3.0     |         | 5.25    | V    |

| Negative supply (ECL mode only)        | V <sub>NN</sub> | -5.5    | -5.2    | -4.75   | V    |

| Operating case temperature (see Figure | 9)              | -40     |         | 125     | °C   |

### Table 6B. Power Supply Connections

| Pin      | +5V TTL/PECL I/O | +3.3V TTL/PECL I/0 | +5V TTL/ECL I/O | +3.3V TTL/ECL I/0 |

|----------|------------------|--------------------|-----------------|-------------------|

| VDD      | +5V              | +5V                | +5V             | +5V               |

| SVDD     | +5V              | +5V                | +5V             | +5V               |

| VCC      | +5V              | +3.3V              | +5V             | +3.3V             |

| AVDD     | Filtered +5V     | Filtered +5V       | Filtered +5V    | Filtered +5V      |

| CDRAVDD  | Filtered +5V     | Filtered +5V       | Filtered +5V    | Filtered +5V      |

| GND      | OV (ground)      | OV (ground)        | OV (ground)     | OV (ground)       |

| AGND     | OV (ground)      | OV (ground)        | OV (ground)     | OV (ground)       |

| CDRGND   | OV (ground)      | OV (ground)        | OV (ground)     | OV (ground)       |

| VPP/DVPP | +5V              | +5V                | OV (ground)     | OV (ground)       |

| VNN      | OV (ground)      | OV (ground)        | -5.2V           | -5.2V             |

PRELIMINARY DATA SHEET

### Table 7. DC Characteristics—ECL/PECL I/O

(Specifications apply over recommended operating ranges).

| Parameter              | Condition                                                                  | Symbol            | Minimum                | Nominal                                     | Maximum                | Unit |

|------------------------|----------------------------------------------------------------------------|-------------------|------------------------|---------------------------------------------|------------------------|------|

| Internal ECL reference | Single-ended inputs                                                        | V <sub>REF</sub>  | _                      | 0.26 V <sub>NN</sub> + 0.74 V <sub>PP</sub> |                        | mV   |

| Common mode voltage    | Differential inputs                                                        | V <sub>COM</sub>  | V <sub>PP</sub> – 1500 | —                                           | V <sub>PP</sub> - 1100 | mV   |

| Differential voltage   | Differential inputs                                                        | V <sub>DIFF</sub> | 200                    | —                                           | 1200                   | mV   |

| Input HIGH voltage     | V <sub>REF</sub> = 1300 mV                                                 | V <sub>IH</sub>   | V <sub>PP</sub> – 1050 | _                                           | V <sub>PP</sub> - 400  | mV   |

| Input LOW voltage      |                                                                            | V <sub>IL</sub>   | V <sub>TT</sub>        | —                                           | V <sub>PP</sub> – 1550 | mV   |

| Output HIGH voltage    | R <sub>LOAD</sub> = 50 ohms<br>to V <sub>TT</sub> = V <sub>PP</sub> - 2.0V | V <sub>OH</sub>   | V <sub>PP</sub> -1000  |                                             | V <sub>PP</sub> - 600  | mV   |

| Output LOW voltage     | R <sub>LOAD</sub> = 50 ohms<br>to V <sub>TT</sub> = V <sub>PP</sub> - 2.0V | V <sub>OL</sub>   | V <sub>TT</sub>        | _                                           | V <sub>PP</sub> - 1600 | mV   |

| Input HIGH current     | V <sub>IH(MAX)</sub>                                                       | I <sub>IH</sub>   | —                      | +130                                        | 335                    | uA   |

| Input LOW current      | V <sub>IL(MIN)</sub>                                                       | IIL               | -265                   | -130                                        | —                      | uA   |

| Output HIGH current    | (Not tested; consistent with $V_{OH}$ and $V_{OL}$ tests)                  | I <sub>OH</sub>   | 20                     | 23                                          | 30                     | mA   |

| Output LOW current     | (Not tested; consistent with $V_{OH}$ and $V_{OL}$ tests)                  | I <sub>OL</sub>   | 0                      | 5                                           | 8                      | mA   |

| Input capacitance      |                                                                            | CIN               | _                      | _                                           | TBD                    | pF   |

| Output capacitance     |                                                                            | C <sub>OUT</sub>  | _                      | _                                           | TBD                    | pF   |

| ESD breakdown rating   | (Design objective)                                                         | V <sub>ESD</sub>  | Class I                | —                                           | —                      |      |

Note:  $V_{TT} = V_{PP}$ -2.0V

### Table 8. DC Characteristics—TTL I/O

(Specifications apply over recommended operating ranges)

| Parameter            | Condition                | Symbol           | Minimum | Nominal | Maximum         | Unit |

|----------------------|--------------------------|------------------|---------|---------|-----------------|------|

| Input HIGH voltage   |                          | V <sub>IH</sub>  | 2.0     | _       | V <sub>CC</sub> | V    |

| Input LOW voltage    |                          | V <sub>IL</sub>  | 0       | _       | 0.8             | V    |

| Input HIGH current   | V <sub>IH(MAX)</sub>     | I <sub>IH</sub>  | —       | —       | 200             | uA   |

| Input LOW current    | V <sub>IL(MIN)</sub>     | I <sub>IL</sub>  | -400    | -200    |                 | uA   |

| Output HIGH voltage  | I <sub>OH</sub> = 50 mA  | V <sub>OH</sub>  | 2.4     | —       | V <sub>CC</sub> | V    |

| Output LOW voltage   | I <sub>OL</sub> = -20 mA | V <sub>OL</sub>  | 0       | _       | 0.4             | V    |

| Tristate current     |                          | I <sub>OZ</sub>  | -100    | —       | 100             | uA   |

| Input capacitance    |                          | C <sub>IN</sub>  | —       | —       | TBD             | рF   |

| Output capacitance   |                          | C <sub>OUT</sub> | _       | _       | TBD             | рF   |

| ESD breakdown rating | (Design objective)       | V <sub>ESD</sub> | Class I | _       | _               |      |

PRELIMINARY DATA SHEET

### Table 9. AC Characteristics

(Specifications apply over recommended operating ranges)

| Parameter                                                                         | Symbol                   | Minimum | Nominal | Maximum | Unit |

|-----------------------------------------------------------------------------------|--------------------------|---------|---------|---------|------|

| RXCK clock period                                                                 | T <sub>C(RXCK)</sub>     | 1.6     | —       |         | ns   |

| REFCKE clock period                                                               | T <sub>C(REFCKE)</sub>   | 1.6     | —       | _       | ns   |

| TXCK clock period                                                                 | T <sub>C(TXCK)</sub>     | 1.6     | —       |         | ns   |

| REFCKT clock period                                                               | T <sub>C(REFCKT)</sub>   | 12.8    | _       | —       | ns   |

| TXBC clock period                                                                 | T <sub>C(TXBC)</sub>     | 12.8    | —       | _       | ns   |

| RXBC clock period                                                                 | T <sub>C(RXBC)</sub>     | 12.8    | —       | _       | ns   |

| REFCKT/REFCKE clock duty cycle                                                    | T <sub>C(REF)</sub>      | 40      | _       | 60      | %    |

| REFCKT to TXBC skew <sup>2,3,5</sup>                                              | T <sub>SK(TXBC)</sub>    | TBD     |         | TBD     |      |

| SONETCK clock period                                                              | T <sub>C(SONETCK)</sub>  | _       | 19.29   | _       | ns   |

| RXBC clock duty cycle <sup>3,5</sup>                                              | T <sub>DC(RXBC)</sub>    | 40      | 50      | 60      | %    |

| TXBC clock duty cycle <sup>3,5</sup>                                              | T <sub>DC(TXBC)</sub>    | 40      | 50      | 60      | %    |

| FXCK clock duty cycle <sup>6</sup>                                                | T <sub>DC(TXCK)</sub>    | 40      | 50      | 60      | %    |

| SONETCK clock duty cycle <sup>3,5</sup>                                           | T <sub>DC(SONETCK)</sub> | 40      | 50      | 60      | %    |

| SDHCK clock duty cycle <sup>3,5</sup>                                             | T <sub>DC(SDHCK)</sub>   | 40      | 50      | 60      | %    |

| RXCK clock duty cycle <sup>6</sup>                                                | T <sub>DC(RXCK)</sub>    | 40      | 50      | 60      |      |

| High-speed rise/fall time <sup>4</sup> (> 79 MHz), Data                           | T <sub>H(R/F)</sub>      | —       | _       | 500     | ps   |

| High-speed rise/fall time <sup>4</sup> (>79 MHz), Clock                           | T <sub>H(R/F)</sub>      | _       | —       | 320     | ps   |

| _ow-speed rise/fall time <sup>1,3,5</sup> (< 79 MHz)                              | T <sub>L(R/F)</sub>      | _       | —       | 3       | ns   |

| RXD setup time to RXCK <sup>6</sup> (see Figure 6)                                | T <sub>S(RXD)</sub>      | 240     | —       | _       | ps   |

| RXD hold time to RXCK <sup>6</sup> (see Figure 6)                                 | T <sub>H(RXD)</sub>      | 20      | _       | —       | ps   |

| DOF rising edge before A1 changes to A2 <sup>7</sup><br>(see Figure 8)            | T <sub>(OOFH)</sub>      | 51.44   | _       |         | ns   |

| DXSYNC rising edge from parallel data output<br>change from A1 to A2 <sup>7</sup> | T <sub>(DSYNC)</sub>     | _       | 25.72   | —       | ns   |

| DXSYNC pulse width <sup>3,5,7</sup> (see Figure 8)                                | T <sub>(DXSYNCPW)</sub>  | 11.0    | _       | —       | ns   |

| RXBC falling edge to valid parallel data output <sup>3</sup><br>(see Figure 7)    | T <sub>P(DXD)</sub>      | 0.5     |         | 1.0     | ns   |

| MXD(0:7) setup time to $TXBC^{2,3,5}$ (see Figure 6)                              | T <sub>S(MXD)</sub>      | 600     | _       | _       | ps   |

| MXD(0:7) hold time to $TXBC^{2,3,5}$ (see Figure 6)                               | T <sub>H(MXD)</sub>      | 600     | _       | _       | ps   |

| TXCK falling edge to TXD <sup>6</sup> (see Figure 7)                              | T <sub>P(TXD)</sub>      | 200     |         | 400     | ps   |

Notes: 1. At 0.8V/2.0V levels

2. With PH(1:0) set to 00, 18pF total loading 3. TTL outputs test load ( $V_{CC} = +5V$ ):

4. 20%/80% levels

5. At 1.4V logic threshold level 6. Differential measurement

7. OC12 mode

PRELIMINARY DATA SHEET

Figure 6. Input Timing

# Figure 7. Output Timing

For additional information and latest specifications, see our website: www.triquint.com

# TQ8105/TQ8106 PRELIMINARY DATA SHEET

### Figure 8. Demultiplexer Timing

Figure 9. Required Airflow for Operation without Heatsink

### PRELIMINARY DATA SHEET

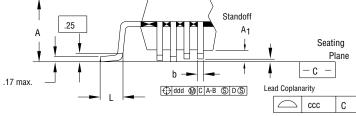

Figure 10. Mechanical Package (100 pins, 14 x 14 mm)

PRELIMINARY DATA SHEET

**Ordering Information**

| TQ8105P | SONET/SDH Transceiver, PECL/ECL I/O       |

|---------|-------------------------------------------|

| TQ8106P | SONET/SDH Transceiver w/CDR, PECL/ECL I/O |

| TQ8105S | SONET/SDH Transceiver, PECL I/O           |

| TQ8106S | SONET/SDH Transceiver w/CDR, PECL I/O     |

### **Reference Designs**

The following products are available for 14-day loan to qualified customers:

### ATM SONET/SDH Line Interface Module (SLIM)

Supports OC12c/STM-4 (622.08 Mbps) and OC-3c/STM-1 (155.52 Mbps)

- **SLIM** Documentation Package

- Functional Partition Drawing Set, including block, state machine, and timing diagrams

- Schematics

- Programmable Logic Listings

- User's Manual / Product Specification

- PCB Artwork (all layers)

- Component Placement Drawing

### Additional Information

For latest specifications, additional product information, worldwide sales and distribution locations, and information about TriQuint:

| Web: www.triquint.com | Tel: (503) 615-9000 |

|-----------------------|---------------------|

| Email: sales@tqs.com  | Fax: (503) 615-8900 |

For technical questions and additional information on specific applications:

### Email: applications@tqs.com

The information provided herein is believed to be reliable; TriQuint assumes no liability for inaccuracies or omissions. TriQuint assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. TriQuint does not authorize or warrant any TriQuint product for use in life-support devices and/or systems. Copyright © 1998 TriQuint Semiconductor, Inc. All rights reserved.

Revision 0.3.A July 1998