# Unisen

#### 5 BIT PROGRAMMABLE SYNCHRONOUS BUCK PLUS TRIPPLE LDO CONTROLLER PRELIMINARY DATASHEET

#### **FEATURES**

- Provides Single Chip Solution for Vcore, GTL+,AGP Bus, and 1.8V

- Automatic Voltage Selection for AGP slot Vddq supply

- Linear regulator controller on board for 1.8V

- Designed to meet Intel Latest VRM specification for next generation micrprocessors

- On board DAC programs the output voltage from 1.3V to 3.5V

- Linear regulator controller on board for 1.5V GTL+ supply

- Loss less Short Circuit Protection for all outputs

- Synchronous operation allows maximum efficiency

- Patented architecture allows fixed frequency operation as well as 100% duty cycle during dynamic load

- Minimum part count

- Soft Start

- High current totem pole driver for direct driving of the external Power MOSFET

- Power Good function Monitors all Outputs

- OVP Circuitry Protects the Switcher Output and generates a Fault output

#### **APPLICATIONS**

Total Power Soloution for Next Generation Intel Processor application

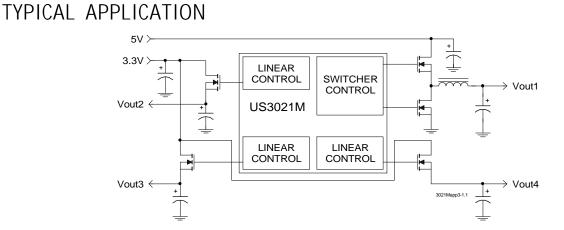

## DESCRIPTION

The US3021M controller IC is specifically designed to meet Intel specification for next generation microprocessor applications requiring multiple on board regulators. The US3021M provides a single chip controller IC for the Vcore, 3LDO controllers, one with the automatic select pin that connects to the TYPE DE-TECT pin of the AGP slot for the AGP Vddq supply, one for GTL+ and the other for the 1.8V chip set regulator as required for the next generation PC applications. The US3021M uses N ch MOSFET as pass transistor for Vout2(Vddq), Vout3(1.5V) and Vout4(1.8V). No external resistor divider is necessary for any of the regulators. The switching regulator feature a patented topology that in combination with a few external components as shown in the typical application circuit, will provide well in excess of 20A of output current for an on- board DC/DC converter while automatically providing the right output voltage via the 5 bit internal DAC .The US3021M also features, loss less current sensing for both switcher by using the Rds-on of the high side Power MOSFET as the sensing resistor, an output under voltage shutdown that detects short circuit condition for the linear outputs and latches the system off, and a Power Good window comparator that switches its open collector output low when any one of the outputs is outside of a pre programmed window.

#### PACKAGE ORDER INFORMATION

| <br>    |           |                        |

|---------|-----------|------------------------|

| Ta (°C) | Device    | Package                |

| 0 TO 70 | US3021MCW | 28 pin Plastic SOIC WB |

# US3021M

#### ABSOLUTE MAXIMUM RATINGS

| V5 supply Voltage    |                      | 7V           |

|----------------------|----------------------|--------------|

| V12 Supply Voltage   |                      | 20V          |

| Storage Temperature  | e Range              | -65 TO 150°C |

| Operating Junction T | emperature Range 0 T | O 125°C      |

# PACKAGE INFORMATION

| 28 PIN WIDE I                                                                                                                                         | BODY PLAS  | STIC SOIC (W)                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drive2 1<br>Fix 2<br>VID4 3<br>VID3 4<br>VID2 5<br>VID1 6<br>VID0 7<br>PGood 8<br>SD 9<br>Vsen2 10<br>Select 11<br>SS 12<br>Fault / Rt 13<br>Vsen4 14 | JA =80°C/W | 28 V12<br>27 UGate<br>26 Phase<br>25 LGate<br>24 PGnd<br>23 OCSet<br>20 V5<br>19 Vsen1<br>20 V5<br>19 Vsen3<br>18 Drive3<br>17 Gnd<br>16 NC<br>15 Drive4 |

|                                                                                                                                                       |            |                                                                                                                                                          |

### ELECTRICAL SPECIFICATIONS

Unless otherwise specified ,these specifications apply over ,V12 = 12V, V5 = 5V and Ta=0 to 70°C. Typical values refer to Ta = $25^{\circ}$ C. Low duty cycle pulse testing are used which keeps junction and case temperatures equal to the ambient temperature.

| PARAMETER                   | SYM      | <b>TEST CONDITION</b> | MIN    | TYP | MAX    | UNITS |

|-----------------------------|----------|-----------------------|--------|-----|--------|-------|

| Supply UVLO Section         |          |                       |        |     |        |       |

| UVLO Threshold-12V          |          | Supply ramping up     |        | 10  |        | V     |

| UVLO Hysterises-12V         |          |                       |        | 0.6 |        | V     |

| UVLO Threshold-5V           |          | Supply ramping up     |        | 4.4 |        | V     |

| UVLO Hysterises-5V          |          |                       |        | 0.3 |        | V     |

| Supply Current              |          |                       |        |     |        |       |

| Operating Supply Current    |          |                       |        |     |        |       |

|                             |          | V12                   |        | 6   |        | mA    |

|                             |          | V5                    |        | 30  |        |       |

| Switching Controllers; Vco  | re (Vser | n 1) and AGP (Vsen 2) | -      |     | -      |       |

| VID Section (Vcore only)    |          |                       |        |     |        |       |

| DAC output voltage (note 1) |          |                       | 0.99Vs | Vs  | 1.01Vs | V     |

| DAC Output Line Regulation  |          |                       |        | 0.1 |        | %     |

| DAC Output Temp Variation   |          |                       |        | 0.5 |        | %     |

| VID Input LO                |          |                       |        |     | 0.8    | V     |

| VID Input HI                |          |                       | 2      | _   |        | V     |

| VID input internal pull-up  |          |                       |        |     |        |       |

| resistor to V5              |          |                       |        | 27  |        | kΩ    |

| Vsen2 Voltage               |          | Select<0.8V           |        | 1.5 |        | V     |

| -                           |          | Select>2V             |        | 3.3 |        | V     |

|                                      |     |                                       | T  |        |     | 1   |

|--------------------------------------|-----|---------------------------------------|----|--------|-----|-----|

| Error Comparator Section             |     |                                       |    |        | -   |     |

| Input bias current                   |     |                                       |    |        | 2   | uA  |

| Input Offset Voltage                 |     |                                       | -2 |        | +2  | mV  |

| Delay to Output                      |     | Vdiff=10mV                            |    |        | 100 | nS  |

| Current Limit Section                |     |                                       |    |        |     |     |

| C.S Threshold Set Current            |     |                                       |    | 200    |     | uA  |

| C.S Comp Offset Voltage              |     |                                       | -5 |        | +5  | mV  |

| Hiccup Duty Cycle                    |     | Css=0.1 uF                            |    | 10     |     | %   |

| Output Drivers Section               |     |                                       |    |        |     |     |

| Rise Time                            |     | CL=3000pF                             |    | 70     |     | nS  |

| Fall Time                            |     | CL=3000pF                             |    | 70     |     | nS  |

| Dead band Time Between               |     |                                       |    |        |     |     |

| High side and Synch Drive            |     |                                       |    |        |     |     |

| (Vcore Switcher Only)                |     | CL=3000pF                             |    | 200    |     | nS  |

| <b>Oscillator Section (internal)</b> |     | · · · · · · · · · · · · · · · · · · · |    |        |     |     |

| Osc Frequency                        |     | Rt=Open                               |    | 217    |     | Khz |

| 1.8V Regulator (Vsen 4)              |     |                                       |    |        |     |     |

| Vsense Voltage                       | Vo4 | Ta=25, Drive4 = Vsen4                 |    | 1.800  |     | V   |

| Vsense Voltage                       |     |                                       |    | 1.800  |     | V   |

| Input bias current                   |     |                                       |    |        | 2   | uA  |

| Output Drive Current                 |     | Vaux-Vdrive>0.6V                      | 50 |        |     | mA  |

|                                      |     |                                       |    |        |     |     |

| 1.5V Regulator (Vsen 3)              |     |                                       |    |        |     |     |

| Vsense Voltage                       | Vo3 | Ta=25, Drive3 = Vsen3                 |    | 1.500  |     | V   |

| Vsense Voltage                       |     |                                       |    | 1.500  |     | V   |

| Input bias current                   |     |                                       |    |        | 2   | uA  |

| Output Drive Current                 |     | Vaux-Vdrive>0.6V                      | 50 |        |     | mA  |

| -                                    |     |                                       |    |        |     |     |

| Power Good Section                   |     |                                       |    |        |     |     |

| Vsen1 UV lower trip point            |     | Vsen1 ramping down                    |    | 0.90Vs |     | V   |

| Vsen1 UV upper trip point            |     | Vsen1 ramping up                      |    | 0.92Vs |     | V   |

| Vsen1 UV Hysterises                  |     |                                       |    | .02Vs  |     | V   |

| Vsen1 HV upper trip point            |     | Vsen1 ramping up                      |    | 1.10Vs |     | V   |

| Vsen1 HV lower trip point            |     | Vsen1 ramping down                    |    | 1.08Vs |     | V   |

| Vsen1 HV Hysterises                  |     |                                       |    | .02Vs  |     | V   |

| Vsen2 trip point                     |     | Select<0.8V                           |    | 1.100  |     | V   |

|                                      |     | Select>2V                             |    | 2.560  |     | V   |

| Vsen4 trip point                     |     | Fix=GND                               |    | 0.920  |     | V   |

|                                      |     | Fix=Open                              |    | 1.320  |     | V   |

| Vsen3 trip point                     |     | Fix=GND                               |    | 0.920  |     | V   |

|                                      |     | Fix=Open                              |    | 1.140  |     | V   |

| Power Good Output LO                 |     | RL=3mA                                |    | 0.4    |     | V   |

| Power Good Output HI                 |     | RL=5K pull up to 5V                   |    | 4.8    |     | V   |

| Fault (Overvoltage) Section          |     |                                       | 1  |        |     | 1   |

| Core O.V. upper trip point           |     | Vsen1 ramping up                      |    | 1.17Vs |     | V   |

| Core O.V. lower trip point           |     | Vsen1 ramping down                    | 1  | 1.17Vs |     | V   |

| FAULT Output HI                      |     | lo=3mA                                |    | 10     |     | V   |

| Soft Start Section                   |     |                                       |    |        |     |     |

| Soft Start Current                   |     | OCset=0V, Phase=5V                    |    | 20     |     | uA  |

| Son Stan Sunen                       |     | 00361-0V, FH036-0V                    | 1  | 20     |     | ųл  |

| D4 | D3 | D2 | D1 | D0 | Vs   |

|----|----|----|----|----|------|

| 0  | 1  | 1  | 1  | 1  | 1.30 |

| 0  | 1  | 1  | 1  | 0  | 1.35 |

| 0  | 1  | 1  | 0  | 1  | 1.40 |

| 0  | 1  | 1  | 0  | 0  | 1.45 |

| 0  | 1  | 0  | 1  | 1  | 1.50 |

| 0  | 1  | 0  | 1  | 0  | 1.55 |

| 0  | 1  | 0  | 0  | 1  | 1.60 |

| 0  | 1  | 0  | 0  | 0  | 1.65 |

| 0  | 0  | 1  | 1  | 1  | 1.70 |

| 0  | 0  | 1  | 1  | 0  | 1.75 |

| 0  | 0  | 1  | 0  | 1  | 1.80 |

| 0  | 0  | 1  | 0  | 0  | 1.85 |

| 0  | 0  | 0  | 1  | 1  | 1.90 |

| 0  | 0  | 0  | 1  | 0  | 1.95 |

| 0  | 0  | 0  | 0  | 1  | 2.00 |

| 0  | 0  | 0  | 0  | 0  | 2.05 |

Note 1: Vs refers to the set point voltage given in Table 1.

| D4 | D3 | D2 | D1 | D0 | Vs  |

|----|----|----|----|----|-----|

| 1  | 1  | 1  | 1  | 1  | 2.0 |

| 1  | 1  | 1  | 1  | 0  | 2.1 |

| 1  | 1  | 1  | 0  | 1  | 2.2 |

| 1  | 1  | 1  | 0  | 0  | 2.3 |

| 1  | 1  | 0  | 1  | 1  | 2.4 |

| 1  | 1  | 0  | 1  | 0  | 2.5 |

| 1  | 1  | 0  | 0  | 1  | 2.6 |

| 1  | 1  | 0  | 0  | 0  | 2.7 |

| 1  | 0  | 1  | 1  | 1  | 2.8 |

| 1  | 0  | 1  | 1  | 0  | 2.9 |

| 1  | 0  | 1  | 0  | 1  | 3.0 |

| 1  | 0  | 1  | 0  | 0  | 3.1 |

| 1  | 0  | 0  | 1  | 1  | 3.2 |

| 1  | 0  | 0  | 1  | 0  | 3.3 |

| 1  | 0  | 0  | 0  | 1  | 3.4 |

| 1  | 0  | 0  | 0  | 0  | 3.5 |

Table 1 - Set point voltage vs. VID codes

# PIN DESCRIPTIONS

| PIN# | PIN SYMBOL | Pin Description                                                                                                                                                                      |

|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | VID0       | LSB input to the DAC that programs the output voltage. This pin is TTL compatible that realizes a logic "1" as either HI or Open. When left open, his pin is pulled up internally by |

|      |            | a $27k\Omega$ resistor to 5V supply.                                                                                                                                                 |

| 6    | VID1       | Input to the DAC that programs the output voltage. This pin is TTL compatible that real-                                                                                             |

|      |            | izes a logic "1" as either HI or Open. When left open, his pin is pulled up internally by a $27k\Omega$ resistor to 5V supply.                                                       |

| 5    | VID2       | Input to the DAC that programs the output voltage. This pin is TTL compatible that real-                                                                                             |

|      |            | izes a logic "1" as either HI or Open. When left open, his pin is pulled up internally by a                                                                                          |

|      |            | $27k\Omega$ resistor to 5V supply.                                                                                                                                                   |

| 4    | VID3       | MSB input to the DAC that programs the output voltage. This pin is TTL compatible that                                                                                               |

|      |            | realizes a logic "1" as either HI or Open. When left open, his pin is pulled up internally by a $27k\Omega$ resistor to 5V supply.                                                   |

| 3    | VID4       | This pin selects a range of output voltages for the DAC.When in the LOW state the range                                                                                              |

| 5    | VID4       | is 1.3V to 2.05V and when it switches to HI state the range is 2.0V to 3.5V. This pin is                                                                                             |

|      |            | TTL compatible that realizes a logic "1" as either HI or Open. When left open, his pin is                                                                                            |

|      |            | pulled up internally by a $27k\Omega$ resistor to 5V supply.                                                                                                                         |

| 8    | PGOOD      | This pin is an open collector output that switches LO when any of the outputs are outside                                                                                            |

|      |            | of the specified under voltage trip point. It also switches low when Vsen1 pin is more than 10% above the DAC voltage setting.                                                       |

| 21   | FB         | This pin provides the feedback for the synchronous switching regulator. Typically this pin                                                                                           |

|      | 1.0        | can be connected directly to the output of the switching regulator. However, a resistor                                                                                              |

|      |            | divider is recommended to be connected from this pin to vout1 and GND to adjust the                                                                                                  |

|      |            | output voltage for any drop in the output voltage that is caused by the trace resistance.                                                                                            |

|      |            | The value of the resistor connected from Vout1 to FB1 must be less than $1000\Omega$ .                                                                                               |

| 1    | Drive2     | This pin controls the gate of an external MOSFET for the AGP linear regulator.                                                                                                       |

| 9    | SD         | This pin provides shutdown for all the regulatos. A TTL compatible, logic level high applied                                                                                         |

|      |            | to this pin disables all the outputs and discharges the soft start capacitor. The SD signal                                                                                          |

|      |            | turns off the synchronous allowing body diode to conduct and discharge the output cap.                                                                                               |

| PIN# | PIN SYMBOL | Pin Description                                                                                                                                                                  |

|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22   | Vsen1      | This pin is internally connected to the undervoltage and overvoltage comparators sensing                                                                                         |

|      |            | the Vcore status. It must be connected directly to the Vcore supply.                                                                                                             |

| 10   | Vsen2      | This pin provides the feedback for the AGP linear regulator. The Select pin when con-                                                                                            |

|      |            | nected to the "Type Detect" pin of the AGP slot automatically selects the right voltage for                                                                                      |

|      |            | the AGP Vddq.                                                                                                                                                                    |

| 15   | Drive4     | This pin controls the gate of an external MOSFET for the 1.8V chip set linear regulator.                                                                                         |

| 23   | OCSET      | This pin is connected to the Drain of the power MOSFET of the Core supply and it                                                                                                 |

|      |            | provides the positive sensing for the internal current sensing circuitry. An external resis-                                                                                     |

|      |            | tor programs the C.S threshold depending on the Rds of the power MOSFET. An external                                                                                             |

|      |            | capacitor is placed in parallel with the programming resistor to provide high frequency                                                                                          |

|      |            | noise filtering.                                                                                                                                                                 |

| 26   | PHASE      | This pin is connected to the Source of the power MOSFET for the Core supply and it                                                                                               |

|      |            | provides the negative sensing for the internal current sensing circuitry.                                                                                                        |

| 12   | SS         | This pin provides the soft start for all the regulators. An internal current source charges                                                                                      |

|      |            | an external capacitor that is connected from this pin to GND which ramps up the outputs                                                                                          |

|      |            | of the regulators, preventing the outputs from overshooting as well as limiting the input                                                                                        |

|      |            | current. The second function of the Soft Start cap is to provide long off time (HICCUP) for                                                                                      |

| 40   |            | the synchronous MOSFET during current limiting.                                                                                                                                  |

| 13   | FAULT/Rt   | This pin has dual function. It acts as an output of the OVP circuitry or it can be used to                                                                                       |

|      |            | program the frequency using an external resistor. When used as a fault detector, if any                                                                                          |

|      |            | of the switcher outputs exceed the OVP trip point, the FAULT pin switches to 12V and                                                                                             |

|      |            | the soft start cap is discharged. If the FAULT pin is to be connected to any external circuitry, it needs to be buffered.                                                        |

| 18   | Drive3     | This pin controls the gate of an external transistor for the 1.5V GTL+ linear regulator.                                                                                         |

| 19   | Vsen3      | This pin provides the feedback for the linear regulator that its output drive is Drive3.                                                                                         |

| 16   | NC         | This pin is not connected internally.                                                                                                                                            |

| 10   |            |                                                                                                                                                                                  |

|      |            |                                                                                                                                                                                  |

| 14   | Vsen4      | This pin provides the feedback for the linear regulator that its output drive is Drive4.                                                                                         |

| 17   | GND        | This pin serves as the ground pin and must be connected directly to the ground plane.                                                                                            |

| 24   | PGND       | This pin serves as the Power ground pin and must be connected directly to the GND                                                                                                |

|      |            | plane close to the source of the synchronous MOSFET. A high frequency capacitor                                                                                                  |

|      |            | (typically 1 uF) must be connected from V12 pin to this pin for noise free operation.                                                                                            |

| 25   | LGATE      | Output driver for the synchronous power MOSFET for the Core supply.                                                                                                              |

| 27   | UGATE      | Output driver for the high side power MOSFET for the Core supply.                                                                                                                |

| 28   | V12        | This pin is connected to the 12 V supply and serves as the power Vcc pin for the output drivers. A high frequency expecter (typically 1 uE) must be placed close to this pin and |

|      |            | drivers. A high frequency capacitor (typically 1 uF) must be placed close to this pin and PGND pin and be connected directly from this pin to the GND plane for the noise free   |

|      |            | operation.                                                                                                                                                                       |

| 20   | V5         | 5V supply voltage. A high frequency capacitor (0.1 to 1 uF) must be placed close to this                                                                                         |

| 20   | V5         | pin and connected from this pin to the GND plane for noise free operation.                                                                                                       |

| 11   | Select     | This pin provides automatic voltage selection for the AGP switching regulator. When it is                                                                                        |

|      | 001001     | pulled LO, the voltage is 1.5V and when left open or pulled to HI, the voltage is 3.3V.                                                                                          |

| 2    |            | Leaving this pin open provides fixed output voltages of the 1.5V and 1.8V for the #3 and #4                                                                                      |

| -    |            | linear regulators. When this pin is grounded the reference to the linear regulators are set                                                                                      |

|      |            | to 1.26V and therefore the output of the regulators can be programmed to any voltages                                                                                            |

|      |            | above the 1.26V using; Vout=1.26*(1+Rtop/Rbot)                                                                                                                                   |

|      |            | Where:                                                                                                                                                                           |

|      |            | Rtop=Top resistor connected from the output to the Vsense pin                                                                                                                    |

|      |            | Rbot=Bottom resistor connected from the Vsense pin to ground.                                                                                                                    |

|      |            |                                                                                                                                                                                  |

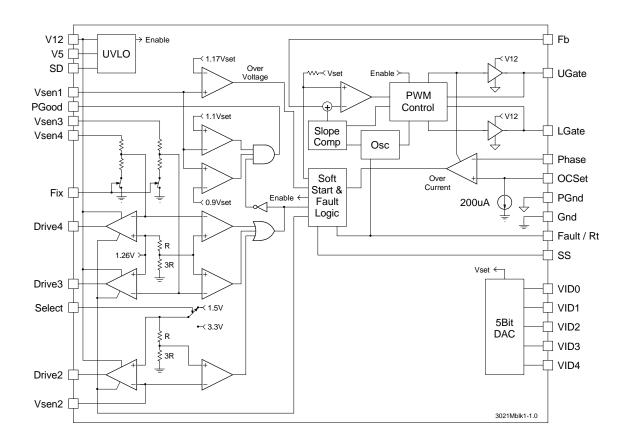

BLOCK DIAGRAM

Figure 1 - Simplified block diagram of the US3021M.

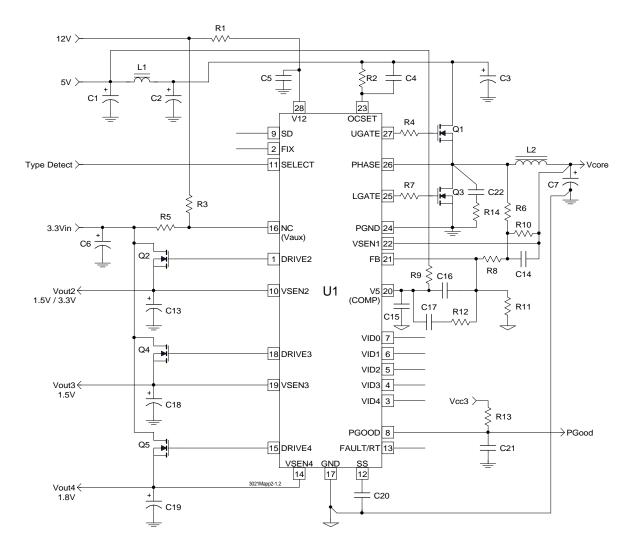

# TYPICAL APPLICATION (Dual Layout with HIP6021)

Figure 2 - Typical application of US3021M in a dual layout with HIP6021 for an on board DC-DC converter providing power for the Vcore, GTL+, 1.8V chip set supply as well as auto select AGP supply for the next generation PC applications.

| Part#   | R3 | R5 | R9 | R12 | C15 | C16 | C17 |

|---------|----|----|----|-----|-----|-----|-----|

| HIP6021 | 0  | S  | 0  | V   | 0   | V   | V   |

| US3021M | S  | 0  | S  | 0   | V   | 0   | 0   |

S - Short O - Open V - See Unisem or Harris parts list for the value.

Table 2 - Dual layout component table

#### US3021M Application Parts List Dual Layout with HIP6021

| Ref Desig | Description             | Qty | Part #                              | Manuf       |

|-----------|-------------------------|-----|-------------------------------------|-------------|

| Q1        | MOSFET                  | 1   | IRL3103S, TO263 package             | IR          |

| Q2        | MOSFET                  | 1   | IRLR3103, TO252 package             | IR          |

| Q3        | MOSFET with Schottky    | 1   | IRL3103D1S, TO263 package           | IR          |

| Q4,5      | MOSFET                  | 2   | IRLR024, TO252 package              | IR          |

| L1        | Inductor                | 1   | L=1uH, 5052 core with 4 turns of    | Micro Metal |

|           |                         |     | 1.0mm wire                          |             |

| L2        | Inductor                | 1   | L=2.7uH, 5052B core with 7 turns of | Micro Metal |

|           |                         |     | 1.2mm wire                          |             |

| C1        | Capacitor, Electrolytic | 1   | 10MV470GX, 470uF,10V                | Sanyo       |

| C2,3      | Capacitor, Electrolytic | 2   | 10MV1200GX, 1200uF,10V              | Sanyo       |

| C4        | Capacitor, Ceramic      | 1   | 220pF, 0603                         |             |

| C5        | Capacitor, Ceramic      | 1   | 1uF, 0805                           |             |

| C6,18     | Capacitor, Electrolytic | 2   | 6MV1000GX, 1000uF,6.3V              | Sanyo       |

| C7        | Capacitor, Electrolytic | 6   | 6MV1500GX, 1500uF,6.3V,             | Sanyo       |

| C13,19    | Capacitor, Electrolytic | 1   | 6MV1500GX, 1500uF,6.3V,             | Sanyo       |

| C14,15    | Capacitor, Ceramic      | 2   | 1uF, 0603                           |             |

| C16,17    | Capacitor, Ceramic      | 2   | See Table 2, dual layout component  |             |

|           |                         |     | 0603 * 2                            |             |

| C20,21    | Capacitor, Ceramic      | 2   | 0.1uF, 0603                         |             |

| C22       | Capacitor, Ceramic      | 1   | 1000pF, 0603                        |             |

| R1        | Resistor                | 1   | 10Ω, 5%, 0603                       |             |

| R2        | Resistor                | 1   | 3.3kΩ, 5%, 0603                     |             |

| R3,5,12   | Resistor                | 3   | See Table 2, dual layout component  |             |

|           |                         |     | 0603 * 3                            |             |

| R4,7,14   | Resistor                | 3   | 4.7Ω, 5%, 1206                      |             |

| R6,8,10   | Resistor                | 3   | 2.2kΩ, 1%, 0603                     |             |

| R9        | Resistor                | 1   | 0Ω, 0603                            |             |

| R11       | Resistor                | 1   | 220kΩ, 1%, 0603                     |             |

| R13       | Resistor                | 1   | 10kΩ, 5%, 0603                      |             |