# **FEATURES**

Preliminary Rev. 0.91

- PC100 compliant functionality and performance.

- JEDEC standard 3.3 V ± 10% power supply.

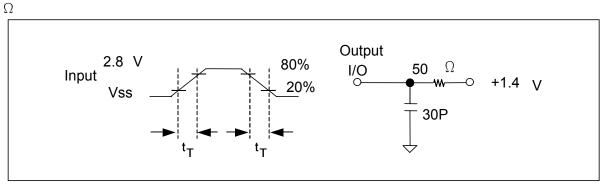

- LVTTL compatible inputs and outputs.

- All inputs are sampled on positive edge of system clock.

- Dual Banks for hidden row access/precharge.

- Internal pipeline operation, column addresses can be changed every cycle.

- DQM for masking.

- MRS cycle with address key programmability

- CAS latency (2.3)

- Burst Length (1, 2, 4, 8 or full page)

- Burst Type ( Sequential & Interleave )

- Auto Precharge and Auto Refresh modes.

- Self Refresh Mode.

- 64ms, 4096 cycle refresh (15.6 us/row)

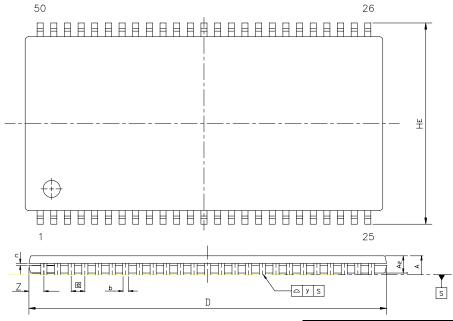

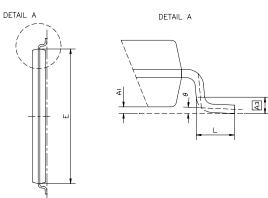

- 50-pin 400 mil plastic TSOP (type II) package.

# **GENERAL DESCRIPTION**

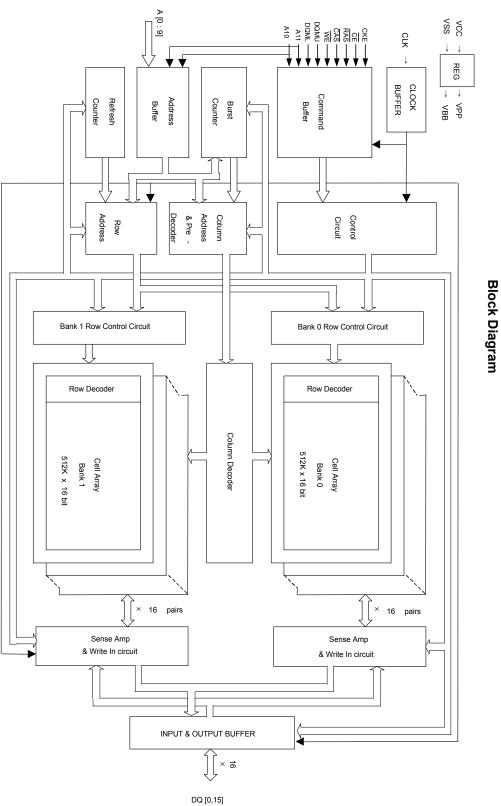

The UT52L1616 is a high-speed CMOS dynamic random-access memory containing 16,777,216 bits. It is internally configured as a dual memory array (512K x 16) with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the two internal banks is organized with 2,048 rows and with either 256 columns by 16 bits.

Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVATE command which will then be followed by a READ or WRITE command. The address bits registered coincident with the ACTIVATE command are used to select the bank and row to be accessed (A11 selects the bank, A0-10 selects the row). The address bits coincident with the READ or WRITE command are used to select the starting column location for the burst access.

The UT52L1616 uses an internal pipelined architecture to achieve high-speed operation. This architecture is compatible with the 2n rule of prefetch architectures, but it also allows the column address to be changed on every clock cycle to achieve a high speed, fully random access. Precharging one bank while accessing the alternate bank will hide the precharge cycles and provides seamless high-speed random access operation. The UT52L1616 is designed to comply with the Intel PC (66MHz) and Intel PC/100 (100MHz) specifications.

The UT52L1616 is designed to operate in 3.3V, low-power memory systems. An AUTO REFRESH mode is provided along with a power saving Power-Down mode. All inputs and outputs are LVTTL-compatible.

SDRAMs offer substantial advances in DRAM operating performance, including the ability to synchronously burst data at a high data rate with automatic column-address generation, the ability to interleave between internal banks in order to hide precharge time, and the capability to randomly change column addresses on each clock cycle during a burst access.

# PRODUCT FAMILY

| Part NO.       | Max Freq. | CL | tAC   | Organization         | Interface | Package                  |  |

|----------------|-----------|----|-------|----------------------|-----------|--------------------------|--|

| UT52L1616MC-7  | 143MHZ    | 3  | 5.5ns |                      |           | 400 mil E0nin            |  |

| UT52L1616MC-8  | 125MHZ    | 3  | 6ns   | 2 banks×512K bits×16 | LVTTL     | 400 mil 50pin<br>TSOP II |  |

| UT52L1616MC-10 | 100MHZ    | 3  | 7ns   |                      |           | 13011                    |  |

UTRON TECHNOLOGY INC. P90004

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C.

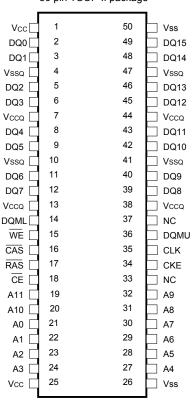

# **PIN ASSIGNMENT**

# UT52L1616 50 pin TSOP II package

# **PIN DESCRIPTION**

| Pin name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| A0 to A11   | Address input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|             | Row address     A0 to A10     A0 to A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|             | Column address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| D00 t- D045 | Bank select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select address A11  Pate in a transfer of the select addre |  |  |  |  |  |  |

| DQ0 to DQ15 | Data-input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| CE          | Chip select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| CAS         | Column address strobe command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| RAS         | Row address strobe command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| WE          | Write enable command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| DQMU        | Upper byte input/output mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| DQML        | Lower byte input/output mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| CLK         | Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| CKE         | Clock enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| $V_{CC}$    | Power for internal circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Vss         | Ground for internal circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| VccQ        | Power for I/O circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| VssQ        | Ground for I/O circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| NC          | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

# **FUNCTION BLOCK DIAGRAM**

# PIN FUNCTIONS

**CLK** (input pin): CLK is the master clock input to this pin. The other input signals are referred at CLK rising edge.

CE (input pin): When CE is Low, the command input cycle becomes valid. When CE is High, all inputs are ignored. However, internal operations (bank active, burst operations, etc.) are held.

RAS, CAS, and WE (input pins): Although these pin names are the same as those of conventional DRAMs, they function in a different way. These pins define operation commands (read, write, etc.) depending on the combination of their voltage levels. For details, refer to the command operation section.

A0 to A10 (input pins): Row address (AX0 to AX10) is determined by A0 to A10 level at the bank active command cycle CLK rising edge. Column address (AY0 to AY7) is determined by A0 to A7 level at the read or write command cycle CLK rising edge. And this column address becomes burst access start address. A10 defines the precharge mode. When A10 = High at the precharge command cycle, both banks are precharged. But when A10 = Low at the precharge command cycle, only the bank that is selected by A11 (BS) is precharged.

A11 (input pin): A11 is a bank select signal (BS). The memory array of the UT52L1616 is divided into bank 0 and bank 1, both which contain 512 K x 16 bits. If A11 is Low, bank 0 is selected, and if A11 is High, bank 1 is selected.

CKE (input pin): This pin determines whether or not the next CLK is valid. If CKE is High, the next CLK rising edge is valid. If CKE is Low, the next CLK rising edge is invalid. This pin is used for power down and clock suspend modes.

**DQMU/DQML** (input pins): DQMU controls upper byte and DQML controls lower byte input/output buffers.

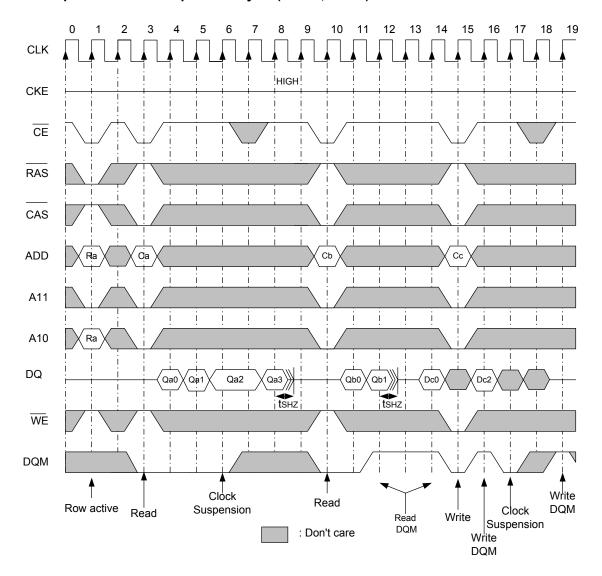

Read operation: If DQMU/DQML is High, the output buffer becomes High-Z. If the DQMU/DQML is Low, the output buffer becomes Low-Z.

Write operation: If DQMU/DQML is High, the previous data is held (the new data is not written).If DQMU/DQML is Low, the data is written.

DQ0 to DQ15 (I/O pins): Data is input to and output from these pins. These pins are the same as those of a conventional DRAM.

Vcc and VccQ (power supply pins): 3.3V is applied. (Vcc is for the internal circuit and VccQ is for the output buffer.)

Vss and VssQ (power supply pins): Ground is connected. (Vss is for the internal circuit and VssQ is for the output buffer.)

LITRON TECHNOLOGY INC.

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C.

# **COMMAND OPERATION**

# **Command Truth Table**

The synchronous DRAM recognizes the following commands specified by the  $\overline{CE}$ ,  $\overline{CAS}$ ,  $\overline{RAS}$ ,  $\overline{WE}$  and address pins.

| Function                  | Symbol   | CKE n-1 | CKe n | CE | RAS | CAS | WE | A11 | A10 | A0 to A9 |

|---------------------------|----------|---------|-------|----|-----|-----|----|-----|-----|----------|

| Ignore command            | DESL     | Н       | Х     | Н  | Х   | Х   | Х  | Х   | Х   | Х        |

| Mode register set         | MRS      | Н       | Х     | L  | L   | L   | L  | V   | V   | V        |

| Refresh                   | REF/SELF | Н       | V     | L  | L   | L   | Н  | Х   | Х   | Х        |

| Precharge select bank     | PRE      | Н       | Х     | L  | L   | Н   | L  | V   | L   | Х        |

| Precharge all bank        | PALL     | Н       | Х     | L  | L   | Н   | L  | Х   | Н   | Х        |

| Bank active               | ACT      | Н       | Х     | L  | L   | Н   | Н  | V   | V   | V        |

| Column address and write  | WRIT     | Н       | Х     | L  | Н   | L   | L  | V   | L   | V        |

| command                   |          |         |       |    |     |     |    |     |     |          |

| Write with auto-precharge | WRITA    | Н       | Х     | L  | Н   | L   | L  | ٧   | Н   | V        |

| Column address and read   | READ     | Н       | Х     | L  | Н   | L   | Н  | V   | L   | <b>V</b> |

| command                   |          |         |       |    |     |     |    |     |     |          |

| Read with auto-precharge  | READA    | Н       | Х     | L  | Н   | L   | Τ  | ٧   | Н   | V        |

| Burst stop in full page   | BST      | Н       | Х     | Ĺ  | Н   | Н   | Ĺ  | Х   | Х   | Х        |

| No operation              | NOP      | Н       | Х     | Ĺ  | Н   | Н   | Τ  | Х   | Х   | Х        |

Note: H: V<sub>IH</sub>. L: V<sub>IL</sub>. x: V<sub>IH</sub> or V<sub>IL</sub>. V: Valid address input.

**Ignore Command [DESL]:** When this command is set ( $\overline{CE}$  is High), the synchronous DRAM ignore command input at the clock. However, the internal status is held.

**Mode register set [MRS]:** Synchronous DRAM has a mode register that defines how it operates. The mode register is specified by the address pins (A0 to A11) at the mode register set cycle. For details, refer to the mode register configuration. After power on, the contents of the mode register are undefined, execute the mode register set command to set up the mode register.

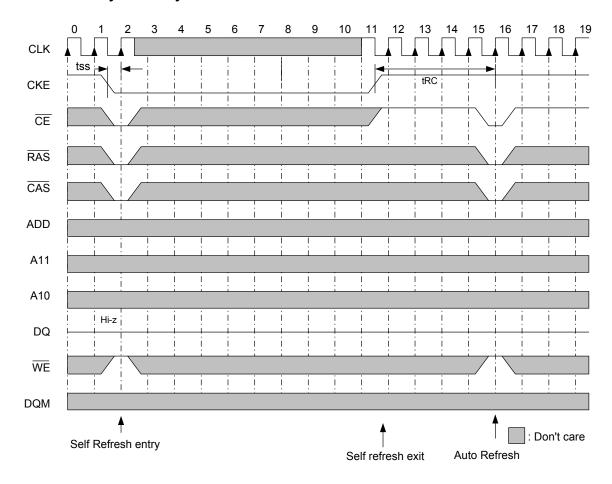

**Refresh [REF/SELF]:** This command starts the refresh operation. There are two types of refresh operation, the one is auto refresh, and the other is self refresh. For details, refer to the CKE truth table section.

**Precharge selected bank [PRE]:** This command starts precharge operation for the bank selected by A11. If A11 is Low, bank 0 is selected. If A11 is High, bank 1 is selected.

**Precharge all banks [PALL]:** This command starts a precharge operation for all banks.

**Row address strobe and bank activate [ACT]:** This command activates the bank that is selected by A11 (BS) and determines the row address (AX0 to AX10). When A11 is Low, bank 0 is activated. When A11 is High, bank 1 is activated.

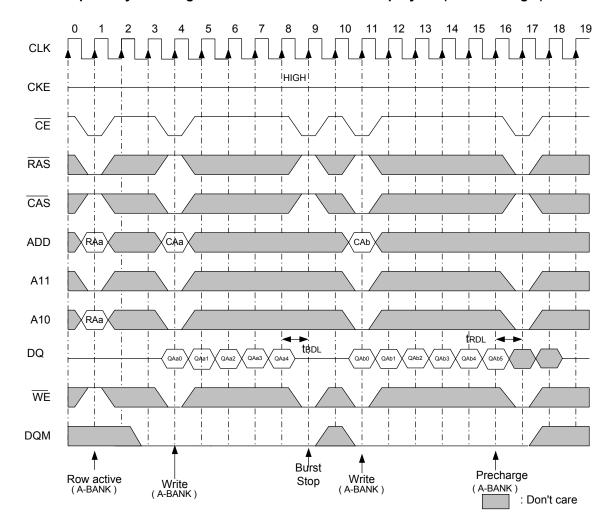

**Column address strobe and write command [WRIT]:** This command starts a write operation. When the burst write mode is selected, the column address (AY0 to AY7) and the bank select address (A11) become the burst write start address. When the single write mode is selected, data is only written to the location specified by the column address (AY0 to AY7) and the bank select address (A11).

**Write with auto precharge [WRIT A]:** This command automatically performs a precharge operation after a burst write with a length of 1, 2, 4 or 8.

**Column address strobe and read command [READ]:** This command starts a read operation. In addition, the start address of burst read is determined by the column address (AY0 to AY7) and the bank select address (BS). After the read operation, the output buffer becomes High-Z.

UTRON TECHNOLOGY INC. P90004

**Read with auto precharge [READ A]:** This command automatically performs a precharge operation after a burst read with a burst length of 1, 2, 4 or 8.

**Burst stop command [BST]:** This command stops the current burst operation.

**No operation [NOP]:** This command is not an execution command. However, the internal operations continue.

# **DQM Truth Table**

|                                         |        | CKE   | CKE |      |      |  |

|-----------------------------------------|--------|-------|-----|------|------|--|

| Function                                | Symbol | n - 1 | n   | DQMU | DQML |  |

| Upper byte write enable/output enable   | ENBU   | Н     | Х   | L    | Х    |  |

| Lower byte write enable/output enable   | ENBL   | Н     | Х   | Х    | L    |  |

| Upper byte write inhibit/output disable | MASKU  | Н     | Х   | Н    | Χ    |  |

| Lower byte write inhibit/output disable | MASKL  | Н     | Х   | Х    | Н    |  |

Note: H: V<sub>IH</sub>. L: V<sub>IL</sub>. x: V<sub>IH</sub> or V<sub>IL</sub>.

The UT52L1616 can mask input/output data by means of DQMU and DQML. DQMU masks the upper byte and DQML masks the lower byte.

During reading, the output buffer is set to Low-Z by setting DQMU/DQML to Low, enabling data output. On the other hand, when DQMU/DQML is set to High, the output buffer becomes High-Z, disabling data output.

During writing, data is written by setting DQMU/DQML to Low. When DQMU/DQML is set to High, the previous data is held (the new data is not written). Desired data can be masked during burst read or burst write by setting DQMU/DQML. For details, refer to the DQM control section of the UT52L1616 operating instructions.

# Preliminary Rev. 0.91

### **CKE Truth Table**

| Current state | Function                   | CKE<br>n-1 | CKE<br>n | CE | RAS | CAS | WE | Address |

|---------------|----------------------------|------------|----------|----|-----|-----|----|---------|

| Active        | Clock suspend mode entry   | Н          | L        | Н  | Х   | Х   | Χ  | X       |

| Any           | Clock suspend              | L          | L        | Χ  | Х   | Χ   | Χ  | X       |

| Clock suspend | Clock suspend mode exit    | L          | Η        | L  | Н   | Н   | Η  | X       |

|               |                            | L          | Η        | Ι  | Χ   | Χ   | Χ  | X       |

| Idle          | Auto-refresh command REF   | Н          | Н        | L  | L   | L   | Н  | X       |

| Idle          | Self-refresh entry SELF    | Н          | L        | L  | L   | L   | Н  | X       |

| Idle          | Power down entry           | Н          | L        | L  | Н   | Н   | Н  | X       |

|               | -                          | Н          | L        | Н  | Х   | Х   | Х  | X       |

| Self refresh  | sh Self refresh exit SELFX |            | Н        | L  | Н   | Н   | Η  | X       |

|               |                            | L          | Η        | Ι  | Χ   | Χ   | Χ  | X       |

| Power down    | Power down exit            | Ĺ          | Н        | L  | Н   | Н   | Н  | X       |

|               |                            | Ĺ          | Η        | Η  | Х   | Χ   | Χ  | X       |

Note: H: V<sub>IH</sub>. L: V<sub>IL</sub>. x: V<sub>IH</sub> or V<sub>IL</sub>.

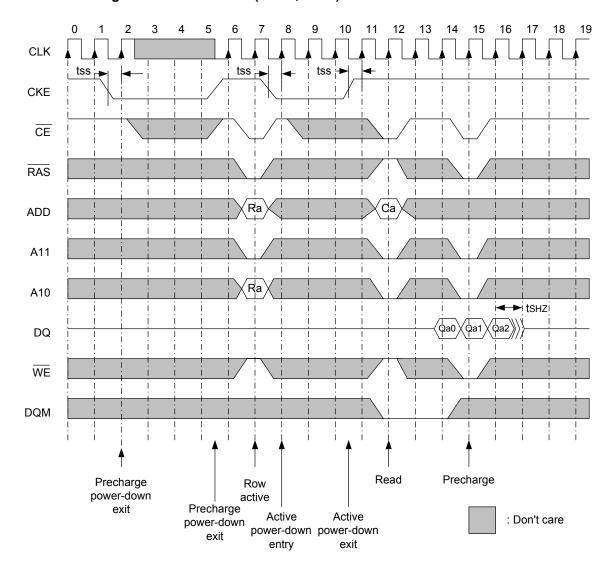

Clock suspend mode entry: The synchronous DRAM enters clock suspend mode from active mode by setting CKE to Low. The clock suspend mode changes depending on the current status (1 clock before) as shown below.

ACTIVE clock suspend: This suspend mode ignores inputs after the next clock by internally maintaining the bank active status.

**READ suspend and READ A suspend:** The data being output is held (and continues to be output).

WRITE suspend and WRIT A suspend: In this mode, external signals are not accepted. However, the internal state is held.

Clock suspend mode exit: The synchronous DRAM exits from clock suspend mode by setting CKE to High during the clock suspend state.

**IDLE:** In this state, all banks are not selected, and completed precharge operation.

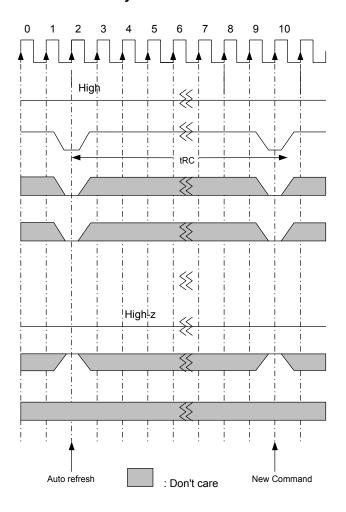

Auto refresh command [REF]: When this command is input from the IDLE state, the synchronous DRAM starts auto-refresh operation, (The auto-refresh is the same as the REF refresh of conventional DRAMs.) During the auto-refresh operation, refresh address and bank select address are generated inside the synchronous DRAM. For every auto-refresh cycle, the internal address counter is updated. Accordingly, 2048 times are required to refresh the entire memory. Before executing the auto-refresh command, all the banks must be in the IDLE state. In addition, since the precharge for all banks is automatically performed after auto-refresh, no precharge command is required after auto refresh.

Self refresh entry [SELF]: When this command is input during the IDLE state, the synchronous DRAM starts self refresh operation. After the execution of this command, self refresh continues while CKE is Low. Since self refresh is performed internally and automatically, external refresh operations are unnecessary.

Power down mode entry: When this command is executed during the IDLE state, the synchronous DRAM enters power down mode. In power down mode, power consumption is suppressed by cutting off the initial input circuit.

Self refresh exit: When this command is executed during self refresh mode, the synchronous DRAM can exit from self refresh mode. After exiting from self refresh mode, the synchronous DRAM enters the IDLE state.

UTRON TECHNOLOGY INC.

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C.

TEL: 886-3-5777882 FAX: 886-3-5777919

P90004

# **Function Truth Table**

The following table shows the operations that are performed when each command is issued in each mode of the synchronous DRAM.

| Current state                           | CE       | RAS      | CAS          | WE                                                | Address   | Command     | Operation                                       |  |  |  |  |  |

|-----------------------------------------|----------|----------|--------------|---------------------------------------------------|-----------|-------------|-------------------------------------------------|--|--|--|--|--|

| Precharge                               | Н        | Χ        | Χ            | X                                                 | Х         | DESL        | Enter IDLE after t <sub>RP</sub>                |  |  |  |  |  |

| · ·                                     | L        | Н        | Н            | Н                                                 | Х         | NOP         | Enter IDLE after t <sub>RP</sub>                |  |  |  |  |  |

|                                         | L        | Н        | Н            | L                                                 | X         | BST         | ILLEGAL                                         |  |  |  |  |  |

|                                         | L        | Н        | L            | Н                                                 | BA,CA,A10 | READ/READ A | ILLEGAL                                         |  |  |  |  |  |

|                                         | L        | Н        | L            | L                                                 | BA,CA,A10 | WRIT/WRIT A | ILLEGAL                                         |  |  |  |  |  |

|                                         | L        | L        | Н            | Н                                                 | BA,RA     | ACT         | ILLEGAL                                         |  |  |  |  |  |

|                                         | L        | L        | Н            | L                                                 | BA,A10    | PRE,PALL    | ILLEGAL                                         |  |  |  |  |  |

|                                         | L        | L        | L            | Н                                                 | X         | REF,SELF    | ILLEGAL                                         |  |  |  |  |  |

|                                         | L        | L        | L            | Ĺ                                                 | MODE      | MRS         | ILLEGAL                                         |  |  |  |  |  |

| Idle                                    | Н        | Х        | Х            | X                                                 | X         | DESL        | NOP                                             |  |  |  |  |  |

|                                         | L        | Н        | Н            | Н                                                 | X         | NOP         | NOP                                             |  |  |  |  |  |

|                                         | ī        | Н        | Н            | i                                                 | X         | BST         | NOP                                             |  |  |  |  |  |

|                                         |          | H        | L            | H                                                 | BA,CA,A10 | READ/READ A | ILLEGAL                                         |  |  |  |  |  |

|                                         | <u> </u> | H        | Ĺ            | i                                                 | BA,CA,A10 | WRIT/WRIT A | ILLEGAL                                         |  |  |  |  |  |

|                                         |          | L        | Н            | Н                                                 | BA,RA     | ACT         | Bank and row active                             |  |  |  |  |  |

|                                         | -        | -        | H            | i                                                 | BA,A10    | PRE,PALL    | NOP                                             |  |  |  |  |  |

|                                         | <u> </u> | L        | L            | H                                                 | X         | REF,SELF    | Refresh                                         |  |  |  |  |  |

|                                         | -        | <u> </u> |              | 1                                                 | MODE      | MRS         | Mode register set                               |  |  |  |  |  |

| Row active                              | Н        | X        | X            | X                                                 | X         | DESL        | NOP                                             |  |  |  |  |  |

| Now active                              | -        | H        | H            | H                                                 | X         | NOP         | NOP                                             |  |  |  |  |  |

|                                         | -        | Н        | Н            | П                                                 | X         | BST         | NOP                                             |  |  |  |  |  |

|                                         | <u> </u> |          | П            | L                                                 |           |             |                                                 |  |  |  |  |  |

|                                         | Ļ.       | Н        | L            | Н                                                 | BA,CA,A10 | READ/READ A | Begin read                                      |  |  |  |  |  |

|                                         | <u> </u> | H        | L            | L                                                 | BA,CA,A10 | WRIT/WRIT A | Begin write                                     |  |  |  |  |  |

|                                         | L        | L        | Н            | Н                                                 | BA,RA     | ACT         | Other bank active; ILLEGAL on same bank*3       |  |  |  |  |  |

|                                         | L        | L        | Н            | L                                                 | BA,A10    | PRE,PALL    | Precharge                                       |  |  |  |  |  |

|                                         | L        | L        | L            | Н                                                 | X         | REF,SELF    | ILLEGAL                                         |  |  |  |  |  |

|                                         | L        | L        | L            | L                                                 | MODE      | MRS         | ILLEGAL                                         |  |  |  |  |  |

| Read                                    | Н        | Χ        | Χ            | Χ                                                 | X         | DESL        | Continue burst to end                           |  |  |  |  |  |

|                                         | L        | Н        | Н            | Н                                                 | X         | NOP         | Continue burst to end                           |  |  |  |  |  |

|                                         | L        | Н        | Н            | L                                                 | X         | BST         | Burst stop to full page                         |  |  |  |  |  |

|                                         | L        | Н        | L            | Н                                                 | BA,CA,A10 | READ/READ A | Continue burst read to CAS latency and New read |  |  |  |  |  |

|                                         | L        | Н        | L            | L                                                 | BA,CA,A10 | WRIT/WRIT A | Term burst read/start write                     |  |  |  |  |  |

|                                         | L        | L        | Н            | Н                                                 | BA,RA     | ACT         | Other bank active; ILLEGAL on same bank*3       |  |  |  |  |  |

|                                         | L        | L        | Н            | L                                                 | BA,A10    | PRE,PALL    | Term burst read and<br>Precharge                |  |  |  |  |  |

|                                         | ı        | L        | L            | Н                                                 | Х         | REF,SELF    | ILLEGAL                                         |  |  |  |  |  |

|                                         | i        | i        | <del>-</del> | L                                                 | MODE      | MRS         | ILLEGAL                                         |  |  |  |  |  |

| Write                                   | Н        | X        | X            | X                                                 | X         | DESL        | Continue burst to end                           |  |  |  |  |  |

| *************************************** | H -      | H        | H            | H                                                 | X         | NOP         | Continue burst to end                           |  |  |  |  |  |

|                                         | <b> </b> | H        | H            | <del>                                     </del>  | X         | BST         | Burst stop on full page                         |  |  |  |  |  |

|                                         | <b> </b> | H        | L            | H                                                 | BA,CA,A10 | READ/READ A | Term burst and New read                         |  |  |  |  |  |

|                                         | <b>F</b> | Н        | L            | <del>                                      </del> | BA,CA,A10 | WRIT/WRIT A | Term burst and New read                         |  |  |  |  |  |

|                                         | <b>F</b> | L        | Н            | H                                                 | BA,RA     | ACT         | Other bank active; ILLEGAL on                   |  |  |  |  |  |

|                                         | _        |          |              |                                                   |           |             | same bank*3                                     |  |  |  |  |  |

|                                         | L        | L        | Н            | L                                                 | BA,A10    | PRE,PALL    | Term burst write and Precharge*2                |  |  |  |  |  |

|                                         | L        | L        | L            | Н                                                 | X         | REF,SELF    | ILLEGAL                                         |  |  |  |  |  |

|                                         | L        | L        | L            | L                                                 | MODE      | MRS         | ILLEGAL                                         |  |  |  |  |  |

| Current state   | CE | RAS | CAS | WE | Address   | Command     | Operation                        |

|-----------------|----|-----|-----|----|-----------|-------------|----------------------------------|

| Write with auto | Н  | X   | X   | X  | X         | DESL        | Continue burst to end and        |

|                 |    |     |     |    |           |             | precharge                        |

| precharge       | L  | Н   | Н   | Н  | X         | NOP         | Continue burst to end and        |

|                 |    |     |     |    |           |             | precharge                        |

|                 | L  | Н   | Н   | L  | X         | BST         | ILLEGAL                          |

|                 | L  | Н   | L   | Н  | BA,CA,A10 | READ/READ A | ILLEGAL                          |

|                 | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRIT A | ILLEGAL                          |

|                 | L  | L   | Н   | Н  | BA,RA     | ACT         | Other bank active; ILLEGAL on    |

|                 |    |     |     |    |           |             | same bank*3                      |

|                 | L  | L   | Н   | L  | BA,A10    | PRE,PALL    | ILLEGAL                          |

|                 | L  | L   | L   | Н  | X         | REF,SELF    | ILLEGAL                          |

|                 | L  | L   | L   | L  | MODE      | MRS         | ILLEGAL                          |

| Refresh         | Н  | Χ   | Χ   | Χ  | X         | DESL        | Enter IDLE after t <sub>RC</sub> |

| (auto refresh)  | L  | Н   | Н   | Н  | Χ         | NOP         | Enter IDLE after t <sub>RC</sub> |

| , ,             | L  | Н   | Н   | L  | Χ         | BST         | Enter IDLE after t <sub>RC</sub> |

|                 | L  | Н   | L   | Н  | BA,CA,A10 | READ/READ A | ILLEGAL                          |

|                 | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRIT A | ILLEGAL                          |

|                 | L  | L   | Н   | Н  | BA,RA     | ACT         | ILLEGAL                          |

|                 | L  | L   | Н   | L  | BA,A10    | PRE,PALL    | ILLEGAL                          |

|                 | L  | L   | L   | Н  | X         | REF.SELF    | ILLEGAL                          |

|                 | L  | L   | L   | L  | MODE      | MRS         | ILLEGAL                          |

Notes

P90004

H:  $V_{IH}$ . L:  $V_{IL}$  x:  $V_{IH}$  or  $V_{IL}$ .

1. The other combinations are inhibit.

2. An interval of  $t_{RWL}$  is required between the final valid data input and the precharge command.

3. If  $t_{RRD}$  is not satisfied, other bank active command is illegal.

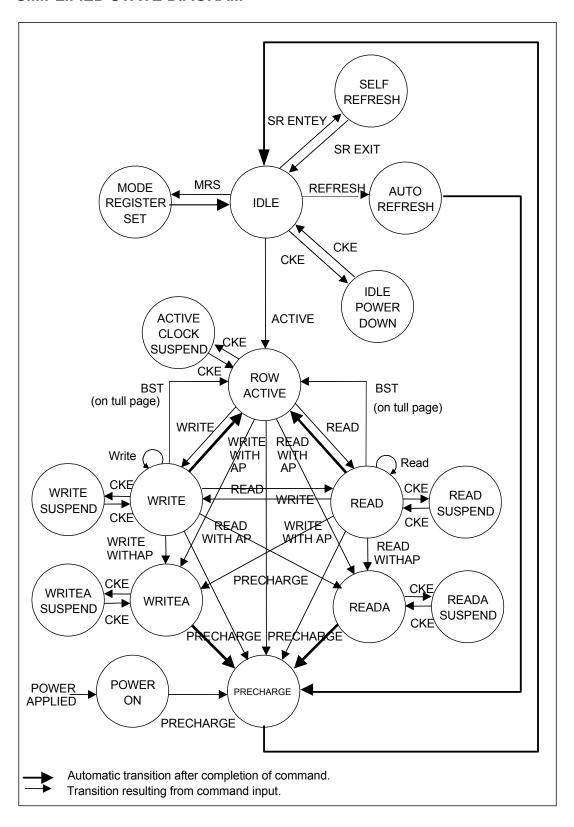

# SIMPLIFIED STATE DIAGRAM

# **DEVICE OPERATION**

# **Power Up Sequence**

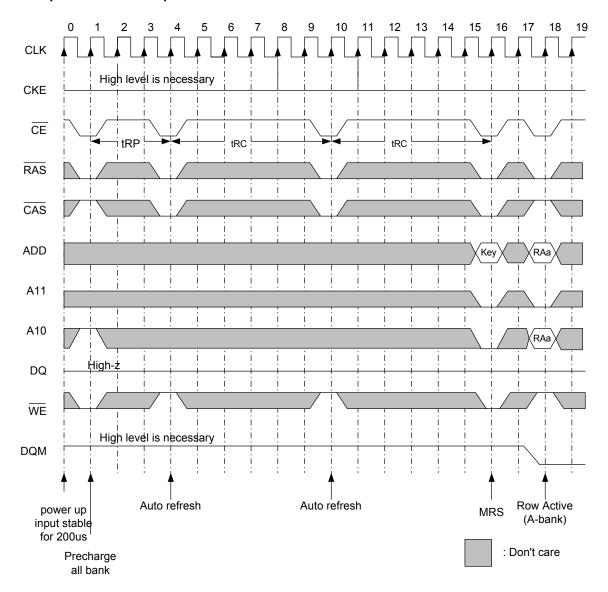

- Apply power and start clock, attempt to maintain CKE= "H", DQM= "H". Other pins are NOP condition at their inputs.

- Maintain stable power, stable clock and NOP input condition for a minimum of 200us.

# **Initialization Sequence**

After the following initialization sequence, the device is ready for full functionality:

- Precharge both banks.

- Issue 2 or more Auto refresh (REF) commands to the device.

- Issue a mode register set (MRS) command to set the device mode of operation.

- After t<sub>MRD0</sub> (3 clocks) is met. The device is ready for operation.

- \*\* Step 2 and 3 are interchangeable.

# Precharge Select bank (PRE)

The precharge operation will be performed on the active bank when the precharge selected bank command is issued. When the precharge command is issued with address A10 low, A11 selects the bank to be precharged. At the end of the precharge selected bank command the selected bank will be in idle state after the minimum  $t_{RP}$  is met.

# Precharge All (PALL)

Both banks are precharged at the same time when this command is issued. When the precharge command is issued with address A10 high then all banks will be precharged. At the end of the precharge all command both banks will be in idle state after the minimum  $t_{\rm RP}$  is met.

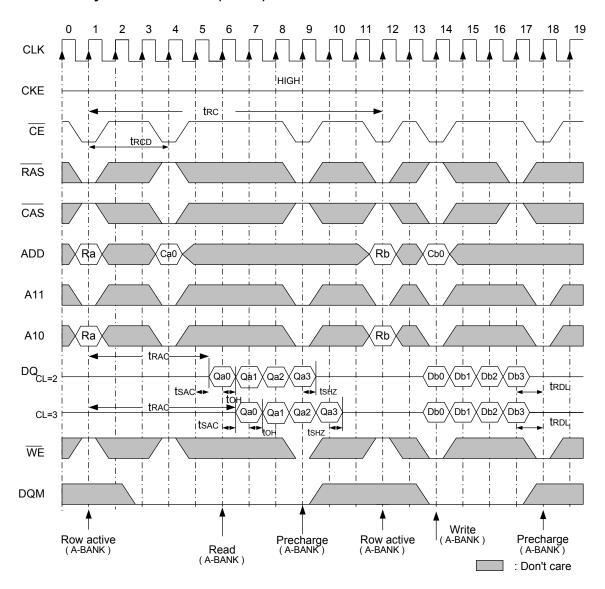

# **Auto Precharge**

AUTO PRECHARGE is a feature which performs the same individual-bank PRECHARGE function described above, but without requiring an explicit command. This is accomplished by using A10 to enable AUTO PRECHARGE in conjunction with a specific READ or WRITE command. A precharge of the bank/row that is addressed with the READ or WRITE command is automatically performed upon completion of the READ or WRITE burst, except in the full-page burst mode, where AUTO PRECHARGE does not apply. AUTO PRECHARGE is nonpersistent in that it is either enabled or disabled for each individual READ or WRITE command. AUTO PRECHARGE ensures that the PRECHARGE is initiated at the earliest valid stage within a burst. The user must not issue another command to the same bank until the precharge time ( $t_{RP}$ ) is completed. This is determined as if an explicit PRECHARGE command was issued at the earliest possible time, as described for each burst type in the Operation section of this data sheet.

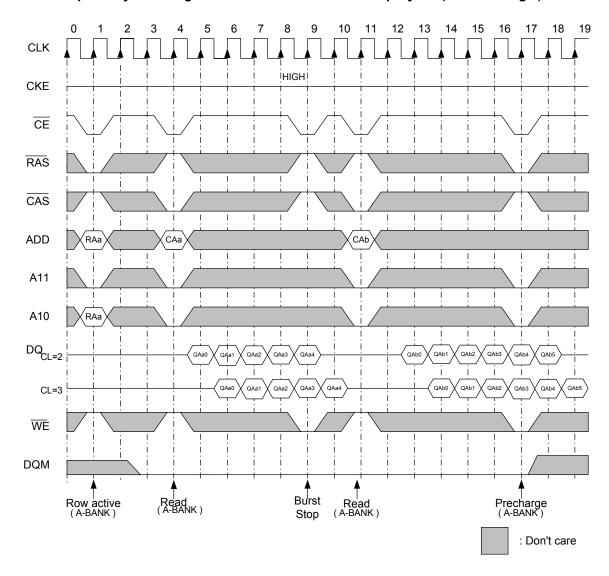

# **Burst Terminate**

The BURST TERMINATE command is used to truncate either fixed-length or full-page bursts. The most recently registered READ or WEITE command prior to the BURST TERMINATE command will be truncated as shown in the Operation section of this data sheet.

# NOP and Device Deselect (NOP, DESL)

The device is deselected by deactivating the  $\overline{CE}$  signal. In this mode the device ignores all the control inputs. The SDRAMs are put in NOP mode when  $\overline{CE}$  is active and by deactivating,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$ . For both Deselect and NOP the device will finish the current operation when this command is issued.

UTRON TECHNOLOGY INC. P90004

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C.

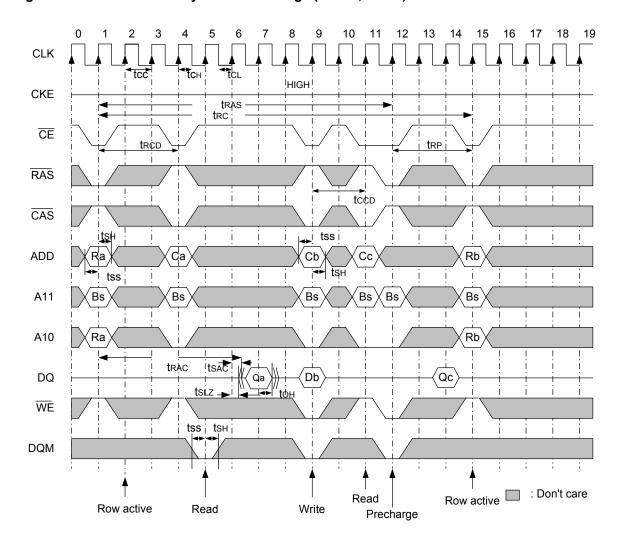

# **Row Activate (ACT)**

This command is used to select a row in a specified bank of the device. Read and write operation can only be initiated on this activated bank after the minimum  $t_{RCD}$  time has elapsed from the activate command.

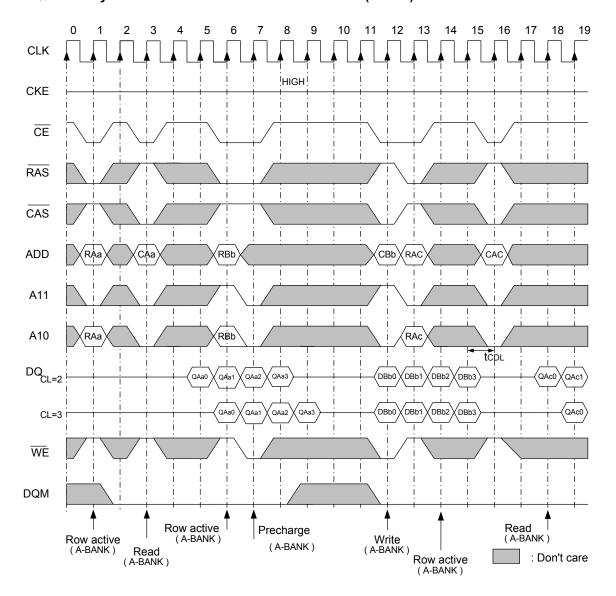

# Read Bank (READ)

This command is issued after the row activate command to initiate the burst read of data. The read command is initiated by activating  $\overline{CE}$ ,  $\overline{CAS}$  and deasserting  $\overline{WE}$  at the same clock sampling (rising) edge as described in the command truth table. The length of the burst and the  $\overline{CAS}$  latency time will be determined by the values programmed during the MRS command.

# Write Bank (WRIT)

This command is used after the row activate command to initiate the burst write of data. The write command is initiated by activating  $\overline{CE}$ ,  $\overline{CAS}$  and  $\overline{WE}$  at the same clock sampling (rising) edge as described in the command truth table. The length of the burst will be determined by the values programmed during the MRS command.

# **Functionality of SDRAM device:**

The following operations are supported by SDRAM:

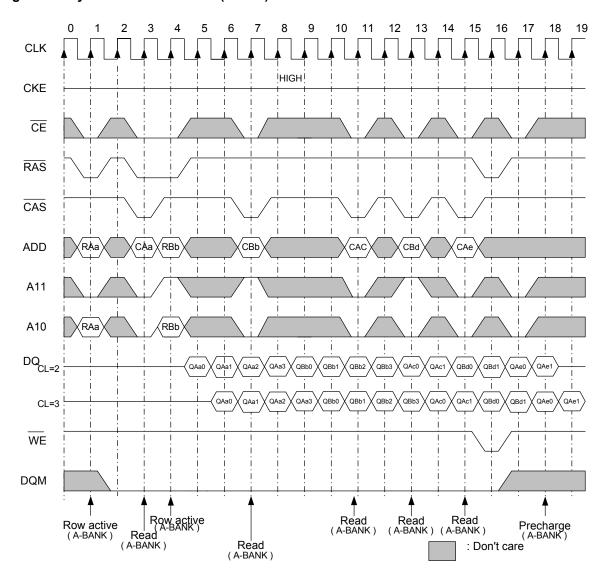

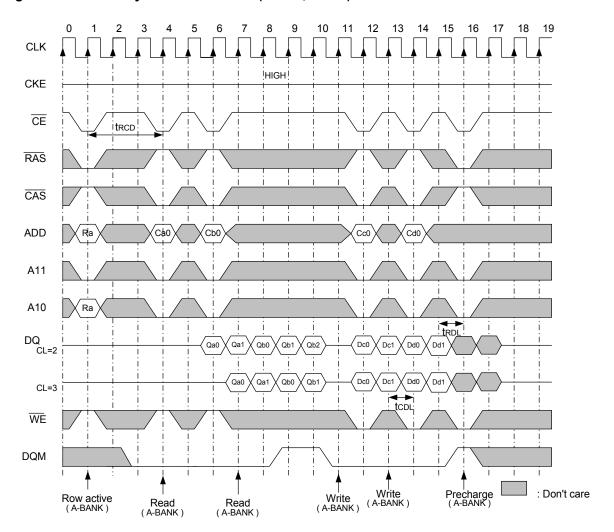

- Burst Read

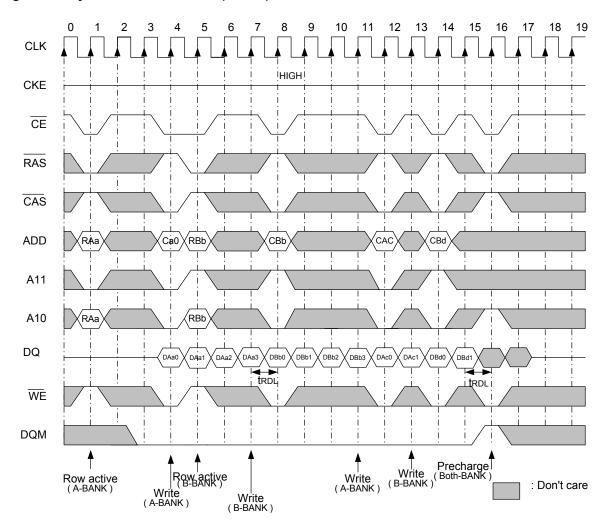

- Burst Write

- Multi bank Ping-Pong access

- Burst Read with Autoprecharge

- Burst Write with Autoprecharge

- Burst Read terminated with precharge

- Burst Write terminated with precharge

- Burst Read terminated with another Burst Read/Write

- Burst Write terminated with another Burst Write/Read

- DQM masking

- Fastest command to command delay of 1 clock

- Precharge All command

- Auto Refresh

- CL=2,3

- Burst Length 1,2,4, 8 and full page (256)

- Self Refresh Command

- Power down

- Terminating a read burst

- Terminating a write burst

UTRON TECHNOLOGY INC. P90004

# Mode Register Set (MRS)

Preliminary Rev. 0.91

This command is used to program the SDRAM for the desired operating mode. This command is normally used after power up as defined in the power up sequence before the actual operation of the SDRAM is initiated. The functionality of the SDRAM device can be altered by re-programming the mode register through the execution of Mode Register Set command. Both banks must be precharged (i.e. in idle state) before the MRS command can be issued.

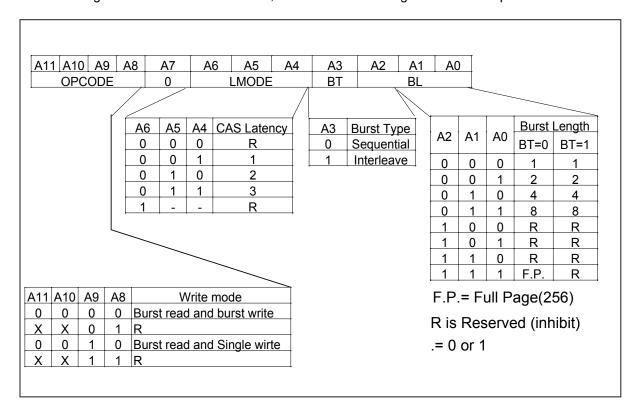

# **Mode Register Definition**

The mode register is set by the input to the address pins (A0 to A11) during mode register set cycles. The mode register consists of five sections, each of which is assigned to address pins.

# A11, A10, A9, A8: (OP Mode):

The synchronous DRAM has two types of write modes. One is the burst write mode, and the other is the single write mode. These bits specify write mode.

### Burst read and burst write:

Burst write is performed for the specified burst length starting from the column address specified in the write cycle.

# Burst read and single write:

Data is only written to the column address specified during the write cycle, regardless of the burst length.

# A6, A5, A4: (CAS Latency):

These pins specify the CAS latency.

# A3: (BT):

A burst type is specified. When full-page burst is performed, only "sequential" can be selected.

# A2, A1, A0: (Burst Length):

These pins specify the burst length.

UTRON TECHNOLOGY INC. P90004

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C.

# **Mode Register Configuration**

The mode register is set by the input to the address pins (A0 to A11) during mode register set cycles. The mode register consists of five sections, each of which is assigned to address pins.

| _  |     |     |     |   | _ |

|----|-----|-----|-----|---|---|

| Вu | rst | len | ath | = | 2 |

| Starting Ad. | Addressing | (decimal)  |  |  |  |  |

|--------------|------------|------------|--|--|--|--|

| A0           | Sequence   | Interleave |  |  |  |  |

| 0            | 0, 1,      | 0, 1,      |  |  |  |  |

| 1            | 1, 0,      | 1, 0,      |  |  |  |  |

# Burst length = 4

| Starti | ng Ad. | Addressing (decimal) |             |  |  |  |  |  |  |

|--------|--------|----------------------|-------------|--|--|--|--|--|--|