# VISION VV5409 Digital CMOS Sensor

CIF Format Monochrome Digital Image Sensor

# CUSTOMER DATASHEET (RESTRICTED)

# CHARACTERISTICS

- 525 line, 60 fps / 625 line, 50 fps output formats

CCIR-601/656 compliant timing

CIF Format Pixel-Array:

- 355 x 292 (306 x 244 for 525 line mode) Variable frame rate: 60/30/15/7.5 fps & 50/25/12.5/6.25 fps

- Crystals Supported: 13.5 MHz, 14.31818 MHz, and 35.46895 MHz On-chip 8-bit A/D convertor

- 1 / 2/ 4 wire proprietary digital video bus 2-wire serial control interface

- Programmable exposure and gain values Automatic black level calibration Programmable inter line/frame timings

- Low power Standard 48 BGA and 48LCC Packages

- On-chip Audio pre-amp.

# GENERAL DESCRIPTION

GENERAL DESCRIPTION

VV5409 is a highly-integrated CMOS camera with output in 3 digital video formats:

1. 525 line, 60 fps - 306 x 244 image size -13.5 MHz or 14.31818 MHz crystals.

2. 625 line, 50 fps - 356 x 292 image size -13.5 MHz or 17.734475 MHz crystal.

3. "VV6404 mode" - 356 x 292 image size -13.5 MHz or 17.734475 MHz crystal.

VV5409 contains a two stage flash 8-bit analogue-to-digital converter. Device serve jis fully automatic through the CMOS sensor's built in automatic black level calibration algorithm.

The main features of the sensor's digital interface are as follows:

# TECHNICAL SPECIFICATION

| Pixel Resolution | 306 x 244 or 356 x 292      |

|------------------|-----------------------------|

| Pixel Size       | 9.0 μm x 8.25 μm            |

| Exposure control | 25000:1 (performed by host) |

| Format           | CIF                         |

| SNR              | TBD                         |

| Supply Voltage                    | 5.0 V DC +/- 5%          |

|-----------------------------------|--------------------------|

| Supply Current                    | TBD                      |

| Operating<br>Temperature<br>Range | 0°C - 40°C               |

| Technology                        | 0.6um 2-Level Metal CMOS |

| Package type                      | 48BGA and 48LCC          |

1

Important:

A host processor is required to perform Automatic Exposure and Gain control (AEC/AGC) via the sensor serial interface, and to generate an appropriate video output timing format.

# **Commercial In Confidence**

cd38041a.fm 08/10/98

# VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

|  | Coi |  |

|--|-----|--|

|  |     |  |

| 1.                                                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                            | 4                                                                    |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1.1                                                                                                 | Typical applications                                                                                                                                                                                                                                                                                                                                                                                                    | 4                                                                    |

| 1.2                                                                                                 | VV5409 overview                                                                                                                                                                                                                                                                                                                                                                                                         | 4                                                                    |

| 1.3                                                                                                 | Automatic Black Level Calibration                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                    |

| 1.4                                                                                                 | Exposure Control                                                                                                                                                                                                                                                                                                                                                                                                        | 5                                                                    |

| 1.5                                                                                                 | Digital Interface                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                    |

| 1.6                                                                                                 | System Reset                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

| 1.7                                                                                                 | Startup configuration of Setup Data                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| 1.8                                                                                                 | Other Features                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                    |

| 2.                                                                                                  | Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                    |

| 2.1                                                                                                 | Video Timing                                                                                                                                                                                                                                                                                                                                                                                                            | 8                                                                    |

| 2.2                                                                                                 | Pixel-Array                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                                    |

| 3.                                                                                                  | Automatic Black Level Calibration                                                                                                                                                                                                                                                                                                                                                                                       | 11                                                                   |

| 4.                                                                                                  | Exposure Control                                                                                                                                                                                                                                                                                                                                                                                                        | 12                                                                   |

| 5.                                                                                                  | Digital Video Interface Format                                                                                                                                                                                                                                                                                                                                                                                          | 14                                                                   |

| 5.1                                                                                                 | General description                                                                                                                                                                                                                                                                                                                                                                                                     | 14                                                                   |

| 5.2                                                                                                 | Embedded control data                                                                                                                                                                                                                                                                                                                                                                                                   | 15                                                                   |

| 5.3                                                                                                 | Video timing reference and status/configuration data                                                                                                                                                                                                                                                                                                                                                                    | 17                                                                   |

| 5.4                                                                                                 | Detection of sensor using data bus state                                                                                                                                                                                                                                                                                                                                                                                | 33                                                                   |

| 5.5                                                                                                 | Resetting the Sensor Via the Serial Interface                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 5.6                                                                                                 | Power-up, Low-power and Sleep modes                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| 5.7                                                                                                 | Qualification of Output Data                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

| 6.                                                                                                  | Serial Control Bus                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| 6.1                                                                                                 | General Description                                                                                                                                                                                                                                                                                                                                                                                                     | 43                                                                   |

| 6.1<br>6.2                                                                                          | General Description Serial Communication Protocol                                                                                                                                                                                                                                                                                                                                                                       | 43<br>43                                                             |

| 6.1<br>6.2<br>6.3                                                                                   | General Description Serial Communication Protocol. Data Format                                                                                                                                                                                                                                                                                                                                                          | 43<br>43                                                             |

| 6.1<br>6.2<br>6.3<br>6.4                                                                            | General Description Serial Communication Protocol Data Format Message Interpretation.                                                                                                                                                                                                                                                                                                                                   | 43<br>43<br>43                                                       |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                                     | General Description Serial Communication Protocol Data Format Message Interpretation The Programmers Model                                                                                                                                                                                                                                                                                                              | 43<br>43<br>43<br>45<br>45                                           |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                              | General Description Serial Communication Protocol. Data Format Message Interpretation The Programmers Model Register descriptions                                                                                                                                                                                                                                                                                       | 43<br>43<br>45<br>45<br>47                                           |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                                       | General Description Serial Communication Protocol. Data Format Message Interpretation The Programmers Model. Register descriptions Types of serial interface messages                                                                                                                                                                                                                                                   | 43<br>43<br>45<br>45<br>47                                           |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                                | General Description Serial Communication Protocol.  Data Format Message Interpretation.  The Programmers Model. Register descriptions Types of serial interface messages.  Serial-Interface Timing                                                                                                                                                                                                                      | 43<br>43<br>45<br>45<br>47<br>58                                     |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                                | General Description Serial Communication Protocol. Data Format Message Interpretation. The Programmers Model Register descriptions. Types of serial interface messages. Serial-Interface Timing Clock Signal                                                                                                                                                                                                            | 43<br>43<br>45<br>45<br>47<br>58<br>62                               |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.                                          | General Description Serial Communication Protocol. Data Format Message Interpretation The Programmers Model Register descriptions Types of serial interface messages Serial-Interface Timing Clock Signal Synchronising Multiple Cameras                                                                                                                                                                                | 43<br>43<br>45<br>45<br>47<br>58<br>62<br>64                         |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                                | General Description Serial Communication Protocol. Data Format Message Interpretation The Programmers Model Register descriptions Types of serial interface messages. Serial-Interface Timing Clock Signal Synchronising Multiple Cameras Other Features                                                                                                                                                                | 43<br>43<br>45<br>45<br>58<br>62<br>64<br>65                         |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.<br>8.<br>9.                              | General Description  Serial Communication Protocol.  Data Format  Message Interpretation  The Programmers Model.  Register descriptions.  Types of serial interface messages.  Serial-Interface Timing.  Clock Signal.  Synchronising Multiple Cameras.  Other Features.  Microphone Amplifier.                                                                                                                         | 43<br>43<br>45<br>45<br>58<br>62<br>64<br>65<br>67                   |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.<br>8.<br>9.                              | General Description Serial Communication Protocol.  Data Format Message Interpretation. The Programmers Model. Register descriptions Types of serial interface messages. Serial-interface Timing.  Clock Signal.  Synchronising Multiple Cameras.  Other Features.  Microphone Amplifier. Debounced Switch Input.                                                                                                       | 43<br>43<br>45<br>45<br>62<br>64<br>65<br>67<br>68                   |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.<br>8.<br>9.                              | General Description  Serial Communication Protocol.  Data Format  Message Interpretation  The Programmers Model.  Register descriptions.  Types of serial interface messages.  Serial-Interface Timing.  Clock Signal.  Synchronising Multiple Cameras.  Other Features.  Microphone Amplifier.                                                                                                                         | 43<br>43<br>45<br>45<br>62<br>64<br>65<br>67<br>68                   |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.<br>8.<br>9.                              | General Description Serial Communication Protocol Data Format Message Interpretation The Programmers Model Register descriptions Types of serial interface messages. Serial-Interface Timing Clock Signal Synchronising Multiple Cameras Other Features Microphone Amplifier Debounced Switch Input Serial-Interface Programmable Pins Detailed specifications                                                          | 43<br>43<br>45<br>45<br>62<br>64<br>65<br>67<br>68<br>68             |

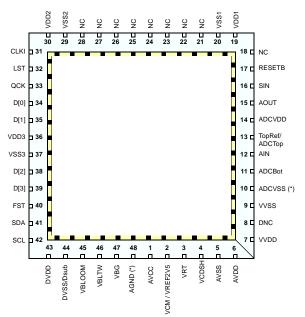

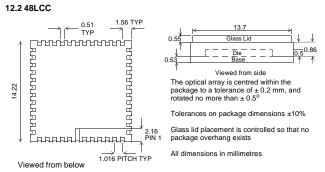

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.<br>8.<br>9.<br>9.1<br>9.2<br>9.3         | General Description  Serial Communication Protocol  Data Format  Message Interpretation  The Programmers Model  Register descriptions  Types of serial interface messages  Serial-Interface Tirning  Clock Signal  Synchronising Multiple Cameras  Other Features  Microphone Amplifier  Debounced Switch Input  Serial-Interface Programmable Pins  Detailed specifications  Pinouts and pin descriptions              | 43<br>43<br>45<br>45<br>62<br>64<br>65<br>67<br>68<br>68<br>69       |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.<br>8.<br>9.1<br>9.2<br>9.3<br>10.<br>11. | General Description  Serial Communication Protocol.  Data Format Message Interpretation The Programmers Model. Register descriptions. Types of serial interface messages. Serial-Interface Timing.  Clock Signal Synchronising Multiple Cameras  Other Features Microphone Amplifier Debounced Switch Input Serial-Interface Programmable Pins  Detailed specifications. Pinouts and pin descriptions Sensor pin list.  | 43<br>43<br>45<br>45<br>62<br>64<br>65<br>67<br>68<br>68<br>69<br>70 |

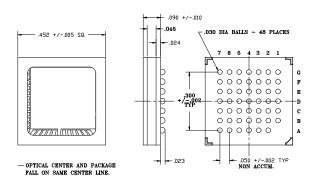

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.<br>8.<br>9.<br>9.1<br>9.2<br>9.3<br>10.  | General Description Serial Communication Protocol Data Format Message Interpretation The Programmers Model Register descriptions Types of serial interface messages Serial-Interface Timing Clock Signal Synchronising Multiple Cameras Other Features Microphone Amplifier Debounced Switch Input Serial-Interface Programmable Pins Detailed specifications Pinouts and pin descriptions Sensor pin list 48BGA pinout | 43<br>43<br>45<br>45<br>62<br>65<br>67<br>68<br>68<br>69<br>70       |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.<br>8.<br>9.<br>9.1<br>9.2<br>9.3<br>10.  | General Description  Serial Communication Protocol.  Data Format Message Interpretation The Programmers Model. Register descriptions. Types of serial interface messages. Serial-Interface Timing.  Clock Signal Synchronising Multiple Cameras  Other Features Microphone Amplifier Debounced Switch Input Serial-Interface Programmable Pins  Detailed specifications. Pinouts and pin descriptions Sensor pin list.  | 43<br>43<br>45<br>45<br>62<br>65<br>67<br>68<br>68<br>69<br>70       |

# **Commercial In Confidence**

# VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

|     | 48BGA (400G)                     |   |

|-----|----------------------------------|---|

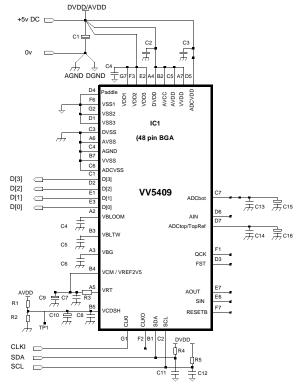

| 13. | Suggested VV5409 support circuit | 7 |

| 14. | Evaluation kits (EVK's)          | 7 |

| 15. | Ordering details                 | 7 |

$\underline{\text{Note}}$ : In this document, where hexadecimal values are used, they are indicated by a subscript H, such as  $\overline{\text{FF}}_{\text{H}}$ ; other values are decimal.

**Commercial In Confidence**

08/10/98

cd38041a.fm

# VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

# 1. Introduction

The VV5409 is a highly integrated CMOS digital imaging sensor with 3 different digital video output formats. The sensor contains a two-stage flash, 8-bit ADC (Analogue to Digital Converter). Exposure control can be handled automatically by the host. Other device set-ups can be controlled using the 2-wire serial-interface.

# 1.1 Typical applications

- Monochrome Video Surveillance/CCTV

- Biometrics Automotive

- Automotive

Machine Vision

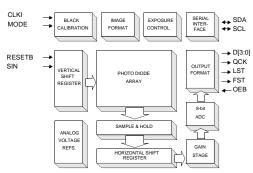

Figure 1.1 : Typical block diagram: Monochrome Video application

# 1.2 VV5409 overview

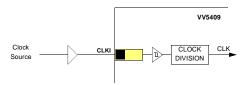

VV5409 is a CIF format CMOS image sensor which outputs digital pixel-data at frame and line rates compatible with either NTSC or PAL video standards. Table 1.1 summarises the main video modes. The pixel-data is digitised by an on-chip 8-bit ADC (Figure 1.2).

All of the video modes can be programmed through the serial-interface. The various operating modes are detailed in Section 2.

detailed in Section 2.

Important: The sensor's video-data stream only contains raw pixel-data. An intelligent host co-processor is required to perform auto-exposure and gain control, and to generate appropriate video output timing.

| ٠ | Mode         | Clock<br>(MHz) | Pixel<br>Clock | Image<br>Size | Line Time<br>(µs) | Lines | Frame<br>Rate |

|---|--------------|----------------|----------------|---------------|-------------------|-------|---------------|

|   |              | ` '            | Divisor        |               | u -/              | Frame | (fps)         |

|   | CIF - 25 fps | 7.15909        | 2              | 356 x 292     | 131.580969        | 304   | 24.99961      |

|   | CIF - 30 fps | 7.15909        | 2              | 356 x 292     | 109.790490        | 304   | 29.96137      |

|   | PAL (656)    | 13.500000      | 2              | 356 x 292     | 64.000000         | 625   | 25.00000      |

|   | NTSC (656)   | 13.500000      | 2              | 306 x 244     | 63.555564         | 525   | 29.97003      |

|   | PAL (8 fsc)  | 35.46895       | 5              | 356 x 292     | 63.999639         | 625   | 25.00014      |

|   | NTSC (8 fsc) | 28.636360      | 5              | 306 x 244     | 63.555564         | 525   | 29.97003      |

Table 1.1 : Video Modes

# 1.3 Automatic Black Level Calibration

Automatic black level control ensures consistent picture quality across the whole range of operating conditions.

# **Commercial In Confidence**

VV5409 does not include any form of automatic exposure and gain control. To produce a correctly exposed image in the sensor-array, an exposure control algorithm must be implemented externally. This must be performed by a host controller/co-processor.

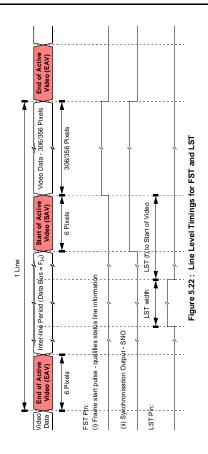

#### 1.5 Digital Interface

- The sensor offers a very flexible digital interface, its main components are listed below:

1. A tri-stateable, 4-wire, data-bus (D[3:0]) for sending both video-data, and embedded timing references

- A data qualification clock, QCK, which can be programmed through the serial-interface, to behave in a number of different ways (Tri-stateable)

A line start signal, LST (Tri-stateable)

- 4. A frame start signal, FST (Tri-stateable)

- 5. OEB tri-states all 8 data-bus lines, D[7:0], the qualification clock, QCK, LST, and FST

- The ability to synchronise the operation of multiple cameras

A 2-wire, serial-interface, (SDA,SCL) for controlling and setting up the device

Figure 1.2 : Block Diagram of VV5409 Image Sensor

# 1.5.1 Digital Data Bus

Along within the pixel-data, codes representing the start and end of fields and the start and end of lines are embedded within the video-data stream to allow a host controller to synchronise with video-data the camera module is generating. Section 5. defines the format for the output video-data stream.

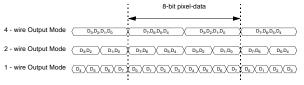

The 8-bit data which makes up the video-data stream can be output on the data-bus in one of 3 ways:

1. A series pair of 4-bit nibbles, most significant nibble first, on 4-wires.

- 2. Four, 2-bit values, most significant 2-bit value first, on 2-wires.

- Bit-serial data, eight 1-bit values, least significant bit first, on 1-wire.

For the 2, and 1-wire modes, the complement of the data can also be enabled in addition to the data itself.

# **Commercial In Confidence**

cd38041a fm 08/10/98

### VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

# 1.5.2 Frame Grabber Control Signals

To complement the embedded control sequences, the data qualification clock (QCK), the line-start-signal (LST) and the field-start-signal (FST), signals can independently be set-up to either be

- Disabled

- 2. Free-running

- Qualify only the control sequences and the pixel-data

- 4. Qualify the pixel-data only.

There is also the choice of two different QCK frequencies where one is twice the frequency of the other.

- 1. Fast QCK; the falling edge of the clock qualifies every 4, 2 or 1-bit block of data that makes up a pixel

- Slow QCK: the rising edge qualifies the 1st, 3rd, 5th, etc. blocks of data which make up a pixel value, while the falling edge qualifies the 2nd, 4th, 6th etc. blocks of data. For example, in the 4-wire mode, the rising edge of the clock qualifies the most significant nibbles, while the falling edge of the clock qualifies the least significant nibbles.

# 1.5.3 Synchronisation of Multiple Cameras

Multiple camera configurations can be synchronised by applying a rising edge to the SIN pins once per frame

The FST/DIN pin of the one of cameras (the master) can be re-configured as a SNO output to supply the synchronidsation signal for the other cameras.

Note: The SNO function has not been verified.

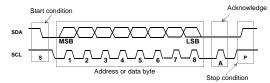

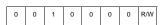

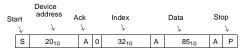

### 1.5.4 2-wire Serial-Interface

The 2-wire serial-interface provides complete control over how the sensor is setup and run. The sensor serial address is fixed at  $20_{\rm H}$ .

Two broadcast serial-interface addresses are supported. One allows all sensors to be written to in parallel, and if a VISION co-processor is in use, the other allows all sensors and co-processors to be written to in

Section 6. defines the serial-interface communications protocol, and the register map of all the locations which can be accessed through the serial-interface.

# 1.6 System Reset

Using the RESETB pin (active low, internal pull-up), a System Reset of the sensor can be activated. The sensor behaves exactly as if a power down then power up has taken place, i.e., all sensor serial registers are reset to their default status, and video timing will be reset.

# 1.7 Startup configuration of Setup Data

The sensor should be correctly configured on power up, or following a System Reset (Section 1.6), , for correct operation of the sensor, by writing settings to the camera registers on startup. This applies to the Setup0 [16], Setup1 [17], and at1 [121] registers in particular.

# 1.8 Other Features

# 1.8.1 Microphone Pre-Amplifier

Pins AIN, and AOUT, are the input, and output respectively, for a 2-stage Microphone amplifier. The gain of this amplifier is programmable through the serial-interface

The output of the Microphone can be multiplexed at the end of a video line, onto the input of the 8-bit ADC

# **Commercial In Confidence**

#### VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

digitised pixel-data. This value is output, once per line, as part of the embedded "end-of-line" sequence. While this amplifier is primarily intended as a Microphone amplifier, it can be used as way to digitise any "slow-moving" analogue input. The maximum sample rate is approximately 15k samples/second as there is only one sample per line of video. See also Section 9.1.

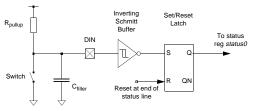

# 1.8.2 Debounced Switch Input

cd38041a fm

This de-bounced input (the FST/DIN pin re-configured as a debounced switch input pin) is designed for use with a switch, for still-image capture. If the switch is pressed, it sets a flag in the status line for the next field, marking it as the one the user has selected. See also Section 9.2.

**Commercial In Confidence**

08/10/98

# VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

# 2. Operating Modes

# 2.1 Video Timing

The video format mode on power-up is determined by the value of bits 6-7 of the setup0 register. It may be desirable to access a larger image array size by enabling PAL or NTSC video output modes. While the video output timing from the sensor is *compatible* with PAL.NTSC/CCIR656 formats, video sync timing and encoding must be performed by an external host controller.

The frame/field rate is programmable only through the serial-interface. Setup0 bit 3 selects between 30 and 25 frames per second for the CIF modes, and 60/50 fields per second for the Digital, and Analog Timing

| Video Mode     | setup0[6-7] | setup0 Bit3 | Video Mode   |

|----------------|-------------|-------------|--------------|

| CIF (VV6404)   | 002         | 0           | CIF - 25 fps |

|                |             | 1           | CIF - 30 fps |

| DIGITAL (CCIR) | 012         | 0           | PAL (656)    |

|                |             | 1           | NTSC (656)   |

| ANALOG (TV)    | 102         | 0           | PAL (8 fsc)  |

|                |             | 1           | NTSC (8 fsc) |

Table 2.1 : Video Timing Mode Select Pins

The number of video lines-in for each frame-rate, is the same (304) for each of the CIF modes. The slower The number of video lines-in for each frame-rate, is the same (304) for each of the CIF modes. The slower frame rate is implemented, by simply extending the line period from 399 pixel periods, to 471 pixel periods. Table 2.2 details the setup for each of the video timing modes. Changing either the mode pin, or a serial write to the *video\_timing* register will force the contents of other registers in the serial-interface to change to the appropriate values. If, for example, a different data output-mode is required from the default, for a particular video mode, a write to the appropriate register after the mode has changed will setup the desired value.

| Mode | Video Mode   | Clock<br>(MHz) | Pixel<br>Clock<br>Divisor | Video<br>Data | Line<br>Length | Field<br>Length | Data<br>Output<br>Mode |

|------|--------------|----------------|---------------------------|---------------|----------------|-----------------|------------------------|

| 0    | CIF - 25 fps | 7.15909        | 2                         | 356 x 292     | 471            | 304             | 4-wire                 |

| 1    | CIF - 30 fps | 7.15909        | 2                         | 356 x 292     | 393            | 304             | 4-wire                 |

| 2    | PAL(656)     | 13.500000      | 2                         | 356 x 292     | 432            | 312/313         | 4-wire                 |

| 3    | NTSC (656)   | 13.500000      | 2                         | 306 x 244     | 429            | 262/263         | 4-wire                 |

| 4    | PAL (8 fsc)  | 28.636360      | 5                         | 356 x 292     | 454            | 312/313         | 4-wire                 |

| 5    | NTSC (8 fsc) | 35.46895       | 5                         | 306 x 244     | 364            | 262/263         | 4-wire                 |

Table 2.2 : Video Timing Modes

For flexibility, the number of pixel clocks per line, and the number of lines per field, can be programmed through the serial-interface, both to a maximum value of 510.

# **Commercial In Confidence**

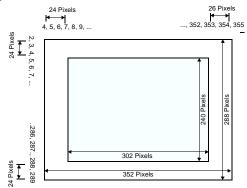

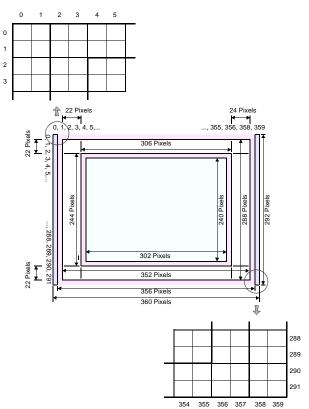

The physical pixel-array is 360 x 292 pixels. The pixel size is 9.0µm by 8.25 µm. The useable image size for NTSC format is 302 x 240 pixels while for PAL and CIF formats it is 352 x 288 pixels. An optional border 2 pixels deep on all 4 sides of the array can be enabled (Figure 2.3). The resulting image sizes are 306 x 244 for NTSC, and 356 x 292 pixels for PAL and CIF video modes. The border option is programmable through the serial-interface.

| Video Modes | Border   | Output Image size (column x row) |

|-------------|----------|----------------------------------|

| NTSC        | Disabled | 302 x 240                        |

|             | Enabled  | 306 x 244                        |

| PAL, CIF    | Disabled | 352 x 288                        |

|             | Enabled  | 356 x 292                        |

Table 2.3 : Image Format Selection

Figure 2.2 shows how the 302 x 240 sub-array is aligned within the bigger 352 x 288 pixel-array. The position of the 306 x 244 sub-array has been offset by one column, relative to central location. Image read-out is non-interlaced raster scan. The larger 352 x 288 array covers pixels 4-355 and 2-289.

With extra border rows/columns enabled, and Figure 2.3 shows the relative array positions.

Note: To enable correct readout of sensor pixels, bit 7 of the Setup1 register [17] must be set to 0. Its default power-up value is 1.

Figure 2.1 : VV5409 Image format with border rows/columns disabled

# **Commercial In Confidence**

cd38041a.fm 08/10/98 9 VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

Figure 2.3: VV5409 Image format with border rows/columns enabled

# **Commercial In Confidence**

# 3. Automatic Black Level Calibration

Black calibration is used to remove voltage offsets that cause shifts in the black level of the video signal. VV5409 is equipped with an automatic function that continually monitors the output black level and calibrates if it has moved out of range. The signal is corrected using two "Black-Calibration" DACs:

- ADC stage DAC, B0[7:0].

OSA Input Offset Compensation DAC, B1 [7:0]

Black calibration can be split into two stages, monitor and update. During the monitor phase the current black level of 4 black reference lines at the top of the pixel array is compared against two threshold values.

If the current value falls outside the threshold window then an update cycle is triggered. The update cycle can also be triggered by a change in the gain applied to sensor core or via the serial interface (see also Section

# VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

# 4. Exposure Control

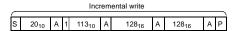

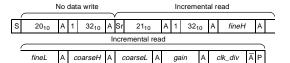

The exposure time for a pixel and the gain of the input amplifier to the 8-bit ADC are programmable via the serial interface. The explanation below assumes that the gain and exposure values are updated together as part of a 5 byte serial interface auto-increment sequence.

The exposure is divided into 2 components - coarse and fine. The coarse exposure value sets the number of lines a pixel exposes for, while the fine exposure sets the number of additional pixel clock cycles a pixel integrates for. The sum of the two gives the overall exposure time for the pixel array.

Exposure Time = Clock Divider Ratio x (Coarse x Line Length + Fine) x (CLKI clock period)

| Register<br>Index | Bits | Function                  | Default | Comment                        |

|-------------------|------|---------------------------|---------|--------------------------------|

| 32                | 0:0  | Fine MSB exposure value   | 0       | Maximum Line Length Mode       |

| 33                | 7:0  | Fine LSB exposure value   |         | Dependant                      |

| 34                | 0:0  | Coarse MSB exposure value | 302     | Maximum equals Field Length-1. |

| 35                | 7:0  | Coarse LSB exposure value |         |                                |

| 36                | 3:0  | Gain value                | 0       |                                |

| 37                | 1:0  | Clock divisor value       | 0       |                                |

Table 4.1 : Exposure, Clock Rate and Gain Registers

If an exposure value is loaded outwith the valid ranges listed in the above table the value is clipped to lie within the above ranges.

Exposure and gain values are re-timed within the sensor to ensure that a new set of values is only applied to the sensor array at the start of each frame. Bit 0 of the Status Register is set high when a new exposure value is written via the serial interface but has not yet been applied to the sensor array.

There is a 1 frame latency between a new exposure value being applied to the sensor array and the results of the new exposure value being applied to the sensor array and the results of the new exposure value being read-out. The same latency does not exist for the gain value. To ensure that the new exposure and gain values are aligned up correctly the sensor delays the application of the new gain value by one frame relative to the application of the new exposure value.

To eliminate the possibility of the sensor array seeing only part of the new exposure and gain setting, if the serial interface communications extends over a frame boundary, the internal re-timing of exposure and gain data is disabled while writing data to any location in the Exposure page of the serial interface register map. Thus if the 5 bytes of exposure and gain data is sent as an auto-increment sequence, it is not possible for the sensor to consume only part of the new exposure and gain data. See also Section 6.6.3.

**Commercial In Confidence**

**Commercial In Confidence**

cd38041a fm 08/10/98 11 cd38041a fm 08/10/98 12

| Gain Binary code | Actual signal gain | Gain Binary code | Actual signal gain |

|------------------|--------------------|------------------|--------------------|

| 00002            | 0.500              | 10002            | 0.533              |

| 00012            | 1.000              | 10012            | 1.143              |

| 00102            | 0.667              | 10102            | 0.727              |

| 00112            | 2.000              | 10112            | 2.667              |

| 01002            | 0.571              | 11002            | 0.615              |

| 01012            | 1.333              | 11012            | 1.600              |

| 01102            | 0.800              | 11102            | 0.889              |

| 01112            | 4.000              | 11112            | 8.000              |

Table 4.2 : System Analog Gain Values

| Clock Divisor Setting | Pixel Clock Divisor |

|-----------------------|---------------------|

| 002                   | 2                   |

| 012                   | 4                   |

| 102                   | 8                   |

| 112                   | 16                  |

Table 4.3 : Clock Divisor Values

**Commercial In Confidence**

08/10/98

cd38041a.fm

# VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

# 5. Digital Video Interface Format

# 5.1 General description

The video interface consists of a unidirectional, tri-stateable 4-wire data-bus. The nibble transmission is synchronised to the rising edge of the system clock.

| Read-out Order                                                      | Progressive Scan (Non-interlaced)                                                                                                                                                                                                                   |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Form of encoding                                                    | Uniformly quantised, PCM, 8 bits per sample                                                                                                                                                                                                         |

| Correspondence between video signal levels and quantisation levels: | Internally valid pixel-data is clipped to ensure that $00_H$ and FF $_H$ values do not occur when pixel-data is being output on the databus. This gives 254 possible values for each pixel (1 - 254). The video black level corresponds to code 16. |

Table 5.1 : Video encoding parameters

Digital video-data is 8 bits per sample, and can be transmitted in one of three ways:

- A series pair of 4-bit nibbles, most significant nibble first, on 4-wires

Four 2-bit values, most significant 2-bit value first, on 2-wires

- 3. Bit-serial data, eight 1-bit values, least significant bit first, on 1-wire.

Figure 5.1: 4-wire, 2-wire and 1-wire Output Modes

In the following description the 4-wire mode is used as an example. The 2-wire, and 1-wire modes can be viewed as variants of the 4-wire mode.

Control information is multiplexed with the sampled pixel-data. Such control information includes both video timing references, sensor status/configuration data and digitised values for VV5409's analogue input pin, AIN.

Video timing reference information takes the form of field start characters, line start characters, end of line characters and a line counter.

# **Commercial In Confidence**

### 5.2 Embedded control data

To distinguish the control data from the sampled video data all control data is encapsulated in embedded control sequences. These are 6 bytes long and include a combined escape/sync character, 1 control byte (the 'command byte') and 2 bytes of supplementary data.

To minimise the susceptibility of the embedded control data to random bit errors redundant coding

techniques have been used to allow single bit errors in the embedded control words to be corrected However, more serious corruption of control words or the corruption of escape/sync characters cannot be tolerated without loss of sync to the data stream. To ensure that a loss of sync is detected a simple set of rules has been devised. The four exceptions to the rules are outlined below:

1. Data containing a command words that has two bit errors.

- 2. Data containing two 'end of line' codes that are not separated by a 'start of line' code

- Data preceding an 'end of field' code before a start of frame' code has been received.

- 4. Data containing line that do not have sequential line numbers (excluding the 'end of field' line). If the video processor detects one of these violations then it should abandon the current field of video

### 5.2.1 The combined escape and sync character

Each embedded control sequence begins with a combined escape and sync character that is made up of three words. The first two of these are FF<sub>H</sub> FF<sub>H</sub><sup>-</sup> constituting two words that are illegal in normal data. The next word is 00<sub>H</sub> - guaranteeing a clear signal transition that allows a video processor to determine the position of the word boundaries in the serial stream of nibbles. Combined escape and sync characters are always followed by a command byte - making up the four byte minimum embedded control sequence.

### 5.2.2 The command word

The byte that follows the combined escape/sync characters defines the type of embedded control data. Three of the 8 bits are used to carry the control information, four are 'parity bits' that allow the video processor to detect and correct a certain level of errors in the transmission of the command words, the remaining bit is always set to 1 to ensure that the command word is never has the value 00  $_{\rm H}$ . The coding scheme used allows the correction of single bit errors (in the 8-bit sequence) and the detection of 2 bit errors The three data bits of the command word are interpreted as shown in Figure 5.2.The even parity bits are based on the following relationships: relationships:

- 1. An even number of ones in the 4-bit sequence (C2, C1, C0 and P0).

- 2. An even number of ones in the 3-bit sequence  $(C_2,\,C_1,\,P_1)$

- 3. An even number of ones in the 3-bit sequence  $(C_2, C_0, P_2)$ .

- An even number of ones in the 3-bit sequence (C<sub>1</sub>, C<sub>0</sub>, P<sub>3</sub>).

Table 5.3 shows how the parity bits maybe used to detect and correct 1-bit errors and detect 2-bit errors.

# 5.2.3 Supplementary Data

The last 2 bytes of the embedded control sequence contains supplementary data. Three options:

- The current 12-bit line number. The 12-bit line number is packaged up by splitting it into two 6-bit values. Each 6-bit values is then converted into an 8-bit value by adding a zero to the start and an odd word parity bit at the end.

- 2. If the line code equals the end of line, the 2 bytes are padded out using null characters (FFH).

- 3. If the line code equals the end of line and digitise analogue input enabled then the 2 supplementary data bytes contain 2 8-bit values representing the values of the analogue input at those two points in

# **Commercial In Confidence**

cd38041a fm 08/10/98 15

Figure 5.2: Embedded Control Sequence

Nibble D<sub>2</sub>

| Line Code   | Nibble X <sub>H</sub> (1 C <sub>2</sub> C <sub>1</sub> C <sub>0</sub> ) | Nibble Y <sub>H</sub> (P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> ) |

|-------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| End of Line | 1000 <sub>2</sub> (8 <sub>H</sub> )                                     | 0000 <sub>2</sub> (0 <sub>H</sub> )                                                  |

Table 5.2 : Embedded Line Codes

# **Commercial In Confidence**

| Line Code                  | Nibble X <sub>H</sub> (1 C <sub>2</sub> C <sub>1</sub> C <sub>0</sub> ) | Nibble Y <sub>H</sub> (P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> ) |

|----------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Blank Line (BL)            | 1001 <sub>2</sub> (9 <sub>H</sub> )                                     | 1101 <sub>2</sub> (D <sub>H</sub> )                                                  |

| Black line (BK)            | 1010 <sub>2</sub> (A <sub>H</sub> )                                     | 1011 <sub>2</sub> (B <sub>H</sub> )                                                  |

| Visible Line (VL)          | 1011 <sub>2</sub> (B <sub>H</sub> )                                     | 0110 <sub>2</sub> (6 <sub>H</sub> )                                                  |

| Start of Even Field (SOEF) | 1100 <sub>2</sub> (C <sub>H</sub> )                                     | 0111 <sub>2</sub> (7 <sub>H</sub> )                                                  |

| End of Even Field (EOEF)   | 1101 <sub>2</sub> (D <sub>H</sub> )                                     | 1010 <sub>2</sub> (A <sub>H</sub> )                                                  |

| Start of Odd Field (SOOF)  | 1110 <sub>2</sub> (E <sub>H</sub> )                                     | 1100 <sub>2</sub> (C <sub>H</sub> )                                                  |

| End of Odd Field (EOOF)    | 1111 <sub>2</sub> (F <sub>H</sub> )                                     | 0001 <sub>2</sub> (1 <sub>H</sub> )                                                  |

Table 5.2 : Embedded Line Codes

| Parity Checks  |                |                |                | Comment                                                  |

|----------------|----------------|----------------|----------------|----------------------------------------------------------|

| P <sub>3</sub> | P <sub>2</sub> | P <sub>1</sub> | P <sub>0</sub> | Comment                                                  |

| 4              | 4              | 4              | 4              | Code word un-corrupted                                   |

| 4              | 4              | 4              | 8              | P <sub>0</sub> corrupted, line code OK                   |

| 4              | 4              | 8              | 4              | P <sub>1</sub> corrupted, line code OK                   |

| 4              | 8              | 4              | 4              | P <sub>2</sub> corrupted, line code OK                   |

| 8              | 4              | 4              | 4              | P <sub>3</sub> corrupted, line code OK                   |

| 8              | 8              | 4              | 8              | C <sub>0</sub> corrupted, invert sense of C <sub>0</sub> |

| 8              | 4              | 8              | 8              | C <sub>1</sub> corrupted, invert sense of C <sub>1</sub> |

| 4              | 8              | 8              | 8              | C <sub>2</sub> corrupted, invert sense of C <sub>2</sub> |

|                | All othe       | r codes        |                | 2-bit error in code word.                                |

Table 5.3 : Detection of 1-bit and 2-bit errors in the Command Word

# 5.3 Video timing reference and status/configuration data

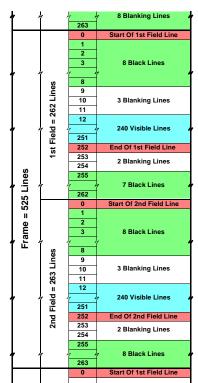

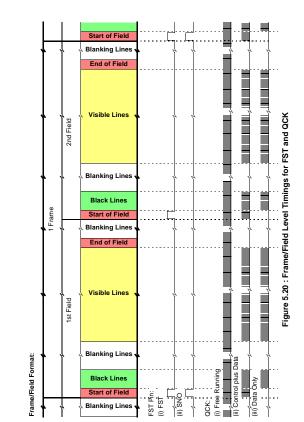

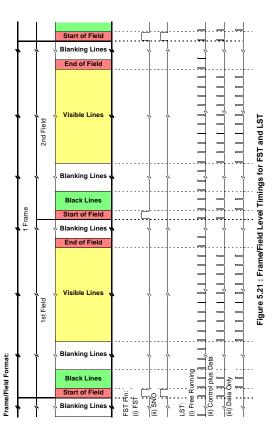

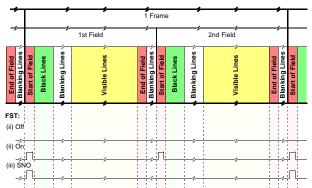

Each frame of video sequence is made up of 2 fields. Each field of data is constructed of the following

- sequence of data-lines.

1. A start-of-field line

- 2. 2 'black lines' (used for black level calibration) 3. A number of blank lines

- 4. A number active video lines

- 5. An end of field line 6. A number of blank lines.

# **Commercial In Confidence**

cd38041a.fm 08/10/98 17

# VV5409 CMOS Monochrome Sensor Datasheet (Restricted) Rev 1.0

|           |                     |      |     |     |     | 1   |     |  |

|-----------|---------------------|------|-----|-----|-----|-----|-----|--|

|           | Video Format        | NTSC |     | P/  | PAL |     | CIF |  |

|           | Border Lines        | On   | Off | On  | Off | On  | Off |  |

|           | Start-of-field Line | 1    | 1   | 1   | 1   | 1   | 1   |  |

|           | Black Lines         | 2    | 2   | 2   | 2   | 2   | 2   |  |

| 20        | Blanking Lines      | 7    | 9   | 7   | 9   | 7   | 9   |  |

| t Field   | Active Video lines  | 244  | 240 | 292 | 288 | 292 | 288 |  |

| 1st       | End of Field Line   | 1    | 1   | 1   | 1   | 1   | 1   |  |

|           | Blanking Lines      | 7    | 9   | 9   | 11  | 1   | 3   |  |

|           | Total               | 262  | 262 | 311 | 311 | 304 | 304 |  |

|           | Start-of-field Line | 1    | 1   | 1   | 1   | 1   | 1   |  |

|           | Black Lines         | 2    | 2   | 2   | 2   | 2   | 2   |  |

| 2         | Blanking Lines      | 7    | 9   | 7   | 9   | 7   | 9   |  |

| 2nd Field | Active Video lines  | 244  | 240 | 292 | 288 | 292 | 288 |  |

| 2         | End of Field Line   | 1    | 1   | 1   | 1   | 1   | 1   |  |

|           | Blanking Lines      | 8    | 10  | 10  | 12  | 1   | 3   |  |

|           | Total               | 263  | 263 | 312 | 312 | 304 | 304 |  |

Table 5.4 : Field and Frame Formats

Table 5.4 details the number of each type of data-lines for NTSC, PAL and CIF output formats when the border rows and columns, are output, and not output, on the data-bus. Each line of data starts with an embedded control sequence, which identifies the line type (as outlined in Table 5.2). The control sequence is then followed by two bytes which, except in the case of the end-of-frame line, contain a coded line number. The line number sequences starts with the start-of-frame line at 00<sub>H</sub>, and increments, one per line, until the end-of-frame line. Each line is terminated with an end-of-line embedded control sequence. The line start embedded sequences, must be used to recognise data-lines, as a number of null bytes may be inserted between data-lines.

# 5.3.1 Blank lines

In addition to padding between data-lines, actual blank data-lines may appear in the positions indicated above. These lines begin with start-of-blank-line embedded control sequences, and are constructed identically to active video lines except that they will contain only blank bytes (07  $_{\rm H}$ ).

# 5.3.2 Black line timing

The black lines (which are used for black level calibration) are identical in structure to valid video lines except that they begin with a start-of-black line sequence and contain either information from the sensor 'black lines' or blank bytes  $(07_{\rm H})$ .

# **Commercial In Confidence**

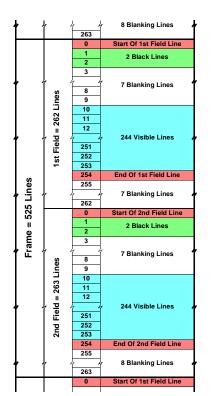

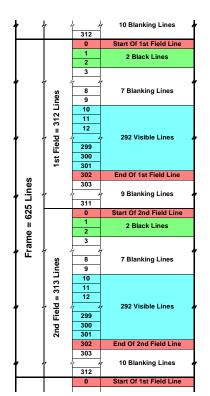

Figure 5.3 : NTSC Field and Frame Formats - Borders On, Extra Black Lines Off

# Commercial In Confidence

cd38041a.fm 08/10/98 19

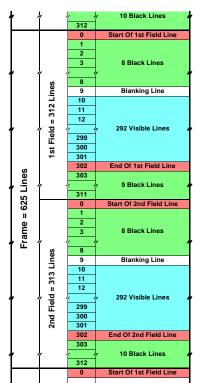

Figure 5.4 : NTSC Field and Frame Formats - Borders On, Extra Black Lines On

Commercial In Confidence

Figure 5.5 : NTSC Field and Frame Formats - Borders Off, Extra Black Lines Off

# **Commercial In Confidence**

cd38041a.fm 08/10/98 21

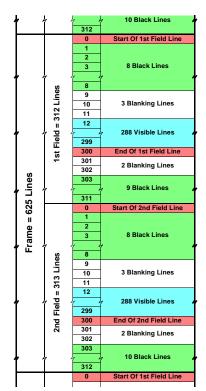

Figure 5.6 : NTSC Field and Frame Formats - Borders Off, Extra Black Lines On

# Commercial In Confidence

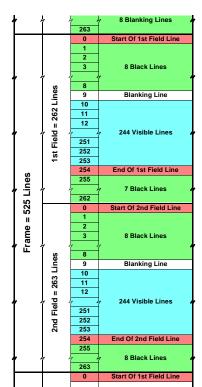

Figure 5.7 : PAL Field and Frame Formats - Borders On, Extra Black Lines Off

# **Commercial In Confidence**

cd38041a.fm 08/10/98 23

Figure 5.8 : PAL Field and Frame Formats - Borders On, Extra Black Lines On

# Commercial In Confidence

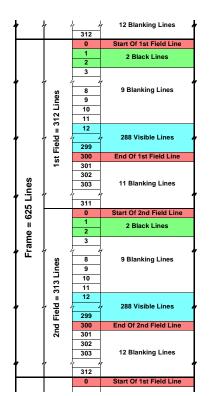

Figure 5.9 : PAL Field and Frame Formats - Borders Off, Extra Black Lines Off

# Commercial In Confidence

cd38041a.fm 08/10/98 25

Figure 5.10 : PAL Field and Frame Formats - Borders Off, Extra Black Lines On

Commercial In Confidence

|                   |                       |     | ı                       |

|-------------------|-----------------------|-----|-------------------------|

|                   |                       | 302 | End Of 2nd Field Line   |

|                   |                       | 303 | Blanking Line           |

|                   |                       | 0   | Start Of 1st Field Line |

|                   |                       | 1   | 2 Black Lines           |

|                   |                       | 2   | 2 Black Lilles          |

|                   |                       | 3   |                         |

| ,                 | ļ ģ                   | 4 . | 7 Blanking Lines        |

|                   | 1st Field = 304 Lines | 8   |                         |

|                   | =                     | 9   |                         |

|                   | 9                     | 10  |                         |

|                   | ii e                  | 11  |                         |

|                   | <u> </u>              | 12  |                         |

| ,                 | եր i <mark>e</mark>   | 9 . | 292 Visible Lines       |

|                   | #                     | 299 |                         |

| 8                 | <del>"</del>          | 300 |                         |

| 두                 |                       | 301 |                         |

| Frame = 608 Lines |                       | 302 | End Of 1st Field Line   |

| õ                 |                       | 303 | Blanking Line           |

| ı                 |                       | 0   | Start Of 1st Field Line |

| <u>o</u>          |                       | 1   | 2 Black Lines           |

| 듩                 |                       | 2   |                         |

| Ë                 |                       | 3   |                         |

| , –               | 4 s                   | 4 1 | 7 Blanking Lines        |

|                   | ۽ ا                   | 8   |                         |

|                   | 14                    | 9   |                         |

|                   | 2nd Field = 304 Lines | 10  |                         |

|                   | Ш                     | 11  |                         |

|                   | 1 8                   | 12  |                         |

| ,                 | 々正                    | 4 , | 292 Visible Lines       |

|                   | 2                     | 299 |                         |

|                   | 7                     | 300 |                         |

|                   |                       | 301 |                         |

|                   |                       | 302 | End Of 1st Field Line   |

|                   |                       | 303 | Blanking Line           |

|                   |                       | 0   | Start Of 1st Field Line |

|                   | 1                     | 1   | I .                     |

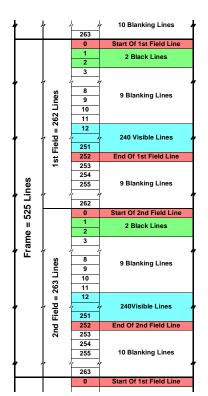

Figure 5.11 : CIF Field and Frame Formats - Borders On, Extra Black Lines Off

| ı                 | 1                     |     |                         |  |

|-------------------|-----------------------|-----|-------------------------|--|

|                   |                       | 302 | End Of 2nd Field Line   |  |

|                   |                       | 303 | Black Line              |  |

|                   |                       | 0   | Start Of 1st Field Line |  |

|                   |                       | 1   |                         |  |

|                   |                       | 2   |                         |  |

|                   |                       | 3   | 8 Black Lines           |  |

| ł                 | 4 s                   | 4 1 | 7                       |  |

|                   | <u>≅</u> .            | 8   |                         |  |

|                   | 1st Field = 304 Lines | 9   | Blanking Line           |  |

|                   | 9                     | 10  |                         |  |

|                   | ii                    | 11  |                         |  |

|                   | 9                     | 12  |                         |  |

| þ                 | ր <u>։</u>            | 4 1 | 292 Visible Lines       |  |

|                   | #                     | 299 |                         |  |

| ő                 | <del>"</del>          | 300 |                         |  |

| .≒                |                       | 301 |                         |  |

| I ≂               |                       | 302 | End Of 1st Field Line   |  |

| ığ                |                       | 303 | Black Line              |  |

| Frame = 608 Lines |                       | 0   | Start Of 1st Field Line |  |

| ė.                |                       | 1   |                         |  |

| I≣                |                       |     | 2                       |  |

| <u> </u>          |                       | 3   | 8 Black Lines           |  |

| <b>,</b>          | 4 g                   | 4 1 | 7                       |  |

|                   | 1 .≝                  | 8   |                         |  |

|                   | _                     | 9   | Blanking Line           |  |

|                   | ĕ                     | 10  |                         |  |

|                   | ii                    | 11  |                         |  |

|                   | 9                     | 12  |                         |  |

| ļ.                | ļ i                   | 4 4 | 292 Visible Lines       |  |

|                   | 2nd Field = 304 Lines | 299 |                         |  |

|                   | 2n                    | 300 |                         |  |

| I                 |                       | 301 |                         |  |

| I                 |                       | 302 | End Of 1st Field Line   |  |

| I                 |                       | 303 | Black Line              |  |

|                   |                       | _   | Start Of 1st Field Line |  |

|                   |                       | 0   | Start Of 1st Field Line |  |

Figure 5.12 : CIF Field and Frame Formats - Borders On, Extra Black Lines On

**Commercial In Confidence**

cd38041a.fm 08/10/98 27

**Commercial In Confidence**

|          | 1                     | i   |                         |  |

|----------|-----------------------|-----|-------------------------|--|

|          |                       | 302 | Blanking Lines          |  |

|          |                       | 303 | · ·                     |  |

|          |                       | 0   | Start Of 1st Field Line |  |

|          |                       | 1   | 2 Black Lines           |  |

|          |                       | 2   | 2 Black Ellics          |  |

|          |                       | 3   |                         |  |

|          | s s                   | 4 1 | ,                       |  |

|          | <u>.</u>              | 8   | 9 Blanking Lines        |  |

|          | 1st Field = 304 Lines | 9   |                         |  |

|          | , ž                   | 10  |                         |  |

|          | ii                    | 11  |                         |  |

|          | <u> </u>              | 12  |                         |  |

|          | ļ i <u>₽</u>          | 4 4 | 288 Visible Lines       |  |

| "        | - <del>-</del> z      | 299 |                         |  |

| ě        | ~                     | 300 | End Of 1st Field Line   |  |

| -        | Frame = 608 Lines     | 301 | 3 Blanking Lines        |  |

| -        |                       | 302 |                         |  |

| 09       |                       | 303 |                         |  |

| ı        |                       | 0   | Start Of 1st Field Line |  |

| <u>o</u> |                       | 1   | 2 Black Lines           |  |

| Ę        |                       | 2   |                         |  |

| i.       |                       | 3   |                         |  |

| ,  –     | es es                 | 4 1 | ,                       |  |

|          | .≅                    | 8   | 9 Blanking Lines        |  |

|          | 14                    | 9   | ·                       |  |

|          | 8                     | 10  |                         |  |

|          | Ш                     | 11  |                         |  |

|          | 문                     | 12  |                         |  |

| ,        | 2nd Field = 304 Lines | 4 1 | 288 Visible Lines       |  |

|          | 2                     | 299 |                         |  |

|          | 2                     | 300 | End Of 1st Field Line   |  |

|          |                       | 301 |                         |  |

|          |                       | 302 | 3Blanking Lines         |  |

|          | l                     | 303 |                         |  |

|          |                       | 0   | Start Of 1st Field Line |  |

Figure 5.13 : CIF Field and Frame Formats - Borders Off, Extra Black Lines Off

# Commercial In Confidence

cd38041a.fm 08/10/98 29

302 Blanking Line Black Line Start Of 1st Field Line 1st Field = 304 Lines 3 Blanking Lines 11 288 Visible Lines Frame = 608 Lines End Of 1st Field Line 301 2 Blanking Lines 302 303 Black Line Start Of 1st Field Line 8 Black Lines 2nd Field = 304 Lines 9 10 11 12 3 Blanking Lines 288 Visible Lines End Of 1st Field Line 2 Blanking Lines 302

Figure 5.14 : CIF Field and Frame Formats - Borders Off, Extra Black Lines On

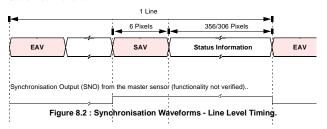

# 5.3.3 Valid video line timing

All valid video data is contained on active video lines. The pixel data appears as a continuous stream of bytes

# Commercial In Confidence

within the active lines. The pixel data may be separated from the line header and end-of-line control sequence by a number of 'blank' bytes  $(07_{H})$  e.g. when the border lines and pixels are disabled  $07_{H}$  is output in place of first 2 and last 2 pixels in a valid video line.

#### 5.3.4 Start of frame line timing

The start of frame line which begins each video field contains no video data but instead contains the contents of all the serial interface registers. This information follows the start-of-line header immediately and is terminated by an end-of-line control sequence. To ensure that no escape/sync characters appear in the sensor status/configuration information the code 07<sub>H</sub> is output after each serial interface value. Thus it takes 256 pixel lock periods (§12 system clocks) to output all 128 of the serial interface registers. The remainder of the 356 pixel periods of the video portion of the line is padded out using 07<sub>H</sub> values. The first two pixel locations are also padded with 07<sub>H</sub> characters (Figure 5.16)

If a serial interface register location is unused then 07<sub>H</sub> is output

# 5.3.5 End of frame line timing

The end of frame line which begins each video field contains no video data. Its sole purpose is to indicate the

#### 5.4 Detection of sensor using data bus state

The video processor device must have internal pull-down terminations on the data bus. On power-up a sensor will pull all data lines high for a guaranteed period. This scheme allows the presence of a sensor on the interface to be detected by the video processor on power-up, and the connection of a sensor to an already power-up interface (a 'hot' connection).

The absence of a sensor is detected by the video processor seeing more than 32 consecutive nibbles of  $0_{\rm H}$  on the data bus. On detecting the absence of a sensor, CKI, should be disabled (held low). The presence of a sensor is detected by the video processor seeing more than 32 consecutive nibbles of  $F_{\rm H}$  on the data bus. On detecting the presence of a sensor, CKI, should be enabled.

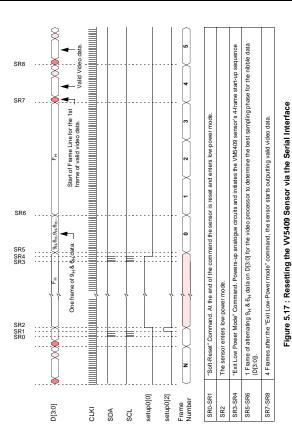

# 5.5 Resetting the Sensor Via the Serial Interface

Bit 2 of setup register 0 allows the VV5409 sensor to be reset to its power-on state via the 2-wire serial Interface. Setting this "Soft Reset" bit causes all of the serial interface registers including the "Soft Reset" bit to be reset to their default values. This "Soft Reset" leaves the sensor in low-power mode and thus an "Exit Low-Power Mode" command (Table 6.7, Section 6.6.2) must be issued via the serial interface before the sensor will start to generate video data (Figure 5.17).

# 5.6 Power-up, Low-power and Sleep modes

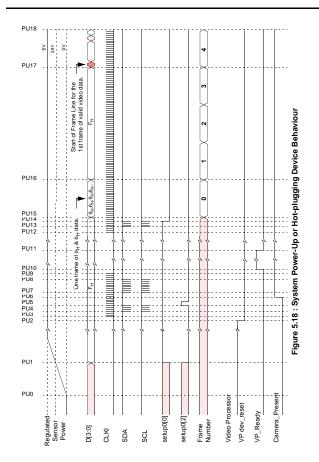

To clarify the state of the interface on power-up and in the case of a 'hot' connection of the interface cable the power-up state of the bus is defined below.

| PU0 | System Power Up or Sensor Hot Plugged                                                                        |

|-----|--------------------------------------------------------------------------------------------------------------|

| PU1 | Sensor Internal-on Reset Triggers, the sensor enters low power mode and D[3:0] is set to ${\sf F}_{\sf H}$ . |

| PU2 | Video Processor released from reset.                                                                         |

| PU3 | Video Processor enables the sensor clock, CLKI.                                                              |

Table 5.5 : System Power-Up or Hot-plugging Device Behaviour

# **Commercial In Confidence**

cd38041a fm 08/10/98 33

**Commercial In Confidence**

36

| PU4-PU5   | At least 16 CLKI clock periods after CLKI has been enabled the host controller must serving a "Soft-Reset" command to the sensor via the serial interface. This ensures that if a sensor is present then it is in low-power mode. |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PU6       | On detecting 32 consecutive ${\rm FF_H}$ (F <sub>H</sub> ) values on the data bus, the Video Processor sets the no_camera low.                                                                                                    |  |  |  |

| PU7-PU8   | Initiate the Auto-load Daisy-Chain (only where a VISION co-processor is used) to read setup data and the sensor defect map from the appropriate serial E <sup>2</sup> PROMs into the sensor and co-processor.                     |  |  |  |

| PU9       | Video Processor disables the sensor clock, CLKI.                                                                                                                                                                                  |  |  |  |

| PU10      | Video Processor generates the VP_Ready interrupt.                                                                                                                                                                                 |  |  |  |

| PU11      | The host software services the VP_Ready interrupt.                                                                                                                                                                                |  |  |  |

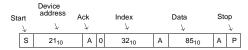

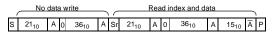

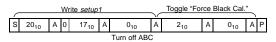

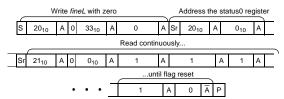

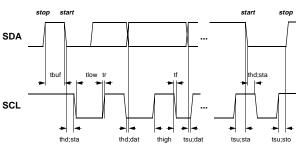

| PU12      | Host issues command to remove sensor from low-power mode. co-processor/host controller enables the sensor clock, CLKI.                                                                                                            |  |  |  |