# FET BIAS CONTROLLER WITH POLARISATION SWITCH AND TONE DETECTION

### ZNBG3115 ZNBG3116

#### **ISSUE 1 - JUNE 2001**

#### **DEVICE DESCRIPTION**

The ZNBG series of devices are designed to meet the bias requirements of GaAs and HEMT FETs commonly used in satellite receiver LNBs, PMR, cellular telephones etc. with a minimum of external components.

With the addition of two capacitors and a resistor the devices provide drain voltage and current control for three external grounded source FETs, generating the regulated negative rail required for FET gate biasing whilst operating from a single supply. This negative bias, at -2.8 volts, can also be used to supply other external circuits.

The ZNBG3115/16 includes bias circuits to drive up to three external FETs. A control input to the device selects either one of two FETs as operational, the third FET is permanently active. This feature is normally used as an LNB polarisation switch. Also specific to Universal LNB applications is the 22kHz tone detection and logic output feature which is used to enable high and low band frequency switching.

The ZNBG3115/16 has been designed to cope with DiSEqC<sup>™</sup> ready set top boxes and rejects all transients from channel switching.

Drain current setting of the ZNBG3115/16 is user selectable over the range 0 to 15mA, this is achieved with addition of a single resistor. The series also offers the choice of drain voltage to be set for the FETs, the 3115 gives 2.2 volts drain whilst the 3116 gives 2 volts.

These devices are unconditionally stable over the full working temperature with the FETs in place, subject to the inclusion of the recommended gate and drain capacitors. These ensure RF stability and minimal injected noise.

It is possible to use less than the devices full complement of FET bias controls, unused drain and gate connections can be left open circuit without affecting operation of the remaining bias circuits.

To protect the external FETs the circuits have been designed to ensure that, under any conditions including power up/down transients, the gate drive from the bias circuits cannot exceed the range -3.5V to 1V. Additionally each stage has its own individual current limiter. Furthermore if the negative rail experiences a fault condition, such as overload or short circuit, the drain supply to the FETs will shut down avoiding excessive current flow.

The ZNBG3115/16 are available in QSOP16 and QSOP20 for the minimum in device size. Device operating temperature is -40 to 80°C to suit a wide range of environmental conditions.

#### FEATURES

- Provides bias for GaAs and HEMT FETs

- Drives up to three FETs

- Dynamic FET protection

- Drain current set by external resistor

- Regulated negative rail generator requires only 2 external capacitors

- Choice in drain voltage

- Wide supply voltage range

- Polarisation switch for LNBs

- 22kHz tone detection for band switching

- Tone detector ignores unwanted signals

- Support fr MIMIC, FET and Bipolar local oscillator devices

- Compliant with ASTRA control specifications

- QSOP 16 and 20 surface mount packages

#### APPLICATIONS

- Satellite receiver LNBs

- Private mobile radio (PMR)

- Cellular telephones

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                                        | -0.6V to 12V   | Power Dissipation | (T <sub>amb</sub> = 25°C) |

|-------------------------------------------------------|----------------|-------------------|---------------------------|

| Supply Current                                        | 100mA          | QSOP16            | 500mW                     |

| Input Voltage (V <sub>POL</sub> )                     | 25V Continuous | QSOP20            | 500mW                     |

| Drain Current (per FET)<br>(set by R <sub>CAL</sub> ) | 0 to 15mA      |                   |                           |

| Operating Temperature                                 | -40 to 80°C    |                   |                           |

| Storage Temperature                                   | -50 to 85°C    |                   |                           |

## ELECTRICAL CHARACTERISTICS. TEST CONDITIONS (Unless otherwise stated): $T_{amb}$ = 25°C, $V_{CC}$ =5V, $I_D$ =10mA ( $R_{CAL}$ =33k )

| SYMBOL                             | PARAMETER                                     | CONDITIONS                                                                                                                                                                                                                                                                                 | LIMITS |                             |                            | UNITS                      |

|------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------|----------------------------|----------------------------|

|                                    |                                               |                                                                                                                                                                                                                                                                                            | MIN.   | TYP.                        | MAX.                       |                            |

| V <sub>CC</sub>                    | Supply Voltage                                |                                                                                                                                                                                                                                                                                            | 5      |                             | 10                         | V                          |

| I <sub>CC</sub>                    | Supply Current                                | $      I_{D1} = I_{D2} (or I_{D12}) = I_{D3} = 0       I_{D1} = 0, I_{D2} (or I_{D12}) = I_{D3} = 10 mA, V_{POL} = 14 V       I_{D2} = 0, I_{D1} (or I_{D12}) = I_{D3} = 10 mA, V_{POL} = 15.5 V       I_{D1} and I_{D3} = 0, I_{LB} = 10 mA       I_{D1} and I_{D3} = 0, I_{HB} = 10 mA $ |        | 8.5<br>28<br>28<br>18<br>18 | 15<br>35<br>35<br>25<br>25 | mA<br>mA<br>mA<br>mA<br>mA |

| V <sub>SUB</sub>                   | Substrate Voltage                             | (Internally generated) I <sub>CSUB</sub> =0<br>I <sub>CSUB</sub> =-200μA                                                                                                                                                                                                                   | -3.05  | -2.8                        | -2.55<br>-2.4              | V<br>V                     |

| E <sub>ND</sub><br>E <sub>NG</sub> | Output Noise<br>Drain Voltage<br>Gate Voltage | $C_G$ =4.7nF, $C_D$ =10nF<br>$C_G$ =4.7nF, $C_D$ =10nF                                                                                                                                                                                                                                     |        |                             | 0.02<br>0.005              | Vpkpk<br>Vpkpk             |

| f <sub>O</sub>                     | Oscillator Frequency                          |                                                                                                                                                                                                                                                                                            | 180    | 330                         | 800                        | kHz                        |

| SYMBOL                                                   | PARAMETER                                                     | CONDITIONS                                                                                                                                                                                         |                     | LIMITS                 |                     | UNITS       |

|----------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|---------------------|-------------|

|                                                          |                                                               |                                                                                                                                                                                                    | MIN.                | TYP.                   | MAX.                |             |

| GATE CH                                                  | IARACTERISTICS                                                |                                                                                                                                                                                                    |                     |                        |                     |             |

| I <sub>GO</sub>                                          | Output Current Range                                          |                                                                                                                                                                                                    | -30                 |                        | 2000                | А           |

|                                                          |                                                               | I <sub>Dx</sub> V <sub>POL</sub> I <sub>GOx</sub><br>(mA) (V) (A)                                                                                                                                  |                     |                        |                     |             |

| V <sub>G10</sub><br>V <sub>G1L</sub><br>V <sub>G1H</sub> | Output Voltage<br>Gate 1 Off<br>Low<br>High                   | I <sub>D1</sub> =0 V <sub>POL</sub> =14 I <sub>GO1</sub> =-10<br>I <sub>D1</sub> =12 V <sub>POL</sub> =15.5 I <sub>GO1</sub> =-10<br>I <sub>D1</sub> =8 V <sub>POL</sub> =15.5 I <sub>GO1</sub> =0 | -2.5<br>-2.5<br>0.4 | -2.25<br>-2.25<br>0.75 | -2.0<br>-2.0<br>1.0 | V<br>V<br>V |

| V <sub>G2O</sub><br>V <sub>G2L</sub><br>V <sub>G2H</sub> | Output Voltage<br>Gate 2 Off<br>Low<br>High                   | I <sub>D2</sub> =0 V <sub>POL</sub> =15.5 I <sub>GO2</sub> =-10<br>I <sub>D2</sub> =12 V <sub>POL</sub> =14 I <sub>GO2</sub> =-10<br>I <sub>D2</sub> =8 V <sub>POL</sub> =14 I <sub>GO2</sub> =0   | -2.5<br>-2.5<br>0.4 | -2.25<br>-2.25<br>0.75 | -2.0<br>-2.0<br>1.0 | V<br>V<br>V |

| V <sub>G3L</sub><br>V <sub>G3H</sub>                     | Output Voltage<br>Gate 3 Low<br>High                          | I <sub>D3</sub> =12 I <sub>GO3</sub> =-10<br>I <sub>D3</sub> =8 I <sub>GO3</sub> =0                                                                                                                | -3.0<br>0.4         | -2.75<br>0.75          | -2.5<br>1.0         | V<br>V      |

| DRAIN C                                                  | HARACTERISTICS                                                | 1                                                                                                                                                                                                  | i                   |                        |                     |             |

| I <sub>D</sub>                                           | Current                                                       |                                                                                                                                                                                                    | 8                   | 10                     | 12                  | mA          |

| I <sub>Drng</sub>                                        | Current range                                                 | Set by R <sub>cal</sub>                                                                                                                                                                            | 0                   |                        | 15                  | mA          |

| ΔI <sub>DV</sub><br>ΔI <sub>DV</sub>                     | Current Change<br>with V <sub>CC</sub><br>with T <sub>j</sub> | V <sub>CC</sub> = 5 to 10V<br>T <sub>j</sub> =-40 to +80°C                                                                                                                                         |                     | 0.5<br>0.05            |                     | %/V<br>%/°C |

| V <sub>D1</sub>                                          | Drain 1 Voltage: High<br>ZNBG3115<br>ZNBG3116                 | I <sub>D1</sub> =10mA, V <sub>POL</sub> =15.5V<br>I <sub>D1</sub> =10mA, V <sub>POL</sub> =15.5V                                                                                                   | 2.0<br>1.8          | 2.2<br>2.0             | 2.4<br>2.2          | V<br>V      |

| V <sub>D2</sub>                                          | Drain 2 Voltage: High<br>ZNBG3115<br>ZNBG3116                 | I <sub>D2</sub> =10mA, V <sub>POL</sub> =14V<br>I <sub>D2</sub> =10mA, V <sub>POL</sub> =14V                                                                                                       | 2.0<br>1.8          | 2.2<br>2.0             | 2.4<br>2.2          | V<br>V      |

| V <sub>D3</sub>                                          | Drain 3 Voltage: High<br>ZNBG3115<br>ZNBG3116                 | I <sub>D3</sub> =10mA, V <sub>POL</sub> =15.5V<br>I <sub>D3</sub> =10mA, V <sub>POL</sub> =15.5V                                                                                                   | 2.0<br>1.8          | 2.2<br>2.0             | 2.4<br>2.2          | V<br>V      |

| $\Delta V_{DV}$<br>$\Delta V_{DT}$                       | Voltage Change<br>with V <sub>CC</sub><br>with T <sub>j</sub> | V <sub>CC</sub> = 5 to 10V<br>T <sub>j</sub> =-40 to +80°C                                                                                                                                         |                     | 0.5<br>50              |                     | %/V<br>ppm  |

| <sub>L1</sub><br>  <sub>L2</sub>                         | Leakage Current<br>Drain 1 †<br>Drain 2 †                     | V <sub>D1</sub> =0.5V, V <sub>POL</sub> =14V<br>V <sub>D2</sub> =0.5V, V <sub>POL</sub> =15.5V                                                                                                     |                     |                        | 10<br>10            | A<br>A      |

tQSOP20 only

| SYMBOL PARAMETER |                                                                 | CONDITIONS                                                                            | CONDITIONS                                     |               | LIMITS   |                      |        |

|------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------|---------------|----------|----------------------|--------|

|                  |                                                                 |                                                                                       |                                                | MIN.          | TYP.     | MAX.                 | 1      |

| TONE DE          | TECTION CHARA                                                   | CTERISTICS                                                                            |                                                |               |          |                      |        |

| V <sub>OUT</sub> | <b>Filter Amplifier</b><br>Bias Voltage <sup>5</sup>            | I <sub>fin</sub> =0                                                                   |                                                | 1.75          | 1.95     | 2.15                 | v      |

| F <sub>inz</sub> | Input Impedance                                                 | V <sub>FIN</sub> =100mV p/p                                                           |                                                |               | 150      |                      | Ω      |

| AG               | Amplifier Gain                                                  | V <sub>FIN</sub> =100mV p/p                                                           |                                                |               | 30       |                      | V/mA   |

| FV <sub>T</sub>  | V Threshold⁵                                                    |                                                                                       |                                                | 100           | 170      | 350                  | mV p/p |

| V <sub>LOV</sub> | <b>Output Stage</b><br>L <sub>OV</sub> Volt. Range <sup>6</sup> | I <sub>L</sub> =50mA(L <sub>B</sub> or H <sub>B</sub> )                               |                                                | -0.5          |          | V <sub>CC</sub> -1.8 | v      |

| I <sub>LOV</sub> | L <sub>OV</sub> Bias Current                                    | V <sub>LOV</sub> =0                                                                   |                                                | 0.02          | 0.15     | 1.0                  | μA     |

| V <sub>LBL</sub> | L <sub>B</sub> Output Low                                       | $V_{LOV}=0$ $I_L=0$<br>RIb-Csub=1M $\Omega$                                           | Enabled <sup>6</sup>                           | -3.05         | -2.80    | -2.55                | v      |

|                  |                                                                 | V <sub>LOV</sub> =3V I <sub>L</sub> =0mA<br>RIb-Csub=1MΩ                              | Enabled <sup>6</sup>                           | -0.01         | 0        | 0.1                  | V      |

| V <sub>LBH</sub> | L <sub>B</sub> Output High                                      | V <sub>LOV</sub> =0 I <sub>L</sub> =10mA<br>V <sub>LOV</sub> =3V I <sub>L</sub> =50mA | Disabled <sup>6</sup><br>Disabled <sup>6</sup> | -0.025<br>2.9 | 0<br>3.0 | 0.025<br>3.1         | V<br>V |

| V <sub>HBL</sub> | H <sub>B</sub> Output Low                                       | V <sub>LOV</sub> =0 I <sub>L</sub> =0<br>Rhb-Csub=1MΩ                                 | Disabled <sup>6</sup>                          | -3.05         | -2.80    | -2.55                | v      |

|                  |                                                                 | $V_{LOV}=3V I_{L}=0$<br>Rhb-Gnd=1M $\Omega$                                           | Disabled <sup>6</sup>                          | -0.01         | 0        | 0.1                  | V<br>V |

| V <sub>HBH</sub> | H <sub>B</sub> Output High                                      | V <sub>LOV</sub> =0 I <sub>L</sub> =10mA<br>V <sub>LOV</sub> =3V I <sub>L</sub> =50mA | Enabled <sup>6</sup><br>Enabled <sup>6</sup>   | -0.025<br>2.9 | 0<br>3.0 | 0.025<br>3.1         | V<br>V |

| POLARIT          | Y SWITCH CHARA                                                  | CTERISTICS                                                                            |                                                |               |          |                      |        |

| 1                | Input Current                                                   | V 2EV (Applied)                                                                       | · <b>D O</b> LON                               | 10            | 25       | 10                   |        |

| I <sub>POL</sub>  | Input Current     | $V_{POL}$ =25V (Applied via $R_{POL}$ =2k $\Omega$ )                       | 10 | 25    | 40   | μA |

|-------------------|-------------------|----------------------------------------------------------------------------|----|-------|------|----|

| V <sub>TPOL</sub> | Threshold Voltage | $V_{\text{POL}}\text{=}25V$ (Applied via $R_{\text{POL}}\text{=}2k\Omega)$ | 14 | 14.75 | 15.5 | V  |

| T <sub>SPOL</sub> | Switching Speed   | $V_{\text{POL}}\text{=}25V$ (Applied via $R_{\text{POL}}\text{=}2k\Omega)$ |    |       | 100  | ms |

NOTES:

1. The negative bias voltages specified are generated on-chip using an internal oscillator. Two external capacitors, CNB and CSUB, of 47nF are required for this purpose. 2. The characteristics are measured using an external reference resistor R<sub>CAL</sub> of value 33k wired from pins R<sub>CAL</sub> to ground.

3. Noise voltage is not measured in production.

4. Noise voltage measurement is made with FETs and gate and drain capacitors in place on all outputs. CG, 4.7nF, are connected between gate outputs and ground, C<sub>D</sub>, 10nF, are connected between drain outputs and ground.

5. These parameters are linearly related to Vcc

6. These parameters are measured using Test Circuit 1

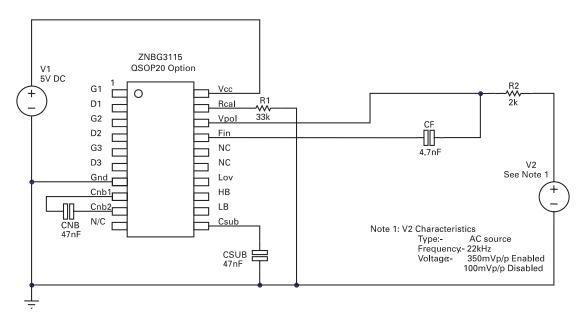

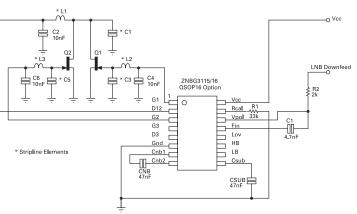

#### **TEST CIRCUIT 1**

Note: Same circuit used for QSOP16 option but with adjusted pinout.

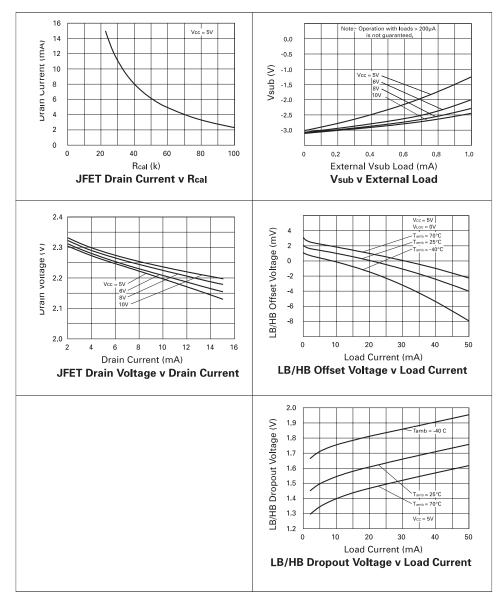

### **TYPICAL CHARACTERISTICS**

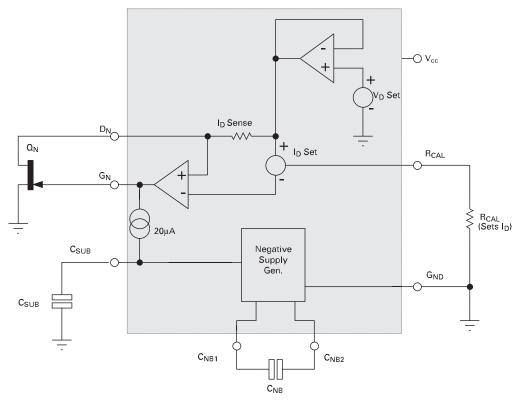

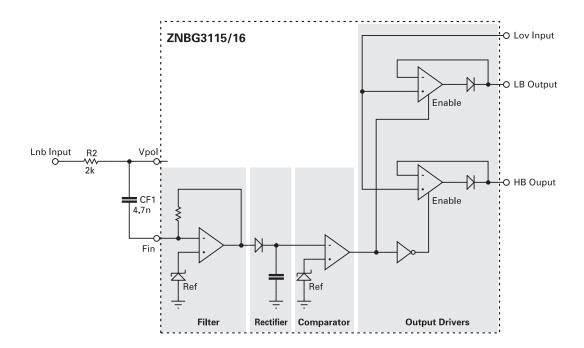

#### **FUNCTIONAL DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

The ZNBG devices provide all the bias requirements for external FETs, including the generation of the negative supply required for gate biasing, from the single supply voltage. The diagram above shows a single stage from the ZNBG series. The ZNBG3115/16 contains 3 such stages. The negative rail generator is common to both devices.

The drain voltage of the external FET  $\Omega_N$  is set by the ZNBG device to its normal operating voltage. This is determined by the on board  $V_D$  Set reference, for the ZNBG3115 this is nominally 2.2 volts whilst the ZNBG3116 provides nominally 2 volts.

The drain current taken by the FET is monitored by the low value resistor ID Sense. The amplifier driving the gate of the FET adjusts the gate voltage of  $Q_N$  so that the drain current taken matches the current called for by an external resistor  $R_{CAL}$ .

Since the FET is a depletion mode transistor, it is often necessary to drive its gate negative with respect to ground to obtain the required drain current. To provide this capability powered from a single positive supply, the device includes a low current negative supply generator. This generator uses an internal oscillator and two external capacitors,  $C_{NB}$  and  $C_{SUB}$ .

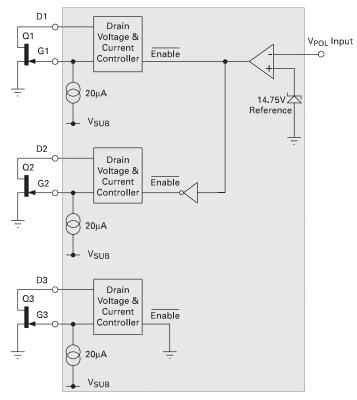

The following schematic shows the function of the  $V_{POL}$  input. Only one of the two external FETs numberd Q1 and Q2 are powered at any one time, their selection is controlled by the input  $V_{POL}$ . This input is designed to be wired to the power input of the LNB via a high value (10k) resistor. With the input voltage of the LNB set at or below 14V, FET Q2 will be enabled. With the input voltage at or above 15.5V, FET Q1 will be enabled. The disabled FET has its gate driven low and its drain terminal is switched open circuit. It is permissible to connect the drain pins D1 and D2 together if required by the application circuit; this is done internally in the QSOP16 version. FET number Q3 is always active regardless of the voltage applied to  $V_{POL}$ .

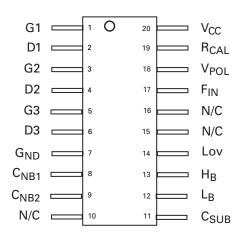

**QSOP 20 Version**

#### **Control Input Switch Function**

| Input Sense       | Polarisation | Select |

|-------------------|--------------|--------|

| ≤ 14 volts        | Vertical     | FET Q2 |

| $\geq$ 15.5 volts | Horizontal   | FET Q1 |

For many LNB applications, tone detection for band switching is required. The ZNBG3115/16 includes all the circuitry necessary to detect the presence of a 22kHz tone modulated on the supply input to the LNB. The main elements of the detector are an op-amp, a rectifier/smoother and a comparitor. The op-amp has a pre-set internal feedback resistor so that just a simple RC network wired to the input gives user defined gain and low frequency cut filter characteristics. The RC network components also serve two other purposes. The resistor provides overvoltage protection for the Vpol pin and the capacitor minimises tone interference of the Vpol threshold. The upper frequency roll-off of the op-amp has been set internally at above 100kHz to allow the amplifier to be used with other common tone switch frequencies.

The rectifier/smoother/comparitor function is provided by a complex propriety circuit that allows the ZNBG3115/16 to reliably detect wanted tones whilst ignoring low frequency square wave switch box signals, DiSEqC<sup>™</sup> bursts and supply switching transients common when using DiSEqC-2<sup>™</sup> ready set-top boxes. This is all achieved without the need for any further external components. The threshold of the comparitor is supply dependent, hence the gain of the preceding op-amp must be adjusted in line with supply voltage. See the table below for recommended values for 22kHz detection, given for a range of supplies.

#### Table\_1

| Filter     | Supply Voltage (Vcc) |       |       |      |      |      |

|------------|----------------------|-------|-------|------|------|------|

| Components | 5V                   | 6V    | 7V    | 8V   | 9V   | 10V  |

| Cf         | 4.7nF                | 4.7nF | 4.7nF | 10nF | 10nF | 10nF |

| Rvpol (R2) | 2k                   | 1.8k  | 1.5k  | 1.3k | 1.1k | 1.0k |

Note: Optimised for F(tone) = 22kHz.

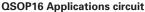

#### **APPLICATIONS CIRCUIT**

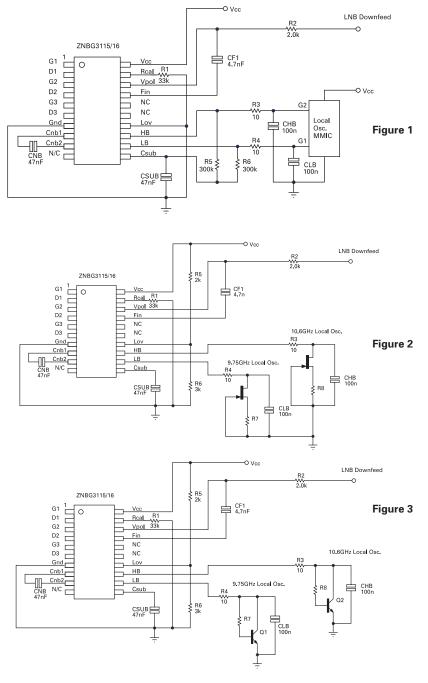

The diagrams below show partial application circuits for the ZNBG series showing all external components required for appropriate biasing. The bias circuits are unconditionally stable over the full temperature range with the associated FETs and gate and drain capacitors in circuit.

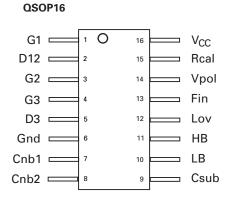

To minimise board space the ZNBG3115/3116 is offered in a QSOP16 package. To reduce the pin count Drain 1 and Drain 2 have been internally connected. This is possible because only one of the two bias stages can biased at one time. The QSOP16 offers a 40% reduction in size over the QSOP20 version.

Capacitors C2 and C4 ensure that residual power supply and substrate generator noise is not allowed to affect other external circuits which may be sensitive to RF interference. They also serve to suppress any potential RF feedthrough between stages via the ZNBG device. These capacitors are required for all stages used. Values of

10nF and 4.7nF respectively are recommended however this is design dependent and any value between 1nF and 100nF could be used.

The capacitors  $C_{NB}$  and  $C_{SUB}$  are an integral part of the ZNBGs negative supply generator. The negative bias voltage is generated on-chip using an internal oscillator. The required value of capacitors  $C_{NB}$  and  $C_{SUB}$  is 47nF. This generator produces a low current supply of approximately -3 volts. Although this generator is intended purely to bias the external FETs, it can be used to power other external circuits via the  $C_{SUB}$  pin.

Resistor R<sub>CAL</sub> sets the drain current at which all external FETs are operated. If any bias control circuit is not required, its related drain and gate connections may be left open circuit without affecting the operation of the remaining bias circuits.

The ZNBG devices have been designed to protect the external FETs from adverse operating conditions. With a JFET connected to any bias circuit, the gate output voltage of the bias circuit can not exceed the range -3.0V to 1V under any conditions, including powerup and powerdown transients. All the bias stages include drain currents limits which work independently in each stage. Should the negative bias generator be shorted or overloaded so that the drain current of the external FETs can no longer be controlled, the drain supply to FETs is shut down to avoid damage to the FETs by excessive drain current.

**QSOP20** Applications circuit

#### **APPLICATIONS INFORMATION(cont)**

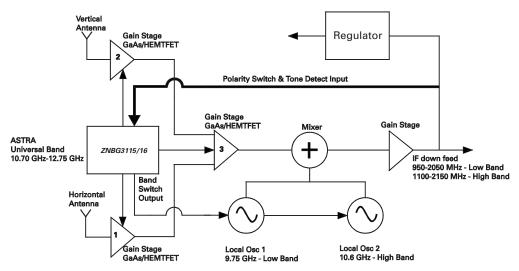

The following block diagram shows the main section of an LNB designed for use with the Astra series of satellites. The ZNBG3115/16 is the core bias and control element of this circuit. The ZNBG provides the negative rail, FET bias control, polarisation switch control, tone detection and band switching with the minimum of external components. Compared to other discrete component solutions the ZNBG circuit reduces component count and overall size required.

#### Single Universal LNB Block Diagram

Tone detection and band switching is provided on the ZNBG3115/16 devices. The following diagrams describes how this feature operates in an LNB and the external components required. The presence or absence of a 22kHz tone applied to pin  $F_{IN}$  enables one of two outputs,  $L_B$  and  $H_B$ . A tone present enables  $H_B$  and tone absent enables  $L_B$ . The  $L_B$  and  $H_B$  outputs are designed to be compatible with both MMIC and discrete (bipolar or FET) local oscillator applications, selected by pin  $L_{OV}$ . Referring to Figure 1 wiring pin  $L_{OV}$  to ground will force  $L_B$  and  $H_B$  to switch between -2.6V (disabled) and 0V (enabled). Referring to Figures 2 and 3 wiring pin  $L_{OV}$  to a positive voltage source (e.g. a potential divider across  $V_{CC}$  and ground set to the required oscillator supply voltage,  $V_{OSC}$ ) will force the  $L_B$  and  $H_B$  outputs to provide the required oscillator supply,  $V_{OSC}$ , when enabled and 0V when disabled.

#### **Tone Detection Function**

| L <sub>OV</sub>  | F <sub>IN</sub> | L <sub>B</sub> | H <sub>B</sub> | L <sub>B</sub>   | H <sub>B</sub>   |

|------------------|-----------------|----------------|----------------|------------------|------------------|

| G <sub>ND</sub>  | 22kHz           | Disabled       | Enabled        | -3 volts         | G <sub>ND</sub>  |

|                  | _               | Enabled        | Disabled       | G <sub>ND</sub>  | -3 volts         |

| V <sub>osc</sub> | 22kHz           | Disabled       | Enabled        | Note 1           | V <sub>OSC</sub> |

|                  | _               | Enabled        | Disabled       | V <sub>osc</sub> | Note 1           |

Note 1: 0 volts in typical LNB applications but ependent on extenal circuits.

#### **APPLICATIONS Local Oscillator Circuits**

#### **CONNECTION DIAGRAM**

#### OSOP20

| Part Number | Package | Part Mark |

|-------------|---------|-----------|

| ZNBG3115Q16 | QSOP16  | ZNBG3115  |

| ZNBG3116Q16 | QSOP16  | ZNBG3116  |

| ZNBG3115Q20 | QSOP20  | ZNBG3115  |

| ZNBG3116Q20 | QSOP20  | ZNBG3116  |

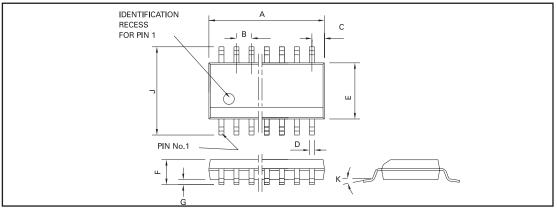

#### QSOP16

| DIM | Millimetr | res  | Inches    |       |

|-----|-----------|------|-----------|-------|

|     | MIN       | MAX  | MIN       | MAX   |

| А   | 4.80      | 4.98 | 0.189     | 0.196 |

| В   | 0.635     |      | 0.025 NC  | M     |

| С   | 0.23 REF  |      | 0.009 REF |       |

| D   | 0.20      | 0.30 | 0.008     | 0.012 |

| E   | 3.81      | 3.99 | 0.15      | 0.157 |

| F   | 1.35      | 1.75 | 0.053     | 0.069 |

| G   | 0.10      | 0.25 | 0.004     | 0.01  |

| J   | 5.79      | 6.20 | 0.228     | 0.244 |

| к   | 0°        | 8°   | 0°        | 8°    |

#### QSOP20

| DIM | Millimetr | es   | Inches    |       |

|-----|-----------|------|-----------|-------|

|     | MIN       | MAX  | MIN       | MAX   |

| А   | 8.55      | 8.74 | 0.337     | 0.344 |

| В   | 0.635     |      | 0.025 NO  | М     |

| С   | 1.47 REF  |      | 0.058 REF |       |

| D   | 0.20      | 0.30 | 0.008     | 0.012 |

| E   | 3.81      | 3.99 | 0.15      | 0.157 |

| F   | 1.35      | 1.75 | 0.053     | 0.069 |

| G   | 0.10      | 0.25 | 0.004     | 0.01  |

| J   | 5.79      | 6.20 | 0.228     | 0.244 |

| к   | 0°        | 8°   | 0°        | 8°    |

Conforms to JEDEC MO-137AD lss A

Conforms to JEDEC MO-137AB lss A

ZETERX Zetex plc. Fields New Road, Chadderton, Oldham, OL9-8NP, United Kingdom. Telephone: (44)161 622 4422 (Sales), (44)161 622 4444 (General Enquiries) Fax: (44)161 622 4420

Zetex GmbH Zetex Inc. Zetex (Asia) Ltd. These are supported by agents and distributors in 47 Mall Drive, Unit 4 Streitfeldstraße 19 3701-04 Metroplaza, Tower 1 D-81673 München Commack NY 11725 Hing Fong Road, major countries world-wide Germany USA Kwai Fong, Hong Kong Zetex plc 2001 Telefon: (49) 89 45 49 49 0 Telephone: (631) 543-7100 Telephone:(852) 26100 611 Fax: (49) 89 45 49 49 49 Fax: (631) 864-7630 Fax: (852) 24250 494 http://www.zetex.com

This publication is issued to provide outline information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned. The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.