# 2ilas

## **Z90209/203/202** TELEVISION CONTROLLERS

#### **FEATURES**

| ■ Part        | ROM<br>(KB) | RAM*<br>(Kbyte) | Speed<br>(MHz) | Package<br>Type |

|---------------|-------------|-----------------|----------------|-----------------|

| ■ Fait        |             | (NDYLE)         | (11112)        | Type            |

| Z90209        | 16          | 236             | 6 1            | 24-Pin PGA      |

| Z90203        | 16          | 236             | 6 4            | 42-Pin SDIP     |

| Z90202        | 8           | 236             | 6              | 42-Pin SDIP     |

| *General-Purp | oose        |                 |                |                 |

- 4.5V to 5.5V Operating Range

- 0°C to +70°C Temperature Range

- Low-Power Consumption

- On-Screen Display (OSD) Logic Circuits

- One 14-Bit and One 108-Bit Pulse Width Modulator (PWM) Circuits

- 20 Input/Output Lines

- Program Memory, Video RAM, and Register File Address Spaces

- Two On-Chip Counter/Timers

#### **GENERAL DESCRIPTION**

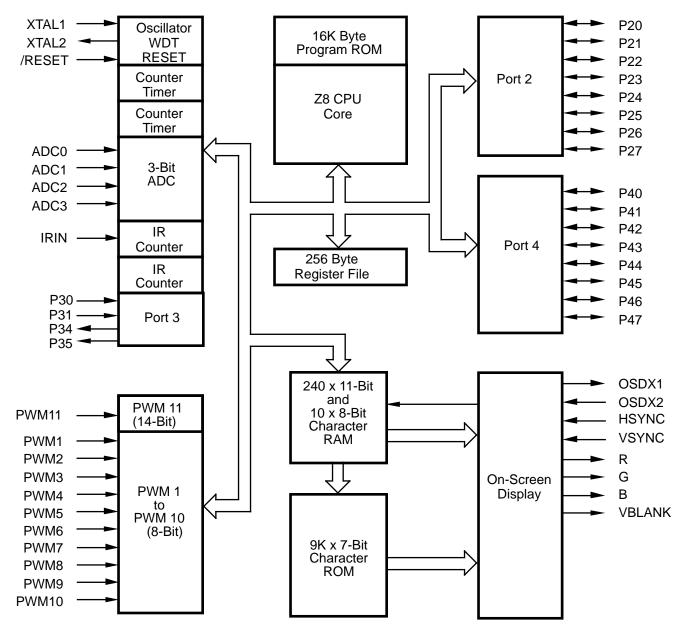

The Z9020X Family of Digital Television Controllers are cost-effective members of the Z8<sup>®</sup> single-chip microcontroller family. The devices provides an ideal performance and reliability solution for consumer and industrial television applications.

The Z90209 is the ROMless In-Circuit Emulation (ICE )Chip version of the Z90200 Digital Television Controller Family used in emulators and development boards.

The device features an 8-bit internal data path controlled by a Z8 microcontroller, On-Screen Display (OSD) logic circuits, and Pulse Width Modulators (PWM). On-chip peripherals include two register mapped I/O ports (Ports 2 and Port 3), interrupt control logic (one software, two external and three internal interrupts) and a standby mode recovery input port (Port 3, pin P30).

The OSD control circuits support ten rows by 24 columns of characters. The character color is specified by character. The OSD inter-row spacing is variable and can be programmed from 0 to 15 horizontal scan lines. The OSD is capable of displaying high resolution (14 x 18 dot pattern) characters.

A 14-bit PWM port provides enough voltage resolution for a voltage synthesizer tuning system. Ten 8-bit PWM ports are used for controlling audio signal levels to vary picture levels. Three basic address spaces, The Program Memory, Video RAM, and Register File, support a wide range of memory configurations.

For applications demanding powerful I/O capabilities, the Z9020X's dedicated input and output lines are grouped into three ports, and are configurable under software control to provide timing, status signals, parallel I/O and an address/data bus for interfacing to external memory.

To unburden the program from coping with the real-time problems such as counting/timing and data communication, the Z9020X offers two on-chip counter/timers with a large number of user selectable modes.

#### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

### **GENERAL DESCRIPTION** (Continued)

**Functional Block Diagram**