DATA SHEET

# ZR36067

# **AV PCI CONTROLLER**

# FEATURES

- Supersedes the Zoran ZR36057.

- Glueless interface to PCI bus (PCI spec. 2.1 compliant).

- Minimum interface to JPEG decoders (ZR36060, ZR36050+ZR36016), MPEG1 and DVD decoders (ZR36110, ZR36700), video decoders and video encoders.

- Bidirectional DMA transfer of compressed data up to 11M bytes/sec.

- DMA transfer of video and mask information.

- Support for fast still image compression and decompression.

- Smooth image down-scaler (up to 5-tap horizontal filter).

- On-chip pixel accurate masking.

- YUV-to-RGB converter with quantization noise reduction by error diffusion.

- APPLICATIONS

- High quality video and audio capture/playback and editing boards for PCI systems.

- Multimedia/Graphics subsystems using a secondary PCI bus.

- Video output: 15- and 16-bit RGB pixel formats, as well as 24-bit (packed and unpacked), and YUV 4:2:2.

- Hardware support for non-contiguous JPEG code buffers.

- Graceful recovery from extreme bus latencies both on video and code transfers.

- Choice of emulated interlaced video display, or single field display, to eliminate motion artifacts.

- Hardware support for simple, cost effective frame grabbing.

- I<sup>2</sup>C bus master port.

- Plug & Play support.

- 208-pin PQFP package.

- Support for Subsystem ID and Subsystem Vendor ID.

- PCI motherboards with multimedia capability.

- JPEG/MPEG1 solutions for PowerPC and Macintosh PCI systems.

# **AV PCI CONTROLLER**

# CONTENTS

| Features                                                                      |     |

|-------------------------------------------------------------------------------|-----|

| Applications                                                                  |     |

| Introduction.                                                                 |     |

| The ZR36067                                                                   |     |

| JPEG System Overview                                                          |     |

| Motion Video Compression                                                      |     |

| Motion Video Decompression                                                    | 4   |

| Still Image Compression                                                       |     |

| Still Image Decompression                                                     |     |

| Notations and Conventions                                                     |     |

| Pin Descriptions                                                              |     |

| Functional Overview                                                           |     |

| Digital Video Path                                                            | 8   |

| Digital Video Front End (VFE)                                                 |     |

| Video Input Processor                                                         |     |

| Pixel Formatting                                                              |     |

| Video DMA Controller                                                          |     |

| Display Modes.                                                                |     |

| Frame Grabbing                                                                |     |

| Overlay Control                                                               |     |

| Host Control/Communication Services                                           |     |

| Application-Specific Registers (ASRs)                                         |     |

| GuestBus PostOffice Handshaking Protocol                                      |     |

| Still Transfer Mechanism.                                                     |     |

| I <sup>2</sup> C Port                                                         |     |

| Interrupt Manager                                                             |     |

| Code DMA Controller                                                           |     |

| MPEG Mode                                                                     |     |

|                                                                               | -   |

| Interfaces                                                                    |     |

| PCI Bus Interface                                                             |     |

| Digital Video Interface                                                       |     |

| Sampling The Incoming Video                                                   |     |

| ZR36067 Connection To ZR36060 Video Interface                                 |     |

| Pixel Transfer In Still Image Compression Mode                                |     |

| Pixel Transfer In Still Image Decompression Mode                              |     |

| GuestBus Interface                                                            |     |

| Flexible GuestBus Timing                                                      |     |

| Code-Write Operations<br>Doubleword to Bytes Mapping in Code-Write Operations |     |

| PostOffice Operations                                                         |     |

| GuestBus Wait States                                                          |     |

| PostOffice Handshaking Protocol                                               |     |

| Host Writes to a Guest Device                                                 |     |

| Host Reads from a Guest Device                                                |     |

| Compression Mode Code Transactions                                            |     |

| Decompression Mode Code Transactions                                          | 16  |

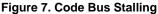

| Code Bus Stalling                                                             | 16  |

| Connecting ZR36067 To ZR36060 Host and Code Interfaces                        |     |

| I2C Bus Interface.                                                            |     |

| General Purpose I/O Pins                                                      |     |

| Interrupt Requests                                                            | .17 |

| Video Input Processor                                                             | 18  |

|-----------------------------------------------------------------------------------|-----|

| Horizontal Filter                                                                 | .18 |

| Color Space Converter                                                             |     |

| Video Output Control                                                              |     |

| Display Modes<br>Frame Grabbing                                                   |     |

| Output Pixel Organization                                                         |     |

| Graphics Overlay                                                                  | 20  |

| JPEG Code Transfer                                                                | 20  |

| The Code Buffer Table                                                             |     |

| Fragment Table                                                                    |     |

| JPEG Compression Modes                                                            |     |

| •                                                                                 |     |

| Reset                                                                             |     |

| Software Reset                                                                    |     |

| JPEG P_reset                                                                      |     |

| Subsystem ID And Subsystem Vendor ID                                              | 23  |

| Subsystem ID                                                                      |     |

| Subsystem Vendor ID                                                               | .23 |

| PCI Configuration Space Registers                                                 | 24  |

| Application-Specific Registers (ASRs)                                             | 25  |

| Video Front End Horizontal Configuration Register                                 |     |

| Video Front End Vertical Configuration Register.                                  |     |

| Video Front End, Scaler and Pixel Format Register<br>Video Display "Top" Register |     |

| Video Display "Bottom" Register                                                   |     |

| Video Stride, Status and Frame Grab Register                                      | .27 |

| Video Display Configuration Register                                              |     |

| Masking Map "Top" Register                                                        |     |

| Overlay Control Register                                                          |     |

| System, PCI and General Purpose Pins Control Register                             |     |

| General Purpose Pins and GuestBus Control Register (I)                            |     |

| MPEG Code Source Address Register                                                 |     |

| MPEG Code Transfer Control Register<br>MPEG Code Memory Pointer Register          |     |

| Interrupt Status Register                                                         |     |

| Interrupt Control Register                                                        | .31 |

| I <sup>2</sup> C-Bus Register                                                     |     |

| PostOffice Register                                                               |     |

| JPEG Process Control                                                              |     |

| Vertical Sync Parameters                                                          |     |

| Horizontal Sync Parameters                                                        |     |

| Field Horizontal Active Portion                                                   |     |

| Field Process Parameters                                                          |     |

| JPEG Code Base Address                                                            |     |

| JPEG Code FIFO Threshold                                                          |     |

| JPEG Codec Guest ID<br>GuestBus Control Register (II)                             |     |

| "Still Transfer" Register                                                         |     |

# **Z@RAN**

# **AV PCI CONTROLLER**

| Electrical Characteristics | 36 |

|----------------------------|----|

| Absolute Maximum Ratings   | 36 |

| Operating Range            | 36 |

| DC Characteristics         | 36 |

| AC Timing Specifications   | 57 |

|----------------------------|----|

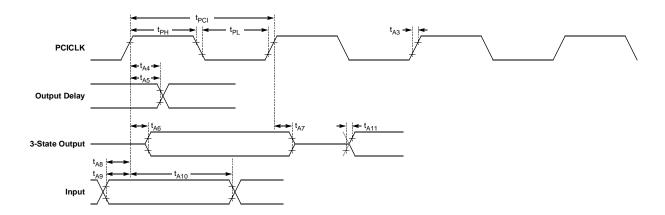

| PCI Bus Timing             | 37 |

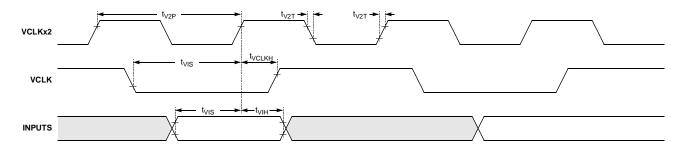

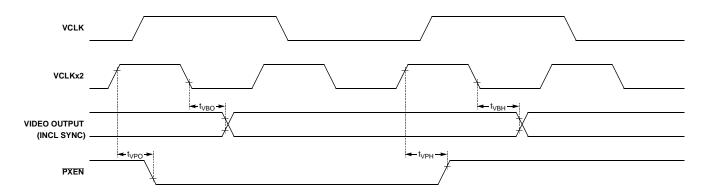

| Video Bus Timing 3         | 38 |

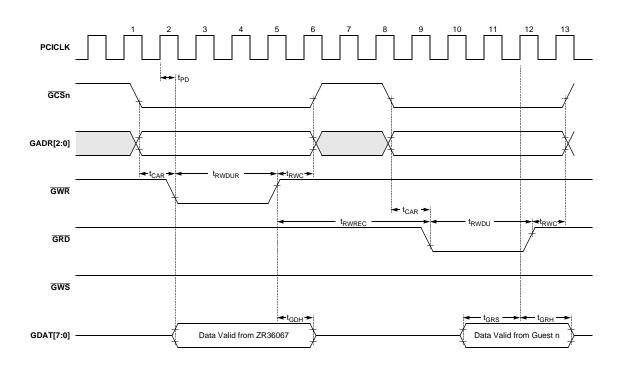

| GuestBus Timing 3          | 39 |

| Codec Bus Interface Timing | 40 |

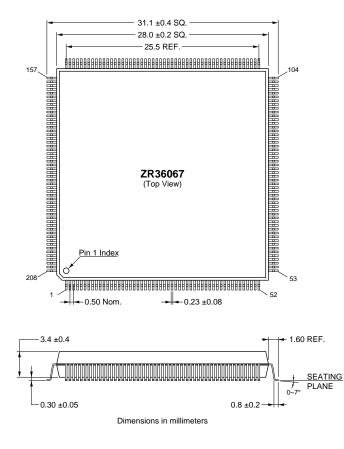

| Mechanical Data4           | 1  |

| Pinout                     | 11 |

| Dimensions 4               | 13 |

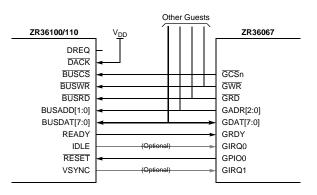

# Appendix A: ZR36110 - ZR36067 Interface 44

| ZR36110 Reset                                 | 44 |

|-----------------------------------------------|----|

| Mapping the ZR36110 on the ZR36067's GuestBus | 44 |

| ZR36110 Initialization                        | 44 |

| On-Line Commands and Status 44 | 1 |

|--------------------------------|---|

| Bitstream Transfer 44          | 1 |

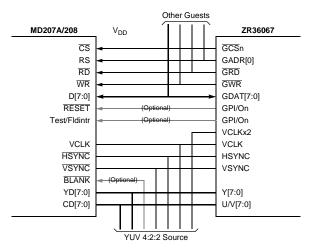

# Appendix B: MD207/MD208 - ZR36067 Interface 45

| MD207/208 Reset                                    |  |

|----------------------------------------------------|--|

| Mapping the MD207/208 on the ZR36067's GuestBus 45 |  |

| Sync Polarity 4                         | 5 |

|-----------------------------------------|---|

| Vertical Interpolation with the MD208 4 |   |

# Appendix C: Fitting the Input Size to the Required Display Window 46

| Calculating the Horizontal Parameters:4 | 7 |

|-----------------------------------------|---|

| Calculating the Vertical Parameters4    | 7 |

# **1.0 INTRODUCTION**

# 1.1 The ZR36067

The ZR36067 is a PCI adapter intended for multimedia applications on PCI systems. It supports high rate code (compressed data stream) transfer between the system memory and JPEG or MPEG processors. Simultaneously to the code transfer, the ZR36067 captures digital video, such as decompressed MJPEG (Motion JPEG), MPEG, or the output of a video decoder, and creates a scaled video window in the graphics display memory.

The ZR36067 provides the host software with full control over a large number of non-PCI multimedia devices:

- Motion JPEG Codecs ZR36050+ ZR36016, ZR36060

- · Audio codecs

- MPEG and DVD decoders ZR36110, ZR36700

- I2C devices, such as video decoders, video encoders, etc.

The ZR36067 interfaces directly to the PCI bus. As a bus master, it transfers data (e.g, JPEG compressed data) to or from the system memory, and writes digital video pixels to the graphics display memory. As a bus target, the ZR36067 reflects the host accesses onto a micro-controller-type 8-bit "Guest Bus".

The ZR36067 has a special "Still Transfer" port by means of which the host software writes (or reads) digitized video, as RGB pixels, from the system memory to (or from) the video bus. This path enables fast transfer of still images to be compressed (or decompressed) by the JPEG chip set.

The ZR36067 supersedes the ZR36057 PCI Bus Multimedia Controller and is recommended for all new designs. The ZR36067 has the same package, pinout and functions and the ZR36057, with the following exceptions:

- The ZR36067 supports programmable PCI Subsystem ID and Subsystem Vendor ID. These ID registers get their values by sampling the state of existing pins of the ZR36067 (Video bus, Guest bus and GPIO pins) at PCI Reset time. Thus, the values can be programmed by means of pull-up or pull-down resistors on these pins. Note that the Subsystem ID and Subsystem Vendor ID registers of the ZR36057 are hard wired to 0.

- Two functional bugs of the ZR36057, documented in its data sheet, have been corrected in the ZR36067 and workarounds are no longer required.

# **1.2 JPEG System Overview**

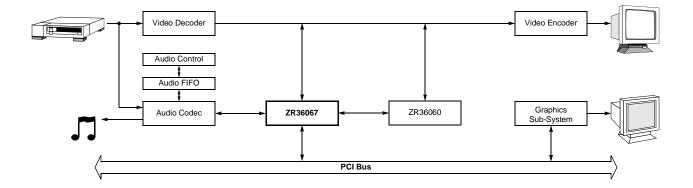

Figure 1 depicts an example of an MJPEG add-on board, using the ZR36067 and ZR36060.

The ZR36067 supports 4 basic JPEG modes of operation:

- Motion Video Compression.

- Motion Video Decompression.

- Still Image Compression.

• Still Image Decompression.

#### 1.2.1 Motion Video Compression

The video decoder directs the video in YUV 4:2:2 format, and the video synchronization signals, to the video input port of the ZR36060. The video is also transferred to the video encoder for display on a TV monitor and simultaneously to the Video Front End of the ZR36067. The ZR36067 can optionally down-scale the video, convert it to RGB, and transfer the pixels using DMA to the display memory of the host PC. In parallel, the ZR36060 performs the JPEG compression. The ZR36050 drives the JPEG code stream to the Codec Front End of the ZR36067, which transfers the compressed video fields using DMA to a system memory buffer allocated by the host.

#### 1.2.2 Motion Video Decompression

In Motion Video Decompression, the ZR36067 transfers the code stream from system memory via the ZR36067 Codec Front End to the ZR36060, using DMA. The ZR36060 decompresses the JPEG code and transfers the video to the video encoder to be displayed on a TV monitor. The ZR36060 video output is driven simultaneously to the Video Front End of the ZR36067 to be processed, as in the compression mode, and transferred using DMA to the PC display memory.

#### 1.2.3 Still Image Compression

In Still Image Compression mode an image bitmap is written by the host, pixel by pixel, through the PCI bus to the ZR36067. The ZR36067 transfers the pixels through its video bus port to the video input port of the ZR36060. The ZR36067 generates and drives the required video synchronization signals for the ZR36060 in this mode. After the first strip of 8 video lines is filled, the ZR36060 starts performing the raster-to-block operation and compressing the data, and drives the code stream to the ZR36067. The code stream is transferred using DMA to the host memory as in Motion Video Compression.

#### 1.2.4 Still Image Decompression

In Still Image Decompression mode, the ZR36067 fetches the code stream from system memory using DMA, as in Motion Video Decompression. The ZR36060 reads the compressed data from the ZR36067, decodes it and send the decompressed video to the video port of the ZR36067. From there the host software reads it out to system memory, pixel by pixel.

Note that still image decompression can also be accomplished by configuring the ZR36067 in Motion Video Decompression mode, and transferring the decompressed video to a contiguous buffer in system memory instead of the display memory. Since this has a speed advantage over Still Image Decompression mode, it is the preferred method for most applications.

#### 1.2.5 Notations and Conventions

| External signals:                | ital letters (e.g., IDSEL)                                                                                                                                                                                                                      |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Active-low mark <sup>[1]</sup> : | bar (e.g., DEVSEL)                                                                                                                                                                                                                              |  |  |  |

| Internal function units:         | bital (non-bold) letters (e.g., VFE)                                                                                                                                                                                                            |  |  |  |

| Buses:                           | _indexlsb_index (e.g., AD310)                                                                                                                                                                                                                   |  |  |  |

| Register fields:                 | msb_index:lsb_index (e.g., Mode27:16)                                                                                                                                                                                                           |  |  |  |

| Register types:                  | R - read only<br>RC - read-clear. Writing '1' clears the register bit.<br>RS - read-set. Writing '1' sets the register bit to '1'.<br>RW - read-write (contents of write can be read back)<br>W - write only (contents of read are meaningless) |  |  |  |

| Numbers:                         | Unmarked numbers are decimal (e.g., 365, 23.19). Hexadecimal numbers are marked with a '0x' prefix (e.g., 0xB000, 0x3). Binary numbers are marked with a 'b' suffix (e.g., 010b, 0000110100011b).                                               |  |  |  |

1. In this document, an overbar is used to denote active low signals. In other documents referenced herein, such as the PCI specifications, the # suffix notation is often used instead. The two forms of notation are interchangeable. Thus, for example, DEVSEL is equivalent to DEVSEL#.

# 2.0 ARCHITECTURAL OVERVIEW

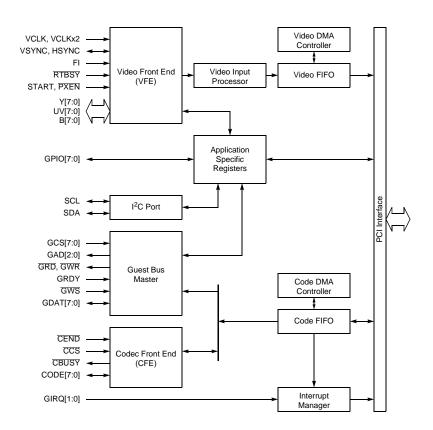

The ZR36067 architecture contains two main data paths, the video path and the code path. The incoming video is processed along the video path and transferred to the graphics display memory using PCI DMA bursts.

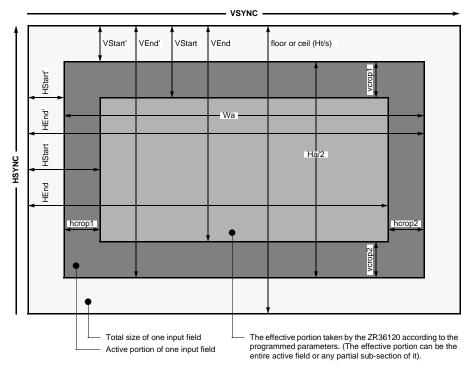

The ZR36067 Video Front End samples the video bus within a programmable active field window, defined with respect to the video synchronization signals. An optional vertical and horizontal smooth scale down can be applied, in order to support variable image sizes and variable PCI video data rate. The scaled video stream can be converted to various RGB formats. The converted pixels are packed and stored in a 256-byte Video FIFO, organized as 64 32-bit doublewords. The stored video pixels are read from the Video FIFO and transferred to the graphics display memory according to a display masking map controlled by and stored inside the ZR36067.

The Code path is bidirectional. The data flow direction depends on the mode of operation. The code stream (MPEG or JPEG) is transferred between system memory and the internal Code FIFO of the ZR36067 using PCI DMA bursts. The ZR36067 controls the transfer and addressing in both directions. The Code FIFO size is 640 bytes, organized as 160 doublewords.

In JPEG Compression modes the ZR36067 Codec Front End fills the Code FIFO. From the Code FIFO the code is transferred to the system memory, field by field.

In JPEG Decompression modes the code stream flows in the opposite direction, from the system memory to the ZR36067 Code FIFO. The Codec Front End reads out the Code FIFO byte by byte onto the Code Bus.

In MPEG Playback mode, the code stream is transferred to the ZR36067 Code FIFO from the system memory. The code bytes are read from the Code FIFO out to the Guest Bus.

The ZR36067 video and the code paths operate simultaneously while the ZR36067 arbitrates the PCI bus requests for each process.

Besides managing the Video and Code paths, the ZR36067 bridges the host CPU to peripheral devices (known as Guests). Using a dedicated handshaking mechanism (the "PostOffice" mechanism), host accesses to an internal ZR36067 register are reflected to the Guest Bus in order to enable indirect host read and write operations to the Guests.

The ZR36067 contains a dedicated "Still Transfer" port which enables data flow between the PCI interface and the Video Front End. Using a specific handshake protocol, the host software may transfer digitized video (RGB pixels) from the system memory to the Video bus, and vice versa. This path enables very fast transfer of still video images to be compressed or decompressed by the JPEG codec.

Figure 2. ZR36067 Block Diagram

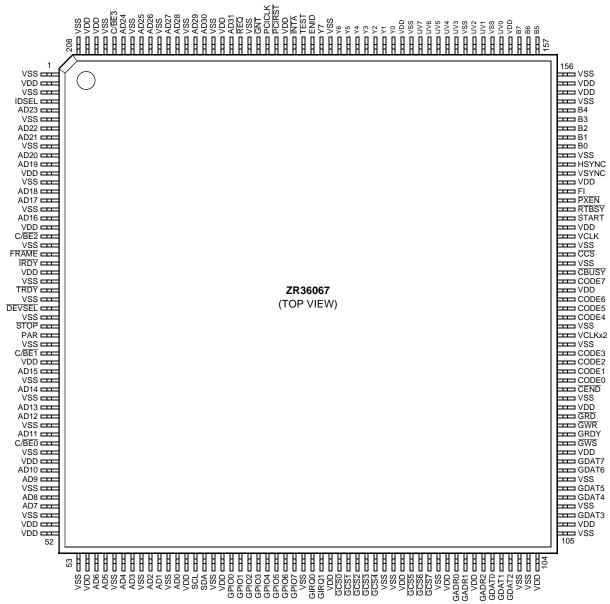

# 3.0 PIN DESCRIPTIONS

| PCI Interface (48 pinAD[31:0]C/BE[3:0]PARFRAMETRDY | 3-state<br>3-state<br>3-state<br>3-state*<br>3-state* | I/O<br>I/O<br>I/O | Multiplexed address and data bus pins.<br>Bus commands or byte enables.                                                                                                                          |  |

|----------------------------------------------------|-------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| C/BE[3:0]<br>PAR<br>FRAME                          | 3-state<br>3-state<br>3-state*                        | I/O               |                                                                                                                                                                                                  |  |

| PAR FRAME                                          | 3-state<br>3-state*                                   |                   | Bus commands or byte enables.                                                                                                                                                                    |  |

| FRAME                                              | 3-state*                                              | I/O               |                                                                                                                                                                                                  |  |

|                                                    |                                                       |                   | Even parity bit for AD310 and C/BE[3:0].                                                                                                                                                         |  |

| TRDY                                               | 3-state*                                              | I/O               | PCI cycle frame.                                                                                                                                                                                 |  |

|                                                    |                                                       | I/O               | PCI target ready indicator.                                                                                                                                                                      |  |

| IRDY                                               | 3-state*                                              | I/O               | PCI initiator ready.                                                                                                                                                                             |  |

| STOP                                               | 3-state*                                              | I/O               | Indicates a target request to stop the current data transfer.                                                                                                                                    |  |

| DEVSEL                                             | 3-state*                                              | I/O               | PCI device select, indicates that the target has decoded its address.                                                                                                                            |  |

| IDSEL                                              | I                                                     | I                 | PCI initialization device select. Used as a chip-select to the ZR36067's configuration space.                                                                                                    |  |

| REQ                                                | 3-state                                               | 0                 | PCI bus request.                                                                                                                                                                                 |  |

| GNT                                                | 3-state                                               | I                 | PCI bus grant.                                                                                                                                                                                   |  |

| PCICLK                                             | I                                                     | I                 | PCI clock.                                                                                                                                                                                       |  |

| PCIRST                                             | I                                                     | I                 | PCI reset. When active, all ZR36067 output pins are tri-stated. A low to high transition puts the ZR36067 into its power-on reset state. Minimum active low duration is 3 PCI clocks.            |  |

| INTA                                               | open drain                                            | 0                 | PCI interrupt request A. A low level on this signal requests an interrupt from the host.                                                                                                         |  |

| Digital Video Bus Int                              |                                                       | ns)               |                                                                                                                                                                                                  |  |

| Y[7:0]/R[7:0]                                      | 3-state                                               | I/O               | Luminance/Red video lines. Also used to program the low byte of Subsystem Vendor ID.                                                                                                             |  |

| UV[7:0]/G[7:0]                                     | 3-state                                               | I/O               | Chrominance/Green video lines. Also used to program the low byte of Subsystem ID.                                                                                                                |  |

| B[7:0]                                             | 3-state                                               | I/O               | Blue video lines.                                                                                                                                                                                |  |

| VCLKx2                                             | I                                                     | Ι                 | Double frequency video bus clock.                                                                                                                                                                |  |

| VCLK                                               | I                                                     | Ι                 | Digital video bus clock. Used as a qualifier to VCLKx2. Must be synchronized to VCLKx2.                                                                                                          |  |

| HSYNC                                              | 3-state                                               | I/O               | Digital video bus horizontal sync.                                                                                                                                                               |  |

| VSYNC                                              | 3-state                                               | I/O               | Digital video bus vertical sync.                                                                                                                                                                 |  |

| FI                                                 | I                                                     | I                 | Digital video bus field indicator (top/bottom).                                                                                                                                                  |  |

| PXEN                                               | 0                                                     | 0                 | Active low Pixel Enable output to the ZR36016.                                                                                                                                                   |  |

| RTBSY                                              | I                                                     | Ι                 | Active low Strip Memory Overflow/Underflow signal from the ZR36016.                                                                                                                              |  |

| START                                              | 0                                                     | 0                 | Active high Start process output to the ZR36016.                                                                                                                                                 |  |

| GuestBus Interface                                 | (25 pins)                                             |                   |                                                                                                                                                                                                  |  |

| GCS[7:0]                                           | 0                                                     | 0                 | Active low chip-select output to guest bus devices.                                                                                                                                              |  |

| GADR[2:0]                                          | 0                                                     | 0                 | Address outputs to guest bus devices.                                                                                                                                                            |  |

| GDAT[7:0]                                          | 3-state                                               | I/O               | Guest data bus. Also used to program the high byte of Subsystem Vendor ID.                                                                                                                       |  |

| GRD                                                | 0                                                     | 0                 | Active low read output to guest bus devices.                                                                                                                                                     |  |

| GWR                                                | 0                                                     | 0                 | Active low write output to guest bus devices.                                                                                                                                                    |  |

| GRDY                                               | I                                                     | Ι                 | Active high "guest ready" input, used only in MPEG code-DMA mode as a data request.                                                                                                              |  |

| GWS                                                | I                                                     | I                 | Guest Wait-State indication. Assertion of this active-low input allows the guest device to extend the GuestBus write (or read) cycle until it is capable of latching-in (or providing) the data. |  |

| GIRQ[1:0]                                          | I                                                     | I                 | Positive-edge-sensitive interrupt request inputs from one or two of the guest bus slave devices.                                                                                                 |  |

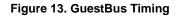

| CodecBus Interface                                 | (11 pins)                                             |                   |                                                                                                                                                                                                  |  |

| CODE[7:0]                                          | 3-state                                               | I/O               | Code Bus connected to the ZR36050.                                                                                                                                                               |  |

| CEND                                               | I                                                     | I                 | Active low End of field process indication from the ZR36050.                                                                                                                                     |  |

| CCS                                                | I                                                     | I                 | Active low Code Bus active cycle signal from the ZR36050.                                                                                                                                        |  |

| CBUSY                                              | 0                                                     | 0                 | Active low Code FIFO Busy indication to the ZR36050.                                                                                                                                             |  |

| I2C Bus Interface (2                               | I2C Bus Interface (2 pins)                            |                   |                                                                                                                                                                                                  |  |

| SDA                                                | OD                                                    | I/O               | I <sup>2</sup> C bus data                                                                                                                                                                        |  |

# 3.0 PIN DESCRIPTIONS (CONTINUED)

| Symbol            | Type <sup>[1]</sup> | Direction   | Description                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------------|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SCL               | OD                  | I/O         | I <sup>2</sup> C bus clock (qualifies for a single master operation only).                                                                                                                                                                                                                                                                                                                              |  |  |

| General Purpose I | Programmable        | Inputs/Outp | uts (8 pins)                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| GPIO[7:0]         | 3-state             | I/O         | General purpose input/output pins. After hardware or software reset all 8 pins are configured as inputs. Their logical levels are reflected as register bits. Any of the pins can be configured as output. In this state its logical level is driven by a register bit. These pins may be used to monitor or control various board-level functions. Also used to program the high byte of Subsystem ID. |  |  |

| Test Pins (2 pin) | Test Pins (2 pin)   |             |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| ENID              | Test                | I           | Used for IDD test. In normal operation must be connected to GND.                                                                                                                                                                                                                                                                                                                                        |  |  |

| TEST              | Test                | I           | Test pin used in test mode only. In normal operation must be connected to GND.                                                                                                                                                                                                                                                                                                                          |  |  |

| Power (80 pins)   |                     |             |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| GND               | ground              |             | Ground (50 pins).                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| VDD               | power               |             | Power supply (5V) (30 pins).                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                   |                     |             | Power suppry (5V) (50 pins).                                                                                                                                                                                                                                                                                                                                                                            |  |  |

1. I - standard input-only • O - standard active driver • 3-state - bidirectional I/O pin • 3-state\* - a special type of 3-state, as defined in the PCI spec. May be driven by only one PCI agent at any time • OD - open drain, may be shared by multiple drivers, as a wired-or.

# **4.0 FUNCTIONAL OVERVIEW**

The ZR36067 multimedia controller performs the following functions:

- Interfacing to a YUV 4:2:2 digital video bus (e.g., Phillips SAA7110 or SAA7111).

- Video DMA channel for burst transfers of video pixels.

- Independent horizontal and vertical downscaling of the input image, with optional horizontal filtering.

- Optional sync mastering with configurable HSYNC and VSYNC pulse widths and polarity.

- Conversion of the YUV 4:2:2 digital video input into one of the following pixel formats: YUV 4:2:2, RGB 5,6,5, RGB 5,5,5 or RGB 8,8,8 (packed or unpacked).

- Overlay support: any number of video pixels can be masked off, letting the corresponding graphics pixels appear instead of them.

- Frame grabbing.

- Two display modes: emulation of the interlaced input video, or a single field display.

- Bidirectional Code DMA transfer with support for fragmented code buffers.

- Control of the ZR36060 Motion JPEG Codec or ZR36050/ ZR36016 Motion JPEG chip set.

The ZR36067 supports digital video in CCIR 601 or square pixel formats, following either the NTSC or PAL video standard. Other non-standard input schemes are supported as well.

The functional description below follows the block diagram.

# 4.1 Digital Video Path

#### 4.1.1 Digital Video Front End (VFE)

The VFE samples the incoming YUV 4:2:2 video data and sync signals with a flexible sampling scheme, that makes it compatible with a wide variety of digital video sources. The digital input video can be cropped. The input resolutions supported by the VFE range from 32x32 to 1023x1023, in increments of one pixel.

#### 4.1.2 Video Input Processor

The chroma components of the video data are upsampled to YUV 4:4:4 format. All components are horizontally filtered. Five filtering schemes are implemented, with different parameters for chrominance and luminance samples. Horizontal and vertical downscaling is available if required. The vertical downscaling can be optimized for live video or full screen Motion JPEG playback, in which each field is independent, or for the output of an MPEG-1 decoder, which duplicates fields to produce its interlaced video output.

#### 4.1.3 Pixel Formatting

The filtered and scaled video is converted to the desired color space and packed according to the selected pixel format. YUV 4:2:2, 24-bit RGB (packed or unpacked) and 15- and 16-bit RGB are supported. An error diffusion algorithm can be applied to the RGB 5,5,5 and 5,6,5, in order to eliminate quantization artifacts on the output image.

# 4.2 Video DMA Controller

#### 4.2.1 Pixel Bursts

The packed pixels are transferred directly to the display memory (or to the system memory), using PCI DMA bursts. Both Little

# Z**@RAN**

# **AV PCI CONTROLLER**

and "Gib" Endian formats are supported where applicable (Refer to the PCI Multimedia Design Guide, Revision 1.0).

### 4.2.2 Display Modes

The display mode can be configured to either emulated interlaced video (both input fields are displayed simultaneously on the non-interlaced monitor) or single field display. The latter is appropriate for motion artifact elimination when displaying live or decompressed Motion JPEG video.

### 4.2.3 Frame Grabbing

The ZR36067 can grab video frames (scaled or non scaled), or fields, in any of the pixel formats listed above, directly into system memory, eliminating the need for memory on the add-in board.

# 4.2.4 Overlay Control

Graphics overlay is supported, in that display memory areas that are "owned" by graphics applications, may not be loaded with video pixels, allowing true windowing and overlay. The software driver prepares a masking map of the video rectangle, and the ZR36067 uses this map for masking decision, when transferring the pixels to the display memory.

# 4.3 Host Control/Communication Services

## 4.3.1 Application-Specific Registers (ASRs)

The name "application-specific" distinguishes these registers from the PCI configuration space registers. These memory mapped registers provide the host software with full control over the operation of the ZR36067. The ZR36067 claims a contiguous space of 4 KBytes in system memory.

#### 4.3.2 GuestBus

Host software control over non-PCI devices, such as a Motion JPEG codec, an MPEG decoder, a video encoder, etc., is done through the ZR36067's GuestBus. Host accesses to these "guest" devices, mapped as application specific registers inside the ZR36067, are output as GuestBus cycles. Such accesses can either use the PostOffice handshaking protocol, or the Code DMA Controller. The first method is adequate for commands, configuration data, etc., while the second method provides a faster channel, and is intended for continuous transfer of data such as a compressed bitstream.

#### 4.3.3 PostOffice Handshaking Protocol

The ZR36067 PostOffice handshaking protocol, implemented over the GuestBus, allows host accesses to relatively slow guest devices, with no degradation of the PCI bus performance.

#### 4.3.4 Still Transfer Mechanism

The ZR36067 supports a dedicated Still Transfer port, by means of which the host writes (reads) image pixels in JPEG Still Image

Compression (Decompression) mode. The Still Transfer port is mapped inside the ASR area, and a special controller interconnects this port to the ZR36067's extended video bus (24 bits RGB). The Still Transfer handshake protocol enables high rate pixels transfer between the system memory and the JPEG processor via the ZR36067.

# 4.3.5 I<sup>2</sup>C Port

A software-driven I<sup>2</sup>C port allows controlling of I<sup>2</sup>C devices.

### 4.3.6 Interrupt Manager

Interrupt requests associated with several internal and external conditions are sent to the host via the PCI bus (using INTA). Selection of interrupt originators is programmable.

# 4.4 Code DMA Controller

The ZR36067 includes a DMA channel for transferring data between the system memory and a selected device on the Code Bus or GuestBus. Two configurations are supported:

- MPEG mode. The data flow is unidirectional, from the system memory, to the ZR36067's GuestBus.

- JPEG mode. The data flow is bidirectional, and the direction is determined by the selected sub-mode. In JPEG Compression, the data flows from the Codec bus to the system memory. In JPEG Decompression, the data flows from the system memory to the Codec bus.

# 4.4.1 MPEG Mode

In MPEG mode, the data flows from the system memory to the ZR36067's GuestBus. Typically, this would be a compressed bitstream, to be decompressed by a device such as an MPEG decoder attached to the GuestBus. Other examples are sampled audio (WAV data), MIDI token stream, etc. Temporary latencies on the PCI bus or the GuestBus are handled without loss of data.

The GuestBus master simultaneously serves the PostOffice accesses and the code DMA transfers: DMA transfers are viewed as the "main" task of the GuestBus master, while any number of PostOffice requests may occasionally interrupt the DMA traffic.

The DMA controller supports both auto-initialized (cyclic) block transfers, or single block transfers. The size of the destination block in main memory can be selected out of several possible sizes, ranging from 8 KBytes up to 256 KBytes. The destination block may also be virtually split into several sub-blocks, allowing the ZR36067 to interrupt the host when a sub-block has been transferred. This feature provides the software with a means of optimizing the refill accesses according to the application requirements and the disk performance.

# 4.4.2 JPEG Modes

In the JPEG modes, the data flows between the system memory and the ZR36067's Codec bus. In JPEG Compression, from the

Codec bus to the system memory; in JPEG Decompression, from the system memory to the Codec bus.

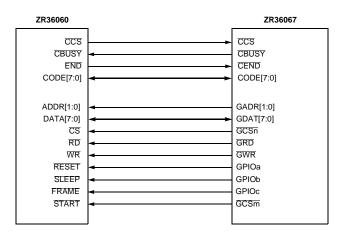

The JPEG code data inside the system memory is structured within code buffers. Each code buffer may contain a compressed field or a frame (2 fields), in accordance with a user configurable register bit.

The ZR36067 supports four code buffers, defined dynamically in a dedicated table (the Code Buffer Table) in the system memory. The actual memory of each code buffer may be fragmented. The content of each entry in the code buffer table is a pointer to a secondary Fragment Table. The fragment table contains the pointers to the allocated memory chunks (fragments). In JPEG Compression mode, the host software builds and updates the code buffer table and the fragment tables according the memory allocated by the operating system. On every JPEG field/frame process, the ZR36067 Code DMA Controller reads the fragment table pointer of the current buffer from the code buffer table, and then fills up the buffer fragments one by one.

In JPEG Decompression mode, the host software builds the code buffer table and fragment tables, and fills the fragments with the compressed field or frame. On every JPEG process, the ZR36067 Code DMA Controller retrieves the code fragments one by one, and directs them to the Codec bus.

# **5.0 INTERFACES**

# 5.1 PCI Bus Interface

In general, the ZR36067 is compatible with the PCI 2.1 specifications. As a bus master, it may initiate two types of data transfer over the PCI bus:

- Memory Write (PCI command 0111b), from the ZR36067's Video FIFO buffer to the display memory (or main memory), and from ZR36067's Code FIFO buffer to the system memory.

- Memory Read Line (PCI command 1110b), from system memory to the ZR36067's Mask Buffer<sup>[1]</sup> and from system memory to the ZR36067's Code FIFO buffer.

As a bus target, the ZR36067 responds to the following types of transfer:

| Memory Read          | (0110b) |

|----------------------|---------|

| Memory Read Line     | (1110b) |

| Memory Read Multiple | (1100b) |

| Memory Write         | (0111b) |

| Configuration Read   | (1010b) |

| Configuration Write  | (1011b) |

All other PCI commands are ignored.

Memory Read Line and Memory Read Multiple are handled exactly like Memory Read.

Normally, as a slave, the ZR36067 is intended to be accessed with single data phase cycles. However, multiple phase bursts are supported. When the ZR36067 is accessed in a burst it increments its internal (offset) address such that each data phase is routed to/from the next address location (in double-words). The ZR36067 supports byte enables, such that an access to explicit bytes is possible.

The error reporting signals, SERR and PERR, are not included in the ZR36067: as a multimedia device it is only required to report parity errors through the PCI status register.

The ZR36067 uses the INTA PCI interrupt request line.

### 5.2 Digital Video Interface

The ZR36067 interfaces to a wide spectrum of digital video devices. The Video Interface is bidirectional and two video pixel flows are supported:

- The incoming video is sampled and directed via the ZR36067's video input processor to the graphics display memory or system memory.

- The video pixels are transferred to or from the system memory using a dedicated mechanism (the Still Transfer mechanism).

The ZR36067 supports two sync signal source configuration options:

- External sync the sync signals are driven by the external video source.

- Internal sync the sync signals are generated internally and mastered by the ZR36067.

In JPEG Motion Video Compression and Decompression modes as well as in MPEG mode, the Video Interface transfers the incoming video to the ZR36067's video input processor. The sampling of the video stream is performed according to the video clocks and sync signals. In JPEG Motion Video Compression mode and in MPEG mode, the synchronization source should be external. In JPEG Motion Video Decompression mode, the synchronization source can be either external or internal.

In JPEG Still Image Compression and Decompression modes, the ZR36067 uses a dedicated mechanism (the Still Transfer mechanism) as a means for the host software to transfer pixels to or from the compression module. The Video Interface masters

<sup>1.</sup> Not shown in the block diagram.

**Z<b>@RAN**

the extended 24-bit video bus and the synchronization signals in order to drive the pixels to the ZR36016 or get them from it, as appropriate.

The following four subsections detail the four basic functions of the Video Interface:

- Sampling the incoming video.

- · Generating the synchronization signals.

- Pixel transfer in Still Image Compression.

- Pixel transfer in Still Image Decompression.

# 5.2.1 Sampling The Incoming Video

The ZR36067's Video Front End (VFE) interfaces to a standard YUV 4:2:2 video bus. It samples the Y7..0, UV7..0, HSYNC and VSYNC with every other positive edge of VCLKx2. The valid positive edge (out of every two consecutive ones), which is the one used for sampling, is qualified by VCLK. The qualifying polarity of VCLK is configured by the host. This scheme makes the ZR36067 compatible with a wide range of digital video sources and immune to board-level parasitic delays. VCLKx2 (positive edges) is used internally in the video processing pipeline.

The VFE generates a field indication signal targeted to some internal video processing units. There are two alternative ways of generating the field indication. With devices that output a field indication, the VFE uses the FI input as an indicator of the current field identity. The interpretation of the logical level of FI (top or bottom field) is configured by the host. With devices that do not provide such an indication, the VFE infers the field identity from the relationship of HSYNC to VSYNC.

The VFE can capture square pixel and CCIR-601 formats, or user defined formats, within the limitation of its parameters. The maximum theoretical total input resolution is 1023 pixels/line x 1023 lines per frame. Cropping of the input image is possible by proper configuration of the VFE parameters.

Table 1 lists the Video Front End parameters. The host software needs to configure these parameters according to the timing parameters of the video source (e.g., SAA7110, SAA7111, ZR36060, etc.) and the required cropping. Note that these parameters relate to the input video, and not to the destination video window.

#### **Table 1: Video Front-End Parameters**

| Parameter | Description                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| VStart    | Number of lines (HSYNCs) from the active edge (pos-<br>itive or negative, according to VSPol) of VSYNC to the<br>first line to be sampled. |

| HStart    | Number of pixel clocks in a line from the active edge of HSYNC until the first pixel to be sampled.                                        |

| VEnd      | Number of lines (HSYNCs) from the active edge (pos-<br>itive or negative, according to VSPol) of VSYNC to the<br>last line to be sampled.  |

| Parameter | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HEnd      | Number of pixel clocks in a line from the active edge of HSYNC until the last pixel to be sampled.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ExtFl     | This one bit parameter indicates whether the video source provides a field indication signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HSPol     | The HSYNC polarity. HStart and HEnd are counted<br>from the active edge of HSYNC. '1' means that HStart,<br>HEnd will be counted from the negative edge of<br>HSYNC. Also determines signal polarity when<br>SyncMstr='1'.                                                                                                                                                                                                                                                                                                                                   |

| VSPol     | The VSYNC polarity. VStart and VEnd are counted<br>from the active edge of VSYNC. '1' means that VStart,<br>VEnd will be counted from the negative edge of<br>VSYNC. Also determines signal polarity when<br>SyncMstr='1'.                                                                                                                                                                                                                                                                                                                                   |

| TopField  | Top Field Interpretation. If field indication is derived<br>from the FI input signal (see ExtFI), TopField indicates<br>the interpretation of the FI signal:<br>TopField='1' - FI high indicates the top field.<br>TopField='0' - FI low indicates the top field.<br>If field indication is derived internally from HSYNC and<br>VSYNC, TopField indicates the interpretation of the<br>level of HSYNC as sampled by the active edge of<br>VSYNC:<br>TopField='1' - HSYNC high indicates the top field.<br>TopField='0' - HSYNC low indicates the top field. |

| VCLKPol   | Polarity of VCLK as a data qualifier. If VCLKPol=1 the video input is sampled with those positive edges of VCLKx2 that correspond to VCLK=1. If VCLKPol=0, the video input is sampled by those positive edges of VCLKx2 that correspond to VCLK=0.                                                                                                                                                                                                                                                                                                           |

# 5.2.2 Synchronization Signal Generation

The ZR36067 supports internal generation of the video synchronization signals. In this mode (when *SyncMstr*=1) the ZR36067 generates and drives VSYNC and HSYNC signals. Using software programmable parameters, the ZR36067 can generate various video synchronization signal formats.

Table 3 lists the sync signal parameters. The host software configures those parameters according the mode of operation and the video peripheral devices used. Note that he polarity of the sync signals is determined by the VSPol and HSPol parameters (Table 2).

# **Table 2: Synchronization Signal Parameters**

| Parameter   | Meaning                                                                  |

|-------------|--------------------------------------------------------------------------|

| FrmTot      | Total number of lines per frame<br>(e.g., in NTSC: 525)                  |

| LineTot     | Total number of pixel clocks per line<br>(e.g., in CCIR NTSC: 858)       |

| VsyncSize   | The length of the VSYNC signal, measured in lines.                       |

| Hsync Start | The point in the scan line at which the HSYNC signal should be asserted. |

# **AV PCI CONTROLLER**

The ZR36067 Video Interface drives out the video synchronization signals synchronized with the negative edge of VCLKx2 (every other edge). The VCLK input is used as a phase qualifier.

The timing of the rising and the falling edges of VSYNC with respect to the HSYNC signal are:

- Odd fields The edges of VSYNC occur in the middle of the non-active portion of HSYNC.

- Even fields The edges of VSYNC occur in the middle of the active portion of HSYNC.

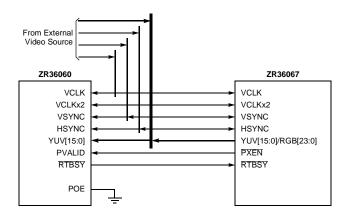

#### 5.2.3 ZR36067 Connection To ZR36060 Video Interface

Figure 3 shows the recommended connections between the ZR36067 and the ZR36060 Video Interface. For recommended connections between the ZR36067 and the ZR36016 Video Interface, refer to the ZR36057 data sheet.

# Figure 3. Recommended Connection of ZR36067 to ZR36060 Video Interface

In Motion Video Compression, the YUV video and synchronization signals are driven by the external video source (for example, a SAA7110) to the inputs of the ZR36067 and ZR36060.

In Motion Video Decompression, the synchronization signals are driven by the ZR36067 (in sync master mode) or by an external sync generator, associated with the video source. The decompressed digital video is transferred from the ZR36060 video bus to the ZR36067 video interface. The video bus of the external video source, and if necessary its sync signals, must be forced to float, typically using software control.

In Still Image Compression, the video bus as well as the sync signals are driven by the ZR36067. Therefore, the video bus of the external video source (such as the video decoder of Figure 1), and if necessary its sync signals, must be forced to float.

In Still Image Decompression mode, the sync signals are driven by the ZR36067. Decompressed video is transferred from the ZR36060 to the ZR36067's Video Interface. In this mode of operation, the video bus and sync signals of an external video source (such as the video decoder of Figure 1) must be forced to float.

Table 3 defines the ZR36060 and ZR36067 parameters which define the portion of the field to be processed (the active portion).

# Table 3: Parameters Defining The Active Portion Of AField

| ZR36067<br>Parameter | ZR36060<br>Parameter              | Meaning                                                                    |

|----------------------|-----------------------------------|----------------------------------------------------------------------------|

| NAX                  | HStart                            | The number of pixels to be skipped, counted from the active edge of HSYNC. |

| PAX                  | HEnd-HStart                       | The number of active pixels in a line.                                     |

| NAY                  | VStart                            | The number of lines to be skipped counted from the active edge of VSYNC.   |

| PAY                  | VEnd-VStart                       | The number of active lines in a field.                                     |

| Odd_Even             | FIDet with<br>the FRAME<br>signal |                                                                            |

#### 5.2.3.1 START Signal Control

The START Signal is used with the ZR36016 only, to start the Compression/Decompression process at the correct time for the desired field type.

#### 5.2.3.2 PXEN Signal Control

The ZR36067 drives the PVALID input of the ZR36060. While PVALID is deactivated, the ZR36060 does not sample the video bus and the video sync inputs.

To keep the ZR36067 and the ZR36060 synchronized, deactivation of PXEN by the ZR36067 also 'holds' the horizontal counting and processing inside the ZR36067.

In Motion Video Compression mode, PXEN is activated continuously.

In Motion Video Decompression mode, PXEN is asserted by then ZR36067 after latching the rising edge of RTBSY, indicating that the first strip is ready in the ZR36060 strip memory.

In Still Image Compression mode, the image is transferred to the ZR36067 by the host software pixel by pixel. PXEN is activated only when a pixel is ready to be sent out from the ZR36067 Video Interface to the ZR36060 video input.

In Still Image Decompression mode, the image is read from the ZR36067 by the host software pixel by pixel. <u>PXEN</u> is activated to get the next pixel from the ZR36060 only after the previous pixel has been read by the host.

PXEN can be de-asserted dynamically (in the middle of a process) in response to several different conditions. The dynamic de-assertion is enabled independently by three configuration bits - VFIFO\_FB, CFIFO\_FB, RTBSY\_FB. The host

# **Z<b>@RAN**

software is allowed to set those bits only while the ZR36067 is the sync master.

When VFIFO\_FB is set, if the Video FIFO is close to overflow status, PXEN is de-asserted to hold the ZR36060 video output until the Video FIFO is emptied. When CFIFO\_FB is set, if the Code FIFO underflows, and CBUSY is asserted, PXEN is de-asserted to hold the ZR36060 video output until the Code FIFO is filled. When RTBSY\_FB is set, if RTBSY is asserted by the ZR36060 during the active portion of the field, PXEN is de-asserted until RTBSY is de-asserted.

# 5.2.3.3 RTBSY Signal Control

The ZR36067's RTBSY input is connected to the ZR36060's RTBSY output. The ZR36067 uses RTBSY to detect overflow and underflow conditions in the ZR36060 strip memory.

In Motion Video Compression mode, if RTBSY is asserted when the first active pixel of a line is sampled, a condition that indicates a strip buffer overflow, the ZR36067 abandons the compression process for the field and waits for the beginning of the following field.

In Motion Video Decompression mode, de-assertion of RTBSY is used to decide when to initiate the decompression process.

In all modes, when RTBSY\_FB is set, RTBSY is checked by the ZR36067 at the following times:

- Before the trailing edge of VSYNC, which triggers the start of a new field process in the ZR36060,

- During the active portion of the field.

The ZR36067 de-asserts PXEN if RTBSY is asserted at those times. PXEN is asserted again after RTBSY is de-asserted.

# 5.2.4 Pixel Transfer In Still Image Compression Mode

The image is transferred by the host software to the ZR36067's extended 24-bit video bus. The host writes the pixels one by one to a dedicated register (the Still Transfer register) in the ZR36067. Each pixel is synchronized with the video clock and transferred to the Video Interface port.

Two modes of host access are supported:

- The host verifies, by polling, the availability of the Still Transfer register before each pixel write access. Typically, this mode would be used after writing the first pixel of each line, before writing the remainder of the line.

- The host configures the WaitState parameter and writes the pixels continuously to the Still Transfer register. The ZR36067 de-asserts the PCI TRDY signal every host access with the timing specified by the WaitState parameter. Typically, this mode would be used to transfer the pixels of a line after the first.

The Still Transfer write protocol and the associated internal mechanism of the ZR36067 are described below:

- The host writes a pixel using a single data phase memory write cycle. The pixel is latched in the Still Transfer register using the PCI clock.

- The Still\_Bsy bit is set.

- The incoming pixel is synchronized with the Video Interface clock. The PXEN output signal is asserted and the pixel is driven out on the correct video clock phase.

- Feedback from the Video Interface resets the Still\_Bsy bit, indicating that the video port is empty and the following host write is permitted.

# 5.2.5 Pixel Transfer In Still Image Decompression Mode

The image is transferred from the ZR36067's extended 24-bit video bus to system memory. The host software reads the pixels one by one from the Still Transfer register. After each pixel is fetched from the video port, it is synchronized with the PCI clock, ready to be read by the software.

Before each read access, the host software should check the Still\_Bsy bit to verify availability of data in the register. The register contents are valid only if the Still\_Bsy bit is 0. Note that by configuring the WaitState parameter, it is possible to ensure that the Still Transfer register will be valid every read access, making it unnecessary to check the Still\_Bsy bit.

The protocol for a still image decompression read operation, and the ZR36067's behavior, are as follows:

- The ZR36067 checks the Still\_Bsy bit. If it is 1, meaning that the previous valid pixel was read by the host, the ZR36067 fetches a new pixel from the ZR36016.

- PXEN is asserted, causing a new pixel to be driven onto the video bus.

- The new pixel is synchronized with the PCI clock and latched in the Still Transfer register.

- Still\_Bsy is reset to 0, to indicate that a new valid pixel is available.

- The host software reads the pixel by means of a memory read access to the Still Transfer register, and Still\_Bsy is set to 1.

# 5.3 GuestBus Interface

The ZR36067 masters a generic MCU-style bus intended to concurrently host up to eight slave devices (referred to as "guests"). The bus consists of 8 data lines (GDAT[7:0]), 3 address lines (GADR[2:0]), 8 active-low chip-select lines (GCS[7:0]), read and write signals (GRD, GWR), and a wait-state insertion line (GWS). The bus also includes two interrupt-request inputs (GIRQ[1:0]) and one status/acknowledge input (GRDY). Three types of data transfers are possible on the guest bus. One is a code-write cycle, initiated by the code DMA controller of the ZR36067, targeted to one of the guests, configured a-priori for

# **AV PCI CONTROLLER**

such write cycles<sup>[2]</sup>. The second is a GO command to the ZR36050 (configured a priori as one of the guests) in JPEG mode; the same type of bus cycle can be used to toggle the START pin of the ZR36060. The third is a PostOffice cycle, initiated by the host software, targeted to any one of the eight guests; in particular, PostOffice cycles are used to program the ZR36060, or the ZR36050 and ZR36016.

### 5.3.1 Flexible GuestBus Timing

Different guest devices may have different bus timing requirements. In order to meet these requirements and still master the GuestBus efficiently, the ZR36067 has two timing parameters for each guest:

$T_{gdurN}$  is the duration of a  $\overline{GWR}$  or  $\overline{GRD}$  signal when accessing guest N.

$T_{grecN}$  is the minimum recovery time in which  $\overline{GRD}$  and  $\overline{GWR}$  must be non active after the rising edge of the previous access (read or write) to guest N.

$T_{gdur}$  and  $T_{grec}$  are configured by the host in units of PCI clock (3,4,12 or 15 PCI clocks are the possible values).

Additional timing parameters are given in section 15.0 "AC Timing Specifications".

### 5.3.2 Code-Write Operations

Code-Write cycles are initiated by the GuestBus master if all of the conditions below are met:

- The CFIFO is not empty.

- A PostOffice request is not pending.

- The GRDY input is high ('1').

A code-write cycle consists of reading one code byte from the CFIFO and writing it to the guest selected by the host for codewrite cycles, to the register address configured by the host. The timing parameters of the code-write cycle are those programmed by the host for this specific guest device. Note that the same parameters apply for PostOffice accesses to this guest.

#### 5.3.3 Doubleword to Bytes Mapping in Code-Write Operations

The code is read in doublewords from main memory, and transferred in bytes to the guest device. The ordering of the bytes is such that the least significant byte of the doubleword is the first one to be sent over the GuestBus, and the most significant byte is the last one.

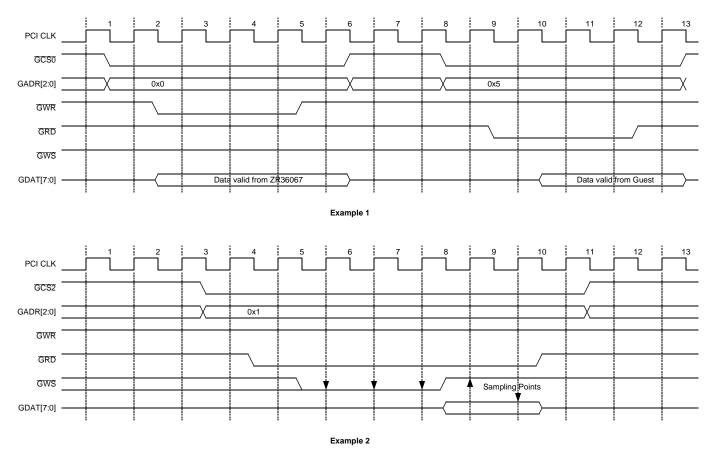

#### 5.3.4 PostOffice Operations

When the PostOffice pending bit (POPen) in the PostOffice register is set to '1', the GuestBus master completes the current code-write cycle (if such is executed), and executes a PostOffice cycle, even when the Code FIFO is not empty. The type of the cycle (read or write) is determined by the PostOffice direction bit

(PODir). The identity of the targeted guest and its specific register are also specified by the PostOffice register. In both read and write cycles the timing parameters of the cycle are those configured by the host for the targeted guest. Upon completion of a PostOffice cycle, the pending bit is reset to '0' by the ZR36067.

PostOffice Write: The GuestBus master transfers the least significant 8 bits of the PostOffice register out on the bus.

PostOffice Read: The GuestBus master reads from the specified target and writes the input byte into the least significant 8 bits of the PostOffice register (POData)

#### 5.3.5 GuestBus Wait States

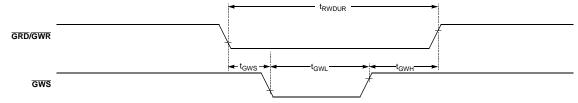

Slow guests that are equipped with a "bus hold" output can force a code-write or PostOffice GuestBus cycle to be extended by one or more additional PCI clocks, by asserting the  $\overline{GWS}$  signal.  $\overline{GWS}$  is first sampled with the PCI clock that precedes the one that triggers the de-assertion of  $\overline{GWR}$  or  $\overline{GRD}$  (if  $T_{gdur}$  of the accessed guest is M PCI clocks,  $\overline{GWS}$  is sampled M-1 clocks after the assertion of  $\overline{GWR}$  or  $\overline{GRD}$ ). When  $\overline{GWS}$  is sampled high again, the cycle is completed.

Insertion of wait states is possible during both code-write and PostOffice cycles.

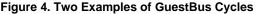

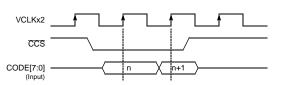

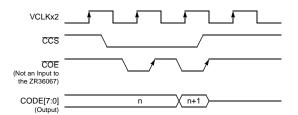

The maximum number of PCI clock cycles allowed for GRD or GWR, including wait-states, is 64. If a guest holds the cycle until this limit expires, the GuestBus master aborts the cycle. If the cycle was a PostOffice one, the PostOffice time-out bit of the PostOffice register is set to '1', and the PostOffice pending bit is cleared. If the cycle was a code-write (or code-read, if viewed from the PCI side), the code-write time-out flag (CodTime) is set to '1'.